#### **FEATURES AND BENEFITS**

- Automotive AEC-Q100 qualified

- V<sub>IN</sub> operating range from 3 to 36 V, with 40 V maximum

- Buck or buck-boost pre-regulator (VREG)

- Adjustable PWM switching frequency: 250 kHz to 2.4 MHz

- PWM frequency can be synchronized to external clock

- Two internal LDO regulators with foldback short-circuit protection

- Power-on reset (NPOR) with fixed delay of 22.5 ms

- Programmable window watchdog timer with a fixed activation delay of 30 ms

- Active low, watchdog timer enable/disable pin (WD<sub>ENn</sub>)

- Dual bandgaps for increased reliability:

- □ BG1 for VREG, 3V3, and VCP reference

- □ BG2 for V5 reference, and VREG, 3V3, and VCP fault detection

- Ignition-enable input (ENBAT)

- Frequency dithering helps reduce EMI/EMC

- Undervoltage protection for all output rails

- Pin-to-pin and pin-to-ground tolerant at every pin

- · Thermal shutdown protection

- -40°C to 150°C junction temperature range

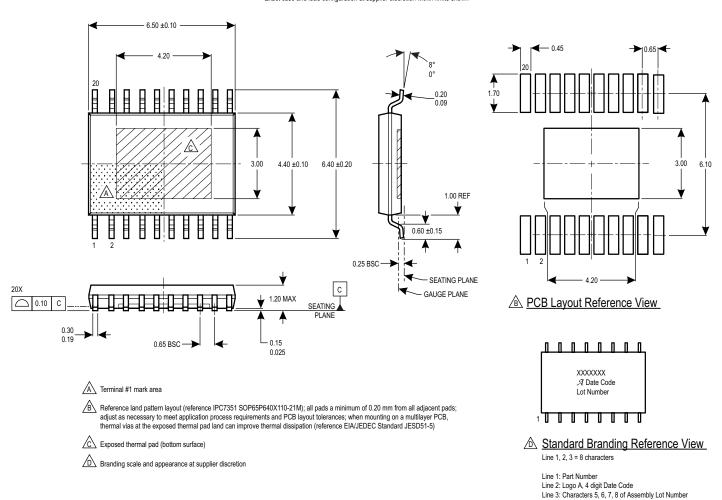

#### PACKAGE: 20-Pin eTSSOP (suffix LP)

Not to scale

#### **DESCRIPTION**

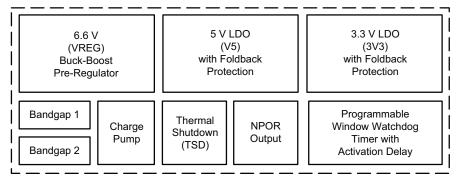

The ARG81401 is a power management IC that uses a buck or buck-boost pre-regulator to efficiently convert automotive battery voltages into a tightly regulated intermediate voltage, complete with control, diagnostics, and protections. The output of the pre-regulator supplies a 5 V, 300 mA LDO and a 3.3 V, 200 mA LDO. Designed to supply CAN or microprocessor power supplies in high-temperature environments, the ARG81401 is ideal for underhood applications.

Enable-input to the ARG81401 is compatible to a high-voltage battery level (ENBAT).

Diagnostic outputs from the ARG81401 include a poweron-reset output (NPOR) with a fixed 22.5 ms typical delay. Dual bandgaps, one for regulation and one for fault checking, improve long-term reliability of a system designed around the ARG81401.

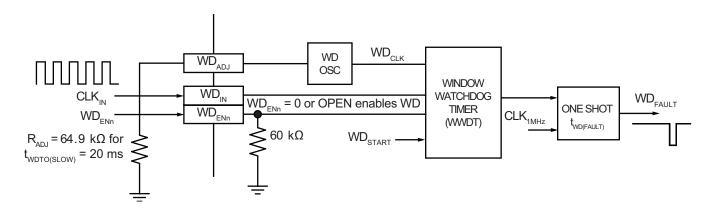

The ARG81401 contains a window watchdog timer that can be programmed to accept a wide range of clock frequencies (WD<sub>ADJ</sub>). The watchdog timer has a fixed 30 ms activation delay to accommodate processor startup. The watchdog timer has an enable/disable pin (active low, WD<sub>ENn</sub>) to facilitate initial factory programming or field reflash programming.

Continued on next page...

#### **APPLICATIONS**

Provides System Power for ( $\mu$ C/DSP, CAN, sensors, etc.) in Automototive Control Modules, such as:

- Electronic Power Steering (EPS)

- Transmission Control Units (TCU)

- Advanced Braking Systems (ABS)

- · Emissions Control Modules

- Other automotive applications

ARG81401 Simplified Block Diagram

# Adjustable Frequency Buck or Buck-Boost Pre-Regulator with 2 LDOs, Window Watchdog Timer, and NPOR

#### **DESCRIPTION** (continued)

Protection features include dual control loop for pre-regulator rail. In case of a shorted output, all linear regulators feature foldback overcurrent protection. The switching regulator includes pulse-by-pulse current limit, hiccup mode short-circuit protection, LX short-circuit protection, missing asynchronous diode protection, and thermal shutdown.

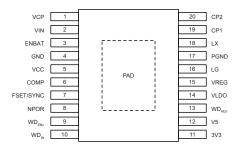

The ARG81401 is supplied in a low-profile (1.2 mm maximum height), 20-lead eTSSOP package (suffix "LP") with exposed thermal pad.

#### **SELECTION GUIDE**

| Part Number Package |                                | Packing [1]                 | Lead Frame     |  |

|---------------------|--------------------------------|-----------------------------|----------------|--|

| ARG81401KLPATR      | 20-pin eTSSOP with thermal pad | 4000 pieces per 13-in. reel | 100% Matte Tin |  |

<sup>[1]</sup> Contact Allegro for additional packing options.

#### ABSOLUTE MAXIMUM RATINGS [2]

| Characteristic            | Symbol                              | Notes                              | Rating                        | Unit |

|---------------------------|-------------------------------------|------------------------------------|-------------------------------|------|

| VIN pin                   | V <sub>IN</sub>                     |                                    | -0.3 to 40                    | V    |

|                           | .,                                  |                                    | -0.3 to 8                     | V    |

| ENBAT pin                 | V <sub>ENBAT</sub>                  | With current limiting resistor [3] | -13 to 40                     | V    |

|                           | I <sub>ENBAT</sub>                  |                                    | ±75                           | mA   |

|                           |                                     |                                    | -0.3 to V <sub>IN</sub> + 0.3 | V    |

| LX pin                    | $V_{LX}$                            | t < 250 ns                         | -1.5                          | V    |

|                           |                                     | t < 50 ns                          | V <sub>IN</sub> + 3           | V    |

| VCP, CP1, and CP2 pins    | V <sub>VCP</sub> , V <sub>CPx</sub> |                                    | -0.3 to 50                    | V    |

| All other pins            |                                     |                                    | -0.3 to 7.5                   | V    |

| Junction Temperature      | T <sub>J</sub>                      |                                    | -40 to 150                    | °C   |

| Storage Temperature Range | T <sub>S</sub>                      |                                    | -55 to 150                    | °C   |

<sup>[2]</sup> Stresses beyond those listed in this table may cause permanent damage to the device. The absolute maximum ratings are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the Electrical Characteristics table is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

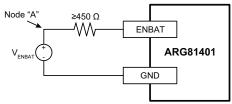

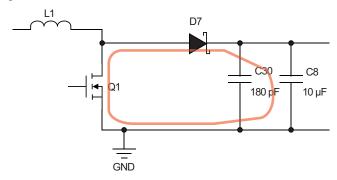

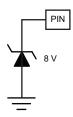

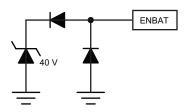

<sup>[3]</sup> The higher ENBAT ratings (-13 V and 40 V) are measured at node "A" in the following circuit configuration:

#### THERMAL CHARACTERISTICS: May require derating at maximum conditions; see application information

| Characteristic                         | Symbol          | Test Conditions [4]    | Value | Unit |

|----------------------------------------|-----------------|------------------------|-------|------|

| Junction-to-Ambient Thermal Resistance | $R_{\theta JC}$ | eTSSOP-20 (LP) Package | 32    | °C/W |

<sup>[4]</sup> Additional thermal information available on the Allegro website.

# Adjustable Frequency Buck or Buck-Boost Pre-Regulator with 2 LDOs, Window Watchdog Timer, and NPOR

#### **Table of Contents**

| Features and Benefits            | 1  |

|----------------------------------|----|

| Description                      | 1  |

| Applications                     | 1  |

| Package                          | 1  |

| Simplified Block Diagram         | 1  |

| Selection Guide                  | 2  |

| Absolute Maximum Ratings         | 2  |

| Thermal Characteristics          | 2  |

| Functional Block Diagram         | 4  |

| Pinout Diagram and Terminal List | 5  |

| Electrical Characteristics       | 6  |

| Startup and Shutdown Logic       | 14 |

| Summary of Fault Mode Operation  |    |

| Timing Diagrams                  | 17 |

| Design and Component Selection   |    |

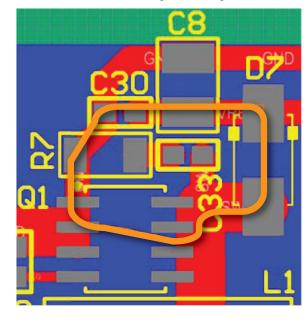

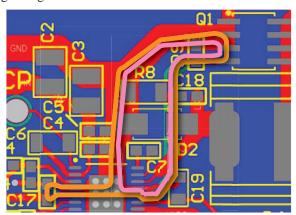

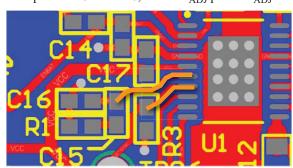

| PCB Layout Guidelines            |    |

| Pin ESD Structures               | 29 |

| Package Outline Drawing          | 30 |

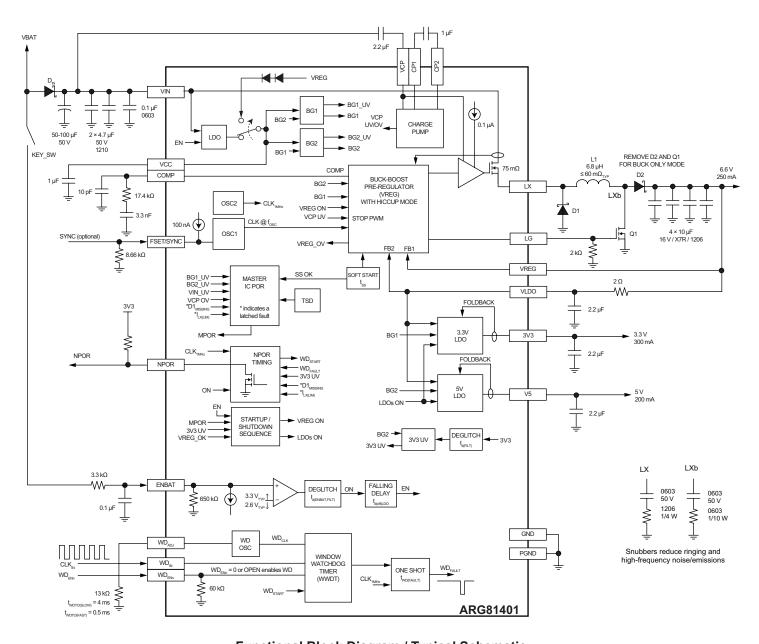

Functional Block Diagram / Typical Schematic

Buck-Boost Mode ( $f_{OSC} = 2 \text{ MHz}$ )

#### PINOUT DIAGRAM AND TERMINAL LIST

Package LP, 20-Pin eTSSOP Pinout Diagram

#### **Terminal List**

| Number | Name              | Function                                                                                      |

|--------|-------------------|-----------------------------------------------------------------------------------------------|

| 1      | VCP               | Charge pump reservoir capacitor                                                               |

| 2      | VIN               | Input voltage                                                                                 |

| 3      | ENBAT             | Ignition-enable input from the key/switch through a 1 kΩ resistor                             |

| 4      | GND               | Ground                                                                                        |

| 5      | VCC               | Internal voltage regulator bypass capacitor pin                                               |

| 6      | COMP              | Error amplifier compensation network pin for the buck-boost pre-regulator                     |

| 7      | FSET/<br>SYNC     | Frequency setting and synchronization input                                                   |

| 8      | NPOR              | Active low, open-drain regulator fault detection output                                       |

| 9      | WD <sub>ENn</sub> | Watchdog enable pin: Open/Low – WD is enabled, High – WD is disabled                          |

| 10     | WD <sub>IN</sub>  | Watchdog refresh input (rising edge triggered) from a microcontroller or DSP                  |

| 11     | 3V3               | 3.3 V, 300 mA regulator output                                                                |

| 12     | V5                | 5 V, 200 mA regulator output                                                                  |

| 13     | WD <sub>ADJ</sub> | The watchdog window time is programmed by connecting $R_{\text{ADJ}}$ from this pin to ground |

| 14     | VLDO              | Input for the LDOs                                                                            |

| 15     | VREG              | Feeback pin for VREG output, connect to VREG converter output capacitors                      |

| 16     | LG                | Boost gate drive output for the buck-boost pre-regulator                                      |

| 17     | PGND              | Power ground                                                                                  |

| 18     | LX                | Switching node for the buck-boost pre-regulator                                               |

| 19     | CP1               | Charge pump capacitor connection                                                              |

| 20     | CP2               | Charge pump capacitor connection                                                              |

| _      | PAD               |                                                                                               |

# Adjustable Frequency Buck or Buck-Boost Pre-Regulator with 2 LDOs, Window Watchdog Timer, and NPOR

## ELECTRICAL CHARACTERISTICS – GENERAL SPECIFICATIONS [1]: Valid at 3 V $\leq$ V<sub>IN</sub> $\leq$ 36 V in buck-boost mode and V<sub>IN</sub> having first reached V<sub>IN(START)</sub>, –40°C $\leq$ T<sub>J</sub> $\leq$ 150°C, unless otherwise specified.

| Characteristic                  | Symbol                        | Test Conditions                                                                                     | Min. | Тур. | Max. | Unit |  |  |

|---------------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------|------|------|------|------|--|--|

| GENERAL SPECIFICATIONS          |                               |                                                                                                     |      |      |      |      |  |  |

|                                 |                               | After V <sub>IN</sub> > V <sub>IN(START)</sub> , V <sub>ENBAT</sub> ≥ 4 V, buck-boost pre-regulator | 3    | 13.5 | 36   | V    |  |  |

| Operating Input Voltage         | V <sub>IN</sub>               | After V <sub>IN</sub> > V <sub>IN(START)</sub> , V <sub>ENBAT</sub> ≥ 4 V, buck preregulator        | 5.5  | 13.5 | 36   | V    |  |  |

| VIN UVLO Start                  | V <sub>IN(START)</sub>        | V <sub>IN</sub> rising                                                                              | -    | -    | 5    | V    |  |  |

| VIN UVLO Stop                   | V <sub>IN(STOP)</sub>         | V <sub>IN</sub> falling, when in buck-boost mode                                                    | -    | -    | 2.9  | V    |  |  |

| Supply Quippont Current [1]     | I <sub>Q</sub>                | V <sub>IN</sub> = 13.5 V, V <sub>ENBAT</sub> ≥ 4 V, no load on VREG                                 | -    | 10   | _    | mA   |  |  |

| Supply Quiescent Current [1]    | I <sub>Q(SLEEP)</sub>         | V <sub>IN</sub> = 13.5 V, V <sub>ENBAT</sub> ≤ 2 V, no load on VREG                                 | -    | _    | 10   | μA   |  |  |

| PWM SWITCHING FREQUEN           | CY AND DITHERI                | NG                                                                                                  |      |      |      |      |  |  |

| Switching Frequency             | f                             | $R_{FSET}$ = 8.66 k $\Omega$                                                                        | 1.8  | 2    | 2.2  | MHz  |  |  |

| Switching Frequency             | f <sub>OSC</sub>              | $R_{FSET}$ = 57.6 k $\Omega$                                                                        | 343  | 400  | 457  | kHz  |  |  |

| Frequency Divide By 2 Start [2] | V <sub>IN(FREQ/2,START)</sub> | V <sub>IN</sub> rising, frequency = f <sub>OSC</sub> /2                                             | 18   | 19   | 20   | V    |  |  |

| Frequency Divide By 2 Stop [2]  | V <sub>IN(FREQ/2,STOP)</sub>  | V <sub>IN</sub> falling, frequency = f <sub>OSC</sub> /2                                            | 17   | 18   | 19   | V    |  |  |

| Frequency Dithering             | $\Delta f_{OSC}$              | As a percent of f <sub>OSC</sub>                                                                    | _    | ±12  | _    | %    |  |  |

| VIN Dithering START Threshold   | .,                            | Low range, V <sub>IN</sub> rising                                                                   | 9    | 9.5  | 10   | V    |  |  |

| VIN Differing START Threshold   | V <sub>IN(DITHER,ON)</sub>    | High range, V <sub>IN</sub> falling                                                                 | 17   | 18   | 19   | V    |  |  |

| VIN Dithering STOP Threshold    | V                             | Low range, V <sub>IN</sub> falling                                                                  | 8.5  | 9    | 9.5  | V    |  |  |

| VIN Differing 310F Tilleshold   | V <sub>IN(DITHER,OFF)</sub>   | High range, V <sub>IN</sub> rising                                                                  | 18   | 19   | 20   | V    |  |  |

| VIN Dithering Hysteresis        | V <sub>IN(DITHER,HYS)</sub>   |                                                                                                     | _    | 500  | _    | mV   |  |  |

| CHARGE PUMP (VCP)               |                               |                                                                                                     |      |      |      |      |  |  |

| Output Voltage                  | ΔV <sub>VCP</sub>             | $V_{VCP} - V_{IN}$                                                                                  | 4.1  | 6.6  | _    | V    |  |  |

| Switching Frequency             | f <sub>SW(CP)</sub>           |                                                                                                     | _    | 65   | _    | kHz  |  |  |

| VCC OUTPUT                      |                               |                                                                                                     |      |      |      |      |  |  |

| Output Voltage                  | V <sub>VCC</sub>              | V <sub>VREG</sub> = 6.6 V                                                                           | -    | 4.6  | _    | V    |  |  |

| THERMAL PROTECTION              |                               |                                                                                                     |      |      |      |      |  |  |

| Thermal Shutdown Threshold [2]  | T <sub>TSD</sub>              | $T_J$ rising                                                                                        | 160  | 170  | 180  | °C   |  |  |

| Thermal Shutdown Hysteresis [2] | T <sub>HYS</sub>              |                                                                                                     | _    | 20   | _    | °C   |  |  |

<sup>[1]</sup> Negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>[2]</sup> Ensured by design and characterization, not production tested.

# Adjustable Frequency Buck or Buck-Boost Pre-Regulator with 2 LDOs, Window Watchdog Timer, and NPOR

## ELECTRICAL CHARACTERISTICS – BUCK AND BUCK-BOOST PRE-REGULATOR SPECIFICATIONS [1]: Valid at $3 \text{ V} \le \text{V}_{\text{IN}} \le 36 \text{ V}$ in buck-boost mode and $\text{V}_{\text{IN}}$ having first reached $\text{V}_{\text{IN}(\text{START})}$ , –40°C $\le \text{T}_{\text{J}} \le 150$ °C, unless otherwise specified.

| Characteristic                                    | Symbol                     | Test Conditions                                                                                                                       | Min. | Тур. | Max. | Unit |

|---------------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| OUTPUT VOLTAGE SPECIFICAT                         | IONS                       |                                                                                                                                       | ,    |      |      |      |

| Pre-Regulator Output Voltage – VREG Regulating    | V <sub>VREG</sub>          | V <sub>IN</sub> = 13.5 V, ENBAT = 1,<br>0.1 A ≤ I <sub>VREG</sub> ≤ 1 A                                                               | 6.47 | 6.6  | 6.7  | V    |

| Pre-Regulator Output Voltage –<br>VLDO Regulating | V <sub>VLDO(REG)</sub>     | VREG pin open, measured at VLDO pin,<br>$V_{IN}$ = 13.5 V, ENBAT = 1,<br>0.1 A $\leq$ I <sub>VREG</sub> $\leq$ 1 A                    | 5.88 | 6    | 6.12 | V    |

| PULSE WIDTH MODULATION (P                         | WM)                        |                                                                                                                                       | •    |      |      |      |

| PWM Ramp Offset                                   | V <sub>PWMOFFSET</sub>     | V <sub>COMP</sub> for 0% duty cycle                                                                                                   | _    | 400  | _    | mV   |

| LX Rising Slew Rate [2]                           | SR <sub>LX(RISE)</sub>     | V <sub>IN</sub> = 13.5 V, 10% to 90%, I <sub>VREG</sub> = 1 A                                                                         | _    | 1.7  | _    | V/ns |

| LX Falling Slew Rate [2]                          | SR <sub>LX(FALL)</sub>     | V <sub>IN</sub> = 13.5 V, 10% to 90%, I <sub>VREG</sub> = 1 A                                                                         | _    | 1.5  | _    | V/ns |

| Buck Minimum On-Time [2]                          | t <sub>ON(BUCK,MIN)</sub>  |                                                                                                                                       | _    | 85   | 160  | ns   |

| Buck Minimum Off-Time                             | t <sub>OFF(BUCK,MIN)</sub> |                                                                                                                                       | _    | 0    | _    | ns   |

| Buck Maximum Duty Cycle                           | D <sub>BUCK(MAX)</sub>     |                                                                                                                                       | _    | 100  | -    | %    |

| Boost Minimum On-Time                             | t <sub>ON(BOOST,MIN)</sub> |                                                                                                                                       | _    | 60   | 120  | ns   |

| Boost Maximum Duty Cycle                          | D <sub>BOOST(MAX)</sub>    | V <sub>IN</sub> = 3.5 V                                                                                                               | _    | 70   | _    | %    |

| COMP to LX Current Gain                           | g <sub>m(POWER)</sub>      |                                                                                                                                       | _    | 4.5  | _    | A/V  |

| Slope Compensation [2]                            | S <sub>E</sub>             | f <sub>OSC</sub> = 2 MHz                                                                                                              | 3.84 | 4.8  | 5.76 | A/µs |

| Slope Compensation 1-3                            |                            | f <sub>OSC</sub> = 400 kHz                                                                                                            | 0.76 | 0.96 | 1.16 | A/µs |

| INTERNAL MOSFET                                   |                            |                                                                                                                                       |      |      |      |      |

|                                                   |                            | $V_{IN} = 13.5 \text{ V}, T_J = -40^{\circ}\text{C}$ [2], $I_{DS} = 0.1 \text{ A}$                                                    | _    | 60   | 75   | mΩ   |

| MOSFET On Resistance                              | R <sub>DS(on)</sub>        | $V_{IN}$ = 13.5 V, $T_J$ = 25°C [2], $I_{DS}$ = 0.1 A                                                                                 | _    | 80   | 100  | mΩ   |

|                                                   |                            | $V_{IN} = 13.5 \text{ V}, T_J = 150^{\circ}\text{C}, I_{DS} = 0.1 \text{ A}$                                                          | _    | 140  | 170  | mΩ   |

|                                                   |                            | $V_{ENBAT} \le 2 \text{ V}, V_{LX} = 0 \text{ V}, V_{IN} = 13.5 \text{ V}, -40^{\circ}\text{C} \le T_{J} \le 85^{\circ}\text{C}$ [2]  | _    | _    | 10   | μΑ   |

| MOSFET Leakage                                    | I <sub>FET(LEAK)</sub>     | $V_{ENBAT} \le 2 \text{ V}, V_{LX} = 0 \text{ V}, V_{IN} = 13.5 \text{ V}, -40^{\circ}\text{C} \le T_{J} \le 125^{\circ}\text{C}$ [2] | _    | _    | 100  | μА   |

|                                                   |                            | $V_{ENBAT} \le 2 \text{ V}, V_{LX} = 0 \text{ V}, V_{IN} = 13.5 \text{ V}, -40^{\circ}\text{C} \le T_{J} \le 150^{\circ}\text{C}$     | _    | 50   | 150  | μА   |

| ERROR AMPLIFIER                                   | '                          |                                                                                                                                       | '    |      |      |      |

| Open Loop Voltage Gain                            | A <sub>VOL</sub>           |                                                                                                                                       | _    | 65   | _    | dB   |

| Transconductance                                  | g <sub>m(EA)</sub>         |                                                                                                                                       | 550  | 750  | 950  | μA/V |

| Output Current                                    | I <sub>O(EA)</sub>         |                                                                                                                                       | _    | ±75  | _    | μA   |

| Maximum Output Voltage                            | V <sub>O(EA,MAX)</sub>     |                                                                                                                                       | 1.3  | 1.7  | 2.1  | V    |

| Minimum Output Voltage                            | V <sub>O(EA,MIN)</sub>     |                                                                                                                                       | _    | _    | 200  | mV   |

| COMP Pull-Down Resistance                         | R <sub>COMP</sub>          | HICCUP = 1 or FAULT = 1 or IC disabled                                                                                                | _    | 1    | _    | kΩ   |

<sup>[1]</sup> Negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>[2]</sup> Ensured by design and characterization, not production tested.

# Adjustable Frequency Buck or Buck-Boost Pre-Regulator with 2 LDOs, Window Watchdog Timer, and NPOR

## ELECTRICAL CHARACTERISTICS – BUCK AND BUCK-BOOST PRE-REGULATOR SPECIFICATIONS (continued) [1]: Valid at $3 \text{ V} \le \text{V}_{\text{IN}} \le 36 \text{ V}$ in buck-boost mode and $\text{V}_{\text{IN}}$ having first reached $\text{V}_{\text{IN}(\text{START})}$ , –40°C $\le \text{T}_{\text{J}} \le 150$ °C, unless otherwise specified.

| Characteristic                 | Symbol                | Test Conditions                                                                 | Min. | Тур.                | Max. | Unit          |

|--------------------------------|-----------------------|---------------------------------------------------------------------------------|------|---------------------|------|---------------|

| BOOST MOSFET (LG) GATE DRIV    | /ER                   |                                                                                 |      |                     |      |               |

| LG High Output Voltage         | V <sub>LG(ON)</sub>   | V <sub>IN</sub> = 7 V, V <sub>VREG</sub> = 6.35 V                               | 4.6  | _                   | 6.35 | V             |

| LG Low Output Voltage          | V <sub>LG(OFF)</sub>  | V <sub>IN</sub> = 13.5 V, V <sub>VREG</sub> = 6.85 V                            | _    | 0.2                 | 0.4  | V             |

| LG Source Current [1]          | I <sub>LG(ON)</sub>   | $V_{IN} = 7 \text{ V}, V_{VREG} = 6.35 \text{ V}, V_{LG} = 1 \text{ V}$         | _    | -500                | -    | mA            |

| LG Sink Current [1]            | I <sub>LG(OFF)</sub>  | $V_{IN}$ = 13.5 V, $V_{VREG}$ = 6.85 V, $V_{LG}$ = 1 V                          | _    | 500                 | ı    | mA            |

| LG Leakage Current [2]         | I <sub>LG(LEAK)</sub> | $V_{IN}$ = 13.5 V, $V_{VREG}$ = 6.6 V, $V_{LG}$ = 3 V                           | _    | _                   | 10   | μΑ            |

| SOFT START                     |                       |                                                                                 |      |                     |      |               |

| SS Ramp Time                   | t <sub>SS(ramp)</sub> |                                                                                 | _    | 1                   | -    | ms            |

|                                |                       | $0 \text{ V} \leq V_{VREG} \leq 3.3 \text{ V}, V_{COMP} = V_{O(EA,MAX)}$        | _    | f <sub>OSC</sub> /8 | _    | _             |

| SS PWM Frequency Foldback      | f <sub>SW(SS)</sub>   | 0 V ≤ V <sub>VREG</sub> ≤ 3.3 V                                                 | _    | f <sub>OSC</sub> /2 | _    | _             |

|                                |                       | V <sub>VREG</sub> > 3.3 V                                                       | _    | f <sub>OSC</sub>    | -    | _             |

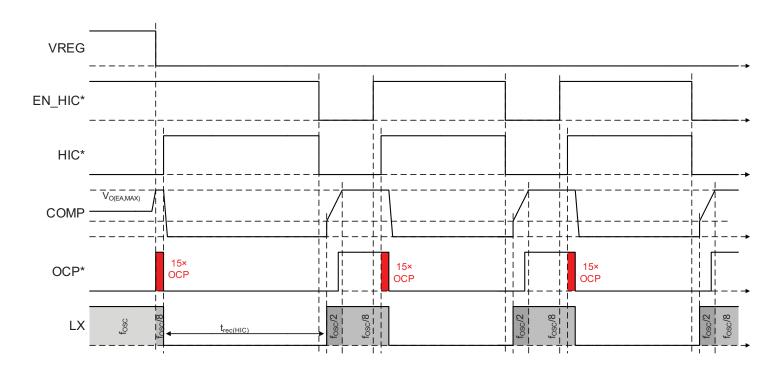

| HICCUP MODE                    |                       |                                                                                 |      |                     |      |               |

| Lliceup OCR DWM Counts         |                       | V <sub>VREG</sub> < 2.4 V (typical), V <sub>COMP</sub> = V <sub>O(EA,MAX)</sub> | _    | 15                  | _    | PWM<br>cycles |

| Hiccup OCP PWM Counts          | t <sub>HIC(OCP)</sub> | V <sub>VREG</sub> > 2.4 V (typical), V <sub>COMP</sub> = V <sub>O(EA,MAX)</sub> | _    | 60                  | _    | PWM<br>cycles |

| Hiccup Mode Recovery Time      | t <sub>rec(HIC)</sub> | LX switching stops to LX switching starts, during VREG overcurrent              | _    | 2                   | _    | ms            |

| CURRENT PROTECTIONS            | *                     |                                                                                 |      |                     |      |               |

| Pulse-by-Pulse Current Limit   | I <sub>LIM</sub>      |                                                                                 | 3.6  | 4.1                 | 4.6  | А             |

| LX Short-Circuit Current Limit | I <sub>LIM(LX)</sub>  |                                                                                 | 6    | 7                   |      | А             |

| MISSING ASYNCHRONOUS DIOD      | E (D1) PROTE          | CTION                                                                           |      |                     |      |               |

| Detection Level                | V <sub>D(OPEN)</sub>  |                                                                                 | -1.5 | -1.3                | -0.9 | V             |

| Time Filtering [2]             | t <sub>D(OPEN)</sub>  |                                                                                 | 50   | _                   | 250  | ns            |

<sup>[1]</sup> Negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

$<sup>\</sup>ensuremath{^{[2]}}$  Ensured by design and characterization, not production tested.

# Adjustable Frequency Buck or Buck-Boost Pre-Regulator with 2 LDOs, Window Watchdog Timer, and NPOR

## ELECTRICAL CHARACTERISTICS – LINEAR REGULATOR (LDO) SPECIFICATIONS [1]: Valid at 3 V $\leq$ V<sub>IN</sub> $\leq$ 36 V in buck-boost mode and V<sub>IN</sub> having first reached V<sub>IN(START)</sub>, –40°C $\leq$ T<sub>J</sub> $\leq$ 150°C, unless otherwise specified.

| Characteristic                   | Symbol                   | Test Conditions                                                                           | Min. | Тур. | Max. | Unit |

|----------------------------------|--------------------------|-------------------------------------------------------------------------------------------|------|------|------|------|

| V5 LINEAR REGULATOR              |                          |                                                                                           |      |      |      |      |

| V5 Accuracy and Load Regulation  | $V_{V5}$                 | 10 mA ≤ I <sub>V5</sub> ≤ 200 mA, V <sub>VREG</sub> = 5.4 V                               | 4.9  | 5    | 5.1  | V    |

| V5 Dropout                       | V <sub>V5(DROPOUT)</sub> | I <sub>V5</sub> = 200 mA, V <sub>VLDO</sub> = 4.91 V                                      | 4.75 | -    | -    | V    |

| V5 Output Capacitance Range [2]  | C <sub>V5(OUT)</sub>     |                                                                                           | 1    | -    | 22   | μF   |

| V5 OVERCURRENT PROTECTIO         |                          |                                                                                           | •    |      | •    |      |

| V5 Current Limit [1]             | I <sub>V5(LIM)</sub>     | V <sub>V5</sub> = 5 V                                                                     | -230 | -325 | _    | mA   |

| V5 Foldback Current [1]          | I <sub>V5(FB)</sub>      | V <sub>V5</sub> = 0 V                                                                     | -80  | -120 | -160 | mA   |

| V5 STARTUP                       |                          |                                                                                           |      |      |      |      |

| V5 Startup Time [2]              | t <sub>V5(START)</sub>   | $C_{V5} \le 2.9 \ \mu\text{F}, \ \text{load} = 25 \ \Omega \ \pm 5\% \ (200 \ \text{mA})$ | _    | 0.24 | 1    | ms   |

| 3V3 LINEAR REGULATOR             |                          |                                                                                           |      |      |      |      |

| 3V3 Accuracy and Load Regulation | V <sub>3V3</sub>         | 10 mA $\leq$ I <sub>3V3</sub> $\leq$ 300 mA, V <sub>VREG</sub> = 5.4 V                    | 3.23 | 3.3  | 3.37 | V    |

| 3V3 Output Capacitance Range [2] | C <sub>3V3(OUT)</sub>    |                                                                                           | 1    | _    | 22   | μF   |

| 3V3 OVERCURRENT PROTECTION       |                          |                                                                                           |      |      |      |      |

| 3V3 Current Limit [1]            | I <sub>3V3(LIM)</sub>    | V <sub>3V3</sub> = 3.3 V                                                                  | -345 | -485 | _    | mA   |

| 3V3 Foldback Current [1]         | I <sub>3V3(FB)</sub>     | V <sub>3V3</sub> = 0 V                                                                    | -120 | -165 | -210 | mA   |

| 3V3 STARTUP                      |                          |                                                                                           |      |      |      |      |

| 3V3 Startup Time [2]             | t <sub>3V3(START)</sub>  | $C_{3V3} \le 2.9 \ \mu\text{F, load} = 15 \ \Omega \pm 5\% \ (220 \ \text{mA})$           | _    | 0.24 | 1    | ms   |

<sup>[1]</sup> Negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>[2]</sup> Ensured by design and characterization, not production tested.

# Adjustable Frequency Buck or Buck-Boost Pre-Regulator with 2 LDOs, Window Watchdog Timer, and NPOR

## ELECTRICAL CHARACTERISTICS – CONTROL INPUTS [1]: Valid at 3 V $\leq$ V<sub>IN</sub> $\leq$ 36 V in buck-boost mode and V<sub>IN</sub> having first reached V<sub>IN(START)</sub>, –40°C $\leq$ T<sub>J</sub> $\leq$ 150°C, unless otherwise specified.

| Characteristic                                          | Symbol                     | Test Conditions                                                                                        | Min. | Тур. | Max. | Unit |

|---------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------|------|------|------|------|

| IGNITION-ENABLE (ENBAT) INF                             | PUT                        |                                                                                                        |      |      |      |      |

| ENBAT Thresholds                                        | V <sub>ENBAT(H)</sub>      | V <sub>ENBAT</sub> rising                                                                              | 2.8  | 3.2  | 3.5  | V    |

| ENDAT THESHOIDS                                         | V <sub>ENBAT(L)</sub>      | V <sub>ENBAT</sub> falling                                                                             | 2.1  | 2.5  | 2.8  | V    |

| ENBAT Hysteresis                                        | V <sub>ENBAT(HYS)</sub>    | $V_{ENBAT(H)} - V_{ENBAT(L)}$                                                                          | _    | 700  | _    | mV   |

| ENBAT Bias Current [1]                                  |                            | T <sub>J</sub> = 25°C <sup>[2]</sup> , V <sub>ENBAT</sub> = 3.51 V                                     | _    | 28   | 45   | μA   |

| ENDAT bias currenting                                   | I <sub>IB(ENBAT)</sub>     | T <sub>J</sub> = 150°C, V <sub>ENBAT</sub> = 3.51 V                                                    | _    | 35   | 60   | μA   |

| ENBAT Resistance                                        | R <sub>ENBAT</sub>         |                                                                                                        | _    | 650  | _    | kΩ   |

| ENBAT DEGLITCH                                          |                            |                                                                                                        |      |      |      |      |

| Enable Filter/Deglitch Time                             | t <sub>d(ENBAT,FILT)</sub> |                                                                                                        | 10   | 15   | 20   | μs   |

| ENBAT SHUTDOWN DELAY                                    |                            |                                                                                                        |      |      |      |      |

| LDO Shutdown Delay                                      | t <sub>d(off)LDO</sub>     | Measure t <sub>d(off)LDO</sub> from the falling edge of ENBAT to the time when all LDOs begin to decay | 15   | 50   | 100  | μs   |

| FSET/SYNC INPUT                                         | •                          |                                                                                                        |      |      |      |      |

| FSET/SYNC Pin Voltage                                   | V <sub>FSET/SYNC</sub>     | No external SYNC signal                                                                                | -    | 800  | _    | mV   |

| FSET/SYNC Open Circuit<br>(Undercurrent) Detection Time | t <sub>FSET/SYNC(UC)</sub> | PWM switching frequency becomes 900 kHz upon detection                                                 | _    | 3    | _    | μs   |

| FSET/SYNC Short-Circuit<br>(Overcurrent) Detection Time | t <sub>FSET/SYNC(OC)</sub> | PWM switching frequency becomes 900 kHz disabled upon detection                                        | _    | 3    | _    | μs   |

| Sync. High Threshold                                    | V <sub>SYNC(H)</sub>       | V <sub>SYNC</sub> rising                                                                               | _    | _    | 2    | V    |

| Sync. Low Threshold                                     | V <sub>SYNC(L)</sub>       | V <sub>SYNC</sub> falling                                                                              | 0.5  | _    | _    | V    |

| Sync. Input Duty Cycle                                  | D <sub>SYNC</sub>          |                                                                                                        | _    | _    | 80   | %    |

| Sync. Input Pulse Width                                 | t <sub>PW(SYNC)</sub>      |                                                                                                        | 200  | _    | _    | ns   |

| Sync. Input Transition Times [2]                        | t <sub>T(SYNC)</sub>       |                                                                                                        | _    | 10   | 15   | ns   |

<sup>[1]</sup> Negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>[2]</sup> Ensured by design and characterization, not production tested.

# Adjustable Frequency Buck or Buck-Boost Pre-Regulator with 2 LDOs, Window Watchdog Timer, and NPOR

## ELECTRICAL CHARACTERISTICS – DIAGNOSTIC OUTPUTS $^{[1]}$ : Valid at 3 V $\leq$ V $_{IN}$ $\leq$ 36 V in buck-boost mode and V $_{IN}$ having first reached V $_{IN(START)}$ , –40°C $\leq$ T $_{J}$ $\leq$ 150°C, unless otherwise specified.

| Characteristic                          | Symbol                    | Test Conditions                                                                      | Min. | Тур. | Max. | Unit |

|-----------------------------------------|---------------------------|--------------------------------------------------------------------------------------|------|------|------|------|

| NPOR UNDERVOLTAGE PROTECT               | ION THRESH                | OLDS                                                                                 |      |      |      |      |

| 2)/2 Undervoltege Threeholds            | V <sub>3V3(UV,H)</sub>    | V <sub>3V3</sub> rising                                                              | _    | 3.1  | _    | V    |

| 3V3 Undervoltage Thresholds             | V <sub>3V3(UV,L)</sub>    | V <sub>3V3</sub> falling                                                             | 2.97 | 3.07 | 3.17 | V    |

| 3V3 Undervoltage Hysteresis             | V <sub>3V3(UV,HYS)</sub>  | $V_{3V3(UV,H)} - V_{3V3(UV,L)}$                                                      | _    | 30   | _    | mV   |

| NPOR TURN-ON AND TURN-OFF D             | ELAYS                     |                                                                                      |      |      |      |      |

| NPOR Turn-On Delay                      | t <sub>d(on)NPOR</sub>    |                                                                                      | 18   | 22.5 | 27   | ms   |

| NPOR Turn-Off Propagation Delay         | t <sub>d(off)NPOR</sub>   | ENBAT low to NPOR low, measured after ENBAT deglitch time t <sub>d(ENBAT,FILT)</sub> | _    | _    | 3    | μs   |

| NPOR OUTPUT VOLTAGES                    |                           |                                                                                      | ·    |      |      | •    |

| NDOD Costruct Lave Valtage              |                           | ENBAT high, V <sub>IN</sub> ≥ 2.5 V, I <sub>NPOR</sub> = 4 mA                        | _    | 150  | 400  | mV   |

| NPOR Output Low Voltage                 | V <sub>NPOR(L)</sub>      | ENBAT high, V <sub>IN</sub> = 1.5 V, I <sub>NPOR</sub> = 2 mA                        | _    | -    | 800  | mV   |

| NPOR Leakage Current [1]                | I <sub>NPOR(LEAK)</sub>   | V <sub>NPOR</sub> = 3.3 V                                                            | _    | _    | 2    | μΑ   |

| NPOR UNDERVOLTAGE FILTERING             | DEGLITCH                  |                                                                                      |      |      |      |      |

| NPOR Undervoltage Filter/Deglitch Times | t <sub>d(NPOR,FILT)</sub> | Applies to undervoltage of the 3V3 voltage                                           | 10   | 15   | 20   | μs   |

<sup>[1]</sup> Negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

# Adjustable Frequency Buck or Buck-Boost Pre-Regulator with 2 LDOs, Window Watchdog Timer, and NPOR

## ELECTRICAL CHARACTERISTICS – DIAGNOSTIC OUTPUTS (continued) [1]: Valid at 3 V $\leq$ V<sub>IN</sub> $\leq$ 36 V in buck-boost mode and V<sub>IN</sub> having first reached V<sub>IN(START)</sub>, –40°C $\leq$ T<sub>J</sub> $\leq$ 150°C, unless otherwise specified.

| Characteristic                             | Symbol                    | Test Conditions                        | Min. | Тур. | Max. | Unit |

|--------------------------------------------|---------------------------|----------------------------------------|------|------|------|------|

| VREG, VCP, AND BG THRESHOL                 | _DS                       |                                        | ·    | `    | `    |      |

| VREG Overvoltage Threshold                 | V <sub>VREG(OV,H)</sub>   | V <sub>VREG</sub> rising, PWM disabled | 6.8  | 6.93 | 7.18 | V    |

| VREG Overvoltage Hysteresis                | V <sub>VREG(OV,HYS)</sub> |                                        | _    | 100  | _    | mV   |

| VDFC Undervoltere Threeholds               | V <sub>VREG(UV,H)</sub>   | V <sub>VREG</sub> rising               | 4.16 | 4.41 | 4.64 | V    |

| VREG Undervoltage Thresholds               | V <sub>VREG(UV,L)</sub>   | V <sub>VREG</sub> falling              | _    | 4.3  | _    | V    |

| VREG Undervoltage Hysteresis               | V <sub>VREG(UV,HYS)</sub> | $V_{VREG(UV,H)} - V_{VREG(UV,L)}$      | _    | 100  | _    | mV   |

| VCP Overvoltage Threshold                  | V <sub>VCP(OV,H)</sub>    | V <sub>VCP</sub> rising, PWM disabled  | 11   | 12.5 | 14   | V    |

| VCD I Indominitorio Throuboldo             | V <sub>VCP(UV,H)</sub>    | V <sub>VCP</sub> rising, PWM enabled   | 3    | 3.2  | 3.4  | V    |

| VCP Undervoltage Thresholds                | V <sub>VCP(UV,L)</sub>    | V <sub>VCP</sub> falling, PWM disabled | _    | 2.7  | _    | V    |

| VCP Undervoltage Hysteresis                | V <sub>VCP(UV,HYS)</sub>  | $V_{VCP(UV,H)} - V_{VCP(UV,L)}$        | _    | 500  | _    | mV   |

| BG1 and BG2 Undervoltage<br>Thresholds [2] | V <sub>BGx(UV)</sub>      | BG1 or BG2 rising                      | 1    | 1.05 | 1.1  | V    |

| UNDERVOLTAGE AND OVERVO                    | LTAGE FILTERI             | NG/DEGLITCH                            |      |      |      |      |

| Undervoltage Filter/Deglitch Time          | t <sub>d(UV,FILT)</sub>   |                                        | 10   | 15   | 20   | μs   |

| Overvoltage Response Time [2]              | t <sub>d(OV,FILT)</sub>   |                                        | _    | 1    | _    | μs   |

<sup>[1]</sup> Negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>[2]</sup> Ensured by design and characterization, not production tested.

# Adjustable Frequency Buck or Buck-Boost Pre-Regulator with 2 LDOs, Window Watchdog Timer, and NPOR

## ELECTRICAL CHARACTERISTICS – WINDOW WATCHDOG TIMER (WWDT) [1]: Valid at 3 V $\leq$ V<sub>IN</sub> $\leq$ 36 V in buck-boost mode and V<sub>IN</sub> having first reached V<sub>IN(START)</sub>, –40°C $\leq$ T<sub>J</sub> $\leq$ 150°C, unless otherwise specified.

| Characteristic                            | Symbol                     | Test Conditions                                                             | Min. | Тур. | Max. | Unit |

|-------------------------------------------|----------------------------|-----------------------------------------------------------------------------|------|------|------|------|

| WD ENABLE INPUT (WD <sub>ENn</sub> )      |                            |                                                                             |      |      |      |      |

| WD <sub>ENn</sub> Voltage Thresholds      | V <sub>WDENn(L)</sub>      | V <sub>WDENn</sub> falling, WWDT enabled                                    | 0.8  | _    | _    | V    |

|                                           | V <sub>WDENn(H)</sub>      | V <sub>WDENn</sub> rising, WWDT disabled                                    | _    | _    | 2    | V    |

| WD <sub>ENn</sub> Input Resistance        | R <sub>WDENn</sub>         |                                                                             | _    | 60   | -    | kΩ   |

| WD <sub>IN</sub> VOLTAGE THRESHOLDS       | AND CURRENT                |                                                                             |      |      |      |      |

| WD <sub>IN</sub> Input Voltage Thresholds | V <sub>WDIN(L)</sub>       | V <sub>WDIN</sub> falling, WD <sub>ADJ</sub> pulled low by R <sub>ADJ</sub> | 0.8  | _    | _    | V    |

|                                           | V <sub>WDIN(H)</sub>       | V <sub>WDIN</sub> rising, WD <sub>ADJ</sub> charging                        | _    | _    | 2    | V    |

| WD <sub>IN</sub> Input Current [1]        | I <sub>WDIN</sub>          | V <sub>WDIN</sub> = 5 V                                                     | -10  | ±1   | 10   | μA   |

| WD <sub>IN</sub> TIMING SPECIFICATIONS    | 3                          |                                                                             |      |      |      |      |

| WD <sub>IN</sub> Frequency                | f <sub>WDIN</sub>          |                                                                             | _    | _    | 750  | Hz   |

| WD <sub>IN</sub> Duty Cycle               | D <sub>WDIN</sub>          |                                                                             | 20   | 50   | 80   | %    |

| Watchdog Activation Delay                 | t <sub>WD(START)</sub>     |                                                                             | 24   | 30   | 36   | ms   |

| WD PROGRAMMING                            |                            |                                                                             |      |      |      |      |

| WD Timeout FAST Range [2]                 | t <sub>WDTO(FAST)</sub>    |                                                                             | 0.5  | _    | 12.5 | ms   |

| WD Timeout SLOW Range [2]                 | t <sub>WDTO(SLOW)</sub>    |                                                                             | 4    | _    | 100  | ms   |

| WD Timeout, FAST Clock                    | twdto(fastclk)             | R <sub>ADJ</sub> = 13 kΩ                                                    | 0.4  | 0.5  | 0.6  | ms   |

|                                           |                            | R <sub>ADJ</sub> = 324 kΩ                                                   | 10   | 12.5 | 15   | ms   |

| WD Timeout, SLOW Clock                    | t <sub>WDTO(SLOWCLK)</sub> | R <sub>ADJ</sub> = 13 kΩ                                                    | 3.2  | 4    | 4.8  | ms   |

|                                           |                            | R <sub>ADJ</sub> = 324 kΩ                                                   | 80   | 100  | 120  | ms   |

| WD ONE-SHOT TIME                          |                            |                                                                             |      |      |      |      |

| WD Pulse Time After WD Fault              | t <sub>WD(FAULT)</sub>     |                                                                             | 1.6  | 2    | 2.4  | ms   |

<sup>[1]</sup> Negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>[2]</sup> Ensured by design and characterization, not production tested.

Table 1: Startup and Shutdown Logic (signal names consistent with Functional Block Diagram)

|              |                 |         |                  | _                       |         | -    |       |

|--------------|-----------------|---------|------------------|-------------------------|---------|------|-------|

|              | RG81401<br>MODE |         | Supply<br>(0=OFF | ARG81401 Status Signals |         |      |       |

|              | MODE            | LDOs ON | VREG ON          | 3V3_UV                  | VREG UV | MPOR | ENBAT |

| ı            | RESET           | 0       | 0                | Χ                       | X       | 1    | Х     |

|              | OFF             | 0       | 0                | 1                       | 1       | 0    | 0     |

|              | TARTUP          | 0       | 1                | 1                       | 1       | 0    | 1     |

|              | <b>1</b>        | 0       | 1                | 1                       | 0       | 0    | 1     |

| $I_{\dashv}$ | $\downarrow$    | 1       | 1                | 1                       | 0       | 0    | 1     |

| TIME         | RUN             | 1       | 1                | 0                       | 0       | 0    | 1     |

|              | µs DELAY        | 1       | 1                | 0                       | 0       | 0    | 0     |

|              | UTDOWN          | 0       | 1                | 0                       | 0       | 0    | 0     |

|              | <b>↓</b>        | 0       | 1                | 1                       | 0       | 0    | 0     |

|              | <b>↓</b>        | 0       | 0                | 1                       | 0       | 0    | 0     |

| ▼            | OFF             | 0       | 0                | 1                       | 1       | 0    | 0     |

X = DON'T CARE

$\label{eq:mpor} \begin{aligned} \textbf{MPOR} = BG1\_UV \text{ or } BG2\_UV \text{ or } VIN\_UV \text{ or } TSD \text{ or } VCP\_UV \text{ or } VCP\_OV \text{ or } D1_{MISSING} \\ & (latched) + I_{LIM(LX)} \text{ (latched)} \end{aligned}$

# Adjustable Frequency Buck or Buck-Boost Pre-Regulator with 2 LDOs, Window Watchdog Timer, and NPOR

**Table 2: Summary of Fault Mode Operation**

| FAULT TYPE and CONDITION                                                                     | ARG81401 RESPONSE TO FAULT                                                                                                                          | NPOR                                            | LATCHED FAULT? | RESET METHOD or CORRECTION                                           |

|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|----------------|----------------------------------------------------------------------|

| 3V3 undervoltage                                                                             | Closed loop control will try to raise the voltage but may be constrained by the foldback current limit                                              | Low                                             | NO             | Decrease the load                                                    |

| 3V3 overcurrent                                                                              | Foldback current limit will reduce the output voltage                                                                                               | Transitions low if 3V3 < V <sub>3V3(UV,L)</sub> | NO             | Decrease the load                                                    |

| V5 undervoltage                                                                              | Closed loop control will try to raise the voltage but may be constrained by the foldback current limit                                              | Not affected                                    | NO             | Decrease the load                                                    |

| V5 overcurrent                                                                               | Foldback current limit will reduce the output voltage                                                                                               | Not affected                                    | NO             | Decrease the load                                                    |

| VREG pin open circuit                                                                        | VLDO pin will take over regulation, power dissipation in IC will increase                                                                           | Not affected                                    | NO             | Connect the VREG pin                                                 |

| VREG shorted to ground,<br>$V_{VREG} < 2.4 \text{ V}$ ,<br>$V_{COMP} \neq E_{AVO(MAX)}$      | Continue to PWM but turn off LX when the high-<br>side MOSFET current exceeds I <sub>LIM</sub>                                                      | Depends on 3V3                                  | NO             | Remove the short circuit                                             |

| VREG overcurrent,<br>$V_{VREG} < 2.4 \text{ V},$<br>$V_{COMP} = E_{AVO(MAX)}$                | Enters hiccup mode after 15 OCP faults                                                                                                              | Depends on 3V3                                  | NO             | Decrease the load                                                    |

| VREG overcurrent,<br>V <sub>VREG</sub> > 2.4 V,<br>V <sub>COMP</sub> = E <sub>AVO(MAX)</sub> | Enters hiccup mode after 60 OCP faults                                                                                                              | Depends on 3V3                                  | NO             | Decrease the load                                                    |

| VREG asynchronous diode (D1) missing                                                         | Results in an MPOR after 1 detection, so all regulators are off                                                                                     | Low                                             | YES            | Place D1 then cycle ENBAT or VIN                                     |

| Asynchronous diode (D1) short circuited or LX shorted to ground                              | Results in an MPOR after the high-side MOSFET current exceeds I <sub>LIM,LX</sub> , so all regulators are off                                       | Low                                             | YES            | Remove the short then cycle ENBAT or VIN                             |

| FSET/SYNC pin open circuit                                                                   | Oscillator frequency becomes default frequency 900 kHz                                                                                              | Not affected                                    | NO             | Connect the FSET/SYNC pin                                            |

| FSET/SYNC pin shorted to ground                                                              | Oscillator frequency becomes default frequency 900 kHz                                                                                              | Not affected                                    | NO             | Remove the short circuit                                             |

| Charge pump (VCP) overvoltage                                                                | Results in an MPOR, so all regulators are shut off                                                                                                  | Depends on 3V3                                  | NO             | Check VCP/CP1/CP2 pins<br>and components, then<br>cycle ENBAT or VIN |

| Charge pump (VCP) undervoltage                                                               | Results in an MPOR, so all regulators are shut off                                                                                                  | Depends on 3V3                                  | NO             | Check VCP/CP1/CP2 pins and components                                |

| VCP pin open circuit                                                                         | Results in VCP_UV and an MPOR, so all regulators are shut off                                                                                       | Depends on 3V3                                  | NO             | Connect the VCP pin                                                  |

| VCP pin shorted to ground                                                                    | Results in high current from the charge pump and (intentional) fusing of an internal trace. Also results in an MPOR, so all regulators are shut off | Depends on 3V3                                  | NO             | Remove the short circuit and replace the ARG81401                    |

| COMP shorted high                                                                            | VREG <sub>OV,H</sub> will trip, so all regulators are shut off                                                                                      | Depends on 3V3                                  | YES            | Remove the high level from the COMP pin then cycle ENBAT or VIN      |

| CP1 or CP2 pin open circuit                                                                  | Results in VCP_UV and an MPOR, so all regulators are shut off                                                                                       | Depends on 3V3                                  | NO             | Connect the CP1 or CP2 pins                                          |

| CP1 pin shorted to ground                                                                    | Results in VCP_UV and an MPOR, so all regulators are shut off                                                                                       | Depends on 3V3                                  | NO             | Remove the short circuit                                             |

Continued on next page...

**Table 2: Summary of Fault Mode Operation (continued)**

| FAULT TYPE and CONDITION                                | ARG81401 RESPONSE TO FAULT                                                                                                                               | NPOR           | LATCHED FAULT? | RESET METHOD or CORRECTION                        |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|---------------------------------------------------|

| CP2 pin shorted to ground                               | Results in high current from the charge pump and (intentional) fusing of an internal trace. Also results in an MPOR, so all regulators are shut off.     | Depends on 3V3 | NO             | Remove the short circuit and replace the ARG81401 |

| BG1 or BG2 undervoltage                                 | Results in an MPOR, so all regulators are shut off                                                                                                       | Depends on 3V3 | NO             | Raise VIN or wait for BGs to power up             |

| BG1 or BG2 overvoltage                                  | If BG1 is too high, 3V3 will appear to be overvoltage, because BG2 is good. If BG2 is too high, 3V3 will appear to be undervoltage, because BG1 is good. | Low            | NO             | Replace the ARG81401                              |

| VIN undervoltage                                        | Results in an MPOR, so all regulators are shut off                                                                                                       | Depends on 3V3 | NO             | Raise VIN                                         |

| Thermal shutdown                                        | Results in an MPOR, so all regulators are shut off                                                                                                       | Depends on 3V3 | NO             | Let the ARG81401 cool                             |

| WD <sub>ADJ</sub> pin shorted to ground or open circuit | A WD <sub>ADJ</sub> fault only affects the NPOR output. The remainder of the ARG81401 operates normally.                                                 | Low            | NO             | Remove the short circuit or connect the pin       |

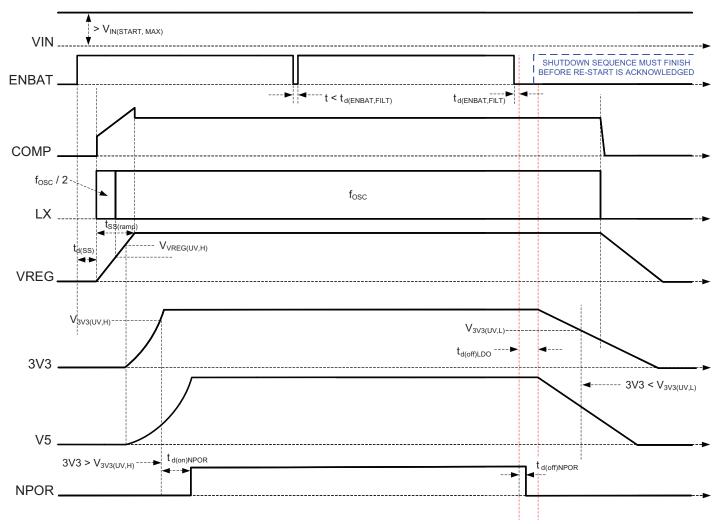

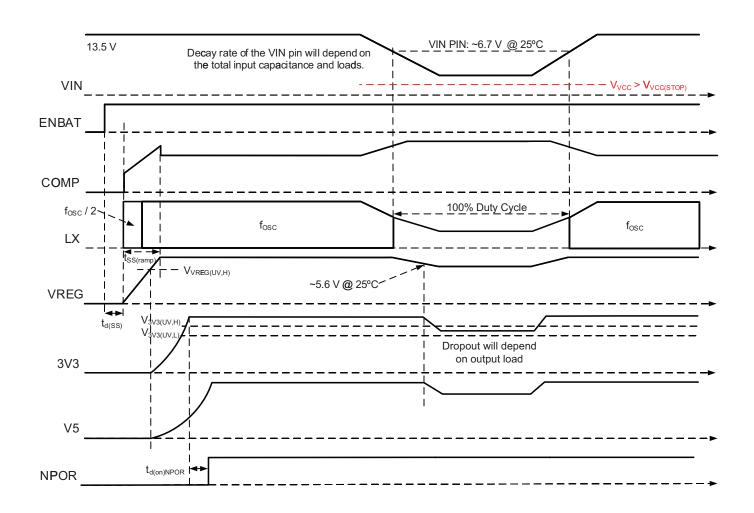

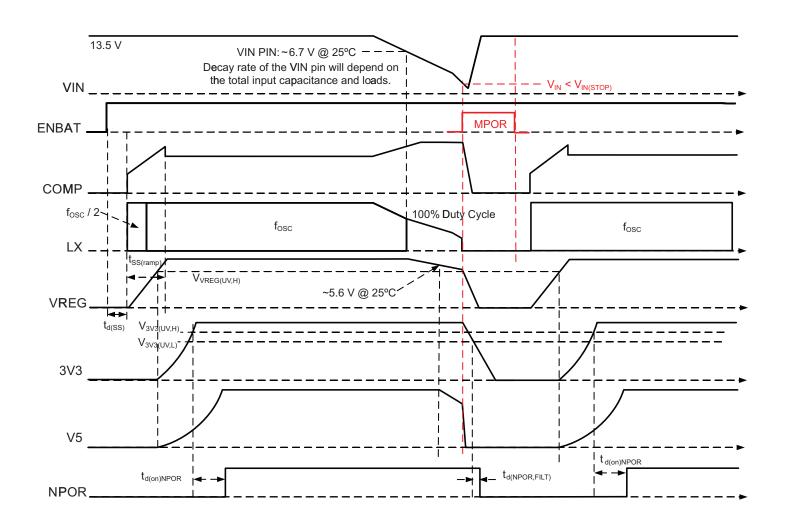

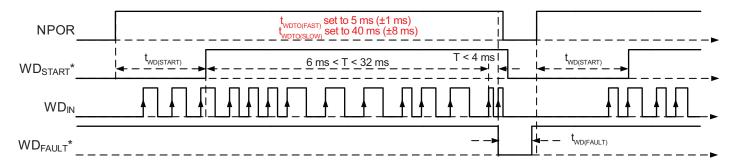

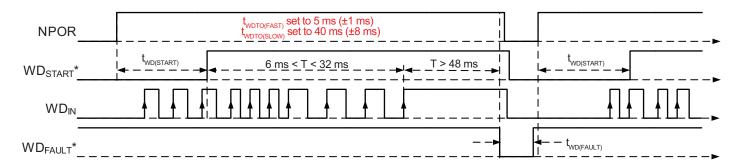

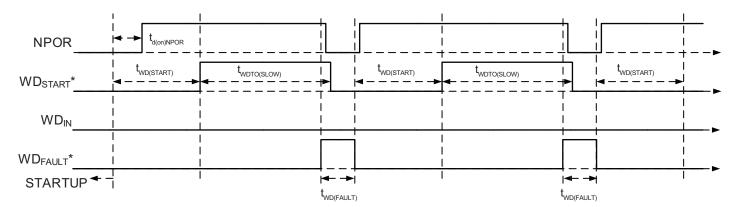

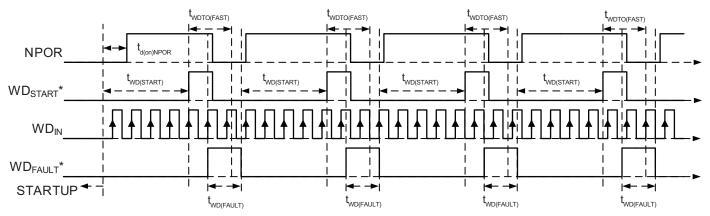

## TIMING DIAGRAMS (not to scale)

Figure 1: Startup and Shutdown Sequence

Figure 2: Input Undervoltage Timing, when  $VIN > V_{IN(STOP)}$

Figure 3: Input Undervoltage Timing, when  $VIN < V_{IN(STOP)}$

Figure 4: VREG Short Circuit to Ground Hiccup Operation

\* Signal is internal to ARG81401

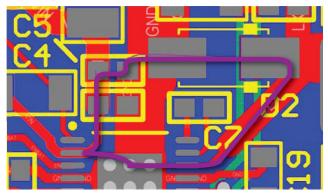

#### **DESIGN AND COMPONENT SELECTION**

#### Setting Up the Pre-Regulator

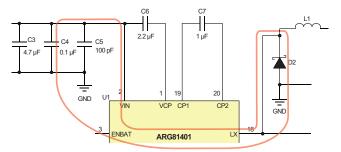

This section describes component selection for the ARG81401 pre-regulator, including charge-pump circuit, inductor, diodes, boost MOSFET, and input and output capactors. This section also covers loop compensation.

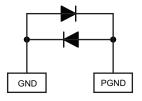

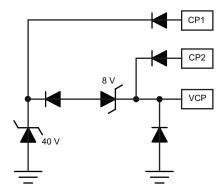

#### **Charge Pump Capacitors**

The charge pump requires two capacitors: a 2.2  $\mu$ F capacitor connected from pin VCP to pin VIN, and a 1  $\mu$ F capacitor connected between pins CP1 and CP2. These capacitors should be high quality ceramic capacitors, such as X7R, with a voltage rating of at least 50 V.

#### PWM Switching Frequency

When the PWM switching frequency is chosen, the designer should be aware of the minimum controllable on-time,  $t_{\rm ON(MIN)}$ , of the ARG81401. If the system's required on-time is less than the ARG81401's minimum controllable on-time, then switch-node jitter will occur and the output voltage will have increased ripple or oscillations.

The PWM switching frequency should be calculated using equation 1, where  $t_{ON(BUCK,MIN)}$  is the minimum controllable on-time of the ARG81401 (160 ns typical), and  $V_{IN(MAX)}$  is the maximum required operational input voltage (not the peak surge voltage).

$$f_{\rm osc} < \frac{6.6 \text{ V}}{t_{\rm ON(BUCK,MIN)} \times V_{\rm IN(MAX)}} \tag{1}$$

If the ARG81401's synchronization function is used, then the base oscillator frequency should be chosen such that jitter will not result at the maximum synchronized switching frequency according to equation 1.

R<sub>FSET</sub> can be estimated using equation 2 below.

$$R_{\text{FSET}} = \frac{1}{0.0455 \times f_{\text{OSC}}} - 1.98 \,(\text{k}\Omega)$$

(2)

where f<sub>OSC</sub> is in MHz.

#### Pre-Regulator Output Inductor (L1)

For peak current mode control, it is well known that the system will become unstable when the duty cycle is above 50% without adequate slope compensation ( $S_E$ ). However, the slope compensation in the ARG81401 is a fixed value based on the oscillator

frequency ( $f_{OSC}$ ). Therefore, it is important to calculate an inductor value so the falling slope of the inductor current ( $S_F$ ) will work well with the ARG81401's slope compensation.

Equation 3 can be used to calculate a range of values for the output inductor for buck or buck-boost.

$$\frac{(VREG + V_{_{\rm F}})}{S_{_{\rm E}}} \le L1 \le \frac{2 \times (VREG + V_{_{\rm F}})}{S_{_{\rm E}}}$$

(3)

where  $V_F$  is the asynchronous diode forward voltage,  $f_{\rm OSC}$  is the programmed oscillator frequency in kHz, and  $S_E$  slope compensation can be calculated from equation 4 and is in amperes per microsecond (A/ $\mu$ s). The resultant inductor value will be in microhenries ( $\mu$ H).

$$S_{\rm E} = 0.0024 \times f_{\rm OSC} \tag{4}$$

If equation 3 yields an inductor value that is not a standard value, then the next closest available value should be used. The final inductor value should allow for 10%-20% of initial tolerance and 20%-30% of inductor saturation.

The inductor should not saturate given the peak operating current during overload. Equation 5 calculates the current. In equation 5,  $V_{\rm IN(MAX)}$  is the maximum continuous input voltage, such as 16 V, and  $V_{\rm F}$  is the asynchronous diodes forward voltage.

$$I_{\text{PEAK}} = 4.6 \text{ A} - \frac{S_{\text{E}} \times (VREG + V_{\text{F}})}{0.9 \times f_{\text{OSC}} \times (V_{\text{IN(MAX)}} + V_{\text{F}})}$$

(5)

After an inductor is chosen, it should be tested during output overload and short-circuit conditions. The inductor current should be monitored using a current probe. A good design should ensure the inductor or the regulator is not damaged when the output is shorted to ground at maximum input voltage and the highest expected ambient temperature.

Inductor ripple current can be calculated using equation 6 for buck mode and equation 7 for buck-boost mode.

$$\Delta I_{\rm L1} = \frac{(V_{\rm IN} - VREG) \times VREG}{f_{\rm SW} \times LI \times V_{\rm IN}} \tag{6}$$

$$\Delta I_{\rm B/B} = \frac{V_{\rm IN} \times D_{\rm BOOST}}{f_{\rm SW} \times L1} \tag{7}$$

# Adjustable Frequency Buck or Buck-Boost Pre-Regulator with 2 LDOs, Window Watchdog Timer, and NPOR

#### **Pre-Regulator Output Capacitors**

The output capacitors filter the output voltage to provide an acceptable level of ripple voltage, and they store energy to help maintain voltage regulation during a load transient. The voltage rating of the output capacitors must support the output voltage with sufficient design margin.

The output voltage ripple ( $\Delta V_{OUT}$ ) is a function of the output capacitors parameters:  $C_O$ ,  $ESR_{CO}$ ,  $ESL_{CO}$ .

$$\Delta V_{\text{OUT}} = \Delta I_{\text{L1}} \times ESR_{\text{CO}} + \frac{V_{\text{IN}} - VREG}{LI} \times ESL_{\text{CO}} + \frac{\Delta I_{\text{L1}}}{8 \times f_{\text{sw}} \times C_{O}}$$

(8)

The type of output capacitors will determine which terms of equation 8 are dominant. For ceramic output capacitors, the  $ESR_{CO}$  and  $ESL_{CO}$  are virtually zero, so the output voltage ripple will be dominated by the third term of equation 8.

$$\Delta VREG = \frac{\Delta I_{L1}}{8 \times f_{SW} \times C_O} \tag{9}$$

To reduce the voltage ripple of a design using ceramic output capacitors, simply increase the total capacitance, reduce the inductor current ripple (i.e. increase the inductor value), or increase the switching frequency.

The transient response of the regulator depends on the number and type of output capacitors. In general, minimizing the ESR of the output capacitance will result in a better transient response. The ESR can be minimized by simply adding more capacitors in parallel or by using higher quality capacitors. At the instant of a fast load transient (di/dt), the output voltage will change by the amount

$$\Delta VREG = \Delta I_{\text{LOAD}} \times ESR_{\text{CO}} + \frac{di}{dt} ESL_{\text{CO}}$$

(10)

After the load transient occurs, the output voltage will deviate from its nominal value for a short time. This time will depend on the system bandwidth, the output inductor value, and output capacitance. Eventually, the error amplifier will bring the output voltage back to its nominal value.

The speed at which the error amplifier will bring the output voltage back to its setpoint will depend mainly on the closed-loop bandwidth of the system. A higher bandwidth usually results in a shorter time to return to the nominal voltage. However, it may be more difficult to obtain acceptable gain and phase margins in a a higher bandwidth system. Selection of the compensation components  $(R_Z, C_Z, C_P)$  are discussed in more detail in the Compensation Components section of this datasheet.

#### **Ceramic Input Capacitors**

The ceramic input capacitor or capacitors must limit the voltage ripple at the VIN pin to a relatively low voltage during maximum load. Equation 11 can be used to calculate the minimum input capacitance,

$$C_{\rm IN} \ge \frac{I_{\rm VREG(MAX)} \times 0.25}{0.9 \times f_{\rm SW} \times 50 \text{ mV}}$$

(11)

where I<sub>VREG(MAX)</sub> is the maximum current from the pre-regulator,

$$I_{\text{VREG(MAX)}} \equiv I_{\text{LINEAR}} + I_{\text{AUX}} + 20 \text{ mA}$$

(12)

where I<sub>LINEAR</sub> is the sum of all internal linear regulators output currents, and I<sub>AUX</sub> is any extra current drawn from the VREG output to power other devices external to the ARG81401.

A good design should consider the dc-bias effect on a ceramic capacitor— as the applied voltage approaches the rated value, the capacitance value decreases. An X7R type capacitor should be the primary choice due to its stability with both dc bias and temperature variation. For all ceramic capacitors, the dc-bias effect is even more pronounced on smaller case sizes, so a good design will use the largest affordable case size.

Also for improved noise performance, it is recommended to add smaller-sized capacitors close to the ARG81401 VIN pin and the D1 anode. Use a  $0.1~\mu F$ , 0603 capacitor.

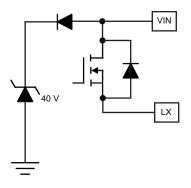

#### **Buck-Boost Asynchronous Diode (D1)**

The highest peak current in the asynchronous diode (D1) occurs during overload and is limited by the ARG81401. Equation 5 can be used to calculate this current.

The highest average current in the asynchronous diode occurs when  $V_{IN}$  is at its maximum,  $D_{BOOST} = 0\%$ , and  $D_{BUCK} = minimum$  (10%),

$$I_{\text{AVG}} = 0.9 \times I_{\text{VREG(MAX)}} \tag{13}$$

where  $I_{VREG(MAX)}$  is calculated using equation 12.

#### **Boost MOSFET (Q1)**

The RMS current in the boost MOSFET (Q1) occurs when  $V_{IN}$  is at its minimum and both the buck and boost operate at their maximum duty cycles (approximately 64% and 58%, respectively),

$$I_{\text{QI(RMS)}} = \sqrt{D_{\text{BOOST}} \times \left[ \left( I_{\text{PEAK}} - \frac{\Delta I_{\text{B/B}}}{2} \right)^2 + \frac{\Delta I_{\text{B/B}}}{12} \right]}$$

(14)

where  $I_{PEAK}$  and  $\Delta I_{B/B}$  are derived using equations 5 and 7, respectively.

#### **Boost Diode (D2)**

In buck mode, this diode will simply conduct the output current. However, in buck-boost mode, the peak currents in this diode may increase significantly. The ARG81401 limits the peak current to the value calculated using equation 5. The average current is simply the output current.

## Pre-Regulator Compensation Components $(R_7, C_7, C_P)$

Although the ARG81401 can operate in buck-boost mode at low input voltages, it can still be considered a buck converter when looking at the control loop. The following equations can be used to calculate the compensation components.

First, the target crossover frequency for the final system must be selected. Although the ARG81401 can switch at over 2 MHz, the crossover will be governed by the required phase margin. Since a type II compensation scheme is used, there are limits to the amount of phase that can be added. Therefore, a crossover frequency,  $f_{\rm C}$ , of around 40 kHz is selected. The total system phase will drop off at higher crossover frequencies. The  $R_{\rm Z}$  selection is based on the gain required at the crossover frequency, and can be calculated by the following simplified equation:

$$R_{\rm Z} = \frac{13.36 \times \pi \times f_{\rm C} \times C_{o}}{g_{\rm m(POWER)} \times g_{\rm m(EA)}}$$

(15)

The series capacitor,  $C_Z$ , along with the resistor,  $R_Z$ , set the location of the compensation zero. This zero should be placed no lower than  $\frac{1}{4}$  of the crossover frequency and should be kept to minimum value. Equation 18 can be used to estimate this capacitor value.

$$C_{\rm z} > \frac{4}{2\pi \times R_{\rm z} \times f_{\rm c}} \tag{16}$$

Determine if the second compensation capacitor  $(C_P)$  is required. It is required if the ESR zero of the output capacitor is located at less than half of the switching frequency or the following relationship is valid:

$$\frac{1}{2\pi \times C_o \times ESR_{co}} < \frac{f_{sw}}{2} \tag{17}$$

If this is the case, then add the second compensation capacitor  $(C_P)$  to set the pole  $f_{P3}$  at the location of the ESR zero. Determine the  $C_P$  value by the equation:

$$C_{\rm p} = \frac{C_{\rm OUT} \times ESR}{R_{\rm z}} \tag{18}$$

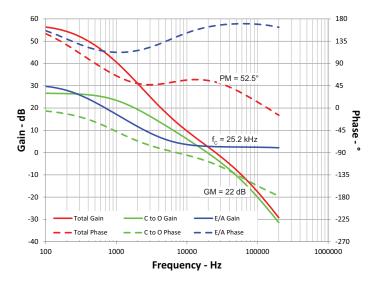

Finally, take a look at the combined bode plot of both the control-to-output and the compensated error amp— see the red curves shown in Figure 5. Careful examination of this plot shows that the magnitude and phase of the entire system are simply the sum of the error amp response (blue) and the control-to-output response (green). As shown in Figure 5, the bandwidth of this system ( $f_C$ ) is 25.2 kHz, the phase margin is 52.5 degrees, and the gain margin is 22 dB. These values are theoretical; actual measured values may be different. Some fine-tuning of the final compensation components may be necessary in the lab.

Figure 5: Bode plot of the complete system (red curve)  $R_Z$  = 6.19 k $\Omega$ ,  $C_Z$  = 4.7 nF,  $C_P$  = 10 pF  $L_O$  = 33  $\mu$ H,  $C_O$  = 4 × 10  $\mu$ F ceramic

#### **Linear Regulators**

The two linear regulators only require a ceramic capacitor to ensure stable operation. The capacitor can be any value between 1  $\mu F$  and 22  $\mu F$ . A 2.2  $\mu F$  or 4.7  $\mu F$  capacitor per regulator is recommended.

# Adjustable Frequency Buck or Buck-Boost Pre-Regulator with 2 LDOs, Window Watchdog Timer, and NPOR

#### Internal Bias (VCC)

The internal bias voltage should be decoupled at the VCC pin using a 1  $\mu$ F, 25 V X7R ceramic capacitor. It is not recommended to use this pin as a source.

#### Signal Pins (NPOR, ENBAT)

The NPOR signal is an open drain output and requires an external pull-up resistor. It is recommended to pull NPOR up to the 3V3 rail, so when the ARG81401 is disabled, NPOR will not be high.

The ENBAT is a high-voltage input pin. It does require a current-limiting resistor when connected to voltages greater than 8 V. There are limitations on this resistor value based on ENBAT sink current, ENBAT enable threshold, and input voltage operating conditions. Minimum ENBAT resistor is 450  $\Omega.$  If ENBAT must ensure ARG81401 is enabled down to the minimum operating voltage, then a resistor less than 3.37  $k\Omega$  is recommended.

#### Watchdog (WD<sub>ENn</sub>, WD<sub>IN</sub>, WD<sub>ADJ</sub>)