# National Semiconductor is now part of Texas Instruments.

Search <a href="http://www.ti.com/">http://www.ti.com/</a> for the latest technical information and details on our current products and services.

# PC16550D Universal Asynchronous Receiver/Transmitter with FIFOs†

## **General Description**

The PC16550D is an improved version of the original 16450 Universal Asynchronous Receiver/Transmitter (UART). Functionally identical to the 16450 on powerup (CHARACTER mode)\* the PC16550D can be put into an alternate mode (FIFO mode) to relieve the CPU of excessive software overhead.

In this mode internal FIFOs are activated allowing 16 bytes (plus 3 bits of error data per byte in the RCVR FIFO) to be stored in both receive and transmit modes. All the logic is on chip to minimize system overhead and maximize system efficiency. Two pin functions have been changed to allow signalling of DMA transfers.

The UART performs serial-to-parallel conversion on data characters received from a peripheral device or a MODEM, and parallel-to-serial conversion on data characters received from the CPU. The CPU can read the complete status of the UART at any time during the functional operation. Status information reported includes the type and condition of the transfer operations being performed by the UART, as well as any error conditions (parity, overrun, framing, or break interrupt).

The UART includes a programmable baud rate generator that is capable of dividing the timing reference clock input by divisors of 1 to (2^{16}-1), and producing a 16  $\times$  clock for driving the internal transmitter logic. Provisions are also included to use this 16  $\times$  clock to drive the receiver logic. The UART has complete MODEM-control capability, and a processor-interrupt system. Interrupts can be programmed to the user's requirements, minimizing the computing required to handle the communications link.

The UART is fabricated using National Semiconductor's advanced M<sup>2</sup>CMOS process.

\*Can also be reset to 16450 Mode under software control.

†Note: This part is patented.

#### **Features**

- Capable of running all existing 16450 software.

- Pin for pin compatible with the existing 16450 except for CSOUT (24) and NC (29). The former CSOUT and NC pins are TXRDY and RXRDY, respectively.

- After reset, all registers are identical to the 16450 register set

- In the FIFO mode transmitter and receiver are each buffered with 16 byte FIFO's to reduce the number of interrrupts presented to the CPU.

- Adds or deletes standard asynchronous communication bits (start, stop, and parity) to or from the serial data.

- Holding and shift registers in the 16450 Mode eliminate the need for precise synchronization between the CPU and serial data.

- Independently controlled transmit, receive, line status, and data set interrupts.

- $\blacksquare$  Programmable baud generator divides any input clock by 1 to (2  $^{16}-$  1) and generates the 16  $\times$  clock.

- Independent receiver clock input.

- MODEM control functions (CTS, RTS, DSR, DTR, RI, and DCD).

- Fully programmable serial-interface characteristics:

- 5-, 6-, 7-, or 8-bit characters

- Even, odd, or no-parity bit generation and detection

- 1-, 11/2-, or 2-stop bit generation

- Baud generation (DC to 1.5M baud).

- False start bit detection.

- Complete status reporting capabilities.

- TRI-STATE® TTL drive for the data and control buses.

- Line break generation and detection.

- Internal diagnostic capabilities:

- Loopback controls for communications link fault isolation

TL/C/8652-1

- Break, parity, overrun, framing error simulation.

- Full prioritized interrupt system controls.

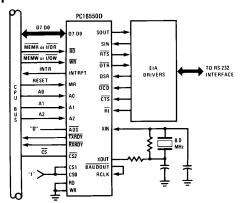

# **Basic Configuration**

TRI-STATE® is a registered trademark of National Semiconductor Corp

# **Table of Contents**

1.0 ABSOLUTE MAXIMUM RATINGS

2.0 DC ELECTRICAL CHARACTERISTICS

3.0 AC ELECTRICAL CHARACTERISTICS

4.0 TIMING WAVEFORMS

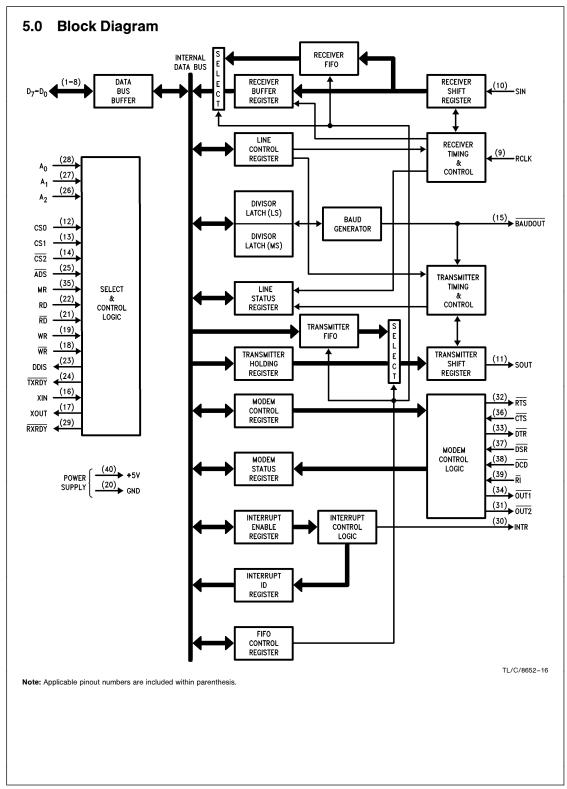

**5.0 BLOCK DIAGRAM**

6.0 PIN DESCRIPTIONS

7.0 CONNECTION DIAGRAMS

8.0 REGISTERS

8.1 Line Control Register

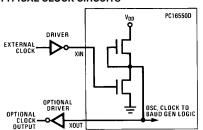

8.2 Typical Clock Circuits

8.0 REGISTERS (Continued)

8.3 Programmable Baud Generator

8.4 Line Status Register

8.5 FIFO Control Register

8.6 Interrupt Identification Register

8.7 Interrupt Enable Register

8.8 Modem Control Register

8.9 Modem Status Register

8.10 Scratchpad Register

8.11 FIFO Interrupt Mode Operation

8.12 FIFO Polled Mode Operation

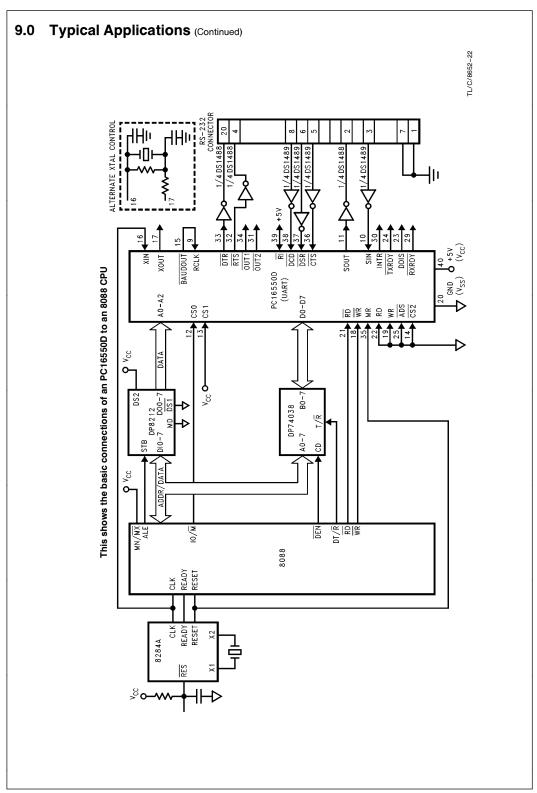

9.0 TYPICAL APPLICATIONS

# 1.0 Absolute Maximum Ratings

$\begin{tabular}{lll} Temperature Under Bias & 0 ^{\circ}C to +70 ^{\circ}C \\ Storage Temperature & -65 ^{\circ}C to +150 ^{\circ}C \\ \end{tabular}$

All Input or Output Voltages

with Respect to  $V_{SS}$  -0.5V to +7.0VPower Dissipation 1W Note: Maximum ratings indicate limits beyond which permanent damage may occur. Continuous operation at these limits is not intended and should be limited to those conditions specified under DC electrical characteristics.

# 2.0 DC Electrical Characteristics

$T_{A}=\,0^{\circ}C$  to  $\,+70^{\circ}C,\,V_{DD}=\,+5V\,\pm10\%,\,V_{SS}=\,0V,$  unless otherwise specified.

| Symbol               | Parameter                       | Conditions                                                                                                                            | Min  | Max             | Units |

|----------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------|-----------------|-------|

| V <sub>ILX</sub>     | Clock Input Low Voltage         |                                                                                                                                       | -0.5 | 0.8             | V     |

| V <sub>IHX</sub>     | Clock Input High Voltage        |                                                                                                                                       | 2.0  | V <sub>DD</sub> | V     |

| V <sub>IL</sub>      | Input Low Voltage               |                                                                                                                                       | -0.5 | 0.8             | V     |

| V <sub>IH</sub>      | Input High Voltage              |                                                                                                                                       | 2.0  | V <sub>DD</sub> | V     |

| V <sub>OL</sub>      | Output Low Voltage              | I <sub>OL</sub> = 1.6 mA on all (Note 1)                                                                                              |      | 0.4             | V     |

| V <sub>OH</sub>      | Output High Voltage             | $I_{OH} = -1.0 \text{ mA (Note 1)}$                                                                                                   | 2.4  |                 | V     |

| I <sub>CC</sub> (AV) | Average Power Supply<br>Current | $V_{DD}=5.5V, T_A=25^{\circ}C$<br>No Loads on output<br>SIN, DSR, DCD,<br>CTS, RI=2.0V<br>All other inputs=0.8V                       |      | 15              | mA    |

| I <sub>IL</sub>      | Input Leakage                   | $V_{DD} = 5.5V, V_{SS} = 0V$                                                                                                          |      | ±10             | μΑ    |

| I <sub>CL</sub>      | Clock Leakage                   | All other pins floating. $V_{IN} = 0V, 5.5V$                                                                                          |      | ±10             | μΑ    |

| l <sub>OZ</sub>      | TRI-STATE Leakage               | V <sub>DD</sub> = 5.5V, V <sub>SS</sub> = 0V<br>V <sub>OUT</sub> = 0V, 5.25V<br>1) Chip deselected<br>2) WRITE mode,<br>chip selected |      | ±20             | μΑ    |

| V <sub>ILMR</sub>    | MR Schmitt V <sub>IL</sub>      |                                                                                                                                       |      | 0.8             | V     |

| V <sub>IHMR</sub>    | MR Schmitt V <sub>IH</sub>      |                                                                                                                                       | 2.0  |                 | V     |

Note 1: Does not apply to XOUT

# **Capacitance** $T_A = 25^{\circ}C$ , $V_{DD} = V_{SS} = 0V$

| Symbol            | Parameter                | Conditions                                                         | Min | Тур | Max | Units |

|-------------------|--------------------------|--------------------------------------------------------------------|-----|-----|-----|-------|

| C <sub>XIN</sub>  | Clock Input Capacitance  |                                                                    |     | 7   | 9   | pF    |

| C <sub>XOUT</sub> | Clock Output Capacitance | f <sub>c</sub> = 1 MHz Unmeasured pins returned to V <sub>SS</sub> |     | 7   | 9   | pF    |

| C <sub>IN</sub>   | Input Capacitance        |                                                                    |     | 5   | 7   | pF    |

| C <sub>OUT</sub>  | Output Capacitance       |                                                                    |     | 6   | 8   | pF    |

| C <sub>I/O</sub>  | Input/Output Capacitance |                                                                    |     | 10  | 12  | pF    |

| Symbol            | Parameter                                                         | Conditions                          | Min  | Max                | Units |

|-------------------|-------------------------------------------------------------------|-------------------------------------|------|--------------------|-------|

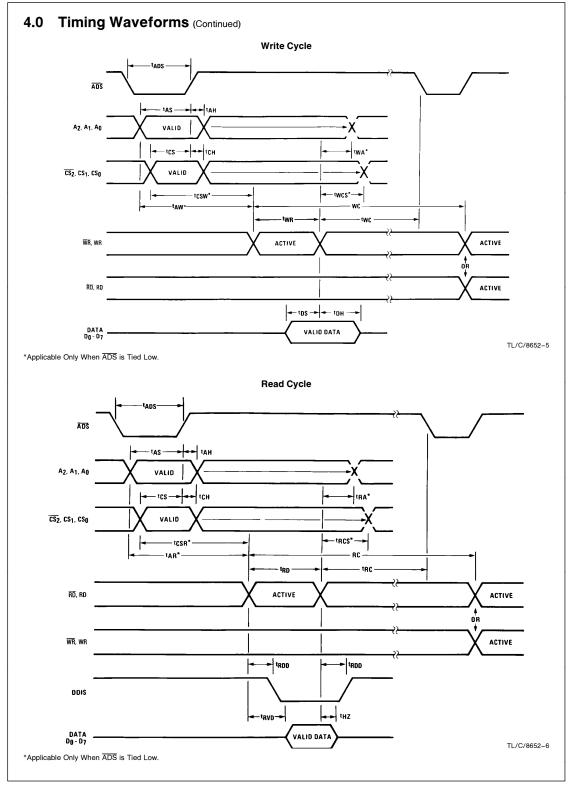

| t <sub>ADS</sub>  | Address Strobe Width                                              |                                     | 60   |                    | ns    |

| t <sub>AH</sub>   | Address Hold Time                                                 |                                     | 0    |                    | ns    |

| t <sub>AR</sub>   | RD, RD Delay from Address                                         | (Note 1)                            | 30   |                    | ns    |

| t <sub>AS</sub>   | Address Setup Time                                                |                                     | 60   |                    | ns    |

| t <sub>AW</sub>   | WR, WR Delay from Address                                         | (Note 1)                            | 30   |                    | ns    |

| t <sub>CH</sub>   | Chip Select Hold Time                                             |                                     | 0    |                    | ns    |

| t <sub>CS</sub>   | Chip Select Setup Time                                            |                                     | 60   |                    | ns    |

| t <sub>CSR</sub>  | RD, RD Delay from Chip Select                                     | (Note 1)                            | 30   |                    | ns    |

| tcsw              | WR, WR Delay from Select                                          | (Note 1)                            | 30   |                    | ns    |

| t <sub>DH</sub>   | Data Hold Time                                                    |                                     | 30   |                    | ns    |

| t <sub>DS</sub>   | Data Setup Time                                                   |                                     | 30   |                    | ns    |

| t <sub>HZ</sub>   | RD, RD to Floating Data Delay                                     | @100 pF loading (Note 3)            | 0    | 100                | ns    |

| t <sub>MR</sub>   | Master Reset Pulse Width                                          |                                     | 5000 |                    | ns    |

| t <sub>RA</sub>   | Address Hold Time from RD, RD                                     | (Note 1)                            | 20   |                    | ns    |

| t <sub>RC</sub>   | Read Cycle Delay                                                  |                                     | 125  |                    | ns    |

| t <sub>RCS</sub>  | Chip Select Hold Time from RD, RD                                 | (Note 1)                            | 20   |                    | ns    |

| t <sub>RD</sub>   | RD, RD Strobe Width                                               | , ,                                 | 125  |                    | ns    |

| t <sub>RDD</sub>  | RD, RD to Driver Enable/Disable                                   | @100 pF loading (Note 3)            |      | 60                 | ns    |

| t <sub>RVD</sub>  | Delay from RD, RD to Data                                         | @100 pF loading                     |      | 60                 | ns    |

| t <sub>WA</sub>   | Address Hold Time from WR, WR                                     | (Note 1)                            | 20   |                    | ns    |

| twc               | Write Cycle Delay                                                 |                                     | 150  |                    | ns    |

| twcs              | Chip Select Hold Time from WR, WR                                 | (Note 1)                            | 20   |                    | ns    |

| t <sub>WR</sub>   | WR, WR Strobe Width                                               |                                     | 100  |                    | ns    |

| t <sub>XH</sub>   | Duration of Clock High Pulse                                      | External Clock (8, Max.)            | 55   |                    | ns    |

| t <sub>XL</sub>   | Duration of Clock Low Pulse                                       | External Clock (8, Max.)            | 55   |                    | ns    |

| RC                | Read Cycle = $t_{AR} + t_{RD} + t_{RC}$                           |                                     | 280  |                    | ns    |

| WC                | Write Cycle = t <sub>AW</sub> + t <sub>WR</sub> + t <sub>WC</sub> |                                     | 280  |                    | ns    |

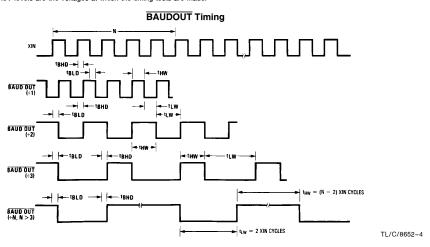

| Baud Gene         |                                                                   |                                     |      |                    |       |

| N                 | Baud Divisor                                                      |                                     | 1    | 2 <sup>16</sup> -1 |       |

| t <sub>BHD</sub>  | Baud Output Positive Edge Delay                                   | 100 pF Load                         |      | 175                | ns    |

| t <sub>BLD</sub>  | Baud Output Negative Edge Delay                                   | 100 pF Load                         |      | 175                | ns    |

| t <sub>HW</sub>   | Baud Output Up Time                                               | f <sub>X</sub> = 8, ÷2, 100 pF Load | 75   |                    | ns    |

| t <sub>LW</sub>   | Baud Output Down Time                                             | f <sub>X</sub> = 8, ÷2, 100 pF Load | 100  |                    | ns    |

| Receiver          |                                                                   |                                     |      |                    |       |

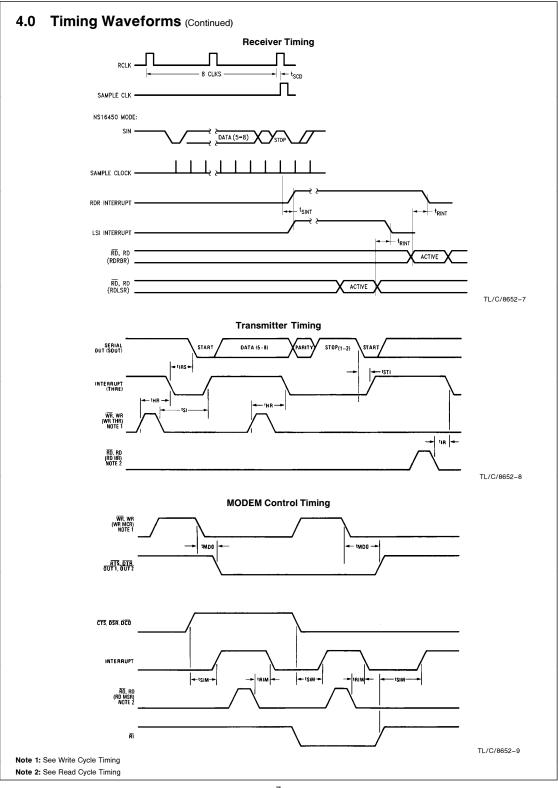

| t <sub>RAI</sub>  | Delay from Active Edge of RD to Reset Interrupt                   |                                     |      | _                  | ns    |

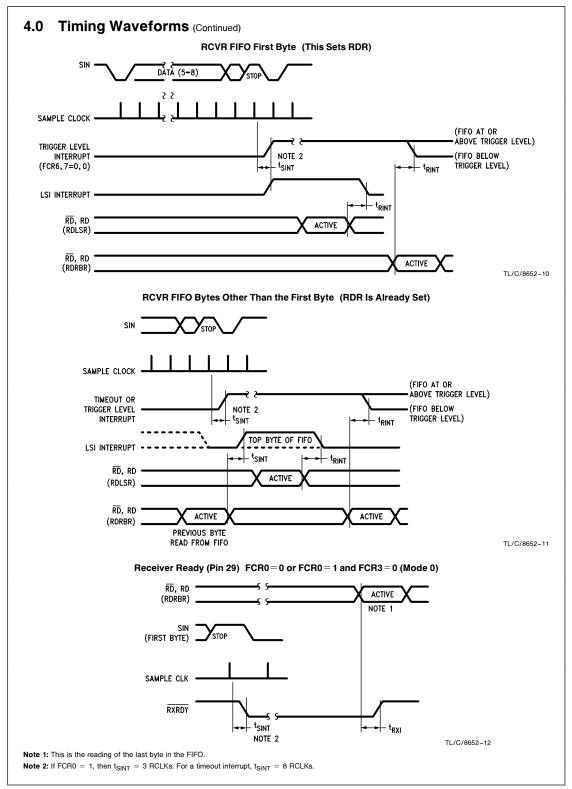

| t <sub>RINT</sub> | Delay from RD, RD<br>(RD RBR/or RD LSR)<br>to Reset Interrupt     | 100 pF Load                         |      | 1000               | ns    |

| t <sub>RXI</sub>  | Delay from RD RBR to RXRDY Inactive                               |                                     |      | 290                | ns    |

| t <sub>SCD</sub>  | Delay from RCLK to Sample Time                                    |                                     |      | 2000               | ns    |

| t <sub>SINT</sub> | Delay from Stop to Set Interrupt                                  | (Note 2)                            |      | 1                  | RCL   |

Note 1: Applicable only when  $\overline{\rm ADS}$  is tied low.

Note 2: In the FIFO mode (FCR0=1) the trigger level interrupts, the receiver data available indication, the active RXRDY indication and the overrun error indication will be delayed 3 RCLKs. Status indicators (PE, FE, BI) will be delayed 3 RCLKs after the first byte has been received. For subsequently received bytes these indicators will be updated immediately after RDRBR goes inactive. Timeout interrupt is delayed 8 RCLKs.

Note 3: Charge and discharge time is determined by  $V_{\mbox{\scriptsize OL}},\,V_{\mbox{\scriptsize OH}}$  and the external loading.

Note 4: These specifications are preliminary.

| Symbol           | Parameter                                            | Conditions  | Min | Max | Units             |

|------------------|------------------------------------------------------|-------------|-----|-----|-------------------|

| Transmitter      | •                                                    |             |     |     |                   |

| t <sub>HR</sub>  | Delay from WR, WR (WR THR) to Reset Interrupt        | 100 pF Load |     | 175 | ns                |

| t <sub>IR</sub>  | Delay from RD, RD (RD IIR) to Reset Interrupt (THRE) | 100 pF Load |     | 250 | ns                |

| t <sub>IRS</sub> | Delay from Initial INTR Reset to Transmit<br>Start   |             | 8   | 24  | BAUDOUT<br>Cycles |

| t <sub>SI</sub>  | Delay from Initial Write to Interrupt                | (Note 1)    | 16  | 24  | BAUDOUT<br>Cycles |

| t <sub>STI</sub> | Delay from Stop to Interrupt (THRE)                  | (Note 1)    | 8   | 8   | BAUDOUT<br>Cycles |

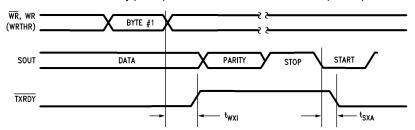

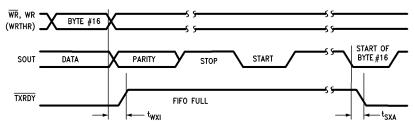

| t <sub>SXA</sub> | Delay from Start to TXRDY active                     | 100 pF Load |     | 8   | BAUDOUT<br>Cycles |

| t <sub>WXI</sub> | Delay from Write to TXRDY inactive                   | 100 pF Load |     | 195 | ns                |

| Modem Cor        | ntrol                                                |             |     |     |                   |

| t <sub>MDO</sub> | Delay from WR, WR (WR MCR) to Output                 | 100 pF Load |     | 200 | ns                |

| t <sub>RIM</sub> | Delay from RD, RD to Reset Interrupt                 | 100 pF Load |     | 250 | ns                |

Note 1: This delay will be lengthened by 1 character time, minus the last stop bit time if the transmitter interrupt delay circuit is active. (See FIFO Interrupt Mode Operation).

100 pF Load

250

Note 2: These specifications are preliminary.

$t_{\text{SIM}}$

# 4.0 Timing Waveforms (All timings are referenced to valid 0 and valid 1)

Delay from MODEM Input to Set Interrupt

Note 1: The 2.4V and 0.4V levels are the voltages that the inputs are driven to during AC testing.

Note 2: The 2.0V and 0.8V levels are the voltages at which the timing tests are made.

# 4.0 Timing Waveforms (Continued)

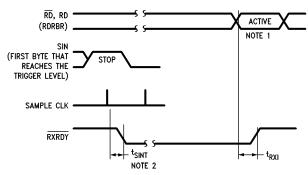

# Receiver Ready (Pin 29) FCR0 = 1 and FCR3 = 1 (Mode 1)

Note 1: This is the reading of the last byte in the FIFO.

Note 2: If FCR0=1,  $t_{SINT}$ =3 RCLKs.

#### Transmitter Ready (Pin 24) FCR0 = 0 or FCR0 = 1 and FCR3 = 0 (Mode 0)

TL/C/8652-14

TL/C/8652-13

### Transmitter Ready (Pin 24) FCR0 = 1 and FCR3 = 1 (Mode 1)

TL/C/8652-15

### 6.0 Pin Descriptions

The following describes the function of all UART pins. Some of these descriptions reference internal circuits.

In the following descriptions, a low represents a logic 0 (0V nominal) and a high represents a logic 1 (+2.4V nominal).

A0, A1, A2, Register Select, Pins 26–28: Address signals connected to these 3 inputs select a UART register for the CPU to read from or write to during data transfer. A table of registers and their addresses is shown below. Note that the state of the Divisor Latch Access Bit (DLAB), which is the most significant bit of the Line Control Register, affects the selection of certain UART registers. The DLAB must be set high by the system software to access the Baud Generator Divisor Latches.

#### Register Addresses

|      |                |                | <del>-</del>   |                                 |

|------|----------------|----------------|----------------|---------------------------------|

| DLAB | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | Register                        |

| 0    | 0              | 0              | 0              | Receiver Buffer (read),         |

|      |                |                |                | Transmitter Holding             |

|      |                |                |                | Register (write)                |

| 0    | 0              | 0              | 1              | Interrupt Enable                |

| Х    | 0              | 1              | 0              | Interrupt Identification (read) |

| X    | 0              | 1              | 0              | FIFO Control (write)            |

| X    | 0              | 1              | 1              | Line Control                    |

| X    | 1              | 0              | 0              | MODEM Control                   |

| Х    | 1              | 0              | 1              | Line Status                     |

| Х    | 1              | 1              | 0              | MODEM Status                    |

| Х    | 1              | 1              | 1              | Scratch                         |

| 1    | 0              | 0              | 0              | Divisor Latch                   |

|      |                |                |                | (least significant byte)        |

| 1    | 0              | 0              | 1              | Divisor Latch                   |

|      |                |                |                | (most significant byte)         |

ADS, Address Strobe, Pin 25: The positive edge of an active Address Strobe (ADS) signal latches the Register Select (A0, A1, A2) and Chip Select (CS0, CS1, CS2) signals.

Note: An active ADS input is required when the Register Select (A0, A1, A2) and Chip Select (CS0, CS1, CS2) signals are not stable for the duration of a read or write operation. If not required, tie the ADS input permanently low.

BAUDOUT, Baud Out, Pin 15: This is the 16 × clock signal from the transmitter section of the UART. The clock rate is equal to the main reference oscillator frequency divided by the specified divisor in the Baud Generator Divisor Latches. The BAUDOUT may also be used for the receiver section by tying this output to the RCLK input of the chip.

CS0, CS1,  $\overline{\text{CS2}}$ , Chip Select, Pins 12–14: When CS0 and CS1 are high and  $\overline{\text{CS2}}$  is low, the chip is selected. This enables communication between the UART and the CPU. The positive edge of an active Address Strobe signal latches the decoded chip select signals, completing chip selection. If  $\overline{\text{ADS}}$  is always low, valid chip selects should stabilize according to the  $t_{\text{CSW}}$  parameter.

CTS, Clear to Send, Pin 36: When low, this indicates that the MODEM or data set is ready to exchange data. The CTS signal is a MODEM status input whose conditions can be tested by the CPU reading bit 4 (CTS) of the MODEM Status Register. Bit 4 is the complement of the CTS signal. Bit 0 (DCTS) of the MODEM Status Register indicates whether the CTS input has changed state since the previous reading of the MODEM Status Register. CTS has no effect on the

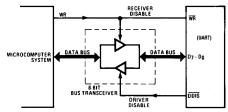

Note: Whenever the CTS bit of the MODEM Status Register changes state, an interrupt is generated if the MODEM Status Interrupt is enabled.  $\mathbf{D_7}$ - $\mathbf{D_0}$ , Data Bus, Pins 1–8: This bus comprises eight TRI-STATE input/output lines. The bus provides bidirectional communications between the UART and the CPU. Data, control words, and status information are transferred via the  $D_7$ - $D_0$  Data Bus.

DCD, Data Carrier Detect, Pin 38: When low, indicates that the data carrier has been detected by the MODEM or data set. The DCD signal is a MODEM status input whose condition can be tested by the CPU reading bit 7 (DCD) of the MODEM Status Register. Bit 7 is the complement of the DCD signal. Bit 3 (DDCD) of the MODEM Status Register indicates whether the DCD input has changed state since the previous reading of the MODEM Status Register. DCD has no effect on the receiver.

Note: Whenever the DCD bit of the MODEM Status Register changes state, an interrupt is generated if the MODEM Status Interrupt is enabled.

**DDIS,** Driver Disable, Pin 23: This goes low whenever the CPU is reading data from the UART. It can disable or control the direction of a data bus transceiver between the CPU and the UART.

DSR, Data Set Ready, Pin 37: When low, this indicates that the MODEM or data set is ready to establish the communications link with the UART. The DSR signal is a MODEM status input whose condition can be tested by the CPU reading bit 5 (DSR) of the MODEM Status Register. Bit 5 is the complement of the DSR signal. Bit 1 (DDSR) of the MODEM Status Register indicates whether the DSR input has changed state since the previous reading of the MODEM Status Register.

Note: Whenever the DDSR bit of the MODEM Status Register changes state, an interrupt is generated if the MODEM Status Interrupt is enabled.

DTR, Data Terminal Ready, Pin 33: When low, this informs the MODEM or data set that the UART is ready to establish a communications link. The DTR output signal can be set to an active low by programming bit 0 (DTR) of the MODEM Control Register to a high level. A Master Reset operation sets this signal to its inactive (high) state. Loop mode operation holds this signal in its inactive state.

INTR, Interrupt, Pin 30: This pin goes high whenever any one of the following interrupt types has an active high condition and is enabled via the IER: Receiver Error Flag; Received Data Available: timeout (FIFO Mode only); Transmitter Holding Register Empty; and MODEM Status. The INTR signal is reset low upon the appropriate interrupt service or a Master Reset operation.

MR, Master Reset, Pin 35: When this input is high, it clears all the registers (except the Receiver Buffer, Transmitter Holding, and Divisor Latches), and the control logic of the UART. The states of various output signals (SOUT, INTR, OUT 1, OUT 2, RTS, DTR) are affected by an active MR input (Refer to Table I.) This input is buffered with a TTL-compatible Schmitt Trigger with 0.5V typical hysteresis.

OUT 1, Output 1, Pin 34: This user-designated output can be set to an active low by programming bit 2 (OUT 1) of the MODEM Control Register to a high level. A Master Reset operation sets this signal to its inactive (high) state. Loop mode operation holds this signal in its inactive state. In the XMOS parts this will achieve TTL levels.

#### **6.0 Pin Descriptions** (Continued)

OUT 2, Output 2, Pin 31: This user-designated output that can be set to an active low by programming bit 3 (OUT 2) of the MODEM Control Register to a high level. A Master Reset operation sets this signal to its inactive (high) state. Loop mode operation holds this signal in its inactive state. In the XMOS parts this will achieve TTL levels.

**RCLK**, Receiver Clock, Pin 9: This input is the 16  $\times$  baud rate clock for the receiver section of the chip.

RD,  $\overline{RD}$ , Read, Pins 22 and 21: When RD is high or  $\overline{RD}$  is low while the chip is selected, the CPU can read status information or data from the selected UART register.

Note: Only an active RD or RD input is required to transfer data from the UART during a read operation. Therefore, tie either the RD input permanently low or the RD input permanently high, when it is not used.

$\overline{

m RI}$ , Ring Indicator, Pin 39: When low, this indicates that a telephone ringing signal has been received by the MODEM or data set. The  $\overline{

m RI}$  signal is a MODEM status input whose condition can be tested by the CPU reading bit 6 (RI) of the MODEM Status Register. Bit 6 is the complement of the  $\overline{

m RI}$  signal. Bit 2 (TERI) of the MODEM Status Register indicates whether the  $\overline{

m RI}$  input **signal** has changed from a low to a high state since the previous reading of the MODEM Status Register.

Note: Whenever the RI bit of the MODEM Status Register changes from a high to a low state, an interrupt is generated if the MODEM Status Interrupt is enabled.

RTS, Request to Send, Pin 32: When low, this informs the MODEM or data set that the UART is ready to exchange data. The RTS output signal can be set to an active low by programming bit 1 (RTS) of the MODEM Control Register. A Master Reset operation sets this signal to its inactive (high) state. Loop mode operation holds this signal in its inactive state.

**SIN**, Serial Input, Pin 10: Serial data input from the communications link (peripheral device, MODEM, or data set).

**SOUT,** Serial Output, Pin 11: Composite serial data output to the communications link (peripheral, MODEM or data set). The SOUT signal is set to the Marking (logic 1) state upon a Master Reset operation.

TXRDY, RXRDY, Pins 24, 29: Transmitter and Receiver DMA signalling is available through two pins (24 and 29). When operating in the FIFO mode, one of two types of DMA signalling per pin can be selected via FCR3. When operating as in the 16450 Mode, only DMA mode 0 is allowed. Mode 0 supports single transfer DMA where a transfer is made between CPU bus cycles. Mode 1 supports multi-transfer DMA where multiple transfers are made continuously until the RCVR FIFO has been emptied or the XMIT FIFO has been filled.

RXRDY, Mode 0: When in the 16450 Mode (FCR0 = 0) or in the FIFO Mode (FCR0 = 1, FCR3 = 0) and there is at least 1 character in the RCVR FIFO or RCVR holding register, the RXRDY pin (29) will be low active. Once it is activated the RXRDY pin will go inactive when there are no more characters in the FIFO or holding register.

**RXRDY**, Mode 1: In the FIFO Mode (FCR0=1) when the FCR3=1 and the trigger level or the timeout has been reached, the RXRDY pin will go low active. Once it is activated it will go inactive when there are no more characters in the FIFO or holding register.

TXRDY, Mode 0: In the 16450 Mode (FCR0=0) or in the FIFO Mode (FCR0=1, FCR3=0) and there are no characters in the XMIT FIFO or XMIT holding register, the TXRDY pin (24) will be low active. Once it is activated the TXRDY pin will go inactive after the first character is loaded into the XMIT FIFO or holding register.

**TXRDY,** Mode 1: In the FIFO Mode (FCR0=1) when FCR3=1 and there are no characters in the XMIT FIFO, the TXRDY pin will go low active. This pin will become inactive when the XMIT FIFO is completely full.

$V_{DD}$ , Pin 40: +5V supply.

V<sub>SS</sub>, Pin 20: Ground (0V) reference.

**WR,**  $\overline{WR}$ , Write, Pins 19 and 18: When WR is high or  $\overline{WR}$  is low while the chip is selected, the CPU can write control words or data into the selected UART register.

Note: Only an active WR or  $\overline{\mathrm{WR}}$  input is required to transfer data to the UART during a write operation. Therefore, tie either the WR input permanently low or the  $\overline{\mathrm{WR}}$  input permanently high, when it is not used

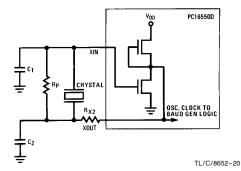

XIN (External Crystal Input), Pin 16: This signal input is used in conjunction with XOUT to form a feedback circuit for the baud rate generator's oscillator. If a clock signal will be generated off-chip, then it should drive the baud rate generator through this pin.

**XOUT** (External Crystal Output), Pin 17: This signal output is used in conjunction with XIN to form a feedback circuit for the baud rate generator's oscillator. If the clock signal will be generated off-chip, then this pin is unused.

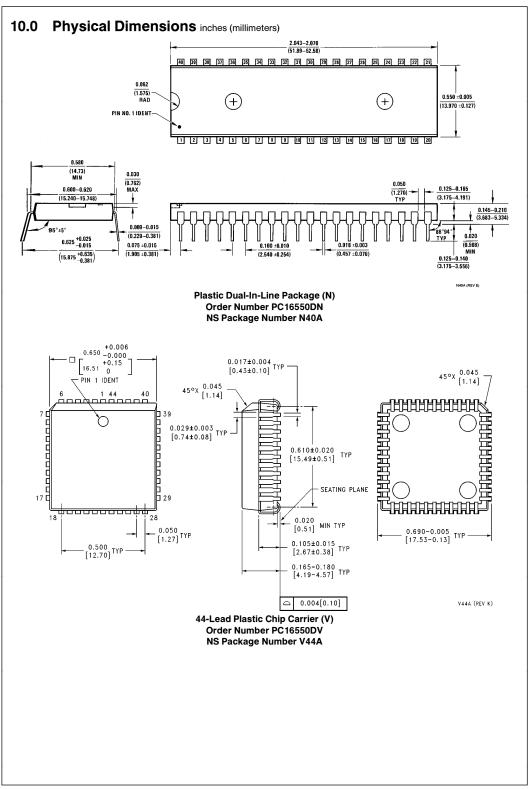

### 7.0 Connection Diagrams

Order Number PC16550DN See NS Package Number N40A

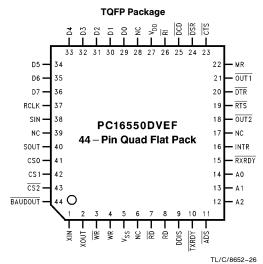

# 7.0 Connection Diagrams (Continued)

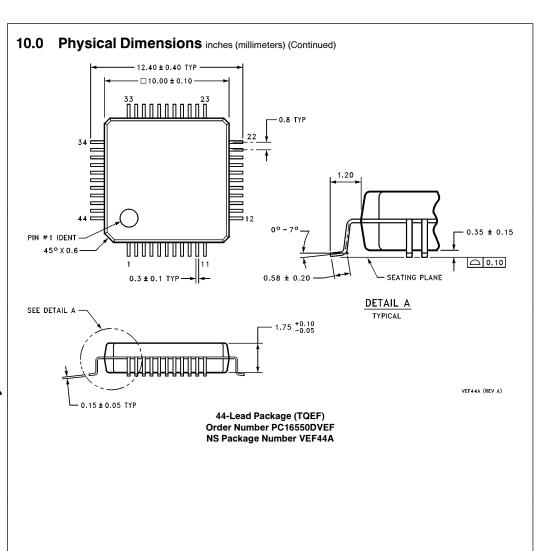

Order Number PC16550DVEF See NS Package Number VEF44A

#### **Chip Carrier Package** D4 D3 D2 D1 D0 NC $V_{DD}$ $\overline{RI}$ $\overline{DCD}$ $\overline{DSR}$ $\overline{CTS}$ 38 — OUT1 37 — DTR D6 D7 36 — RTS RCLK -35 — OUT2 SIN · NC -34 — NC SOUT -33 — INTR cso — 32 RXRDY CS1 - 15 31 — A0 <u>CS2</u> **−** 16 30 — A1 BAUDOUT - 17 29 — A2 XIN XOUT $\overline{\text{WR}}$ WR $V_{SS}$ NC $\overline{\text{RD}}$ RD DDIS $\overline{\text{TXRDY}}$ $\overline{\text{ADS}}$

Top View Number PC16550 TL/C/8652-18

Order Number PC16550DV See NS Package Number V44A

**TABLE I. UART Reset Configuration**

| Register/Signal                   | Reset Control         | Reset State               |

|-----------------------------------|-----------------------|---------------------------|

| Interrupt Enable Register         | Master Reset          | <b>0000</b> 0000 (Note 1) |

| Interrupt Identification Register | Master Reset          | 00 <b>00</b> 0001         |

| FIFO Control                      | Master Reset          | 0000 0000                 |

| Line Control Register             | Master Reset          | 0000 0000                 |

| MODEM Control Register            | Master Reset          | 0000 0000                 |

| Line Status Register              | Master Reset          | 0110 0000                 |

| MODEM Status Register             | Master Reset          | XXXX 0000 (Note 2)        |

| SOUT                              | Master Reset          | High                      |

| INTR (RCVR Errs)                  | Read LSR/MR           | Low                       |

| INTR (RCVR Data Ready)            | Read RBR/MR           | Low                       |

| INTR (THRE)                       | Read IIR/Write THR/MR | Low                       |

| INTR (Modem Status Changes)       | Read MSR/MR           | Low                       |

| OUT 2                             | Master Reset          | High                      |

| RTS                               | Master Reset          | High                      |

| DTR                               | Master Reset          | High                      |

| OUT 1                             | Master Reset          | High                      |

| RCVR FIFO                         | MR/FCR1●FCR0/∆FCR0    | All Bits Low              |

| XMIT FIFO                         | MR/FCR1●FCR0/∆FCR0    | All Bits Low              |

Note 1: Boldface bits are permanently low.

Note 2: Bits 7-4 are driven by the input signals.

| Data Bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0 DLAB = 0<br>Receiver<br>Buffer<br>Register<br>(Read | 0 DLAB=0<br>Transmitter<br>Holding<br>Register<br>(Write | 1 DLAB=0<br>Interrupt<br>Enable<br>Register                                   | 2<br>Interrupt<br>Ident.<br>Register<br>(Read | TABLE 2<br>2 FIFO Control Register (Write Control | TABLE II. Summary of Registers  Register Address  3 4  FO 3 4  FO Line MODEM gister Control Co | ddress 4  MODEM Control Register   | 5<br>Line<br>Status<br>Register              | 6<br>MODEM<br>Status<br>Register             | 7<br>Scratch<br>Reg-<br>ister | 0 DLAB=1<br>Divisor<br>Latch<br>(LS) | 1 DLAB=1<br>Divisor<br>Latch<br>(MS) |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------------------------------------|----------------------------------------------|-------------------------------|--------------------------------------|--------------------------------------|

| Date Bit 0   Frable   -vor'if   FrPO   Word   Teminal   Peady   Colear   Date Bit 0   Perding   Frable   Select   Colear   Cole | 3BR                                                   | THR                                                      | ER                                                                            | IIR                                           | FCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | LCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | MCR                                | LSR                                          | MSR                                          | SCR                           | DLL                                  | DLM                                  |

| Data Bit 1         Tenable Holding Figh         Interrupt Holding         FICO Length (FIS) (OE) Facet (FIS)         Request (OE) Facet (FIS) (OE) Facet (FIS)         Bit 1 (FIS) (OE) Facet (FIS) (OE) (OE) Facet (FIS) (OE) (OE) (OE) Facet (FIS) (OE) (OE) (OE) Facet (FIS) (OE) (OE) (OE) (OE) (OE) (OE) Facet (FIS) (OE) (OE) (OE) (OE) (OE) (OE) (OE) (OE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | tta Bit 0<br>Vote 1)                                  | Data Bit 0                                               | Enable<br>Received<br>Data<br>Available<br>Interrupt<br>(ERBFI)               | "0" if<br>Interrupt<br>Pending                | FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Word<br>Length<br>Select<br>Bit 0<br>(WLS0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Data<br>Terminal<br>Ready<br>(DTR) | Data<br>Ready<br>(DR)                        | Delta<br>Clear<br>to Send<br>(DCTS)          | Bit 0                         | Bit 0                                | Bit 8                                |

| Data Bit 2         Enable Receiver ID FIFO Slop Bits Interrupt (Line Status)         XMIT Resert         Number of (STB) Slop Bits (STB)         Out 1 FIFO Slop Bits (STB)         Trailing (PE) (TERI)         Bit 2 (TERI)         Bit 2 (TERI)         Rode Bit 3 (TERI)         Bit 4 (TERI)         Bit 4 (TERI)         Bit 3 (TERI)         Bit 4 (TERI)         Bit 5 (TERI)         Bit 4 (TERI)         Bit 5 (TERI)         Bit 4 (TERI)         Bit 5 (TERI)         Bit 6 (TERI)         Bit 7 (TERI) <td>tta Bit 1</td> <td>Data Bit 1</td> <td>Enable<br/>Transmitter<br/>Holding<br/>Register<br/>Empty<br/>Interrupt<br/>(ETBEI)</td> <td>Interrupt<br/>ID<br/>Bit (0)</td> <td>Reset</td> <td>Word<br/>Length<br/>Select<br/>Bit 1<br/>(WLS1)</td> <td>Request<br/>to Send<br/>(RTS)</td> <td>Overrun<br/>Error<br/>(OE)</td> <td>Delta<br/>Data<br/>Set<br/>Ready<br/>(DDSR)</td> <td>Bit 1</td> <td>Bit 1</td> <td>Bit 9</td>                                                                                                                                                                                          | tta Bit 1                                             | Data Bit 1                                               | Enable<br>Transmitter<br>Holding<br>Register<br>Empty<br>Interrupt<br>(ETBEI) | Interrupt<br>ID<br>Bit (0)                    | Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Word<br>Length<br>Select<br>Bit 1<br>(WLS1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Request<br>to Send<br>(RTS)        | Overrun<br>Error<br>(OE)                     | Delta<br>Data<br>Set<br>Ready<br>(DDSR)      | Bit 1                         | Bit 1                                | Bit 9                                |

| Data Bit 3         Enable (Note 2)         Interrupt (Note 2)         DMA (PEN)         Parity (PEN)         Out 2 (FE)         Framing (PED)         Delta Bit 3 (DDCD)           Data Bit 4         0         0         Reserved (PEN)         Even (PEN)         Loop (BI)         Break (DDCD)         Bit 4 (DDCD)           Data Bit 5         0         0         Reserved (PEN)         Stick (BI)         CTS)         Send (CTS)           Data Bit 5         0         0         Reserved (PEN)         Stick (BI)         CTS)         Set (CTS)           Data Bit 6         0         0         Reserved (PEN)         Stick (BI)         0         Transmitter (BI)         Set (CTS)           Data Bit 6         0         FIFOs         RCVR (SS)         Set (CTS)         Register (THRE)         Ring (RI)           Data Bit 7         0         FIFOs         RCVR (SS)         CLSB)         Register (TEMT)         Ring (RI)           Data Bit 7         0         FIFOs         RCVR (Note 2)         RCV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ata Bit 2                                             | Data Bit 2                                               | Enable<br>Receiver<br>Line Status<br>Interrupt<br>(ELSI)                      | Interrupt<br>ID<br>Bit (1)                    | XMIT<br>FIFO<br>Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Number of<br>Stop Bits<br>(STB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Out 1                              | Parity<br>Error<br>(PE)                      | Trailing<br>Edge Ring<br>Indicator<br>(TERI) | Bit 2                         | Bit 2                                | Bit 10                               |

| Data Bit 4         0         0         Reserved         Even Served         Loop         Break Interrupt Break         Clear CTS         Bit 4           Data Bit 5         0         0         Reserved         Stick Served         0         Transmitter Served CTS         Bit 5           Data Bit 6         0         FIFOs         RCVR         Set         Register Ready THRE         Ring         Bit 6           Data Bit 6         0         FIFOs         RCVR         Set         Ringer Empty         Ring         Bit 6           Note 2)         (LSB)         Break         (TEMT)         (RI)         (RI)           Data Bit 7         FIFOs         RCVR         Divisor         0         Error in         Data           Robert 1         Robert 1         RCVR         Access Bit 7         RCVR         CRAP         RCVR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ata Bit 3                                             | Data Bit 3                                               | Enable<br>MODEM<br>Status<br>Interrupt<br>(EDSSI)                             | Interrupt<br>ID<br>Bit (2)<br>(Note 2)        | DMA<br>Mode<br>Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Parity<br>Enable<br>(PEN)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Out 2                              | Framing<br>Error<br>(FE)                     | Delta<br>Data<br>Carrier<br>Detect<br>(DDCD) | Bit 3                         | Bit 3                                | Bit 11                               |

| Data Bit 5         0         0         Reserved Parity         Stick Parity         0         Transmitter Ploting Set Holding Set Holding Set Hegister Plegister Plegiste                                                                            | ata Bit 4                                             | # <u>#</u>                                               | 0                                                                             | 0                                             | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Even<br>Parity<br>Select<br>(EPS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Loop                               | Break<br>Interrupt<br>(BI)                   | Clear<br>to<br>Send<br>(CTS)                 | Bit 4                         | Bit 4                                | Bit 12                               |