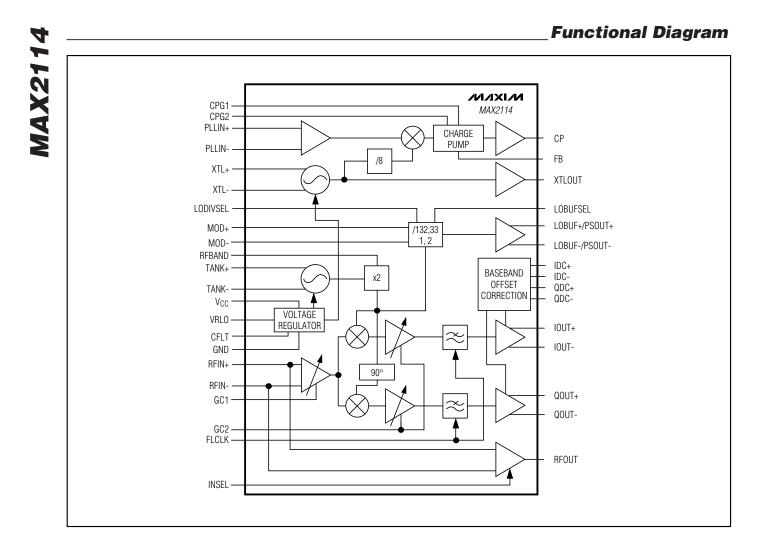

### **General Description**

The MAX2114 low-cost, direct-conversion tuner is designed for use in digital direct-broadcast satellite (DBS) television set-top box units. Its direct-conversion architecture reduces system cost compared to devices with IF-based architectures. The MAX2114 directly tunes L-band signals to baseband using a broadband I/Q downconverter. The operating frequency range spans 925MHz to 2175MHz.

The MAX2114 includes a low-noise amplifier (LNA) with gain control, I and Q downconverting mixers, lowpass filters with gain and frequency control, a local oscillator (LO) buffer with a 90° quadrature network, and a charge-pump-based phase-locked loop (PLL) for frequency control. The MAX2114 has an on-chip LO, requiring only an external varactor-tuned LC tank for operation. The LO's output drives the internal quadrature generator and has a buffer amplifier to drive off-chip circuitry. The MAX2114 comes in a 44-pin QFN package with exposed paddle (EP).

| _Applications |

|---------------|

|---------------|

| Broadband Systems      |

|------------------------|

| LMDS                   |

| Professional Receivers |

| VSAT                   |

| Microwave Links        |

|                        |

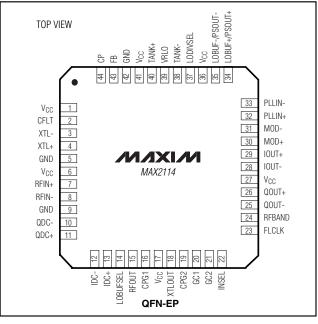

### Pin Configuration

###

\_ Maxim Integrated Products 1

For price, delivery, and to place orders, please contact Maxim Distribution at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

#### **Features**

- Complete Low-Cost Solution for DBS Direct Downconversion

- High Level of Integration Minimizes Component Count

- 1MBaud to 45MBaud Operation

- Selectable LO Buffer

- ♦ +5V Single-Supply Operation

- 925MHz to 2175MHz Input Frequency Range

- On-Chip Quadrature Generator, Dual-Modulus Prescaler (/32, /33)

- On-Chip Crystal Oscillator Amplifier

- PLL Phase Detector with Gain-Controlled Charge Pump

- Input Levels: -25dBm to -68dBm per Carrier

- Over 50dB Gain Control Range

- Noise Figure = 10.6dB; IIP3 = +10.7dBm (at 1550MHz)

- Automatic Baseband Offset Correction

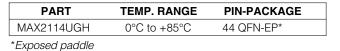

#### **Ordering Information**

Functional Diagram appears at end of data sheet.

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND                       | 0.3V to +7V       |

|----------------------------------------------|-------------------|

| All Other Pins to GND0.3V to                 | $(V_{CC} + 0.3V)$ |

| RFIN+ to RFIN-, TANK+ to TANK-,              |                   |

| IDC+ to IDC-, QDC+ to QDC                    |                   |

| IOUT_, QOUT_ to GND Short-Circuit Duration   |                   |

| LOBUF+/PSOUT+, LOBUF-/PSOUT- Short-Circuit I | Duration10s       |

| VRLO Short-Circuit Duration                  | 0s                |

Continuous Current (any pin other than V<sub>CC</sub> or GND)......20mA Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )

| 44-Pin QFN-EP (derate 27mW/°C al  | bove +70°C)1.8W |

|-----------------------------------|-----------------|

| Operating Temperature             | 0°C to +85°C    |

| Junction Temperature              | +150°C          |

| Storage Temperature Range         | 65°C to +150°C  |

| Lead Temperature (soldering, 10s) | +300°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +4.75V \text{ to } +5.25V, V_{FB} = +2.4V, C_{IOUT} = C_{QOUT} = 10\text{pF}, \text{f}_{FLCLK} = 2\text{MHz}, \text{RFIN} = \text{unconnected}, \text{R}_{IOUT} = \text{R}_{QOUT} = 10\text{k}\Omega, \text{V}_{LOBUFSEL} = +0.5V, \text{V}_{FBAND} = \text{VINSEL} = \text{VCPG1} = \text{VCPG2} = +2.4V, \text{VPLLIN} = \text{VMOD} + = +1.3V, \text{VPLLIN} = \text{VMOD} + = +1.1V, \text{TA} = -1.1V, \text{TA} = -$ +25°C, unless otherwise noted. Typical values are at  $V_{CC} = +5V$ , unless otherwise noted.)

| PARAMETER                    | SYMBOL     | CONDITIONS                                                                    | MIN  | TYP | MAX  | UNITS |

|------------------------------|------------|-------------------------------------------------------------------------------|------|-----|------|-------|

| Operating Supply Voltage     | Vcc        |                                                                               | 4.75 |     | 5.25 | V     |

| Operating Supply Current     | ICC        |                                                                               |      | 195 | 275  | mA    |

| STANDARD DIGITAL INPUTS      | INSEL, CPG | 1, CPG2, LOBUFSEL, LODIVSEL, RFBAND)                                          |      |     |      |       |

| Input Voltage High           | VIH        |                                                                               | 2.4  |     |      | V     |

| Input Voltage Low            | VIL        |                                                                               |      |     | 0.5  | V     |

| Input Current                | lin        |                                                                               | -15  |     | 10   | μA    |

| RFBAND Input Current         |            |                                                                               | -200 |     | 200  | μA    |

| SLEW-RATE-LIMITED DIGITAL    | INPUT (fFL | CLK)                                                                          |      |     |      |       |

| FLCLK Input Voltage High     |            |                                                                               | 1.85 |     |      | V     |

| FLCLK Input Voltage Low      |            |                                                                               |      |     | 1.45 | V     |

| FLCLK Input Current (Note 1) |            | RSOURCE = $50k\Omega$ , VFLCLK = 1.65V                                        | -1   |     | 1    | μA    |

| DIFFERENTIAL DIGITAL INPU    | TS (MOD+,  | MOD-, PLLIN+, PLLIN-)                                                         |      |     |      |       |

| Common-Mode Input Voltage    | VCMI       |                                                                               | 1.08 | 1.2 | 1.32 | V     |

| Input Voltage Low            |            | Referenced to V <sub>CMI</sub>                                                |      |     | -100 | mV    |

| Input Voltage High           |            | Referenced to VCMI                                                            | 100  |     |      | mV    |

| Input Current (Note 1)       |            |                                                                               | -5   |     | 5    | μA    |

| DIFFERENTIAL DIGITAL OUTF    | UTS (LOBL  | IF+/PSOUT+, LOBUF-/PSOUT-)                                                    |      |     |      |       |

| Common-Mode Output Voltage   | Vсмо       |                                                                               | 2.16 | 2.4 | 2.64 | V     |

| Output Voltage Low (Note 2)  |            | Referenced to V <sub>CMO</sub> , LOBUFSEL $\leq$ 0.5V                         |      |     | -150 | mV    |

| Output Voltage High (Note 2) |            | Referenced to V <sub>CMO</sub> , LOBUFSEL $\leq$ 0.5V                         | 150  |     |      | mV    |

| FREQUENCY SYNTHESIZER/L      | O BUFFER   | ·                                                                             |      |     |      |       |

|                              |            | $(V_{MOD+} - V_{MOD-}) \ge 200 \text{mV}, \text{ LOBUFSEL} \le 0.5 \text{V}$  | 32   |     | 32   |       |

| Prescaler Ratio              |            | $(V_{MOD+} - V_{MOD-}) \le -200 \text{mV}, \text{ LOBUFSEL} \le 0.5 \text{V}$ | 33   |     | 33   |       |

|                              |            | LOBUFSEL ≥ 2.4V, LODIVSEL ≤ 0.5V                                              | 2    |     | 2    |       |

|                              |            | LOBUFSEL ≥ 2.4V, LODIVSEL ≥ 2.4V                                              | 1    |     | 1    |       |

| Reference Divider Ratio      |            |                                                                               | 8    |     | 8    |       |

| XTLOUT Output DC Voltage     |            |                                                                               |      | 1.9 |      | V     |

|                              |            | $V_{CPG1} \le 0.5V$ , $V_{CPG2} \le 0.5V$                                     | 0.08 | 0.1 | 0.12 |       |

| Charge-Pump Output High      |            | $V_{CPG1} \le 0.5V, V_{CPG2} \ge 2.4V$                                        | 0.24 | 0.3 | 0.36 | mA    |

| Measured at FB               |            | $V_{CPG1} \ge 2.4V, V_{CPG2} \le 0.5V$                                        | 0.48 | 0.6 | 0.72 | ]     |

|                              |            | $V_{CPG1} \ge 2.4V, V_{CPG2} \ge 2.4V$                                        | 1.44 | 1.8 | 2.16 |       |

### DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = +4.75V \text{ to } +5.25V, V_{FB} = +2.4V, C_{IOUT} = C_{QOUT} = 10\text{pF}, f_{FLCLK} = 2\text{MHz}, \text{RFIN} = \text{unconnected}, \text{R}_{IOUT} = \text{R}_{QOUT} = 10\text{k}\Omega, \\ V_{LOBUFSEL} = +0.5V, V_{RFBAND} = V_{INSEL} = V_{CPG1} = V_{CPG2} = +2.4V, V_{PLLIN+} = V_{MOD+} = +1.3V, V_{PLLIN-} = V_{MOD-} = +1.1V, \text{T}_{A} = +25^{\circ}\text{C}, \text{ unless otherwise noted}.$

| PARAMETER                                                   | SYMBOL     | CONDITIONS                             | MIN   | TYP  | MAX   | UNITS |

|-------------------------------------------------------------|------------|----------------------------------------|-------|------|-------|-------|

|                                                             |            | $V_{CPG1} \le 0.5V, V_{CPG2} \le 0.5V$ | -0.12 | -0.1 | -0.08 |       |

| Charge-Pump Output Low                                      |            | $V_{CPG1} \le 0.5V, V_{CPG2} \ge 2.4V$ | -0.36 | -0.3 | -0.24 | mA    |

| Measured at FB                                              |            | $V_{CPG1} \ge 2.4V, V_{CPG2} \le 0.5V$ | -0.72 | -0.6 | -0.48 |       |

|                                                             |            | VCPG1 ≥ 2.4V, VCPG2 ≥ 2.4V             | -2.16 | -1.8 | -1.44 |       |

| Charge-Pump Output Current<br>Matching Positive to Negative |            | Measured at FB                         | -5    |      | 5     | %     |

| Charge-Pump Output Leakage                                  |            | Measured at FB                         | -25   |      | 25    | nA    |

| Charge-Pump Output Current<br>Drive (Note 1)                |            | Measured at CP                         | 100   |      |       | μA    |

| ANALOG CONTROL INPUTS (G                                    | C1, GC2)   | -                                      |       |      |       |       |

| Input Current                                               | IGC_       | $V_{GC_{-}} = 1V \text{ to } 4V$       | -50   |      | 50    | μA    |

| BASEBAND OUTPUTS (IOUT+,                                    | IOUT-, QOL | JT+, QOUT-)                            |       |      |       |       |

| Differential Output Voltage<br>Swing                        |            | $R_L = 2k\Omega$ differential          | 1     |      |       | Vp-р  |

| Common-Mode Output Voltage<br>(Note 1)                      |            |                                        | 0.65  |      | 0.85  | V     |

| Offset Voltage (Note 1)                                     |            |                                        | -50   |      | 50    | mV    |

### **AC ELECTRICAL CHARACTERISTICS**

(IC driven single-ended with RFIN- AC-terminated in 75 $\Omega$  to GND, V<sub>CC</sub> = +4.75V to +5.25V, V<sub>IOUT</sub> = V<sub>QOUT</sub> = 0.59Vp-p, C<sub>IOUT</sub> = C<sub>QOUT</sub> = 10pF, f<sub>FCLK</sub> = 500kHz, R<sub>IOUT</sub> = R<sub>QOUT</sub> = 10k $\Omega$ , V<sub>LOBUFSEL</sub> = 0.5V, V<sub>RFBAND</sub> = V<sub>INSEL</sub> = V<sub>CPG1</sub> = V<sub>CPG2</sub> = +2.4V, V<sub>PLLIN</sub> = V<sub>MOD</sub> = +1.3V, V<sub>PLLIN</sub> = V<sub>MOD</sub> = +1.1V, T<sub>A</sub> = +25°C, unless otherwise noted. Typical values are at V<sub>CC</sub> = +5V.)

| PARAMETER                                           | SYMBOL                | CONDITIONS                  |                                                      |                                                    | MIN | ТҮР  | MAX  | UNITS      |

|-----------------------------------------------------|-----------------------|-----------------------------|------------------------------------------------------|----------------------------------------------------|-----|------|------|------------|

| RFIN_ Input Frequency Range                         | fRFIN_                | Inferred b<br>phase-err     | 5 1                                                  | re gain and                                        | 925 |      | 2175 | MHz        |

| RFIN_ Input Power for 0.59Vp-p<br>Baseband Levels   |                       | Single<br>carrier           |                                                      | $GC_2 = +4V$ (min gain)<br>$GC_2 = +1V$ (max gain) | -25 |      | -68  | dBm        |

|                                                     |                       |                             |                                                      | $f_{LO} = 2175 \text{MHz}$                         |     | 8.0  | -00  |            |

| RFIN_ Input Third-Order Intercept<br>Point (Note 3) |                       | PRFIN_ = -                  | 2008111                                              | $f_{LO} = 1550 MHz$                                |     | 10.7 |      |            |

|                                                     | IP3 <sub>RFIN</sub> _ | per tone                    |                                                      | $f_{LO} = 950 MHz$                                 |     | 11.1 |      |            |

|                                                     | IF SRFIN_             | PRFIN_ = -65dBm<br>per tone |                                                      | $f_{LO} = 2175 MHz$                                |     | -29  |      | - dBm<br>- |

|                                                     |                       |                             |                                                      | $f_{LO} = 1550 MHz$                                |     | -26  |      |            |

|                                                     |                       |                             |                                                      | $f_{LO} = 950 MHz$                                 |     | -30  |      |            |

| RFIN_ Input Second-Order Intercept<br>(Note 4)      | IP2 <sub>RFIN</sub> _ | -                           | $P_{RFIN} = -25 dBm per tone,$<br>$f_{LO} = 951 MHz$ |                                                    |     | 16.1 |      | dBm        |

| Output-Referred 1dB Compression<br>Point (Note 5)   | P1 <sub>dBOUT</sub>   | -                           | PRFIN_ = -40dBm,<br>signals within filter bandwidth  |                                                    |     | 2    |      | dBV        |

| Naios Figuro                                        | NF                    | $f_{RFIN} = 1$<br>VGC1 = 1  |                                                      | P <sub>RFIN</sub> _ = -65dBm                       |     | 10.6 |      | dB         |

| Noise Figure                                        |                       | adjusted 0.59Vp-p           |                                                      | P <sub>RFIN</sub> = -25dBm                         |     | 44.8 |      | UD         |

### AC ELECTRICAL CHARACTERISTICS (continued)

$(\mathsf{R}_{\mathsf{FIN}} + \mathsf{IC} \text{ driven single-ended with RFIN- AC-terminated in 75} \Omega \text{ to GND}, \mathsf{V}_{\mathsf{CC}} = +4.75\mathsf{V} \text{ to } +5.25\mathsf{V}, \mathsf{V}_{\mathsf{IOUT}} = \mathsf{V}_{\mathsf{QOUT}} = 0.59\mathsf{V}_{\mathsf{P}}\mathsf{P}, \mathsf{C}_{\mathsf{IOUT}} = \mathsf{C}_{\mathsf{QOUT}} = 10\mathsf{p}\mathsf{F}, \mathsf{f}_{\mathsf{FCLK}} = 500\mathsf{kHz}, \mathsf{R}_{\mathsf{IOUT}} = \mathsf{R}_{\mathsf{QOUT}} = 10\mathsf{k}\Omega, \mathsf{V}_{\mathsf{LOBUFSEL}} = 0.5\mathsf{V}, \mathsf{V}_{\mathsf{RFBAND}} = \mathsf{V}_{\mathsf{INSEL}} = \mathsf{V}_{\mathsf{CPG1}} = \mathsf{V}_{\mathsf{CPG2}} = +2.4\mathsf{V}, \mathsf{V}_{\mathsf{PLLIN}} = \mathsf{V}_{\mathsf{MOD}} = +1.3\mathsf{V}, \mathsf{V}_{\mathsf{PLLIN}} = +25^\circ\mathsf{C}, \mathsf{unless otherwise noted}. \mathsf{Typical values are at V}_{\mathsf{CC}} = +5\mathsf{V}. )$

| PARAMETER                                               | SYMBOL | CONDITIONS                                                                  | MIN  | ТҮР  | MAX | UNITS   |

|---------------------------------------------------------|--------|-----------------------------------------------------------------------------|------|------|-----|---------|

| Rever Deturn Loop (Note 6)                              |        | $f_{RFIN}$ = 925MHz, $Z_{SOURCE}$ = 75 $\Omega$                             |      | +13  |     | dB      |

| R <sub>FIN</sub> + Return Loss (Note 6)                 |        | $f_{RFIN}$ = 2175MHz, $Z_{SOURCE}$ = 75 $\Omega$                            |      | +14  |     | ив      |

| LO 2nd Harmonic Rejection (Note 7)                      |        | Average level of VIOUT_, VQOUT_                                             |      | 45   |     | dB      |

| LO Half Harmonic Rejection (Note 8)                     |        | Average level of VIOUT_, VQOUT_                                             |      | 43   |     | dB      |

| LO Leakage Power (Notes 6, 9)                           |        | Measured at R <sub>FIN</sub> +                                              |      | -66  |     | dBm     |

| RFOUT PORT (LOOPTHROUGH)                                | 1      | 1                                                                           | 1    |      |     | 1       |

|                                                         |        | f = 925MHz                                                                  |      | 0.5  |     |         |

| RFIN+ to RFOUT Gain (Note 10)                           |        | f = 1550MHz                                                                 |      | 1.0  |     | dB      |

|                                                         |        | f = 2175MHz                                                                 |      | 2.0  |     |         |

|                                                         |        | f = 925MHz                                                                  |      | 9.5  |     |         |

| RFOUT Output Third-Order Intercept<br>Point (Note 10)   |        | f = 1550MHz                                                                 |      | 7.7  |     | dBm     |

|                                                         |        | f = 2175MHz                                                                 |      | 5.4  |     |         |

| RFOUT Noise Figure (Note 10)                            |        | f = 925MHz                                                                  |      | 12   |     |         |

|                                                         |        | f = 1550MHz                                                                 |      | 10.6 |     | dB      |

|                                                         |        | f = 2175MHz                                                                 |      | 10.8 |     |         |

| RFOUT Return Loss (Notes 6, 10)                         |        | 925MHz < f < 2175MHz, $Z_{LOAD} = 75\Omega$                                 |      | 12   |     | dB      |

| Output Real Impedance (Notes 1)                         |        | IOUT_, QOUT_                                                                |      |      | 50  | Ω       |

| Baseband Highpass -3dB Frequency (Note 1)               |        | $C_{IDC_} = C_{QDC_} = 0.22 \mu F$                                          |      |      | 750 | Hz      |

| LPF -3dB Cutoff-Frequency Range<br>(Note 1)             |        | Controlled by FLCLK signal                                                  | 8    |      | 33  | MHz     |

| Baseband Frequency Response<br>(Note 1)                 |        | Deviation from ideal 7th order, Butterworth, up to 0.7 $\times$ fc          | -0.5 |      | 0.5 | dB      |

|                                                         |        | $f_{FLCLK} = 0.5MHz, f_C = 8MHz$                                            | -5.5 |      | 5.5 |         |

| LPF -3dB Cutoff-Frequency<br>Accuracy (Note 1)          |        | fFLCLK = 1.25MHz, fC = 19.3MHz                                              | -10  |      | 10  | %       |

| Accuracy (Note 1)                                       |        | fFLCLK = 2.0625MHz, fC = 31.4MHz                                            | 10   |      | 10  |         |

| Ratio of In-Filter-Band to Out-of-Filter-<br>Band Noise |        | $f_{IN\_BAND} = 100Hz$ to 22.5MHz,<br>$f_{OUT\_BAND} = 67.5MHz$ to 112.5MHz |      | 23   |     | dB      |

| Quadrature Gain Error                                   |        | Includes effects from baseband filters,<br>measured at 125kHz baseband      |      |      | 1.2 | dB      |

| Quadrature Phase Error                                  |        | Includes effects from baseband filters,<br>measured at 125kHz baseband      |      |      | 4   | degrees |

#### AC ELECTRICAL CHARACTERISTICS (continued)

(IC driven single-ended with RFIN- AC-terminated in 75 $\Omega$  to GND, V<sub>CC</sub> = +4.75V to +5.25V, V<sub>IOUT</sub> = V<sub>QOUT</sub> = 0.59Vp-p, C<sub>IOUT</sub> = C<sub>QOUT</sub> = 10pF, f<sub>FCLK</sub> = 500kHz, R<sub>IOUT</sub> = R<sub>QOUT</sub> = 10k $\Omega$ , V<sub>LOBUFSEL</sub> = 0.5V, V<sub>RFBAND</sub> = V<sub>INSEL</sub> = V<sub>CPG1</sub> = V<sub>CPG2</sub> = +2.4V, V<sub>PLLIN</sub> = V<sub>MOD</sub> = +1.3V, V<sub>PLLIN</sub> = V<sub>MOD</sub> = +1.1V, T<sub>A</sub> = +25°C, unless otherwise noted. Typical values are at V<sub>CC</sub> = +5V.)

| PARAMETER                            | SYMBOL | CONDITIONS                                                                | MIN | TYP | MAX  | UNITS             |  |  |  |

|--------------------------------------|--------|---------------------------------------------------------------------------|-----|-----|------|-------------------|--|--|--|

| SYNTHESIZER                          |        |                                                                           |     |     |      |                   |  |  |  |

| XTLOUT Output Voltage Swing          |        | Load = 10pF II 10k $\Omega$ , f <sub>XTLOUT</sub> = 4MHz                  | 0.8 | 1   | 1.5  | Vp-p              |  |  |  |

| Crystal Frequency Range (Note 1)     |        |                                                                           | 4   |     | 7.26 | MHz               |  |  |  |

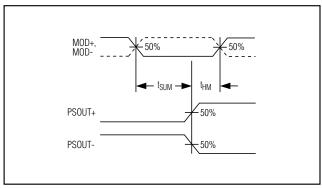

| MOD+, MOD- Setup Time (Note 1)       | tsum   | Figure 1                                                                  | 7   |     |      | ns                |  |  |  |

| MOD+, MOD- Hold Time (Note 1)        | tHM    | Figure 1                                                                  | 0   |     |      | ns                |  |  |  |

| LOCAL OSCILLATOR                     |        |                                                                           |     |     |      |                   |  |  |  |

| LO Tuning Range (Note 11)            |        |                                                                           | 590 |     | 1180 | MHz               |  |  |  |

| LO Buffer Output Voltage (Note 1)    |        | $V_{LOBUFSEL} \ge 2.4V$ ,<br>$f_{LO} = 925 \text{ MHz} + 2175 \text{MHz}$ | 70  |     |      | mV <sub>RMS</sub> |  |  |  |

|                                      |        | At 1kHz offset, f <sub>LO</sub> = 2175MHz                                 |     | -60 |      |                   |  |  |  |

| LO Phase Noise (Notes 6, 12)         |        | At 10kHz offset, fLO = 2175MHz                                            |     | -75 |      | dBc/Hz            |  |  |  |

|                                      |        | At 100kHz offset, fLO = 2175MHz                                           |     | -96 |      |                   |  |  |  |

| RFIN+ to LO Input Isolation (Note 9) |        | f <sub>RFIN</sub> = 2175MHz                                               |     | 58  |      | dB                |  |  |  |

Note 1: Minimum and maximum values are guaranteed by design and characterization over supply voltage.

**Note 2** Driving differential load of  $10k\Omega \parallel 15pF$ .

**Note 3:** Two signals are applied to RFIN\_ at ( $f_{LO}$  - 100MHz) and ( $f_{LO}$  - 199MHz). V<sub>GC2</sub> = 1V, V<sub>GC1</sub> is set so that the baseband outputs are at 590mVp-p. IM products are measured at baseband outputs but are referred to RF inputs.

**Note 4:** Two signals are applied to RFIN\_ at 1200MHz and 2150MHz.  $V_{GC2} = 1V$ ,  $V_{GC1}$  is set so that the baseband outputs are at 590mVp-p. IM products are measured at baseband outputs but are referred to RF inputs.

Note 5: P<sub>RFIN</sub> = -40dBm so that front-end IM contributions are minimized.

Note 6: Using L64733/L64734 demo board from LSI Logic.

Note 7: Downconverted level, in dBc, of carrier present at  $f_{LO} \times 2$ ,  $f_{LO} = 1180$ MHz,  $f_{VCO} = 590$ MHz,  $V_{RFBAND} =$  unconnected.

Note 8: Downconverted level, in dBc, of carrier present at  $f_0 / 2$ ,  $f_{LO} = 2175MHz$ ,  $f_{VCO} = 1087.5MHz$ ,  $V_{RFBAND} = 2.4V$ .

**Note 9:** Leakage is dominated by board parasitics.

**Note 10:**  $V_{CPG1} = V_{CPG2} = V_{RFBAND} = V_{INSEL} = 0.5V$ ,  $f_{FLCLK} = 0.5MHz$ .

**Note 11:** Guaranteed by design and characterization over supply and temperature.

**Note 12:** Measured at tuned frequency with PLL locked. PLL loop bandwidth = 3kHz. All phase noise measurements assume tank components have a Q > 50.

### \_\_\_\_\_Pin Description

|                         |          | -<br>-                                                                                                                                                                                                            |

|-------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN                     | NAME     | FUNCTION                                                                                                                                                                                                          |

| 1, 6, 17,<br>27, 36, 41 | Vcc      | $V_{CC}$ Power-Supply Input. Connect each pin to a +5V $\pm 5\%$ low-noise supply. Bypass each $V_{CC}$ pin to the nearest GND with a ceramic chip capacitor.                                                     |

| 2                       | CFLT     | External Bypass for Internal Bias. Bypass this pin with a 0.22µF ceramic chip capacitor to GND.                                                                                                                   |

| 3                       | XTL-     | Inverting Input to Crystal Oscillator. Consult crystal manufacturer for circuit loading requirements.                                                                                                             |

| 4                       | XTL+     | Noninverting Input to Crystal Oscillator. Consult crystal manufacturer for circuit loading requirements.                                                                                                          |

| 5, 9, 42                | GND      | Ground. Connect each of these pins to a solid ground plane. Use multiple vias to reduce inductance where possible.                                                                                                |

| 7                       | RFIN-    | RF Inverting Input. Bypass RFIN- with 47pF capacitor in series with a 75 $\Omega$ resistor to GND.                                                                                                                |

| 8                       | RFIN+    | RF Noninverting Input. Connect to $75\Omega$ source with a 47pF ceramic chip capacitor.                                                                                                                           |

| 10                      | QDC-     | Baseband Offset Correction. Connect a 0.22µF ceramic chip capacitor from QDC- to QDC+ (pin 11).                                                                                                                   |

| 11                      | QDC+     | Baseband Offset Correction. Connect a 0.22µF ceramic chip capacitor from QDC+ to QDC- (pin 10).                                                                                                                   |

| 12                      | IDC-     | Baseband Offset Correction. Connect a 0.22µF ceramic chip capacitor from IDC- to IDC+ (pin 13).                                                                                                                   |

| 13                      | IDC+     | Baseband Offset Correction. Connect a 0.22µF ceramic chip capacitor from IDC+ to IDC- (pin 12).                                                                                                                   |

| 14                      | LOBUFSEL | Local Oscillator Buffer Select. Connect to GND to select DIV32/33 prescaler output; connect $V_{CC}$ to DIV1 to select DIV2 LO buffer output.                                                                     |

| 15                      | RFOUT    | Buffered RF Output. Enabled when INSEL is low.                                                                                                                                                                    |

| 16                      | CPG1     | Charge-Pump Gain Select. High-impedance digital input. Sets the charge-pump output scaling. See <i>DC Electrical Characteristics</i> for available gain settings.                                                 |

| 18                      | XTLOUT   | Buffered Crystal Oscillator Output                                                                                                                                                                                |

| 19                      | CPG2     | Charge-Pump Gain Select. High-impedance digital input. Sets the charge-pump output scaling. See <i>DC Electrical Characteristics</i> for available gain settings.                                                 |

| 20                      | GC1      | Gain Control Input for RF Front End. High-impedance analog input, with an input range of +1V to +4V. See AC Electrical Characteristics for transfer function.                                                     |

| 21                      | GC2      | Gain Control Input for Baseband Signals. High-impedance analog input, with an input range of +1V to +4V. See AC Electrical Characteristics for transfer function.                                                 |

| 22                      | INSEL    | Loopthrough Mode Enable. High-impedance digital input. Drive low to enable the RFOUT buffer and disable the LO converters. Drive high for normal tuner operation.                                                 |

| 23                      | FLCLK    | Baseband Filter Cutoff Adjust. Connect to a slew-rate-limited clock source. See AC Electrical Characteristics for transfer function.                                                                              |

| 24                      | RFBAND   | RF Input Band Select Input. Drive high to enable 1680MHz to 2175MHz band. Leave unconnected to enable 1180MHz to 1680MHz band. Connect to GND to enable 925MHz to 1180MHz band.                                   |

| 25                      | QOUT-    | Baseband Quadrature Output. Connect to inverting input of high-speed ADC.                                                                                                                                         |

| 26                      | QOUT+    | Baseband Quadrature Output. Connect to noninverting input of high-speed ADC.                                                                                                                                      |

| 28                      | IOUT-    | Baseband In-Phase Output. Connect to inverting input of high-speed ADC.                                                                                                                                           |

| 29                      | IOUT+    | Baseband In-Phase Output. Connect to noninverting input of high-speed ADC.                                                                                                                                        |

| 30                      | MOD+     | PECL Modulus Control. A PECL high on MOD+ sets the dual-modulus prescaler to divide by 32. A PECL logic low sets the divide ratio to 33. Drive with a differential PECL signal in conjunction with MOD- (pin 31). |

### Pin Description (continued)

| PIN | NAME              | FUNCTION                                                                                                                                                                                                                        |

|-----|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31  | MOD-              | PECL Modulus Control. A PECL low on MOD- sets the dual-modulus prescaler to divide by 32. A PECL logic high sets the divide ratio to 33. Drive with a differential PECL signal in conjunction with MOD+ (pin 30).               |

| 32  | PLLIN+            | PECL Phase-Locked Loop Input. Drive with a differential PECL signal in conjunction with PLLIN- (pin 33).                                                                                                                        |

| 33  | PLLIN-            | PECL Phase-Locked Loop Input. Drive with a differential PECL signal in conjunction with PLLIN+ (pin 32).                                                                                                                        |

| 34  | LOBUF+/<br>PSOUT+ | LOBUFSEL = GND: PECL Prescaler Output. Differential output of the dual-modulus prescaler. Used in conjunction with PSOUT Requires PECL-compatible termination. LOBUFSEL = $V_{CC}$ : 50 $\Omega$ LO buffer noninverting output. |

| 35  | LOBUF-/<br>PSOUT- | LOBUFSEL = GND: PECL Prescaler Output. Differential output of the dual-modulus prescaler. Used in conjunction with PSOUT+. Requires PECL-compatible termination. LOBUFSEL = $V_{CC}$ : 50 $\Omega$ LO buffer inverting output.  |

| 37  | LODIVSEL          | LO Buffer Divider Ratio Input. Drive high to enable divide-by-one LO buffer output. Connect to GND to enable divide-by-two buffer output.                                                                                       |

| 38  | TANK-             | LO Tank Oscillator Input. Connect to an external LC tank with varactor tuning.                                                                                                                                                  |

| 39  | VRLO              | LO Internal Regulator. Bypass with a 1000pF ceramic chip capacitor to GND.                                                                                                                                                      |

| 40  | TANK+             | LO Tank Oscillator Input. Connect to an external LC tank with varactor tuning.                                                                                                                                                  |

| 43  | FB                | Feedback Input for Loop Filter                                                                                                                                                                                                  |

| 44  | CP                | Voltage Drive Output. Control of external charge-pump transistor.                                                                                                                                                               |

Figure 1. Modulus Control Timing Diagram

7

MAX2114

**Package Information**

For the latest package outline information, go to **www.maxim-ic.com/packages**.

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Printed USA

#### \_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2001 Maxim Integrated Products

8

is a registered trademark of Maxim Integrated Products.

|                                                                                                                                          |                                                                 |                                                                            |                                                                                                                    | ENC                             | <u>GLISH • ????</u> • <u>???</u> • <u>???</u>           |

|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------------------------------|

|                                                                                                                                          |                                                                 |                                                                            |                                                                                                                    |                                 |                                                         |

| <u>VHAT'S NEWPRODU</u>                                                                                                                   | CTSSOLUTION                                                     | IS DESIGN A                                                                | <u>PPNOTES</u> <u>SUPPORT</u>                                                                                      | BUY                             | COMPANY MEMBERS                                         |

|                                                                                                                                          |                                                                 |                                                                            | <u>X2114</u><br>mber Table                                                                                         |                                 |                                                         |

| Notes:                                                                                                                                   |                                                                 |                                                                            |                                                                                                                    |                                 |                                                         |

| <ol> <li>Other options ar</li> <li><u>Didn't Find What</u>one business day</li> <li>Part number sufficient data sheet or Part</li> </ol> | at You Need? Ask<br>y.<br>fixes: T or T&R =<br>rt Naming Conver | asing parts are lis<br>c our applications<br>= tape and reel; +<br>ntions. | ted at: <u>http://www.maxin</u><br>engineers. Expert assista<br>- = RoHS/lead-free; # =<br>wing. "PkgCode/Variatio | ance in finding<br>RoHS/lead-ex | ; parts, usually within<br>kempt. More: See <u>full</u> |

| Part Number                                                                                                                              | Free Buy<br>Sample Direct                                       | <b>Package:</b> TYF<br>DRA                                                 | PE PINS SIZE<br>AWING CODE/VAR *                                                                                   | Temp                            | RoHS/Lead-Free?<br>Materials Analysis                   |

| MAX2114UGH-TD                                                                                                                            |                                                                 |                                                                            |                                                                                                                    | 0C to +85C                      | RoHS/Lead-Free: <u>No</u>                               |

| MAX2114UGH-D                                                                                                                             |                                                                 | QFN;44 pin;7x´<br>Dwg: <u>21-0092H</u><br>Use pkgcode/va                   |                                                                                                                    | 0C to +85C                      | RoHS/Lead-Free: <u>No</u><br><u>Materials Analysis</u>  |

| Didn't Find What You                                                                                                                     | Need?                                                           |                                                                            |                                                                                                                    |                                 |                                                         |

### CONTACT US: SEND US AN EMAIL

Copyright 2007 by Maxim Integrated Products, Dallas Semiconductor • Legal Notices • Privacy Policy