# **LP3925**

# **High Performance Power Management Unit for Handset Applications**

# **General Description**

The LP3925 is designed to meet the power management requirements of the latest 3G/GSM/GPRS/EDGE cellular phones. The LP3925 PMU contains a single-input Li-Ion battery charger, 14 low-dropout voltage regulators including 3 wide-input, low-output, regulators, 3 buck regulators, a USB Transceiver, two comparators, two TCXO buffers, SIM level shifter, 12-bit ADC, real time clock, and backup battery charger. Programming is handled via an I<sup>2</sup>C-compatible high-speed Serial Interface allowing control of program on/off conditions and the output voltages of individual regulators, and to read status information of the PMU.

It can charge and maintain a single cell Li-lon battery operating from an AC adapter or USB power source.

The Li-lon charger requires few external components and integrates the power FET. Charging is thermally regulated to obtain the most efficient charging rate for a given ambient temperature.

A built-in Over-Voltage Protection (OVP) circuit at the charger input protects the PMU from input voltages up to +28V eliminating the need for any external protection circuitry.

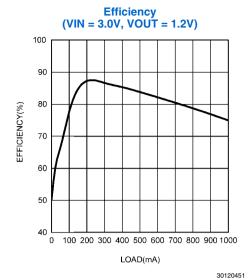

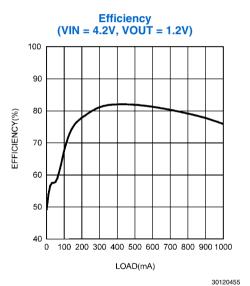

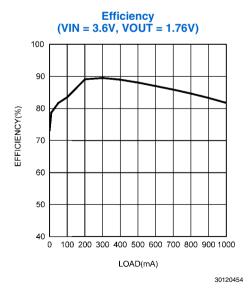

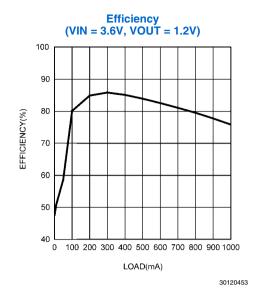

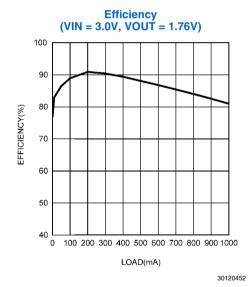

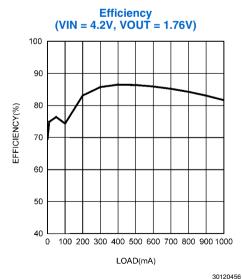

Buck regulators have an automatic switch to ECO mode at low load conditions providing very good efficiency at low output currents.

Buck regulators have an automatic switch to ECO mode at low load conditions providing very good efficiency at low output currents.

General-type "PERFECT" LDO regulators provide excellent PSRR and ULTRA LOW NOISE, 10  $\mu$ V typ., ideally suited for supplying voltage to RF section.

The real-time clock/calendar provides time interval information as well as two programmable alarms.

To accommodate different baseband requirements, the LP3925 PMU has different default voltage settings and start-up sequences. Two general-purpose comparators can be used for detecting external accessories like ear-phones etc. Power conversion and signal level shifting circuits are provided to allow SIM interfacing.

#### **Features**

- Linear charger with single input

- USB or AC adapter input

- Power routing switch

- 28V OVP on the charger input

- Three high-efficiency Synchronous Magnetic Buck Regulators, I<sub>OUT</sub> 800 mA each:

- 2 regulators have DVS support

- High-efficiency ECO mode @ low I<sub>OUT</sub>

- Auto Mode ECO/PWM switch

- 28V OVP on the charger input

- 15 LDOs

- 10 General-type Low-Noise LDOs

8 x 300 mA

2 x 80 mA

- Three wide-input low-output (WILO) LDOs, all capable of supplying up to 300 mA

- 1 micro-power LDO with I<sub>OUT</sub> 30 mA

- 1 high-voltage USB LDO

- S/W controllable outputs

- Outputs configurable for pulldown

- Two Comparators and Two TCXO Buffers

- USB 2.0-compatible Transceiver (12 Mb/s)

- 12-bit A/D Converter for battery management and external monitoring

- Two over-voltage protected outputs for USB transceivers

- Real time clock with two alarms

- SIM card level translator

- Three controllable current sinks for Keypad LEDs

- Backup battery charger

- Thermal Shutdown with Early Warning Alarm

- Momentary Power Loss detection

- Interrupt Request to reduce S/W polling

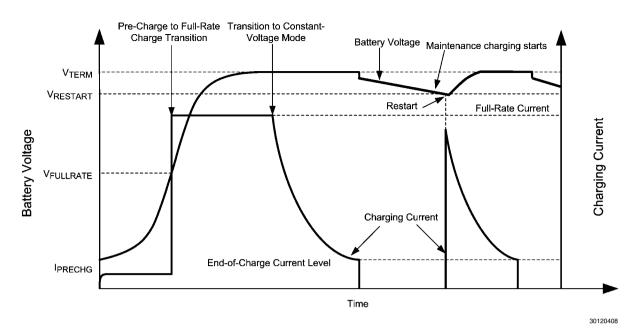

- 81-bump micro SMDxt package

# **Key Specifications**

- LOW PMU I<sub>O</sub> in sleep mode

- 50 mA to 1200 mA Charging Current from AC Adapter

- 3.0V to 4.5V Battery Voltage

- 150 mV typ. Dropout Voltage on LDOs @ 300 mA

- 2% typ. Output Voltage accuracy on LDOs

- ULTRA LOW NOISE (10 µV typ.), ULTRA LOW IQ, remote capacitor General-type "PERFECT" LDOs

- 3% accurate Buck regulators up to 90% efficient

# **Applications**

■ GSM. GPRS. EDGE. CDMA & 3G Handsets

# **Table of Contents**

| General Description                                  |      |

|------------------------------------------------------|------|

| Features                                             |      |

| Key Specifications                                   | 1    |

| Applications                                         |      |

| Typical Application Diagram                          | 4    |

| Pin Configuration                                    | 5    |

| Package Marking Information                          |      |

| Ordering Information                                 |      |

| Pin Descriptions                                     | /    |

| Absolute Maximum Ratings                             | 9    |

| Operating Ratings (Note 1, Note 2)                   | 9    |

| General Electrical Characteristics                   |      |

| Current Consumption                                  |      |

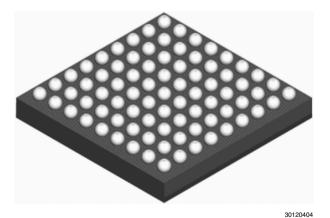

| Device Operating Modes                               | . 11 |

| Startup and Shutdown Sequences                       |      |

| Enable Control                                       |      |

| Multifunctional Pins                                 | . 14 |

| Single-Input Linear Charger with PMOS Routing Switch | . 15 |

| GENERAL CHARGER CONTROL                              | . 15 |

| CHARGER INPUT DETECTION AND LIMITS                   | . 15 |

| SYSTEM SUPPLY FUNCTION                               |      |

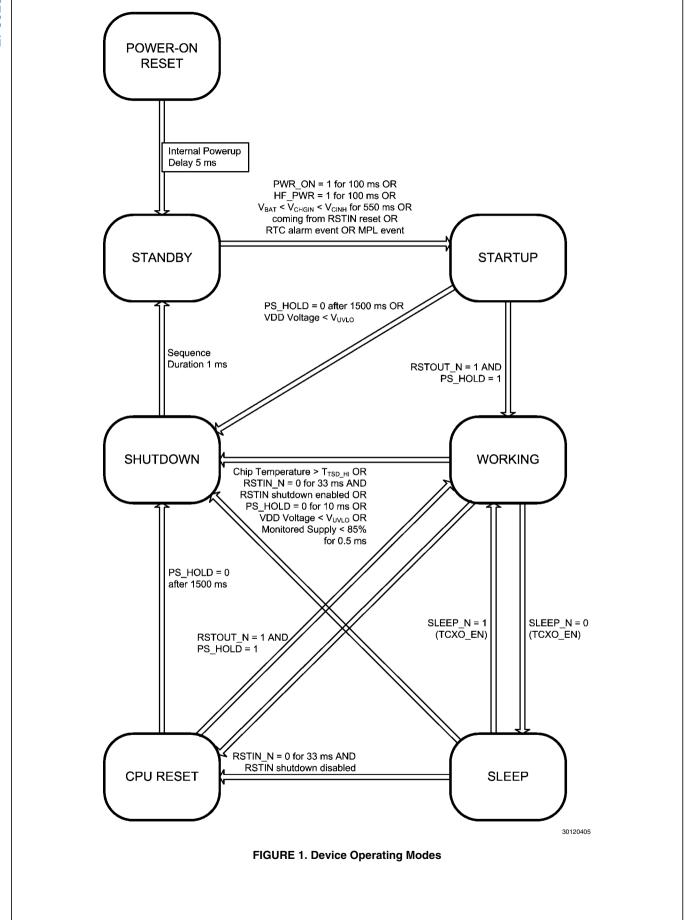

| BATTERY CHARGING FUNCTION                            |      |

| CC TO CV MODE TRANSITION                             | . 16 |

| END-OF-CHARGE AND RESTART                            |      |

| POWER ROUTING SWITCH                                 |      |

| OPERATION WITHOUT BATTERY                            | . 16 |

| HIGH-CURRENT MODE CHARGER ELECTRICAL CHARACTERISTICS | . 16 |

| CHARGER ELECTRICAL CHARACTERISTICS                   | . 21 |

| Buck Information BUCK CIRCUIT OPERATION              | . 22 |

|                                                      |      |

| PWM OPERATIONINTERNAL SYNCHRONOUS RECTIFICATION      | . 22 |

|                                                      |      |

| CURRENT LIMITINGECO MODE OPERATION                   |      |

| BUCK OUTPUT VOLTAGE SELECTION                        |      |

| EXTERNAL COMPONENT SELECTION                         | . 23 |

| DVS CONTROL                                          |      |

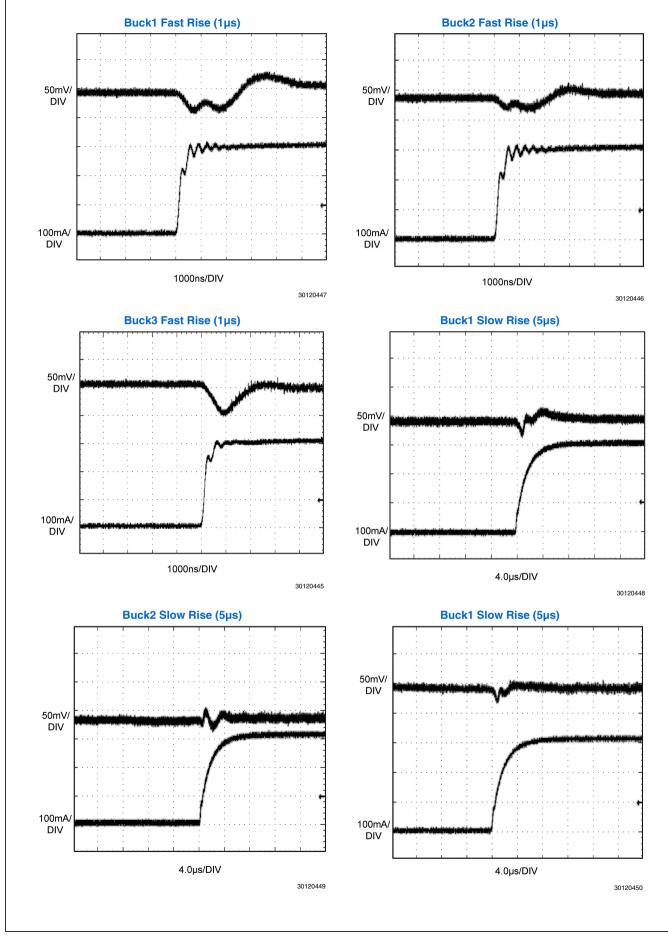

| BUCK TYPICAL PERFORMANCE PLOTS                       | . 24 |

| BUCK ELECTRICAL CHARACTERISTICS                      |      |

| LDO Information                                      |      |

| GENERAL-TYPE "PERFECT" LDOs                          |      |

| WILO-TYPE LDOs                                       |      |

| MICRO-PWR LDO                                        |      |

| USB LDO                                              |      |

| GENERAL LDO ELECTRICAL CHARACTERISTICS               |      |

| WILO-TYPE LDO ELECTRICAL CHARACTERISTICS             |      |

| MICRO-PWR LDO ELECTRICAL CHARACTERISTICS             |      |

| USB LDO ELECTRICAL CHARACTERISTICS                   | . 30 |

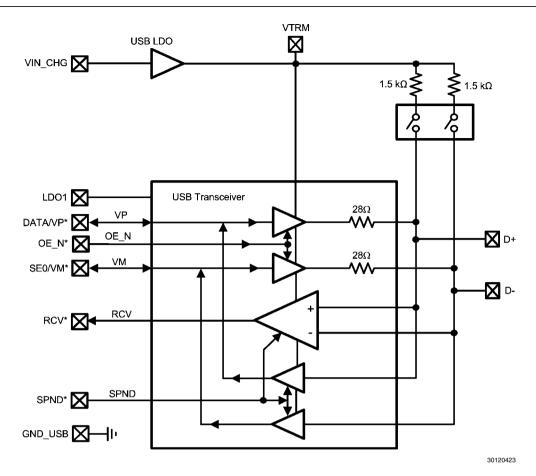

| USB Transceiver                                      |      |

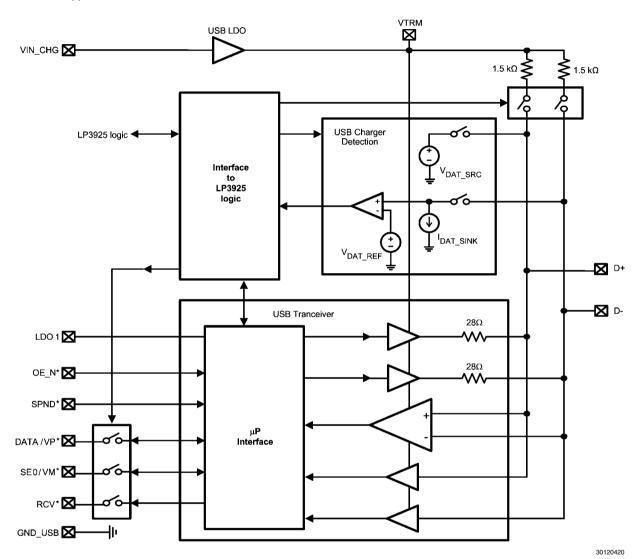

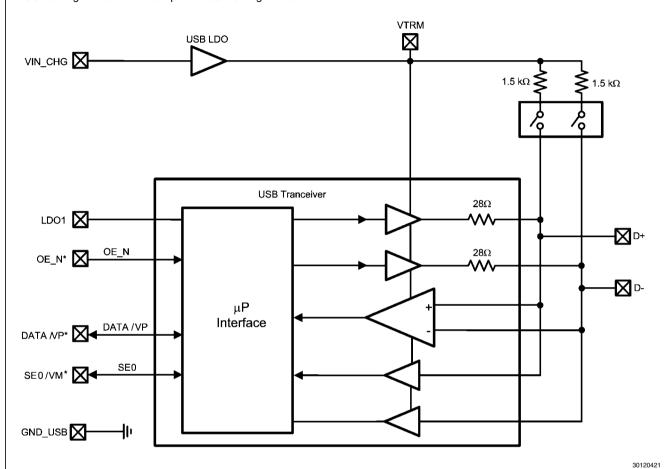

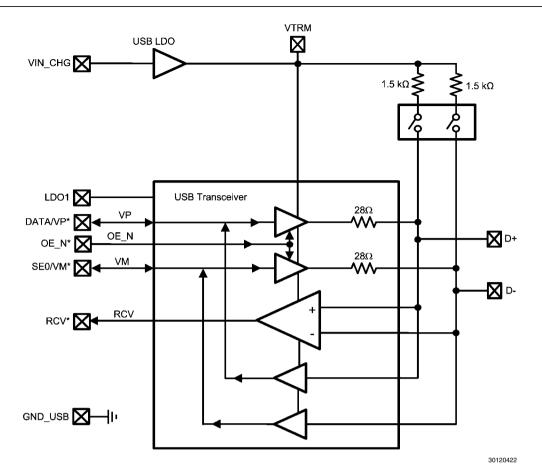

| USB TRANSCEIVER                                      |      |

| USB CHARGER DETECTION                                |      |

| USB CHARGER DETECTION ELECTRICAL CHARACTERISTICS     | 35   |

| USB TRANSCEIVER ELECTRICAL CHARACTERISTICS           |      |

| TCXO Buffers                                         |      |

| TCXO BUFFER ELECTRICAL CHARACTERISTICS               | 36   |

|                                                      |      |

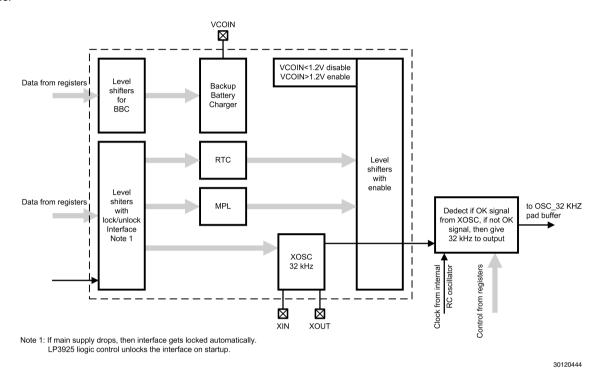

| Backup Battery Charger                               | . 37 |

| 32.768 kHz CRYSTAL OSCILLATOR                        | . 37 |

| BACKUP BATTERY CHARGER ELECTRICAL CHARACTERISTICS    | . 37 |

| Real Time Clock                                      |      |

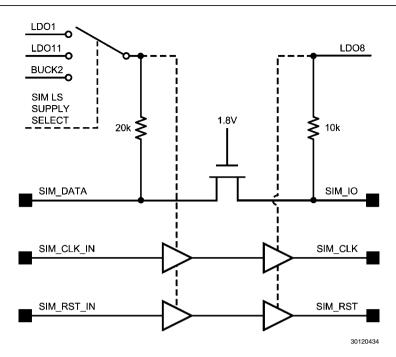

| USIM Interface                                       |      |

| USIM LEVEL TRANSLATOR ELECTRICAL CHARACTERISTICS     |      |

| FIGURE 21. SIM Interface Level Shifters              | . 40 |

| Comparators                                          |      |

|                                                      |      |

| COMPARATOR ELECTRICAL CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 40                                                                                                                               |

| A/D CONVERTER DATA AND CONTROL REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                  |

| BATTERY DISCHARGE CURRENT MEASUREMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                  |

| OTHER ITEM CURRENT VOLTAGE MEASUREMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                  |

| ADC ELECTRICAL CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 41                                                                                                                               |

| Reference Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 42                                                                                                                               |

| REFERENCE BUFFER ELECTRICAL CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 42                                                                                                                               |

| UVLO Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                  |

| Current Sinks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                  |

| Support Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                  |

| REFERENCE OSCILLATOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                  |

| THERMAL SHUTDOWN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                  |

| I2C-Compatible Serial Bus Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                  |

| INTERFACE BUS OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                  |

| DATA TRANSACTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                  |

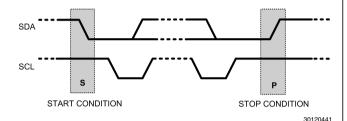

| START AND STOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 44                                                                                                                             |

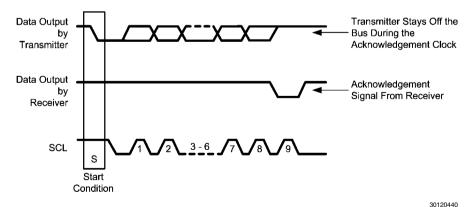

| ACKNOWLEDGE CYCLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                  |

| "ACKNOWLEDGE AFTER EVERY BYTE" RULE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 45                                                                                                                               |

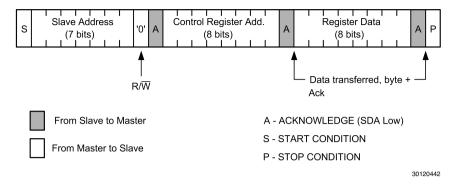

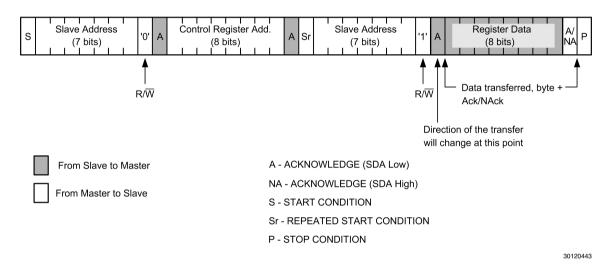

| ADDRESSING TRANSFER FORMATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 45                                                                                                                               |

| CONTROL REGISTER WRITE CYCLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 45                                                                                                                             |

| CONTROL REGISTER READ CYCLEREGISTER READ AND WRITE DETAIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                  |

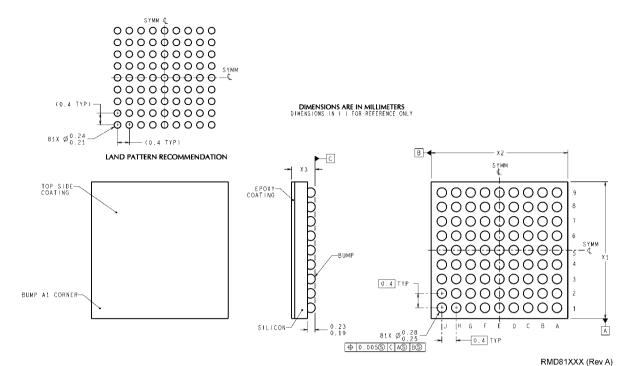

| Physical Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                  |

| Tryologi Dimonologi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 70                                                                                                                               |

| List of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                  |

| FIGURE 1. Device Operating Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                  |

| FIGURE 1. Device Operating Modes FIGURE 2. Startup and Shutdown Sequences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13                                                                                                                               |

| FIGURE 1. Device Operating Modes FIGURE 2. Startup and Shutdown Sequences FIGURE 3. Charging Cycle voltage and Current Plots                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13<br>17                                                                                                                         |

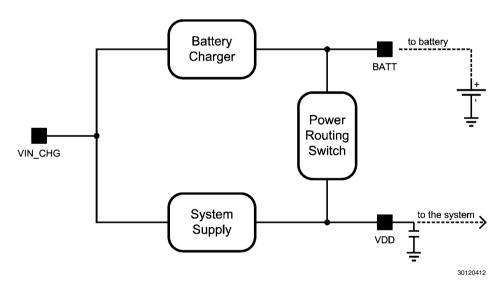

| FIGURE 1. Device Operating Modes FIGURE 2. Startup and Shutdown Sequences FIGURE 3. Charging Cycle voltage and Current Plots FIGURE 4. Charger Power Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13<br>17<br>17                                                                                                                   |

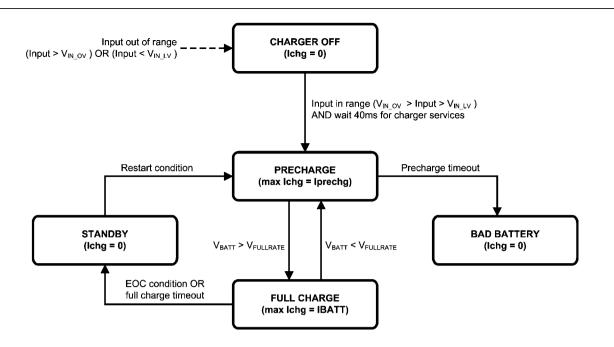

| FIGURE 1. Device Operating Modes FIGURE 2. Startup and Shutdown Sequences FIGURE 3. Charging Cycle voltage and Current Plots FIGURE 4. Charger Power Structure FIGURE 5. Charger Charging Cycle Operation Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13<br>17<br>17                                                                                                                   |

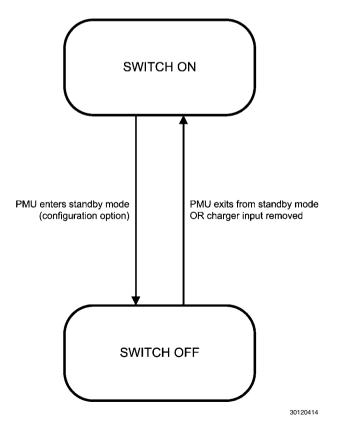

| FIGURE 1. Device Operating Modes FIGURE 2. Startup and Shutdown Sequences FIGURE 3. Charging Cycle voltage and Current Plots FIGURE 4. Charger Power Structure FIGURE 5. Charger Charging Cycle Operation Description FIGURE 6. Charger Internal Power Switch Operation Description When Charger is Off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 13<br>17<br>17<br>18                                                                                                             |

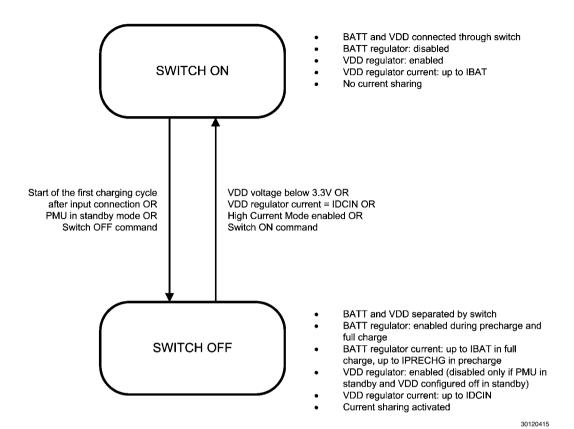

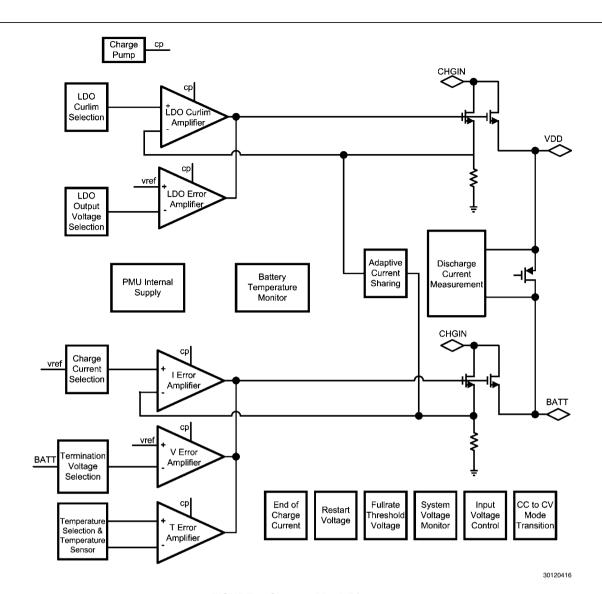

| FIGURE 1. Device Operating Modes FIGURE 2. Startup and Shutdown Sequences FIGURE 3. Charging Cycle voltage and Current Plots FIGURE 4. Charger Power Structure FIGURE 5. Charger Charging Cycle Operation Description FIGURE 6. Charger Internal Power Switch Operation Description When Charger is Off FIGURE 7. Charger Internal Power Switch Operation Description When Charger is On FIGURE 8. Charger Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13<br>17<br>17<br>18<br>18<br>19                                                                                                 |

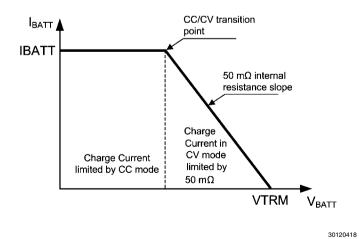

| FIGURE 1. Device Operating Modes FIGURE 2. Startup and Shutdown Sequences FIGURE 3. Charging Cycle voltage and Current Plots FIGURE 4. Charger Power Structure FIGURE 5. Charger Charging Cycle Operation Description FIGURE 6. Charger Internal Power Switch Operation Description When Charger is Off FIGURE 7. Charger Internal Power Switch Operation Description When Charger is On FIGURE 8. Charger Block Diagram FIGURE 9. Charger CC to CV Mode Transition Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13<br>17<br>17<br>18<br>18<br>19<br>20                                                                                           |

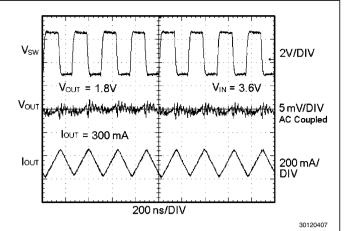

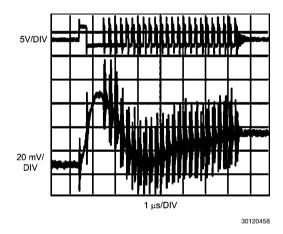

| FIGURE 1. Device Operating Modes FIGURE 2. Startup and Shutdown Sequences FIGURE 3. Charging Cycle voltage and Current Plots FIGURE 4. Charger Power Structure FIGURE 5. Charger Charging Cycle Operation Description FIGURE 6. Charger Internal Power Switch Operation Description When Charger is Off FIGURE 7. Charger Internal Power Switch Operation Description When Charger is On FIGURE 8. Charger Block Diagram FIGURE 9. Charger CC to CV Mode Transition Diagram FIGURE 10. Typical PWM Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13<br>17<br>17<br>18<br>18<br>19<br>20                                                                                           |

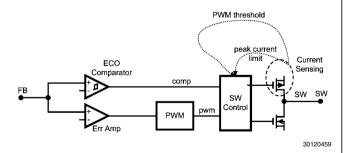

| FIGURE 1. Device Operating Modes FIGURE 2. Startup and Shutdown Sequences FIGURE 3. Charging Cycle voltage and Current Plots FIGURE 4. Charger Power Structure FIGURE 5. Charger Charging Cycle Operation Description FIGURE 6. Charger Internal Power Switch Operation Description When Charger is Off FIGURE 7. Charger Internal Power Switch Operation Description When Charger is On FIGURE 8. Charger Block Diagram FIGURE 9. Charger CC to CV Mode Transition Diagram FIGURE 10. Typical PWM Operation FIGURE 11. Typical ECO Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 13<br>17<br>17<br>18<br>18<br>19<br>20<br>20                                                                                     |

| FIGURE 1. Device Operating Modes FIGURE 2. Startup and Shutdown Sequences FIGURE 3. Charging Cycle voltage and Current Plots FIGURE 4. Charger Power Structure FIGURE 5. Charger Charging Cycle Operation Description FIGURE 6. Charger Internal Power Switch Operation Description When Charger is Off FIGURE 7. Charger Internal Power Switch Operation Description When Charger is On FIGURE 8. Charger Block Diagram FIGURE 9. Charger CC to CV Mode Transition Diagram FIGURE 10. Typical PWM Operation FIGURE 11. Typical ECO Operation FIGURE 12. Buck's Switches Controlling Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13<br>17<br>17<br>18<br>18<br>19<br>20<br>20<br>22<br>22                                                                         |

| FIGURE 1. Device Operating Modes FIGURE 2. Startup and Shutdown Sequences FIGURE 3. Charging Cycle voltage and Current Plots FIGURE 4. Charger Power Structure FIGURE 5. Charger Charging Cycle Operation Description FIGURE 6. Charger Internal Power Switch Operation Description When Charger is Off FIGURE 7. Charger Internal Power Switch Operation Description When Charger is On FIGURE 8. Charger Block Diagram FIGURE 9. Charger CC to CV Mode Transition Diagram FIGURE 10. Typical PWM Operation FIGURE 11. Typical ECO Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 13<br>17<br>17<br>18<br>19<br>20<br>20<br>22<br>22<br>23                                                                         |

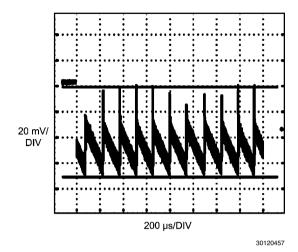

| FIGURE 1. Device Operating Modes FIGURE 2. Startup and Shutdown Sequences FIGURE 3. Charging Cycle voltage and Current Plots FIGURE 4. Charger Power Structure FIGURE 5. Charger Charging Cycle Operation Description FIGURE 6. Charger Internal Power Switch Operation Description When Charger is Off FIGURE 7. Charger Internal Power Switch Operation Description When Charger is On FIGURE 8. Charger Block Diagram FIGURE 9. Charger CC to CV Mode Transition Diagram FIGURE 10. Typical PWM Operation FIGURE 11. Typical ECO Operation FIGURE 12. Buck's Switches Controlling Diagram FIGURE 13. Typical ECO Operation FIGURE 14. Typical Ripple in ECO Mode FIGURE 15. USB Transceiver Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13<br>17<br>17<br>18<br>18<br>19<br>20<br>20<br>22<br>23<br>23<br>23                                                             |

| FIGURE 1. Device Operating Modes FIGURE 2. Startup and Shutdown Sequences FIGURE 3. Charging Cycle voltage and Current Plots FIGURE 4. Charger Power Structure FIGURE 5. Charger Charging Cycle Operation Description FIGURE 6. Charger Internal Power Switch Operation Description When Charger is Off FIGURE 7. Charger Internal Power Switch Operation Description When Charger is On FIGURE 8. Charger Block Diagram FIGURE 9. Charger CC to CV Mode Transition Diagram FIGURE 10. Typical PWM Operation FIGURE 11. Typical ECO Operation FIGURE 12. Buck's Switches Controlling Diagram FIGURE 13. Typical ECO Operation FIGURE 14. Typical Ripple in ECO Mode FIGURE 15. USB Transceiver Block Diagram FIGURE 16. USB Transceiver Configured to 3-Pin Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13<br>17<br>17<br>18<br>18<br>19<br>20<br>20<br>22<br>22<br>23<br>23<br>31                                                       |

| FIGURE 1. Device Operating Modes FIGURE 2. Startup and Shutdown Sequences FIGURE 3. Charging Cycle voltage and Current Plots FIGURE 4. Charger Power Structure FIGURE 5. Charger Charging Cycle Operation Description FIGURE 6. Charger Internal Power Switch Operation Description When Charger is Off FIGURE 7. Charger Internal Power Switch Operation Description When Charger is On FIGURE 8. Charger Block Diagram FIGURE 9. Charger CC to CV Mode Transition Diagram FIGURE 10. Typical PWM Operation FIGURE 11. Typical ECO Operation FIGURE 12. Buck's Switches Controlling Diagram FIGURE 13. Typical ECO Operation FIGURE 14. Typical Ripple in ECO Mode FIGURE 15. USB Transceiver Block Diagram FIGURE 16. USB Transceiver Configured to 3-Pin Interface FIGURE 17. USB Transceiver Configured to 4-Pin Interface                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13<br>17<br>17<br>18<br>19<br>20<br>20<br>22<br>23<br>23<br>23<br>31                                                             |

| FIGURE 1. Device Operating Modes FIGURE 2. Startup and Shutdown Sequences FIGURE 3. Charging Cycle voltage and Current Plots FIGURE 4. Charger Power Structure FIGURE 5. Charger Charging Cycle Operation Description FIGURE 6. Charger Internal Power Switch Operation Description When Charger is Off FIGURE 7. Charger Internal Power Switch Operation Description When Charger is On FIGURE 8. Charger Block Diagram FIGURE 9. Charger CC to CV Mode Transition Diagram FIGURE 10. Typical PWM Operation FIGURE 11. Typical ECO Operation FIGURE 12. Buck's Switches Controlling Diagram FIGURE 13. Typical ECO Operation FIGURE 14. Typical Ripple in ECO Mode FIGURE 15. USB Transceiver Block Diagram FIGURE 16. USB Transceiver Configured to 3-Pin Interface FIGURE 17. USB Transceiver Configured to 4-Pin Interface FIGURE 18. USB Transceiver Configured to 5-Pin Interface                                                                                                                                                                                                                                                                                                                                                                                 | 13<br>17<br>17<br>18<br>19<br>20<br>20<br>22<br>23<br>23<br>23<br>31                                                             |

| FIGURE 1. Device Operating Modes FIGURE 2. Startup and Shutdown Sequences FIGURE 3. Charging Cycle voltage and Current Plots FIGURE 4. Charger Power Structure FIGURE 5. Charger Charging Cycle Operation Description FIGURE 6. Charger Internal Power Switch Operation Description When Charger is Off FIGURE 7. Charger Internal Power Switch Operation Description When Charger is On FIGURE 8. Charger Block Diagram FIGURE 9. Charger CC to CV Mode Transition Diagram FIGURE 10. Typical PWM Operation FIGURE 11. Typical ECO Operation FIGURE 12. Buck's Switches Controlling Diagram FIGURE 13. Typical ECO Operation FIGURE 14. Typical Ripple in ECO Mode FIGURE 15. USB Transceiver Block Diagram FIGURE 16. USB Transceiver Configured to 3-Pin Interface FIGURE 17. USB Transceiver Configured to 4-Pin Interface                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13<br>17<br>17<br>18<br>19<br>20<br>20<br>22<br>23<br>23<br>23<br>31<br>32<br>33                                                 |

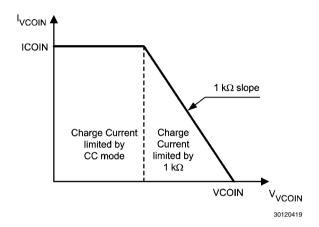

| FIGURE 1. Device Operating Modes FIGURE 2. Startup and Shutdown Sequences FIGURE 3. Charging Cycle voltage and Current Plots FIGURE 4. Charger Power Structure FIGURE 5. Charger Charging Cycle Operation Description FIGURE 6. Charger Internal Power Switch Operation Description When Charger is Off FIGURE 7. Charger Internal Power Switch Operation Description When Charger is On FIGURE 8. Charger Block Diagram FIGURE 9. Charger CC to CV Mode Transition Diagram FIGURE 10. Typical PWM Operation FIGURE 11. Typical ECO Operation FIGURE 12. Buck's Switches Controlling Diagram FIGURE 13. Typical ECO Operation FIGURE 14. Typical Fipple in ECO Mode FIGURE 15. USB Transceiver Block Diagram FIGURE 16. USB Transceiver Configured to 3-Pin Interface FIGURE 17. USB Transceiver Configured to 4-Pin Interface FIGURE 18. USB Transceiver Configured to 5-Pin Interface FIGURE 19. BBC IU Characteristics FIGURE 20. RTC Functional Block Diagram FIGURE 21. SIM Interface Level Shifters                                                                                                                                                                                                                                                               | 13<br>17<br>17<br>18<br>18<br>19<br>20<br>20<br>22<br>23<br>23<br>23<br>31<br>32<br>33<br>34<br>37                               |

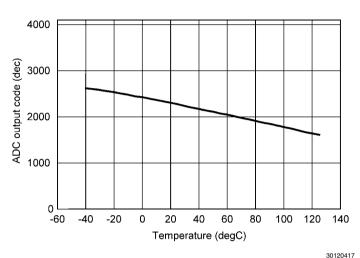

| FIGURE 1. Device Operating Modes FIGURE 2. Startup and Shutdown Sequences FIGURE 3. Charging Cycle voltage and Current Plots FIGURE 4. Charger Power Structure FIGURE 5. Charger Charging Cycle Operation Description FIGURE 6. Charger Internal Power Switch Operation Description When Charger is Off FIGURE 7. Charger Internal Power Switch Operation Description When Charger is On FIGURE 8. Charger Block Diagram FIGURE 9. Charger CC to CV Mode Transition Diagram FIGURE 10. Typical PWM Operation FIGURE 11. Typical ECO Operation FIGURE 12. Buck's Switches Controlling Diagram FIGURE 13. Typical ECO Operation FIGURE 14. Typical Ripple in ECO Mode FIGURE 15. USB Transceiver Block Diagram FIGURE 16. USB Transceiver Configured to 3-Pin Interface FIGURE 17. USB Transceiver Configured to 4-Pin Interface FIGURE 18. USB Transceiver Configured to 5-Pin Interface FIGURE 19. BBC IU Characteristics FIGURE 21. SIM Interface Level Shifters FIGURE 21. SIM Interface Level Shifters FIGURE 22. LP3925 ADC Temperature Range                                                                                                                                                                                                                       | 13<br>17<br>17<br>18<br>18<br>19<br>20<br>22<br>22<br>23<br>23<br>31<br>32<br>33<br>34<br>37<br>38<br>40                         |

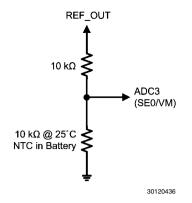

| FIGURE 1. Device Operating Modes FIGURE 2. Startup and Shutdown Sequences FIGURE 3. Charging Cycle voltage and Current Plots FIGURE 4. Charger Power Structure FIGURE 5. Charger Charging Cycle Operation Description FIGURE 6. Charger Internal Power Switch Operation Description When Charger is Off FIGURE 7. Charger Internal Power Switch Operation Description When Charger is On FIGURE 8. Charger Block Diagram FIGURE 9. Charger CC to CV Mode Transition Diagram FIGURE 10. Typical PWM Operation FIGURE 11. Typical ECO Operation FIGURE 11. Typical ECO Operation FIGURE 12. Buck's Switches Controlling Diagram FIGURE 13. Typical ECO Operation FIGURE 14. Typical Ripple in ECO Mode FIGURE 15. USB Transceiver Block Diagram FIGURE 16. USB Transceiver Configured to 3-Pin Interface FIGURE 17. USB Transceiver Configured to 4-Pin Interface FIGURE 18. USB Transceiver Configured to 5-Pin Interface FIGURE 19. BBC IU Characteristics FIGURE 20. RTC Functional Block Diagram FIGURE 21. SIM Interface Level Shifters FIGURE 22. LP3925 ADC Temperature Range FIGURE 23. Typical REF_OUT BatteryTemperature MeasurementApplication Diagram                                                                                                         | 13<br>17<br>17<br>18<br>18<br>19<br>20<br>22<br>23<br>23<br>23<br>31<br>32<br>33<br>34<br>37<br>38<br>40                         |

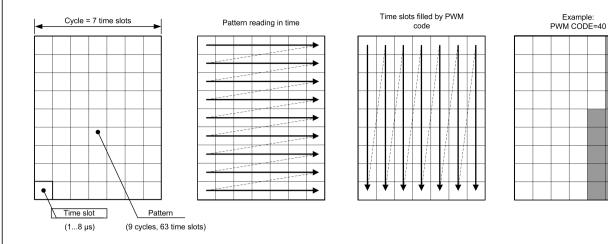

| FIGURE 1. Device Operating Modes FIGURE 2. Startup and Shutdown Sequences FIGURE 3. Charging Cycle voltage and Current Plots FIGURE 4. Charger Power Structure FIGURE 5. Charger Charging Cycle Operation Description FIGURE 6. Charger Internal Power Switch Operation Description When Charger is Off FIGURE 7. Charger Internal Power Switch Operation Description When Charger is On FIGURE 8. Charger Block Diagram FIGURE 9. Charger CC to CV Mode Transition Diagram FIGURE 10. Typical PWM Operation FIGURE 10. Typical ECO Operation FIGURE 11. Typical ECO Operation FIGURE 12. Buck's Switches Controlling Diagram FIGURE 13. Typical ECO Operation FIGURE 14. Typical Ripple in ECO Mode FIGURE 15. USB Transceiver Block Diagram FIGURE 16. USB Transceiver Configured to 3-Pin Interface FIGURE 17. USB Transceiver Configured to 4-Pin Interface FIGURE 19. BBC IU Characteristics FIGURE 20. RTC Functional Block Diagram FIGURE 21. SIM Interface Level Shifters FIGURE 22. LP3925 ADC Temperature Range FIGURE 23. Typical REF_OUT BatteryTemperature MeasurementApplication Diagram FIGURE 24. Current Sinks PWM Control                                                                                                                             | 13<br>17<br>17<br>18<br>18<br>19<br>20<br>22<br>22<br>23<br>23<br>31<br>32<br>33<br>34<br>37<br>38<br>40<br>41<br>42             |

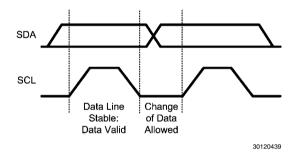

| FIGURE 1. Device Operating Modes FIGURE 2. Startup and Shutdown Sequences FIGURE 3. Charging Cycle voltage and Current Plots FIGURE 4. Charger Power Structure FIGURE 5. Charger Charging Cycle Operation Description FIGURE 6. Charger Internal Power Switch Operation Description When Charger is Off FIGURE 7. Charger Internal Power Switch Operation Description When Charger is On FIGURE 8. Charger Block Diagram FIGURE 9. Charger Ct to CV Mode Transition Diagram FIGURE 10. Typical PWM Operation FIGURE 11. Typical ECO Operation FIGURE 12. Buck's Switches Controlling Diagram FIGURE 13. Typical ECO Operation FIGURE 14. Typical ECO Operation FIGURE 14. Typical Ripple in ECO Mode FIGURE 16. USB Transceiver Block Diagram FIGURE 17. USB Transceiver Configured to 3-Pin Interface FIGURE 18. USB Transceiver Configured to 4-Pin Interface FIGURE 19. USB Transceiver Configured to 5-Pin Interface FIGURE 19. USB Transceiver Configured to 5-Pin Interface FIGURE 19. USB Transceiver Configured to 5-Pin Interface FIGURE 19. SIM Interface Level Shifters FIGURE 20. RTC Functional Block Diagram FIGURE 21. SIM Interface Level Shifters FIGURE 22. LP3925 ADC Temperature Range FIGURE 24. Current Sinks PWM Control FIGURE 25. Bit Transfer | 13<br>17<br>17<br>18<br>18<br>19<br>20<br>22<br>23<br>23<br>23<br>31<br>32<br>33<br>34<br>37<br>38<br>40<br>41<br>42<br>43       |

| FIGURE 1. Device Operating Modes FIGURE 2. Startup and Shutdown Sequences FIGURE 3. Charging Cycle voltage and Current Plots FIGURE 4. Charger Power Structure FIGURE 5. Charger Charging Cycle Operation Description FIGURE 6. Charger Internal Power Switch Operation Description When Charger is Off FIGURE 7. Charger Internal Power Switch Operation Description When Charger is On FIGURE 8. Charger Block Diagram FIGURE 9. Charger CC to CV Mode Transition Diagram FIGURE 10. Typical PWM Operation FIGURE 10. Typical ECO Operation FIGURE 11. Typical ECO Operation FIGURE 12. Buck's Switches Controlling Diagram FIGURE 13. Typical ECO Operation FIGURE 14. Typical Ripple in ECO Mode FIGURE 15. USB Transceiver Block Diagram FIGURE 16. USB Transceiver Configured to 3-Pin Interface FIGURE 17. USB Transceiver Configured to 4-Pin Interface FIGURE 19. BBC IU Characteristics FIGURE 20. RTC Functional Block Diagram FIGURE 21. SIM Interface Level Shifters FIGURE 22. LP3925 ADC Temperature Range FIGURE 23. Typical REF_OUT BatteryTemperature MeasurementApplication Diagram FIGURE 24. Current Sinks PWM Control                                                                                                                             | 13<br>17<br>17<br>18<br>18<br>19<br>20<br>22<br>23<br>23<br>31<br>32<br>33<br>34<br>37<br>38<br>40<br>41<br>42<br>44             |

| FIGURE 1. Device Operating Modes FIGURE 2. Startup and Shutdown Sequences FIGURE 3. Charging Cycle voltage and Current Plots FIGURE 4. Charger Power Structure FIGURE 5. Charger Charging Cycle Operation Description FIGURE 6. Charger Internal Power Switch Operation Description When Charger is Off FIGURE 7. Charger Internal Power Switch Operation Description When Charger is On FIGURE 8. Charger Block Diagram FIGURE 9. Charger Ct to CV Mode Transition Diagram FIGURE 10. Typical PWM Operation FIGURE 11. Typical ECO Operation FIGURE 11. Typical ECO Operation FIGURE 13. Typical ECO Operation FIGURE 14. Typical ECO Operation FIGURE 15. USB Transceiver Block Diagram FIGURE 16. USB Transceiver Configured to 3-Pin Interface FIGURE 17. USB Transceiver Configured to 4-Pin Interface FIGURE 19. BBC IU Characteristics FIGURE 20. RTC Functional Block Diagram FIGURE 21. SIM Interface Level Shifters FIGURE 22. LP3925 ADC Temperature Range FIGURE 23. Typical REF_OUT BatteryTemperature MeasurementApplication Diagram FIGURE 25. Bit Transfer FIGURE 26. Start and Stop Conditions                                                                                                                                                         | 13<br>17<br>17<br>18<br>18<br>19<br>20<br>22<br>23<br>23<br>23<br>31<br>32<br>33<br>34<br>37<br>38<br>40<br>41<br>42<br>44<br>44 |

#### **Typical Application Diagram** V<sub>DD</sub> RSENSE\* 9 ŢΨ. Fsw ADC LDO2 埴 LDO3 LDO3 Charger General LDOs USB LDO LDO5 LDO5 28 OVP LDO6 **LP3925** 10( LDO1 LD07 SE0/VM\* LDO8 LD08 USB µPWR LDO RCV\* LDO10 SPND<sup>3</sup> LDO11 LDOs 32 kHz OSC LDO12 VCOIN 3 WILO LDO13 Backup WILO3 Battery RTC Charger T T µF OSC\_32KHZ MPL 1.5 kΩ **≤** 1.5 kΩ **P**LDO1 RSTOUT\_N M RSTIN\_N TCXO1\_I\* TCX01\_0\* SLEEP\_N (TCXO\_EN) Serial Interface 2TCXO TCXO2\_I\* and Buffers Control TCXO2\_O\* PWR\_ON HF PWR REF\_OUT SIM\_DATA\* VIN\_B1 SIM\_RST\_IN 12bit SIM\_CLK\_IN **USIM** Level ADC 1 μΗ Shifter SIM\_IO\* SIM\_RST SIM card 12 Input MUX SIM CLK 3 Bucks 1 μH \_**^^^**SW\_B2 Thermal INP2\* Shutdown 2 Comparators INP1 Reference SINK3\* Voltage SINK2\* 3 Current Sinks Oscillator SINK1\* GND\_B2 GND\_SINK 30120401

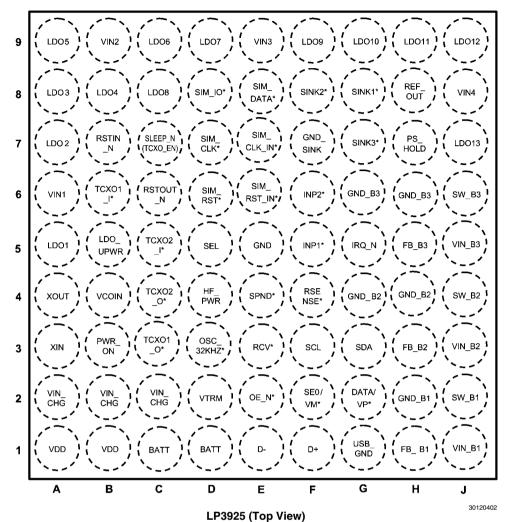

# **Pin Configuration**

\* Pins that can be programmed as analog pins (default as stated in pin configuration) or digital input/output pins. Pins that are used for USB transceiver interfacing are chosen in

accordance of the interface used, either 3-wire or 5-wire. All these pins except SINK1, 2, 3 and INP1, 2 can be used as ADC inputs.

5

# **Package Marking Information**

XY = 2-Digit Date Code TT = 2-Digit Die RunTrace Code LP3925 = Product Identification

⇒ Pin A1

30120403

# **Ordering Information**

| Order Number     | Product Identification | Supplied as      |

|------------------|------------------------|------------------|

| LP3925RME/NOPB   | 3925                   | 250 Tape & Reel  |

| LP3925RMX/NOPB   | 3925                   | 1000 Tape & Reel |

| LP3925RME-A/NOPB | V030                   | 250 Tape & Reel  |

| LP3925RMX-A/NOPB | V030                   | 1000 Tape & Reel |

| LP3925RME-E/NOPB | V030                   | 250 Tape & Reel  |

| LP3925RMX-E/NOPB | V030                   | 1000 Tape & Reel |

# **Pin Descriptions**