#### FEATURES AND BENEFITS

- Contactless 0° to 360° angle sensor IC, for angular position and rotation direction measurement

- ☐ Circular Vertical Hall (CVH) technology provides a single-channel sensor system, with air gap independence

- 12-bit resolution possible in Low RPM mode, 10-bit resolution in High RPM mode

- Angle Refresh Rate (output rate) configurable between 25 and 3200 μs through EEPROM programming

- □ Capable of sensing magnetic rotational speeds up to 7600 rpm, and up to 30,000 rpm with reduced accuracy

Continued on the next page...

### **PACKAGES:**

14-pin TSSOP (Suffix LE)

Single SoC

#### DESCRIPTION

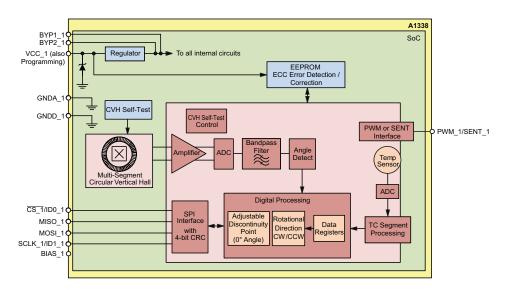

The A1338 is a 0° to 360° angle sensor IC that provides contactless high-resolution angular position information based on magnetic circular vertical Hall (CVH) technology. It has a system-on-chip (SoC) architecture that includes: a CVH front end, digital signal processing, digital SPI, and SENT or PWM outputs. It also includes on-chip EEPROM technology, capable of supporting up to 100 read/write cycles, for flexible end of line programming of calibration and configuration parameters. The A1338 is ideal for automotive applications requiring 0° to 360° angle measurements, such as electronic power steering (EPS), seatbelt motor position systems, rotary PRNDLs, and throttle systems.

The A1338 was designed with safety-critical application requirements in mind. It includes user-controlled on-chip logic built-in self-test (LBIST) and full signal path diagnostics to enable customers to determine if the IC is operating in a proper manner.

The A1338 supports a Low RPM mode for slower rate applications and a High RPM mode for high-speed applications. High RPM mode is for applications that require higher refresh rates to minimize error due to latency. Low RPM mode is for applications that require higher resolution operating at lower angular velocities.

Continued on the next page...

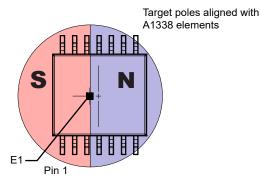

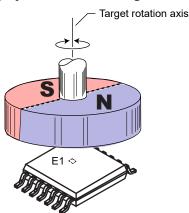

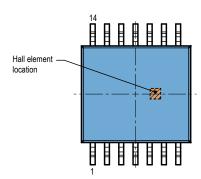

Figure 1: A1338 Magnetic Circuit and IC Diagram

## A1338

# Precision, Hall-Effect Angle Sensor IC with SPI, and SENT or PWM Outputs

#### **FEATURES AND BENEFITS (continued)**

- SPI (mode 3), and SENT (Single Edge Nibble Transmission) or PWM (Pulse-Width Modulation)\*

- □ SPI interface provides a robust communication protocol for fast angle readings\*

- □ SENT output supports four modes: SAEJ2716 (JAN2010) and Allegro proprietary options of Triggered SENT (TSENT), Sequential SENT (SSENT), and Addressable SENT (ASENT)\*

- □ Programmable via Manchester Encoding on the VCC line, reducing external wiring\*

- ☐ SPI and SENT interfaces allows use of multiple independent sensors for applications requiring redundancy\*

- Advanced diagnostics to support safety-critical applications, including:

- □ On-chip, user-controlled logic built-in self-test (LBIST) and signal path diagnostics

- □ 4-bit CRC on SPI messages

- ☐ User-Programmable Missing Magnet Error flag for notifying controller of low magnetic field level

- Diagnostics are initiated over the SPI or SENT interface and can directly test proper operation of the IC in safety-critical applications

- EEPROM with Error Correction Control (ECC) configuration, sensor calibration including end-of line adjustments like programmable angle reference (0°) position and rotation direction (CW or CCW)

- Absolute maximum V<sub>CC</sub> of 26.5 V for increased robustness and direct connection to automotive vehicle battery

#### **DESCRIPTION** (continued)

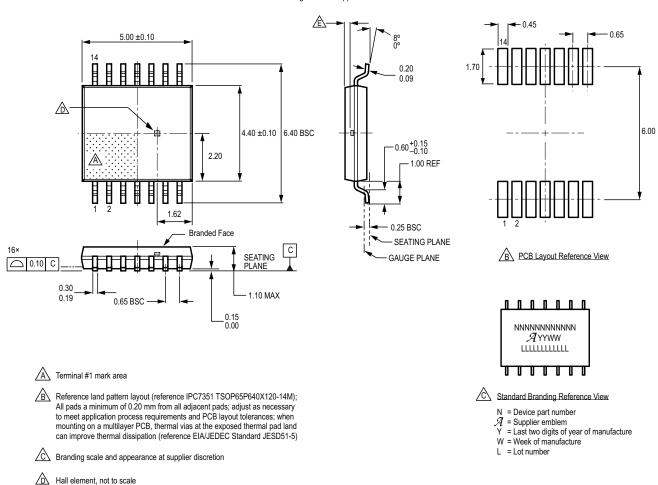

The A1338 is available in a single-die 14-pin TSSOP package. The package is lead (Pb) free with 100% matte-tin leadframe plating.

#### **SELECTION GUIDE**

| Part Number    | System Die | Output Protocols | Package      | Packing <sup>[1]</sup>      |

|----------------|------------|------------------|--------------|-----------------------------|

| A1338LLETR-T   | Single     | SPI and SENT     | 14-pin TSSOP | 4000 pieces per 13-in. reel |

| A1338LLETR-P-T | Single     | SPI and PWM      | 14-pin TSSOP | 4000 pieces per 13-in. reel |

<sup>&</sup>lt;sup>[1]</sup> Contact Allegro<sup>™</sup> for additional packaging options.

<sup>\*</sup> See Selection Guide for more details.

# A1338

# Precision, Hall-Effect Angle Sensor IC with SPI, and SENT or PWM Outputs

### **Table of Contents**

| Features and Benefits                 | 1  | PWM Output ("-P" option)                   | 12             |

|---------------------------------------|----|--------------------------------------------|----------------|

| Description                           | 1  | Error Reporting in PWM                     | 12             |

| Packages                              | 1  | Manchester Serial Interface                | 13             |

| A1338 Magnetic Circuit and IC Diagram | 1  | Entering Manchester Communication Mode     | 13             |

| Selection Guide                       |    | Transaction Types                          | 13             |

| Specifications                        | 3  | Writing to EEPROM                          | 13             |

| Absolute Maximum Ratings              |    | Manchester Interface Reference             | 14             |

| Thermal Characteristics               |    | SENT Output Mode                           | 1              |

| Typical Application Diagram           | 4  | Diagnostics                                | 18             |

| Pinout Diagrams and Terminal List     |    | Serial Interface Structure                 |                |

| Functional Block Diagram              |    | Application Information                    | 2              |

| Operating Characteristics             | 7  | Serial Interface Description               | 2              |

| Functional Description                |    | Calculating Target Zero-Degree Angle       | 2              |

| Overview                              | 10 | Bypass Pins Usage                          | 2              |

| Angle Measurement                     | 10 | Changing Sampling Modes                    | 20             |

| Impact of High-Speed Sensing          | 10 | Magnetic Target Requirements               | 20             |

| Angle Resolution and Representation   | 11 | Redundant Applications and Alignment Error | 2              |

| Programming Modes                     |    | System Timing and Error                    | 2              |

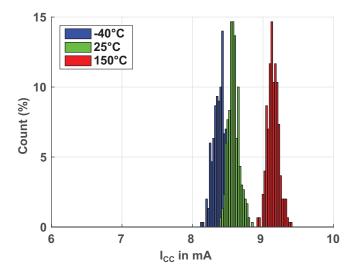

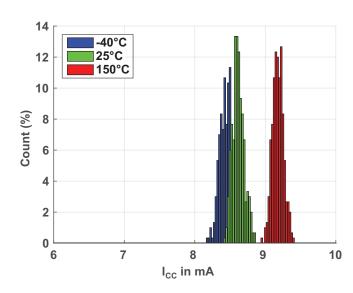

| SPI System-Level Timing               | 12 | Characteristic Performance Data            | 28             |

| Power-Up                              |    | EMC Reduction                              | 30             |

| ·                                     |    | Package Outline Drawings                   | 3 <sup>.</sup> |

#### **ABSOLUTE MAXIMUM RATINGS**

| Characteristic                 | Symbol               | Notes               | Rating     | Unit |

|--------------------------------|----------------------|---------------------|------------|------|

| Forward Supply Voltage         | V <sub>CC</sub>      | Not sampling angles | 26.5       | V    |

| Reverse Supply Voltage         | V <sub>RCC</sub>     | Not sampling angles | -18        | V    |

| All Other Pins Forward Voltage | V <sub>IN</sub>      |                     | 5.5        | V    |

| All Other Pins Reverse Voltage | V <sub>R</sub>       |                     | 0.5        | V    |

| Operating Ambient Temperature  | T <sub>A</sub>       | L range             | -40 to 150 | °C   |

| Maximum Junction Temperature   | T <sub>J</sub> (max) |                     | 165        | °C   |

| Storage Temperature            | T <sub>stg</sub>     |                     | -65 to 170 | °C   |

### THERMAL CHARACTERISTICS: May require derating at maximum conditions; see application information

| Characteristic             | Symbol          | Test Conditions [1] | Value | Unit |

|----------------------------|-----------------|---------------------|-------|------|

| Package Thermal Resistance | $R_{\theta JA}$ | LE-14 package       | 82    | °C/W |

<sup>[1]</sup> Additional thermal information available on the Allegro website.

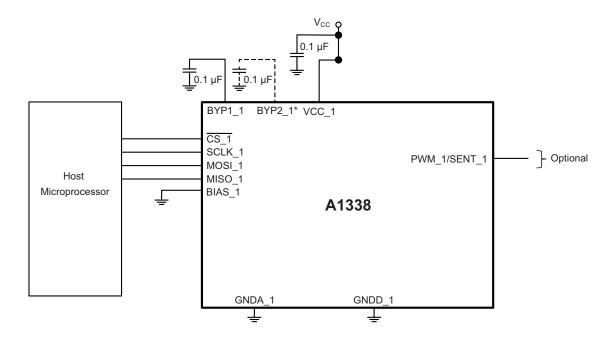

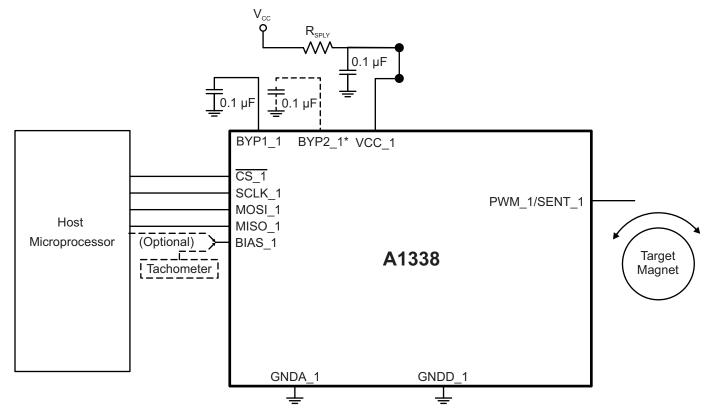

Figure 2: Typical A1338 Configuration Using SPI Interface

(See "EMC Reduction" Section for application circuits that require a higher level of EMC immunity.)

\* Secondary bypass capacitors only required when using Elevated SPI Output Voltage. Contact Allegro for availability.

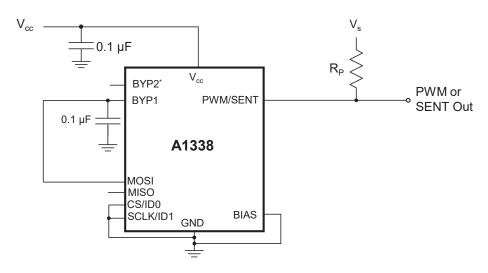

Figure 3: Typical A1338 Configuration Using PWM or SENT Output. ID Value of 002.

ID0/ID1 brought to BYP or GND to configure Manchester address. When configuring an IC for address 002, MOSI should be tied to BYP.

\* Secondary bypass capacitors only required when using Elevated SPI Output Voltage. Contact Allegro for availability.

### PINOUT DIAGRAMS AND TERMINAL LIST

| BYP1_1 1       | 0 | 14 GNDD_1       |

|----------------|---|-----------------|

| GNDD_1 2       |   | 13 CS_1/ID0_1   |

| GNDA_1 3       |   | 12 MOSI_1       |

| SENT_1/PWM_1 4 |   | 11 SCLK_1/ID1_1 |

| VCC_1 5        |   | 10 MISO_1       |

| NC 6           |   | 9 BYP2_1        |

| NC 7           |   | 8 BIAS_1        |

### 14-Pin TSSOP LE Package Pinouts

### **Terminal List Table**

| Pin Name     | Pin Number | Function                                                                                |

|--------------|------------|-----------------------------------------------------------------------------------------|

| BYP1_1       | 1          | External Bypass Capacitor Terminal for Internal Regulator                               |

| BYP2_1       | 9          | External Bypass Capacitor Terminal for Internal Regulator                               |

| CS 1/ID0 1   | 13         | Option 1: SPI Chip Select Terminal, Active Low Input                                    |

| C3_17ID0_1   | 13         | Option 2: ID0 bit to indicate Slave Address for SSENT or ASENT communication modes only |

| GNDA_1       | 3          | Device Analog Ground Terminal                                                           |

| GNDD_1       | 2, 14      | Device Digital Ground Terminal                                                          |

| MISO_1       | 10         | SPI Master Input/Slave Output                                                           |

| MOSI_1       | 12         | SPI Master Output Slave Input                                                           |

| SLCK 1/ID1 1 | 11         | Option 1: SPI Clock Terminal                                                            |

| SLOK_I/ID1_I | 11         | Option 2: ID1 bit to indicate Slave Address for SSENT or ASENT communication modes only |

| SENT_1/PWM_1 | 4          | SENT Output; PWM Output; SENT for A1338LLETR-T; PWM for A1338LLETR-P-T                  |

| BIAS_1       | 8          | Bias Connection; connect to ground or pull up to 3.3 V                                  |

| VCC_1        | 5          | Power Supply; also used for EEPROM Programming                                          |

| NC           | 6, 7       | Not internally connected; tie to GNDD                                                   |

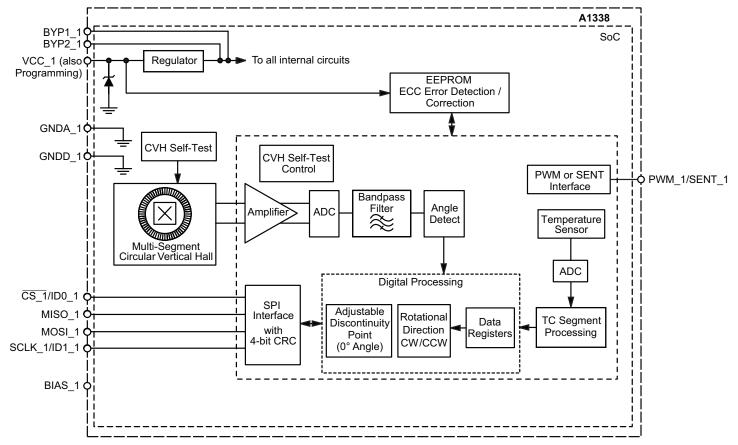

Figure 4: Functional Block Diagram

# A1338

# Precision, Hall-Effect Angle Sensor IC with SPI, and SENT or PWM Outputs

## OPERATING CHARACTERISTICS: Valid over the full operating voltage and ambient temperature ranges, unless otherwise noted

| Characteristics Symb                                                 |                      | Test Conditions                                                                                        |      | Typ. [1] | Max. | Unit <sup>[2]</sup> |

|----------------------------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------|------|----------|------|---------------------|

| ELECTRICAL CHARACTERISTICS                                           |                      |                                                                                                        | '    |          |      |                     |

| Supply Voltage                                                       | V <sub>CC</sub>      |                                                                                                        | 3.7  | _        | 16   | V                   |

| Supply Current                                                       | I <sub>CC</sub>      | T <sub>A</sub> = 150°C                                                                                 | _    | 8.25     | 10   | mA                  |

| Undervoltage Lockout Threshold                                       | V <sub>UVLOHI</sub>  | Maximum V <sub>CC</sub> , dV/dt = 1V/ms, T <sub>A</sub> = 25°C                                         | _    | _        | 3.6  | V                   |

| Voltage <sup>[3]</sup>                                               | V <sub>UVLOLOW</sub> | Maximum V <sub>CC</sub> , dV/dt = 1V/ms, T <sub>A</sub> = 25°C                                         | 2.9  | _        | -    | V                   |

| VCC Low Flag Threshold [4]                                           | V <sub>UVLOTH</sub>  |                                                                                                        | 3.5  | _        | 3.9  | V                   |

| Supply Zener Clamp Voltage                                           | V <sub>ZSUP</sub>    | $I_{CC} = I_{CC(AWAKE)} + 3 \text{ mA}, T_A = 25^{\circ}\text{C}$                                      | 26.5 | 40       | _    | V                   |

| Reverse-Battery Current                                              | I <sub>RCC</sub>     | V <sub>RCC</sub> = -18 V, T <sub>A</sub> = 25°C                                                        | -5   | _        | 0    | mA                  |

| Power-On Time <sup>[5]</sup>                                         | t <sub>PO</sub>      |                                                                                                        | -    | 300      | _    | μs                  |

| Bypass1 Pin Output Voltage <sup>[6]</sup>                            | V <sub>BYP1</sub>    | T <sub>A</sub> = 25°C, C <sub>BYP</sub> = 0.1 μF                                                       | 2.5  | 2.7      | 2.9  | V                   |

| Bypass2 Pin Output Voltage <sup>[6]</sup> (Elevated SPI Output Mode) | V <sub>BYP2</sub>    | $T_A$ = 25°C, $C_{BYP2}$ = 0.1 $\mu$ F;<br>Contact Allegro for availability                            | 2.9  | 3.1      | 3.3  | V                   |

| SPI INTERFACE SPECIFICATIONS                                         |                      |                                                                                                        | '    |          |      |                     |

| Digital Input High Voltage <sup>[7]</sup>                            | V <sub>IH</sub>      | MOSIx, SCLKx, CSx pins                                                                                 | 2.4  | _        | 5.5  | V                   |

| Digital Input Low Voltage <sup>[7]</sup>                             | V <sub>IL</sub>      | MOSIx, SCLKx, CSx pins                                                                                 | -    | _        | 0.5  | V                   |

| CSx Pin Input Bias Current                                           | I <sub>BIAS</sub>    | V <sub>CSx</sub> = 3.3 V                                                                               | _    | 15       | _    | μA                  |

| SPI Output High Level                                                | V <sub>OH1</sub>     | MISOx pins, $C_L$ = 20 pF, $C_{BYP1}$ = 0.1 $\mu$ F, $C_{BYP2}$ grounded                               | 2.5  | 2.7      | 2.9  | V                   |

| SPI Output High Level<br>(Elevated SPI Output Mode)                  | V <sub>OH2</sub>     | MISOx pins, $C_L = 20$ pF, $C_{BYP1} = 0.1$ µF, $C_{BYP2} = 0.1$ µF. Contact Allegro for availability. | 2.9  | 3.1      | 3.3  | V                   |

| SPI Output Low Voltage                                               | V <sub>OL</sub>      | MISOx pins, C <sub>L</sub> = 20 pF                                                                     | _    | 0.3      | _    | V                   |

| SPI Clock Frequency <sup>[7]</sup>                                   | f <sub>SCLK</sub>    | MISOx pins, C <sub>L</sub> = 20 pF                                                                     | 0.1  | _        | 10   | MHz                 |

| SPI Clock Duty Cycle <sup>[7]</sup>                                  | D <sub>fSCLK</sub>   | SPICLK <sub>DC</sub> , 5 V compliant                                                                   | 40   | _        | 60   | %                   |

| SPI Frame Rate <sup>[7]</sup>                                        | t <sub>SPI</sub>     | 5 V compliant                                                                                          | 5.8  | _        | 588  | kHz                 |

| Chip-Select to First SCLK Edge [7]                                   | t <sub>cs</sub>      | Time from CSx going low to SCLKx falling edge                                                          | 50   | _        | _    | ns                  |

| Data Output Valid Time <sup>[7]</sup>                                | t <sub>DAV</sub>     | Data output valid after SCLKx falling edge                                                             | _    | _        | 40   | ns                  |

| MOSI Setup Time <sup>[7]</sup>                                       | t <sub>SU</sub>      | Input setup time before SCLKx rising edge                                                              | 25   | _        | _    | ns                  |

| MOSI Hold Time <sup>[7]</sup>                                        | t <sub>HD</sub>      | Input hold time after SCLKx rising edge                                                                | 40   | _        | _    | ns                  |

| SCLK to CS Hold Time <sup>[7]</sup>                                  | t <sub>CHD</sub>     | Hold SCLKx high time before CSx rising edge                                                            | 5    | _        | _    | ns                  |

| Capacitive Load <sup>[7]</sup>                                       | C <sub>L</sub>       | Loading on digital output (MISOx) pin<br>with SPI Clock Frequency = 10 MHz                             | _    | _        | 20   | pF                  |

Continued on the next page...

# OPERATING CHARACTERISTICS (continued): Valid over the full operating voltage and ambient temperature ranges, unless otherwise noted

| Characteristics                               | Symbol                    | Test Conditions                                                                                   | Min.                 | Typ. [1] | Max. | Unit <sup>[2]</sup> |

|-----------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------|----------------------|----------|------|---------------------|

| PWM INTERFACE SPECIFICATION                   | <b>S</b> (A1338LLE        | TR-P-T variants only)                                                                             |                      |          |      |                     |

|                                               |                           | PWM Frequency Code = 00                                                                           | _                    | 122      | _    | Hz                  |

| PWM Carrier Frequency                         | f <sub>PWM</sub>          | PWM Frequency Code = 01                                                                           | _                    | 1.024    | _    | kHz                 |

|                                               |                           | PWM Frequency Code = 10                                                                           | -                    | 2.048    | _    | kHz                 |

| PWM Duty Cycle Minimum                        | D <sub>PWM(min)</sub>     |                                                                                                   | _                    | 5        | _    | %                   |

| PWM Duty Cycle Maximum                        | D <sub>PWM(max)</sub>     |                                                                                                   | _                    | 95       | _    | %                   |

|                                               |                           | $5 kΩ \le R_{pullup} \le 50 kΩ$                                                                   | _                    | _        | 0.2  | V                   |

|                                               | V <sub>PWM(L)</sub>       | 2 kΩ ≤ R <sub>pullup</sub> < 5 kΩ                                                                 | _                    | _        | 0.4  | V                   |

| PWM Output Signal <sup>[8]</sup>              |                           | Minimum $R_{pullup} = 2 k\Omega$                                                                  | 0.9 × V <sub>S</sub> | _        | _    | V                   |

|                                               | V <sub>PWM(H)</sub>       | Maximum $R_{pullup}$ = 50 kΩ                                                                      | 0.7 × V <sub>S</sub> | _        | _    | V                   |

| Maximum Sink Current                          | I <sub>LIMIT</sub>        | Output FET on, T <sub>A</sub> = 25°C                                                              | _                    | 30       | _    | mA                  |

| PWM Carrier Frequency Tolerance [7]           | _                         | Deviation from expected f <sub>PWM</sub>                                                          | -10                  | _        | 10   | %                   |

| PWM Resolution                                | _                         | 12-bit angle value                                                                                |                      | 0.022    | _    | %DC/LSB             |

|                                               |                           | 1σ, T <sub>A</sub> = 25°C, f <sub>PWM</sub> = 2 kHz                                               |                      | 0.18     | _    | Hz                  |

| PWM Frequency Jitter                          | f <sub>PWM(JITTER)</sub>  | 1σ, T <sub>A</sub> = 25°C, f <sub>PWM</sub> = 1 kHz                                               |                      | 0.11     | _    | Hz                  |

|                                               | (* /                      | 1σ, T <sub>A</sub> = 25°C, f <sub>PWM</sub> = 124 Hz                                              |                      | 0.01     | _    | Hz                  |

|                                               | D <sub>PWM(JITTER)</sub>  | 3σ, 300 G, T <sub>A</sub> = 25°C, no AVG                                                          |                      | 0.095    | _    | %DC                 |

|                                               |                           | 3σ, 300 G, f <sub>PWM</sub> = 2 kHz, AVG = 0x4 or greater                                         |                      | 0.095    | _    | %DC                 |

| PWM Duty Cycle Jitter                         |                           | 3σ, 300 G, f <sub>PWM</sub> = 1 kHz, AVG = 0x5 or greater                                         |                      | 0.03     | _    | %DC                 |

|                                               |                           | 3σ, 300 G, f <sub>PWM</sub> = 124 Hz, AVG = 0x7                                                   |                      | 0.027    | _    | %DC                 |

| PWM Thermal Duty Cycle Drift [7]              | D <sub>PWM(THDRIFT)</sub> | Change in duty cycle from 25°C to 150°C; 300 G                                                    | -0.35                | _        | 0.35 | %DC                 |

| SENT PROTOCOL SPECIFICATION                   |                           |                                                                                                   |                      |          |      |                     |

| SENT Message Duration                         | t <sub>CVHST</sub>        | Tick time = 3 μs                                                                                  | _                    | _        | 1    | ms                  |

| Minimum Programmable SENT Message Duration    | t <sub>SENTMIN</sub>      | Tick time = 0.5 $\mu$ s, 3 data nibbles, SCN, and CRC, nibble length = 27 ticks                   | _                    | 96       | _    | μs                  |

|                                               | V                         | $5 \text{ k}\Omega \le \text{R}_{\text{pullup}} \le 50 \text{ k}\Omega$                           | _                    | _        | 0.2  | V                   |

| SENT Output Signal <sup>[7]</sup>             | V <sub>SENT(L)</sub>      | $2 kΩ ≤ R_{pullup} < 5 kΩ$                                                                        | _                    | _        | 0.4  | V                   |

| SENT Output Signalin                          | \/                        | Minimum R <sub>pullup</sub> = 2 kΩ                                                                | 0.9 × V <sub>S</sub> | _        | _    | V                   |

|                                               | V <sub>SENT(H)</sub>      | Maximum $R_{pullup}$ = 50 kΩ                                                                      | 0.7 × V <sub>S</sub> | _        | _    | V                   |

| CENT Output Trigger Cignel                    | V <sub>SENTtrig(L)</sub>  |                                                                                                   | _                    | _        | 1.4  | V                   |

| SENT Output Trigger Signal                    | V <sub>SENTtrig(H)</sub>  |                                                                                                   | 2.8                  | _        | _    | V                   |

| Minimum Time Frame for SENT<br>Trigger Signal | t <sub>SENTMIN</sub>      | Tick time = 0.5 $\mu$ s, 3 data nibbles, SCN, and CRC, nibble length = 27 ticks                   | 2                    | -        | _    | μs                  |

| Triggered Delay Time                          | t <sub>dSENT</sub>        | From end of trigger pulse to beginning of SENT message frame. TSENT (SENT_MODE 3 and SENT_MODE 4) | _                    | 7        | _    | tick                |

| Maximum Sink Current                          | I <sub>LIMIT</sub>        | Output FET on, T <sub>A</sub> = 25°C                                                              | _                    | 30       | _    | mA                  |

| DIAGNOSTIC SPECIFICATIONS                     |                           |                                                                                                   |                      |          |      |                     |

| CVH Self-Test Time                            | t <sub>UI_DIAG</sub>      |                                                                                                   | _                    | 23       | _    | ms                  |

| Logic BIST Coverage vs. Time                  | t <sub>LBISTXX</sub>      | 70% Coverage                                                                                      | _                    | 10       | _    | ms                  |

Continued on the next page...

### OPERATING CHARACTERISTICS (continued): Valid over the full operating voltage and ambient temperature ranges, unless otherwise noted

| Characteristics                           | Symbol Test Conditions  |                                                                                                     | Min.  | Typ. [1] | Max. | Unit <sup>[2]</sup> |

|-------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------|-------|----------|------|---------------------|

| EEPROM PROGRAMMING PULSES                 | 3                       |                                                                                                     |       |          |      |                     |

| Pulse High Time                           | t <sub>PULSE(H)</sub>   | Time above minimum pulse voltage                                                                    | 8     | 10       | 11   | ms                  |

| Rise Time                                 | t <sub>r</sub>          | 10% to 90% of minimum pulse level                                                                   | 300   | _        | _    | μs                  |

| Fall Time                                 | t <sub>f</sub>          | t <sub>f</sub> 10% to 90% of minimum pulse level                                                    |       | _        | _    | μs                  |

| Pulse Voltage                             | V <sub>PULSE</sub>      | Applied on VCC line                                                                                 | 18    | 19       | 19.5 | V                   |

| Separation Time                           | t <sub>PULSE(f-r)</sub> | Timing between first pulse dropping below 6 V and 2 <sup>nd</sup> pulse rising above 6 V            | 0.002 | _        | 50   | ms                  |

| MAGNETIC CHARACTERISTICS                  |                         |                                                                                                     |       |          | `    | •                   |

| Magnetic Field                            | В                       | Range of input field                                                                                | -     | _        | 1500 | G <sub>pp</sub>     |

| ANGLE CHARACTERISTICS                     |                         |                                                                                                     |       |          |      |                     |

| Digital Output Word Length <sup>[8]</sup> | RES <sub>ANGLE</sub>    |                                                                                                     | _     | 12       | _    | bit                 |

| Effective Resolution [9]                  |                         | B = 300 G, T <sub>A</sub> = 25°C, ORATE = 0                                                         | -     | 11.59    | _    | bit                 |

|                                           | t <sub>ANG</sub>        | High RPM mode                                                                                       | _     | 25       | _    | μs                  |

| Angle Refresh Rate <sup>[10]</sup>        |                         | Low RPM mode, AVG = 011 (varies with AVG mode, refer to the appendix <i>Programming Reference</i> ) | _     | 200      | _    | μs                  |

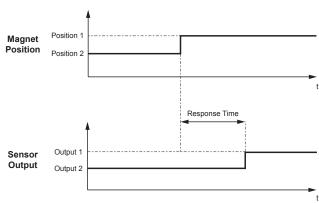

| Response Time                             | t <sub>RESPONSE</sub>   | Low RPM mode (see Figure 4)                                                                         | _     | 60       | -    | μs                  |

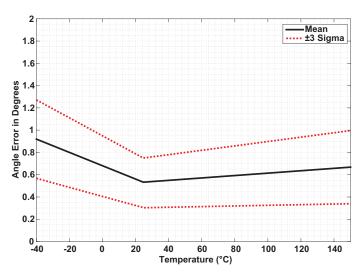

| Angle Free                                |                         | T <sub>A</sub> = 25°C, ideal magnet alignment, B = 300 G, target rpm = 0                            | -     | 0.5      | _    | degrees             |

| Angle Error                               | ERR <sub>ANG</sub>      | T <sub>A</sub> = 150°C, ideal magnet alignment, B = 300 G, target rpm = 0                           | -1.3  | -        | 1.3  | degrees             |

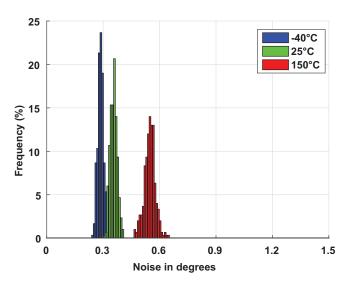

| Angle Naise                               | N                       | T <sub>A</sub> = 25°C, B = 300 G, 3 sigma noise, no internal filtering                              | _     | 0.35     | _    | degrees             |

| Angle Noise                               | N <sub>ANG</sub>        | T <sub>A</sub> = 150°C, no internal filtering, B = 300 G,<br>3 sigma noise, target rpm = 0          | -     | 0.55     | -    | degrees             |

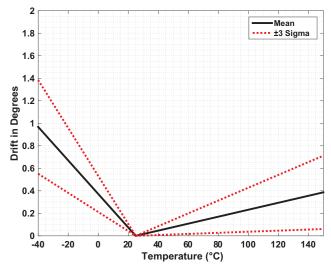

| Tomporatura Drift                         | ANCLE                   | T <sub>A</sub> = 150°C, B = 300 G                                                                   | -1.4  | _        | 1.4  | degrees             |

| Temperature Drift                         | ANGLE <sub>DRIFT</sub>  | T <sub>A</sub> = -40°C, B = 300 G                                                                   | _     | ±1       | _    | degrees             |

| Angle Drift Over Lifetime                 | ANGLE <sub>DRIFT</sub>  | B = 300 G, typical maximum drift observed after AEC-Q100 qualification testing                      | _     | ±0.5     | _    | degrees             |

$<sup>^{[1]}</sup>$  Typical data is at  $\rm T_A$  = 25°C and  $\rm V_{CC}$  = 5 V, and it is for design estimates only.

[9] Effective Resolution is calculated using the formula below:

$$\log_2(360) - \log_2\left(\frac{1}{n}\sum_{i=1}^n \sigma_i\right)$$

[10] The rate at which a new angle reading will be ready.

Figure 5: Definition of Response Time

<sup>[2] 1</sup> G (gauss) = 0.1 mT (millitesla).

$<sup>^{[3]}</sup>$  At power-on, the die will not respond to commands until  $V_{CC}$  rises above  $V_{UVLOHI}$ . After that, the die will perform and respond normally until V<sub>CC</sub> drops below V<sub>UVLOLOW</sub>.

[4] VCC Low Threshold Flag will be sent via the SPI interface as part of the angle

measurement

<sup>[5]</sup> During the power-on time period, the A1338 SPI transactions are not guaranteed.

$<sup>^{[6]}</sup>$  The output voltage and current specifications are to aid in PCB design. The pin is not intended to drive any external circuitry. The specifications indicate the peak capacitor charging and discharging currents to be expected during normal operation.

<sup>[7]</sup> Parameter is not guaranteed at final test. Determined by design.

<sup>[8]</sup> RES<sub>ANGLE</sub> represents the number of bits of data available for reading from the die registers.

### **FUNCTIONAL DESCRIPTION**

#### Overview

The A1338 is a rotary position Hall-sensor-based device. It incorporates an electrically independent Hall-based sensor die to provide solid-state consistency and reliability, and to support a wide variety of automotive applications. The Hall-sensor-based die measures the direction of the magnetic field vector through 360° in the x-y plane (parallel to the branded face of the device) and computes an angle measurement based on the actual physical reading, as well as any internal configuration parameters that have been set by the user. The output of the die is used by the host microcontroller to provide a single channel of target data.

This device is an advanced, programmable system-on-chip (SoC). The integrated circuit includes a circular vertical Hall (CVH) analog frontend, a high-speed sampling A-to-D converter, digital filtering, digital signal processing, and an SPI, SENT, or PWM output of the processed angle data.

### **Angle Measurement**

The A1338 can monitor the angular position of a rotating magnet at speeds ranging from 0 to more than 7600 rpm. At lower rotational speeds, the A1338 is able to measure angle data with minimal angular latency between the actual magnet and sensor output. As the rpm increases, the angular latency between the magnet and sensor output also increases. Above 7600 rpm, the A1338 continues to provide angle data; however, the accuracy is proportionally reduced.

The A1338 can be configured to operate in two angular measurement modes of operation: Low RPM mode, and High RPM mode. Low RPM mode allows a programmable number of internal angle samples to be accumulated and averaged, providing greater resolution while reducing the update rate. This is suitable for lower rpm applications (0 to  $\approx\!500$  rpm). For high-speed applications, the averaging function may be bypassed by operating in High RPM mode.

The actual update rate of Low RPM mode can be changed by setting the AVERAGING bits in the EEPROM (see the appendix *Programming Reference* for details). Table 1 describes the different levels of averaging available in Low RPM mode. A setting of  $000_2$  is equivalent to High RPM mode.

Table 1: Refresh Rate Based on Quantity of Samples Averaged

| AVG<br>[2:0] | Quantity of Samples<br>Averaged | Refresh Rate<br>(µs) |

|--------------|---------------------------------|----------------------|

| 000          | 1                               | 25                   |

| 001          | 2                               | 50                   |

| 010          | 4                               | 100                  |

| 011          | 8                               | 200                  |

| 100          | 16                              | 400                  |

| 101          | 32                              | 800                  |

| 110          | 64                              | 1600                 |

| 111          | 128                             | 3200                 |

The A1338 has a typical output bandwidth of 40 kHz (25  $\mu s$  refresh rate) in High RPM mode. In High RPM mode, a new angle measurement is available at the internal angle output register to be transmitted over the SPI/SENT or PWM output ports every 25  $\mu s$ . There is a latency of 60  $\mu s$  from when there is a change in the position of the target magnet field to when the new representative angle is updated in the internal angle output register. This latency effectively represents the age of the angle measurement.

### Impact of High-Speed Sensing

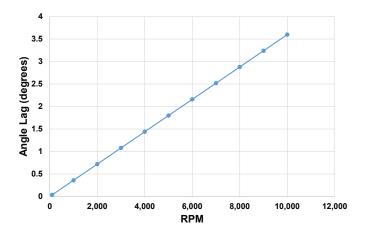

Due to signal path latency, the angle information is delayed by  $t_{RESPONSE}$ . This delay equates to a greater angle value as the rotational velocity increases (i.e. a magnet rotating at 20,000 rpm traverses twice as much angular distance in a fixed time period as a magnet rotating at 10,000 rpm), and is referred to as angular lag.

The lag is directly proportional to rpm, and may be compensated for externally, if the velocity is known.

Angular lag can be expressed using the following equation:

$$Angle\_Lag = (rpm \times 6) / (1^6 \times t_{RESPONSE})$$

(1)

where rpm represents the rotational velocity of the magnet, Angle\_lag is expressed in degrees, and  $t_{RESPONSE}$  is in  $\mu s$ .

Figure 6: Angle Lag versus RPM, 60 µs Response Time

### **Angle Resolution and Representation**

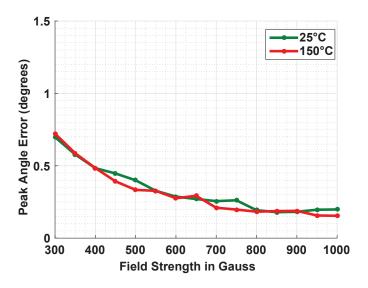

In addition to using the internal averaging of the sensor, angle resolution is also dependent on the intensity (B, in gauss) of the applied magnetic field from the target. At lower intensities, a reduced signal-to-noise ratio will cause one or two LSBs to change state randomly due to noise. These factors work together, so when High RPM mode is selected, the effective range of resolution is 8 to 10 bits (from lower to higher field intensities), and in Low RPM mode, the effective range is 11 to 12 bits, depending on field strength and AVG selection.

Regardless of the field intensity and mode selection, the transmission protocol and number formatting remains the same. The MSB is always transmitted first. The entire number should be read.

The Output Angle is always calculated at maximum resolution. To be more explicit, when reading the digital angle value:

$$Angle_{OUT} = 360 \,(^{\circ}) \times D[12:0] \,/\,(2^{13})$$

(2)

This formula is always true, regardless of the applied field intensity. What changes with the field and speed setting is how "quiet" the LSBs of the measurement data (D 12:x) will be.

### **Programing Modes**

The EEPROM can be programmed through the dedicated SPI interface pins or via Manchester encoding on the VCC pin, allowing process coefficients to be entered and options selected. (Note: programming EEPROM also requires the VCC line to be pulsed, which could adversely affect other devices if powered from the same line). The EEPROM provides persistent storage at end of line for final parameters.

### **SPI System-Level Timing**

The A1338 outputs a new angle measurement every  $t_{\rm ANG}$   $\mu \rm s$ . In High RPM mode, the A1338 outputs a new angle measurement every  $t_{\rm ANG}$   $\mu \rm s$ , with an effective resolution of 10 bits. There is, however, a latency of  $t_{\rm LAT}$ , from when the rotating magnet is sampled by the CVH to when the sampled data has been completely transmitted over the SPI interface. Because an SPI interface Read command is not synchronous with the CVH timing, but instead is polled by the external host microcontroller, the latency can vary. For single back-to-back SPI transactions (first transaction is sending the Read register 0x0 command, second is retrieving the angle data) the following scenarios are possible:

- Worst case: 2 CVH cycle + 2 SPI cycles

- Best case: 1.5 SPI cycles; 2 μs, assuming a 10 MHz SPI clock

### Power-Up

Upon applying power to the A1338, the device automatically runs through an initialization routine. The purpose of this initialization is to ensure that the device comes up in the same predictable operating condition every power cycle. This initialization routine takes a finite amount of time to complete, which is referred to as Power-On Time,  $t_{\rm PO}$ .

The A1338 wakes up in a default state that sets all SPI registers to their default value. It is important to note that, regardless of the state of the device before a power cycle, the device will re-power with default values. For example, on every power-up, the device will power up in the mode set in the EEPROM bit RPM. The state of the EEPROM is unchanged.

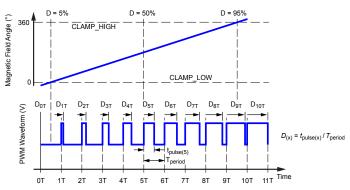

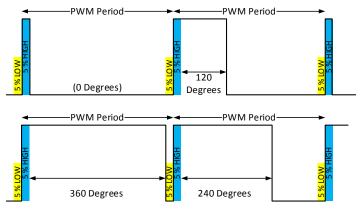

### **PWM Output ("-P-" option)**

The A1338LLETR-P-T option provides a pulse-width-modulated output with duty cycle proportional to the measured angle. The PWM duty cycle ranges between 5% (corresponding to 0° angle) and 95% (corresponding to 360° angle). The 0% and 100% (Pulled Low and Pulled High) states are reserved for error condi-

tion notifications.

Figure 7: PWM mode outputs a duty-cycle-based waveform that can be read by the external controller as a cumulatively changing continuous voltage.

Within each cycle, the output is high for the first 5% of the period. The middle 90% of the period is a linear interpolation of the angle as samples at the beginning of the PWM period.

Figure 8: Pulse-Width Modulation (PWM) Examples

The angle is represented in 12-bit resolution and can never reach exactly  $360^{\circ}$ . The maximum duty cycle high period is:

DutyCycleMax (%) =  $(4095 / 4096) \times 90 + 5$ .

### **Error Reporting in PWM**

The PWM output will tristate when any unmasked error is present (see ERR and ERR2 register descriptions). Error flags are masked via bits within EEPROM 0x1E.

By default, the BATD error mask is set in EEPROM for all PWM output ICs. This prevents the PWM output from tristating on power-on.

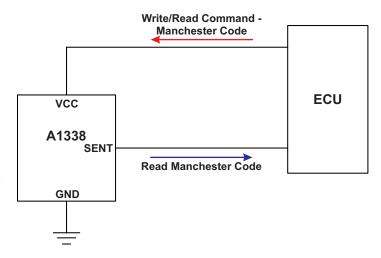

### MANCHESTER SERIAL INTERFACE

To facilitate addressable device programming when using the unidirectional SENT output mode with no need for additional wiring, the A1338 incorporates a serial interface on the VCC line. (Note: The A1338 may be programmed via the SPI interface, with additional wiring connections. For detailed information on part programming, refer to the A1338 programming manual). This interface allows an external controller to read and write registers in the A1338 EEPROM and volatile memory. The device uses a point-to-point communication protocol, based on Manchester encoding per G.E. Thomas (a rising edge indicates a 0 and a falling edge indicates a 1), with address and data transmitted MSB first. The addressable Manchester code implementation uses the logic states of the SA0 (SPI  $\overline{CS}$  pin) / SA1 (SPI SCLK pin) to set address values for the die. In this way, individual communication with up to four A1338 dies is possible.

To prevent any undesired programming of the A1338, the serial interface can be disabled by setting the Disable Manchester bit (0x19 bit 18) to a 1. With this bit set, the A1338 will ignore any Manchester input on VCC.

## **Entering Manchester Communication Mode**

Provided the Disable Manchester bit is not set in EEPROM, the A1338 continuously monitors the VCC line for valid Manchester commands. The part takes no action until a valid Manchester Access Code is received.

There are two special Manchester code commands used to activate or deactivate the serial interface and specify the output format used during Read operations:

- 1. Manchester Access Code: Enters Manchester Communication Mode; Manchester code output on the SENT pin.

- 2. Manchester Exit Code: Returns the SENT pin to normal (angle data) output format.

Once the Manchester Communication Mode is entered, the SENT output pin will cease providing angle data, interrupting any data transmission in progress.

### Transaction Types

As shown in Figure 9, the A1338 receives all commands via the VCC pin, and responds to Read commands via the SENT pin. This implementation of Manchester encoding requires the communication pulses be within a high  $(V_{MAN(H)})$  and low  $(V_{MAN(L)})$  range of voltages on the VCC line. Writing to EEPROM is supported by two high-voltage pulses on the VCC line.

Each transaction is initiated by a command from the controller; the A1338 does not initiate any transactions. Two commands are recognized by the A1338: Write and Read.

### Writing to EEPROM

When a Write command requires writing to non-volatile EEPROM, after the Write command, the controller must also send two *Programming pulses*, high-voltage strobes via the VCC pin. These strobes are detected internally, allowing the A1338 to boost the voltage on the EEPROM gates. Refer to the programming manual for specifics on sensor programming and protocol details.

Figure 9: Top-Level Programming Interface

### **Manchester Interface Reference**

Table 2: Manchester Interface Protocol Characteristics [1]

| Characteristics                        | Symbol                  | Note                                                                                                            | Min.                    | Тур. | Max.                   | Unit |

|----------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------|------|------------------------|------|

| INPUT/OUTPUT SIGNAL TIMING             |                         |                                                                                                                 |                         |      |                        |      |

| Bit Rate                               |                         | Defined by the input message bit rate sent from the external controller                                         | 4                       | _    | 50                     | kbps |

| Bit Time                               | 4                       | Data bit pulse width at 4 kbps                                                                                  | 243                     | 250  | 257                    | μs   |

| Bit Time                               | t <sub>BIT</sub>        | Data bit pulse width at 100 kbps                                                                                | 9.5                     | 10   | 10.5                   | μs   |

| Bit Time Error                         | err <sub>TBIT</sub>     | Deviation in t <sub>BIT</sub> during one command frame                                                          | -11                     | _    | +11                    | %    |

| Write Delay                            | t <sub>WRITE(E)</sub>   | Required delay from the end of the second EEPROM Program pulse to the leading edge of a following command frame | V <sub>CC</sub> < 6.0 V | -    | -                      | _    |

| Read Delay                             | t <sub>START_READ</sub> | Delay from the trailing edge of a Read command frame to the leading edge of the Read Acknowledge frame          | ½ × t <sub>bit</sub>    | -    | ³⁄₄ × t <sub>bit</sub> | μs   |

| EEPROM PROGRAMMING PULS                | E                       |                                                                                                                 | ·                       |      |                        |      |

| EEPROM Programming Pulse<br>Setup Time | t <sub>sPULSE(E)</sub>  | Delay from last bit cell of write command to start of EEPROM programming pulse                                  | 40                      | -    | _                      | μs   |

| Pulse High Time                        | t <sub>PULSE(H)</sub>   | Time above minimum pulse voltage                                                                                | 8                       | 10   | 11                     | ms   |

| Rise Time                              | t <sub>r</sub>          | 10% to 90% of minimum pulse level                                                                               | 300                     | _    | _                      | μs   |

| Fall Time                              | t <sub>f</sub>          | 10% to 90% of minimum pulse level                                                                               | 60                      | _    | _                      | μs   |

| Pulse Voltage                          | V <sub>PULSE</sub>      | Applied on VCC Line                                                                                             | 18                      | 19   | 19.5                   | V    |

| Separation Time                        | t <sub>PULSE(f-r)</sub> | Timing between first pulse dropping below 6 V and 2nd pulse rising above 6 V                                    | 0.002                   | -    | 50                     | ms   |

| INPUT SIGNAL VOLTAGE                   |                         |                                                                                                                 | ·                       |      |                        |      |

| Manchester Code High Voltage           | V <sub>MAN(H)</sub>     | Applied to VCC line                                                                                             | 7.8                     | _    | _                      | V    |

| Manchester Code Low Voltage            | V <sub>MAN(L)</sub>     | Applied to VCC line                                                                                             |                         | _    | 6.3                    | V    |

| OUTPUT SIGNAL VOLTAGE (AP              |                         | NT LINE)                                                                                                        |                         |      |                        |      |

| Manchester Code High Voltage           | V                       | Minimum $R_{pullup} = 5 \text{ k}\Omega$                                                                        | 0.9 × V <sub>S</sub>    | _    | _                      | V    |

| manonester Code High voltage           | V <sub>MAN(H)</sub>     | Maximum $R_{pullup}$ = 50 kΩ                                                                                    | 0.7 × V <sub>S</sub>    | _    | _                      | V    |

| Manchester Code Low Voltage            | V <sub>MAN(L)</sub>     | $5 kΩ \le R_{pullup} \le 50 kΩ$                                                                                 | _                       | _    | 0.2                    | V    |

<sup>[1]</sup> Determined by design.

# **SENT Output Mode** (A1338LLETR-T option)

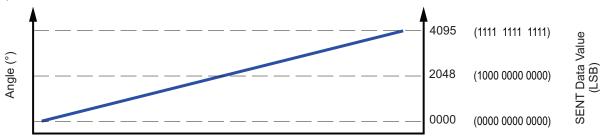

The SENT output converts the measured magnetic field angle to a binary value mapped to the Full-Scale Output (FSO) range of 0 to 4095, shown in Figure 10. This data is inserted into a binary pulse message, referred to as a frame, that conforms to the SENT data transmission specification (SAEJ2716 JAN2010).

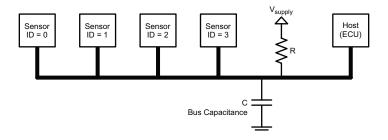

The SENT frame may be configured via EEPROM. The A1338 may operate in one of three broadly defined SENT modes (see the A1337/8 Programming Manual for details on SENT modes and settings).

- SAE J2716 SENT: Free-streaming SENT frame in accordance with industry specification.

- Triggered SENT (TSENT): User-defined sampling and retrieval.

- Shared SENT: Allows multiple devices to share a common SENT line. Devices may either be directly addressed (Addressable SENT or ASENT) or sequentially polled (Sequential SENT or SSENT).

Figure 10: Angle is represented as a 12-bit digital value.

Figure 11: Allegro's proprietary SENT protocol allows multiple parts to share one common output bus.

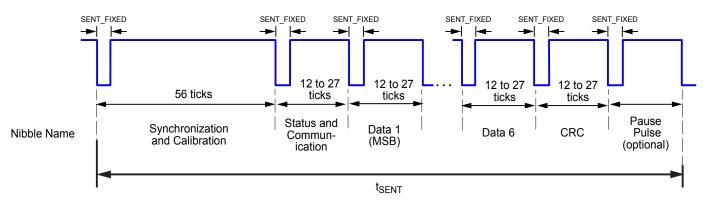

#### SENT MESSAGE STRUCTURE

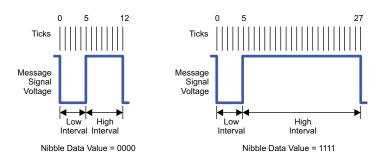

Data within a SENT message frame is represented as a series of nibbles, with the following characteristics:

- Each nibble is an ordered pair of a low-voltage interval followed by a high-voltage interval.

- The low-voltage interval acts as the delimiting state which acts as a boundary between each nibble. The length of this lowvoltage interval is fixed at 5 ticks.

- The high-voltage interval performs the job of the information state and is variable in duration in order to contain the data payload of the nibble.

- The slew rate of the falling edge may be adjusted using the C SENT DRIVE parameter.

The duration of a nibble is denominated in ticks. The period of a tick is set by the C\_TICK\_TIME parameter. The duration of the nibble is the sum of the low-voltage interval

The parts of a SENT message are arranged in the following required sequence (see Figure 13):

- **1. Synchronization and Calibration:** Flags the start of the SENT message.

- **2. Status and Communication Nibble:** Provides A1338 status and the optional serial data determined by the setting of the SENT SERIAL parameter.

- 3. Data: Angle information and optional data.

- 4. CRC: Error checking.

- Pause Pulse (optional): Fill pulse between SENT message frames.

Figure 12: General Value Formation for SENT 0000 (left), 1111 (right)

**Table 3: Nibble Composition and Value**

| Q                           | uantity of Tick              | Binary | Decimal          |                     |  |

|-----------------------------|------------------------------|--------|------------------|---------------------|--|

| Low-<br>Voltage<br>Interval | High-<br>Voltage<br>Interval | Total  | (4-bit)<br>Value | Equivalent<br>Value |  |

| 5                           | 7                            | 12     | 0000             | 0                   |  |

| 5                           | 8                            | 13     | 0001             | 1                   |  |

| 5                           | 9                            | 14     | 0002             | 2                   |  |

|                             | •                            | •      | •                | •                   |  |

| 5                           | 21                           | 26     | 1110             | 14                  |  |

| 5                           | 22                           | 27     | 1111             | 15                  |  |

Figure 13: General Format for SENT Message Frame

Table 4: EEPROM Registers Map Table with Defaults (Factory-Reserved Registers Not Shown) [1]

| EADR | State     |      | Bits |     |     |     |      |      |        |    |       |        |         |       |        |      |    |    |        |        |        |      |    |         |      |

|------|-----------|------|------|-----|-----|-----|------|------|--------|----|-------|--------|---------|-------|--------|------|----|----|--------|--------|--------|------|----|---------|------|

| EADK | State     | 23   | 22   | 21  | 20  | 19  | 18   | 17   | 16     | 15 | 14    | 13     | 12      | 11    | 10     | 9    | 8  | 7  | 6      | 5      | 4      | 3    | 2  | 1       | 0    |

| 0x17 | SENT_CFG  | ZS   | SS   | SM  | PO  | IS  | RES  | SC   | CN_MOD | E  | D     | ATA_MC | DE      | SE    | NT_MOI | DE   |    |    | TICK   | TIME   |        |      | SI | ENT_DRI | VE   |

| 0x18 | CUST_CFG1 |      | RES  |     | CIS | DA  | MA   | XID  | NS     | FA | u_ir  | nt_st  | pw_u    | ıp_st |        |      |    | MI | SSING_ | MAG_TH | IRESHO | )LD  |    |         |      |

| 0x19 | CUST_CFG2 | LOCK | RES  | PWI | M_F | RES | MAND | SCRC | RPMD   | P  | VERAG | E      | POL     |       |        |      |    | P  | NGLE_  | OFFSET |        |      |    |         |      |

| 0x1E | ERM       |      |      |     |     | RES |      |      |        |    | MAN2  | MAN    | UV      | LBST  | CVHST  | GOVF | АН | AL | EU     | ES     | TR     | TRNO | ΙE | MAGM    | BATD |

| 0x1F | CUST2     |      |      |     |     |     |      |      |        |    |       | С      | UST_EEP | )     |        |      |    |    |        |        |        |      |    |         |      |

<sup>[1]</sup> For more details, see Programming Manual.

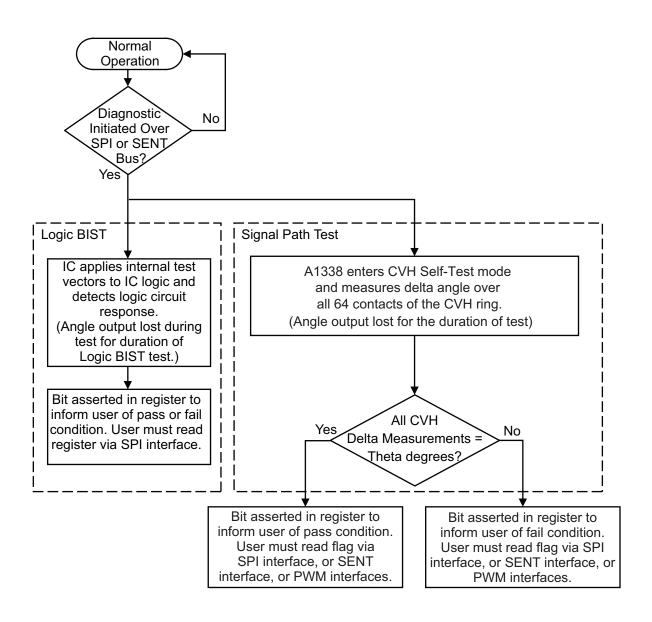

## **Diagnostics**

The A1338 was designed with ISO 26262:2011 requirements in mind and supports a number of on-chip self diagnostics to enable the host microcontroller to assess the operational status of the die. For example, the die can be user-configured for logic built-in self-test (LBIST) evaluation to ensure the digital circuits are operational. Upon completion of an LBIST operation, the A1338 will set a pass/fail LBIST status flag in the device error (ERR) register.

The A1338 die also supports several diagnostic features and status flags, accessible via an SPI read of the ERR register, to let the user know if any issues are present with the A1338 or associated magnetic system, as shown in Table 5.

In addition, the die on the A1338 supports an on-chip user-initiated diagnostic (CVH Self-Test) mode that tests the entire signal path, including the front end CVH sensing circuitry.

#### **USER-INITIATED DIAGNOSTICS**

The die of the A1338 can be controlled by a microcontroller to enter its CVH Self-Test mode via SPI or SENT.

When a CVH Self-Test mode operation is requested by the microcontroller, the die initiates a test mode sequence whereby it sequentially applies an internal constant bias current to every contact element in the CVH ring. As each element in the CVH ring is sequentially biased, an angle measurement is calculated.

The time to complete one revolution around the CVH ring and calculate and store incremental angle measurements is t<sub>CVHST</sub>.

**Table 5: Diagnostic Capabilities**

| Diagnostic/ Protection                | Description                                                                 | Output State                                                                                        |

|---------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Loss of V <sub>CC</sub>               | Determine if battery power was lost.                                        | BATD Error flag is set; see ERR register table.                                                     |

| Reverse V <sub>CC</sub> Condition     | Current Limiting (VCCx pin).                                                | Output Below GND.                                                                                   |

| MISO/SENT/PWM Short to VCC            | Current Limiting (MISOx pin).                                               | MISO/SENT/PWM Line: Pulled up to V-pullup.<br>Should not be tied to VCC if V <sub>CC</sub> > 5.5 V. |

| MISO/SENT/PWM Short to Ground         | Current Limiting (MISOx pin).                                               | MISO/SENT/PWM Line: Pulled up to GND.                                                               |

| Logic Built-In Self-Test (LBIST)      | 70% coverage for 10 ms BIST of all digital circuitry.                       | Error Flags set in SPI message when errors are detected; see ERR2 Register table.                   |

| Signal Path Diagnostics               | User controlled advanced CVH and full signal path diagnostics.              | Error Flags set in SPI message when errors are detected; see ERR2 Register table.                   |

| Internal Error                        | Monitors digital logic for proper function.                                 | IERR Error flag is set; see ERR Register table.                                                     |

| Missing Magnet                        | Monitors magnet field level in case of mechanical failure.                  | MAGM Error flag is set; see ERR Register table.                                                     |

| EEPROM Error Detection and Correction | Detection of single and dual bit error, and correction of single bit error. | Error flags set in SPI message when errors are detected or corrected; see ERR Register table.       |

| V <sub>CC</sub> Low Flag              | Asserted when V <sub>CC</sub> < V <sub>UVLOTH</sub> .                       | Bit 2 of SPI Output on MISO is set high. See Programming manual for more details.                   |

| Temperature Out of Range              | Die temperature has exceeded acceptable range.                              | See ERR Register table for more details.                                                            |

### SERIAL INTERFACE STRUCTURE

The serial interface contains the Primary Serial Interface (PSI) registers and the restricted Extended Addressing registers. The PSI fields are used by the host for routine communication with the A1338, such as retrieving current angle and turns count, error, and status data, and managing certain configuration settings. For information on extended addressing and EEPROM access, see the A1338 programming manual.

Table 6: Primary Serial Interface Registers (Reserved Registers Not Shown)

| Address (Hex) | Name (Symbol)      | Usage                                                                                                 |

|---------------|--------------------|-------------------------------------------------------------------------------------------------------|

| 0x00          | Angle Output (ANG) | Read out current angle (Note: 12-bit Angle Output located MSB first, in bits12:1; Bit0 is always '0') |

| 0x04          | Error (ERR1)       | Read out error flags                                                                                  |

| 0x05          | Error (ERR2)       | Read out error flags                                                                                  |

| 0x08          | Control (CTRL)     | Read or write configuration commands                                                                  |

| 0x0F          | Key Code (KEY)     | Write the Key Code to enable access to Extended Addressing registers                                  |

Table 7: Primary Serial Interface Registers Bits Map (Reserved Registers Not Shown)

| Serial  | Register | Addressed Byte (MSB) |    |    |   |    |         |           |      |       |       |      |      |      |

|---------|----------|----------------------|----|----|---|----|---------|-----------|------|-------|-------|------|------|------|

| Address | Symbol   | 12                   | 11 | 10 | 9 | 8  | 7       | 6         | 5    | 4     | 3     | 2    | 1    | 0    |

| 0x00    | ANG      |                      |    |    |   | ΙA | NGLE OU | TPUT (12: | 1)   |       |       |      |      | 0    |

| 0x04    | ERR      | _                    | _  | _  | - | _  | _       | EEP2      | EEP1 | TMP   | RES   | IERR | MAGM | BATD |

| 0X05    | ERR2     | _                    | _  | _  | _ | _  | _       | MANER     | RES3 | LBIST | CVHST | RES2 | RES1 | RES0 |

| 0x08    | CTRL     | _                    | _  | _  | _ | _  | _       | _         | _    | STS   | TRST  | RPM  | TEN  | ERST |

| 0x0F    | KEY      | _                    | _  | _  | _ | _  |         |           |      | KEY_  | CODE  |      |      |      |

## ANG (Angle Output) Register

Address: 0x00

| Address |              | 0x00 |     |     |     |     |     |     |     |     |     |     |   |

|---------|--------------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|---|

| Bit     | 12           | 11   | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0 |

| Name    | ANGLE_OUTPUT |      |     |     |     |     |     | _   |     |     |     |     |   |

| R/W     | R            | R    | R   | R   | R   | R   | R   | R   | R   | R   | R   | R   | R |

| Value   | 0/1          | 0/1  | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0 |

| Reset   | 0            | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0 |

Stores data on current angle reading.

### **ANGLE\_OUTPUT** [12:1] Current Angle

Most recent angle reading. Value is unsigned, stored in bits 12:1 (bit 0 defaults to 0). As the target turns, the angle value increases or decreases according to the rotational polarity setting in EEPROM (CUST\_CFG2 register, POL bit).

| Bit  | Value | Description            |

|------|-------|------------------------|

| 12:1 | 0/1   | Current angle reading. |

## ERR (Error) Register

Address: 0x04

| Address |    | 0x04 |    |   |   |   |      |      |     |     |      |      |      |

|---------|----|------|----|---|---|---|------|------|-----|-----|------|------|------|

| Bit     | 12 | 11   | 10 | 9 | 8 | 7 | 6    | 5    | 4   | 3   | 2    | 1    | 0    |

| Name    | _  | _    | _  | - | _ | _ | EEP2 | EEP1 | TMP | RES | IERR | MAGM | BATD |

| R/W     | _  | _    | _  | _ | _ | _ | R    | R    | R   | R   | R    | R    | R    |

| Value   | Х  | X    | Х  | Х | Х | Х | 0/1  | 0/1  | 0/1 | 0/1 | 0/1  | 0/1  | 0/1  |

| Reset   | 0  | 0    | 0  | 0 | 0 | 0 | 0    | 0    | 0   | 0   | 0    | 0    | 1    |

Error register. Indicates various current error conditions. When set, can only be cleared via the CTRL register ERST field, hard reset, or power-on reset (see BATD for exception). If any of the error bits are asserted, the error flag on the serial interface will be asserted. Masking an error bit will prevent the bit from asserting the serial interface error flag, but the error bit may still be asserted in this register.

#### EEP2 [6] EEPROM Error Flag 2

Uncorrectable dual-bit EEPROM error flag

| Bit | Value | Description                  |

|-----|-------|------------------------------|

| 6   | 0     | Error condition not present. |

| 0   | 1     | Error condition present.     |

#### EEP1 [5] EEPROM Error Flag 1

Corrected single-bit EEPROM error flag.

| Bit | Value | Description                  |

|-----|-------|------------------------------|

| _   | 0     | Error condition not present. |

| 5   | 1     | Error condition present.     |

#### TMP [4] Temperature Out of Range

This bit indicates an error condition when the die temperature has exceeded the acceptable range.

| Bit | Value | Description                  |

|-----|-------|------------------------------|

| 4   | 0     | Error condition not present. |

| 4   | 1     | Error condition present.     |

#### **RES** [3] Reserved

#### IERR [2] Internal Error

This bit is set to 1 if an internal logic error condition has been detected. When this bit is set to 1, a general reset is recommended.

| Bit | Value | Description                                     |

|-----|-------|-------------------------------------------------|

| 2   | 0     | No digital logic timer error has been detected. |

| 2   | 1     | Digital logic timer error has been detected.    |

#### MAGM [1] Target Magnet Loss

Monitors target magnet field level to detect field loss due to mechanical failure in the application. Missing Magnet Field Threshold can be customer programmed by writing to EEPROM Address 0x18, Bits 10:0 (MISSING\_MAG\_THRESHOLD). Allegro programs this to a default value of 100 G, but the customer can readjust this field if they prefer.

| Bit | Value | Description                  |

|-----|-------|------------------------------|

| 1   | 0     | Error condition not present. |

| '   | 1     | Error condition present.     |

#### **BATD [0] Power Supply Loss**

Indicates if battery power (VCC supply) was lost. By default also indicates at expected low power events: start-up, power-on reset, and after exiting Transport mode. Before commencing normal operation, must be set to 0 by asserting the ERST bit of the CTRL register (unless field is masked in EEPROM by ERM register BATD field).

| Bit | Value | Description                  |

|-----|-------|------------------------------|

| 0   | 0     | Error condition not present. |

|     | 1     | Error condition present.     |

### ERR2 (Error2) Register

Address: 0x05

| Address |    | 0x05 |    |   |   |   |       |      |       |       |      |      |      |

|---------|----|------|----|---|---|---|-------|------|-------|-------|------|------|------|

| Bit     | 12 | 11   | 10 | 9 | 8 | 7 | 6     | 5    | 4     | 3     | 2    | 1    | 0    |

| Name    | _  | -    | -  | - | - | - | MANER | RES3 | LBIST | CVHST | RES2 | RES1 | RES0 |

| R/W     | _  | -    | -  | _ | _ | _ | R     | -    | R     | R     | -    | R    | R    |

| Value   | Х  | Х    | Х  | Х | Х | Х | 0/1   | -    | 0/1   | 0/1   | -    | 0/1  | 0/1  |

| Reset   | 0  | 0    | 0  | 0 | 0 | 0 | 0     | _    | 0     | 0     | -    | 0    | 1    |

Error register. Indicates various current error conditions. When set, can only be cleared via the CTRL register ERST field, hard reset, or power-on reset (see BATD for exception). If any of the error bits are asserted, the error flag on the serial interface will be asserted. Masking an error bit will prevent the bit from asserting the serial interface error flag, but the error bit may still be asserted in this register.

### MANER [6] Manchester/SENT Error Flag

Indicates Manchester/SENT Error.

| Bit | Value | Description                  |  |

|-----|-------|------------------------------|--|

| 6   | 0     | Error condition not present. |  |

| 1   |       | Error condition present.     |  |

**RES2 [2] Factory Reserved Bit**

**RES1 [1] Factory Reserved Bit**

**RES0 [0] Factory Reserved Bit**

### **RES3** [5] Factory Reserved Bit

### LBIST [4] LBIST Error Flag

This bit indicates that the Logic Built-In Self-Test (LBIST) failed.

| Bit | Value | Description                  |

|-----|-------|------------------------------|

| 4   | 0     | Error condition not present. |

| 4   | 1     | Error condition present.     |

### **CVHST [3] Circular Vertical Hall Self-Test**

This bit indicates that the CVH Built-In Self-Test (CVHST) failed.

| Bit | Value | Description                  |

|-----|-------|------------------------------|

| 2   | 0     | Error condition not present. |

| 3   | 1     | Error condition present.     |

#### CTRL (Control) Register

Address: 0x08

| Address | 0x08 |   |   |      |      |     |      |      |

|---------|------|---|---|------|------|-----|------|------|

| Bit     | 7    | 6 | 5 | 4    | 3    | 2   | 1    | 0    |

| Name    | -    | _ | _ | STST | RES1 | RPM | RES0 | ERST |

| R/W     | _    | _ | _ | RW1C | _    | R/W | R/W  | RW1C |

| Value   | X    | X | X | X    | X    | 0/1 | 0/1  | 0/1  |

| Reset   | 0    | 0 | 0 | 0    | 0    | 0   | 0    | 0    |

Initialization and operation configuration control command settings.

RW1C: When a 1 is written to the field, the command is immediately executed, and the value returns to zero. When Reading the field, this type of field will always read back 0.

### STS [4] Self-Test Start

Commands the A1338 to begin Self-Test(s).

Which self-test is run, is determined by the U\_INIT\_ST field within EEPROM. There are two self-tests:

- 1. Logic Built-In Self-Test (LBIST): Verifies digital gate integrity. This is a modified version of digital scan testing. Requires approximately 10 ms to run during which time no angle readings can take place

- CVH Self-Test: Test of the front end transducer and signal path. Requires approximately 40 ms to compete, during which time angle readings are not available.

| Bit | Value | Description                                                                              |  |

|-----|-------|------------------------------------------------------------------------------------------|--|

|     | 0     | Does not trigger Self-Test.                                                              |  |

| 4   | 1     | Self-Test is triggered based on pre-selected options in the "U_INIT_ST" field of EEPROM. |  |

### RES0 [1] Reserved

#### **ERST [0] Error Flags Reset**

A feature to clear the values in the ERR register (0x04).

| Bit | Value | Description               |  |

|-----|-------|---------------------------|--|

| 0   | 0     | ERR register not cleared. |  |

| 0   | 1     | ERR register cleared.     |  |

### RES1 [3] Reserved

### RPM [2] RPM Operating Mode (see Programming Manual)

This field is populated on power-up by the EEPROM field RPMD. This field can be written during operation to temporarily override the EEPROM. On the next power cycle, this field will reset to the value determined by the EEPROM field RPMD. This bit must be a '1' to enable internal averaging.

| Bit | Value | Description                     |  |

|-----|-------|---------------------------------|--|

| 2   | 0     | Internal Averaging not allowed. |  |

| 2 1 |       | Internal Averaging allowed.     |  |

Figure 14: User-Interface Diagnostic Diagram

### **APPLICATION INFORMATION**

### **Serial Interface Description**

The A1338 features SPI, SENT, and PWM interfaces. The following figures show some typical application circuits for using the A1338 with these interfaces.

### **Calculating Target Zero-Degree Angle**

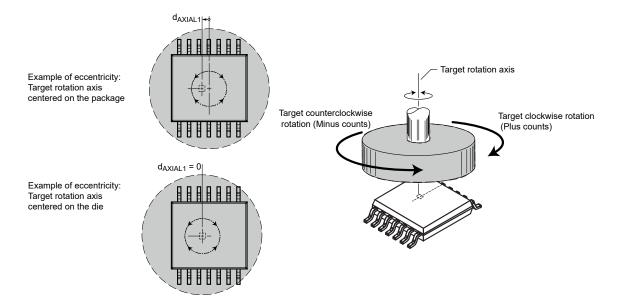

When shipped from the factory, the default angle value when oriented as shown in Figure 15, is approximately 21°. In some cases, the end user may want to program an angle offset in the A1338 to compensate for variation in magnetic assemblies, or for applications where absolute system level readings are required.

The internal algorithm for computing the output angle is as follows:

$$Angle_{OUT} = Angle_{RAW} - Reference Angle$$

. (3)

The procedure to "zero out" the A1338 is quite simple. During final application calibration and programming, position the magnet above the A1338 in the required zero-degree posi-

tion, and read the angle from the A1338 using the SPI interface (Angle<sub>OUT</sub>). From this angle, the Reference Angle required to program the A1338 can be computed as follows:

$$Reference\ Angle = Angle_{OUT}$$

. (4)

### **Bypass Pins Usage**

The bypass pins are required for proper operation of the device. A  $0.1~\mu F$  capacitor should be placed in very close proximity to each of the bypass pins.

When using the SPI communication protocol, the A1338 has the ability to support host microcontroller inputs with Voltage Input High ( $V_{\rm IH}$ ) thresholds of 2 V (minimum). This option only requires BYP1 to be populated with a 0.1  $\mu F$  capacitor.

By using an optional second bypass capacitor on the BYP2 pins, the A1338 can also support host microcontroller inputs with Voltage Input High ( $V_{IH}$ ) thresholds of 2.5 V (minimum). This option requires that both BYP1 and BYP2 pins be populated with 0.1  $\mu$ F capacitors, and that the appropriate EEPROM configuration bit

Target alignment for default angle setting

• Target rotation axis intersects the die

• Sets die 21° default point

(Example shows the die as element E1)

Figure 15: Orientation of Magnet Relative to Die

Figure 16: Hall Element Located Off-Center within the Device Body

(refer to the Package Outline Drawing for reference dimensions)

be enabled. Contact Allegro for availability of parts with elevated SPI output levels.

The bypass pins are not intended to be used to source external components. To assist with PCB layout, see the Operating Characteristics table for output voltage and current requirements.

### **Changing Sampling Modes**

The A1338 features a High RPM sampling mode and a Low RPM sampling mode. The default power-on state of the A1338 is loaded from EEPROM. To configure the A1338 to Low RPM mode, set the Operating mode to Low RPM mode by writing a logic 1 to bit 2 (RPM) of the configuration commands (CTRL) register, via the SPI interface.

### **Magnetic Target Requirements**

The A1338 is designed to operate with magnets constructed with a variety of magnetic materials, cylindrical geometries, and field strengths, as shown in Table 8. Contact Allegro for more detailed information on magnet selection and theoretical error.

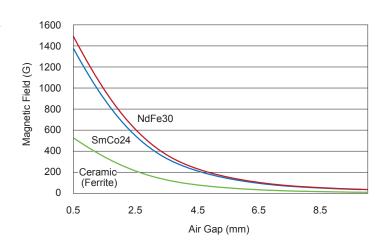

Figure 17: Magnetic Field versus Air Gap for a magnet 6 mm in diameter and 2.5 mm thick.