Rev. 3.2 — 26 March 2014 224632

Product data sheet COMPANY PUBLIC

## 1. Introduction

The PT501 is a highly integrated frontend IC for applications at 13.56 MHz, acting as a card emulator over ISO/IEC 14443-A and FeliCa compliant protocols as well as a passive target IC in the NFC peer-to-peer IP-1 mode.

## 2. General description

The PT501 is a generic 13.56 MHz communication interface, this transceiver IC can be operated in two operating modes:

- Passive target device for NFC peer-to-peer IP-1 mode communication

- Card emulation mode supporting ISO/IEC 14443-A and FeliCa compliant protocol

In card emulation mode, the PT501 transceiver IC is able to answer to a reader/writer command either according to the ISO/IEC 14443A/MIFARE or FeliCa card interface scheme.

Additionally, the PT501 transceiver IC offers the possibility to communicate directly to an NFCIP-1 device in the NFC peer-to-peer passive target mode. The NFCIP-1 mode offers different communication mode and transfer speeds up to 424 kbit/s according to Ecma 340 and ISO/IEC 18092 NFCIP-1 standards.

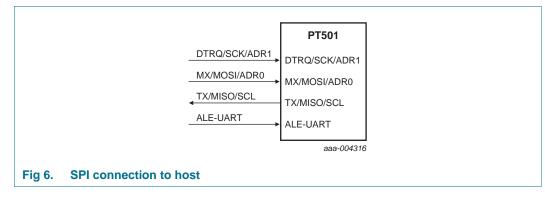

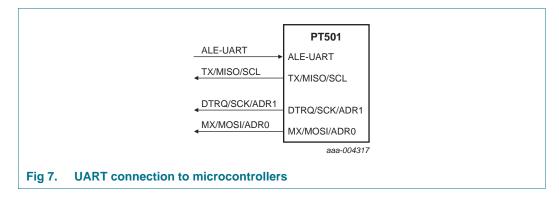

Various host controller interfaces are implemented:

- SPI interface

- Serial UART (similar to RS232 with voltage levels according pad voltage supply)

- I<sup>2</sup>C interface.

## 3. Features and benefits

- Highly integrated analog circuitry to demodulate and decode responses

- Buffered output drivers for connecting an antenna with the minimum number of external components

- Integrated RF level detector

- Integrated data mode detector

- ISO/IEC 14443A higher transfer speed communication at 106 kbit/s

- Contactless communication according to the FeliCa scheme at 212 kbit/s and 424 kbit/s

- Integrated RF interface for NFC peer-to-peer passive target NFCIP-1 up to 424 kbit/s

- Additional power supply to directly supply the smart card IC connected via S2C

- Supported host interfaces

- SPI up to 10 Mbit/s

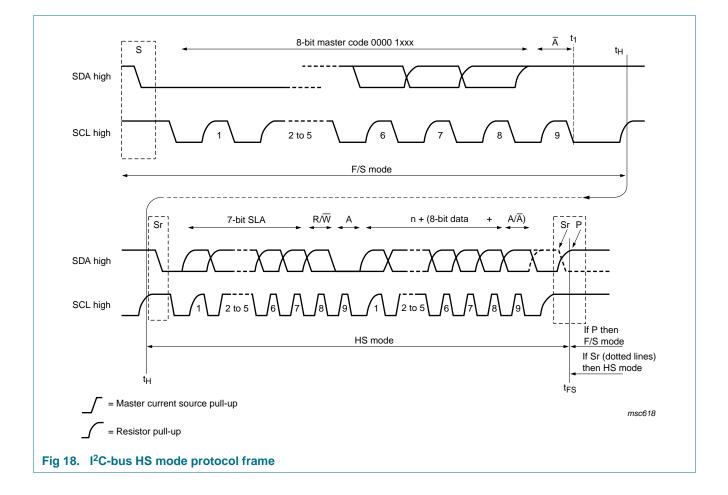

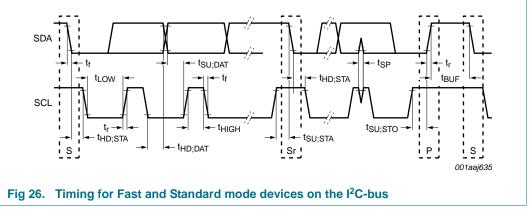

- ◆ I<sup>2</sup>C-bus interface up to 400 kBd in Fast mode, up to 3400 kBd in High-speed mode

- RS232 Serial UART up to 1228.8 kBd, with voltage levels dependent on pin voltage supply

- FIFO buffer handles 64 byte send and receive

- Flexible interrupt modes

- Hard reset with low power function

- Power-down mode per software

- Programmable timer

- 2.5 V to 3.6 V power supply

- CRC coprocessor

- Programmable I/O pins

- Internal self-test

## 4. Quick reference data

| Table I.              |                                     |                                                                                            |                                                       |     |     |     |      |  |  |  |

|-----------------------|-------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------|-----|-----|-----|------|--|--|--|

| Symbol Parameter      |                                     | Conditions                                                                                 |                                                       |     |     | Max | Unit |  |  |  |

| V <sub>DDA</sub>      | analog supply voltage               | $V_{DD(PVDD)} \le V_{DDA} = V_{DDD} = V_{DD(TVDD)};$                                       | <u>[1][2]</u>                                         | 2.5 | -   | 3.6 | V    |  |  |  |

| V <sub>DDD</sub>      | digital supply voltage              | $V_{SSA} = V_{SSD} = V_{SS(PVSS)} = V_{SS(TVSS)} = 0 V$                                    | $_{SA} = V_{SSD} = V_{SS(PVSS)} = V_{SS(TVSS)} = 0 V$ |     |     |     |      |  |  |  |

| V <sub>DD(TVDD)</sub> | TVDD supply voltage                 | _                                                                                          |                                                       |     |     |     |      |  |  |  |

| V <sub>DD(PVDD)</sub> | PVDD supply voltage                 |                                                                                            | <u>[3]</u>                                            | 1.6 | -   | 3.6 | V    |  |  |  |

| V <sub>DD(SVDD)</sub> | SVDD supply voltage                 | $V_{SSA} = V_{SSD} = V_{SS(PVSS)} = V_{SS(TVSS)} = 0 V$                                    |                                                       | 1.6 | -   | 3.6 | V    |  |  |  |

| I <sub>pd</sub>       | power-down current                  | $V_{DDA} = V_{DDD} = V_{DD(TVDD)} = V_{DD(PVDD)} = 3 V$                                    |                                                       |     | -   |     |      |  |  |  |

|                       | hard power-down; pin NRSTPD set LOW | <u>[4]</u>                                                                                 | -                                                     | -   | 5   | μΑ  |      |  |  |  |

|                       |                                     | soft power-down; RF level detector on                                                      | <u>[4]</u>                                            | -   | -   | 10  | μA   |  |  |  |

| I <sub>DDD</sub>      | digital supply current              | pin DVDD; V <sub>DDD</sub> = 3 V                                                           |                                                       | -   | 6.5 | 9   | mA   |  |  |  |

| I <sub>DDA</sub>      | analog supply current               | pin AVDD; $V_{DDA} = 3 V$ , CommandReg register's<br>RcvOff bit = 0                        |                                                       | -   | 7   | 10  | mA   |  |  |  |

|                       |                                     | pin AVDD; receiver switched off; $V_{DDA} = 3 V$ ,<br>CommandReg register's RcvOff bit = 1 |                                                       | -   | 3   | 5   | mA   |  |  |  |

| I <sub>DD(PVDD)</sub> | PVDD supply current                 | pin PVDD                                                                                   | <u>[5]</u>                                            | -   | -   | 40  | mA   |  |  |  |

| T <sub>amb</sub>      | ambient temperature                 | HVQFN32                                                                                    |                                                       | -30 | -   | +85 | °C   |  |  |  |

[1] Supply voltages below 3 V reduce the performance in, for example, the achievable operating distance.

[2]  $V_{DDA}$ ,  $V_{DDD}$  and  $V_{DD(TVDD)}$  must always be the same voltage.

[3]  $V_{DD(PVDD)}$  must always be the same or lower voltage than  $V_{DDD}$ .

[4] I<sub>pd</sub> is the total current for all supplies.

[5]  $I_{DD(PVDD)}$  depends on the overall load at the digital pins.

## 5. Ordering information

| Table 2. Ordering information |         |                                                                                                               |          |  |  |  |

|-------------------------------|---------|---------------------------------------------------------------------------------------------------------------|----------|--|--|--|

| Type number                   | Package |                                                                                                               |          |  |  |  |

|                               | Name    | Description                                                                                                   | Version  |  |  |  |

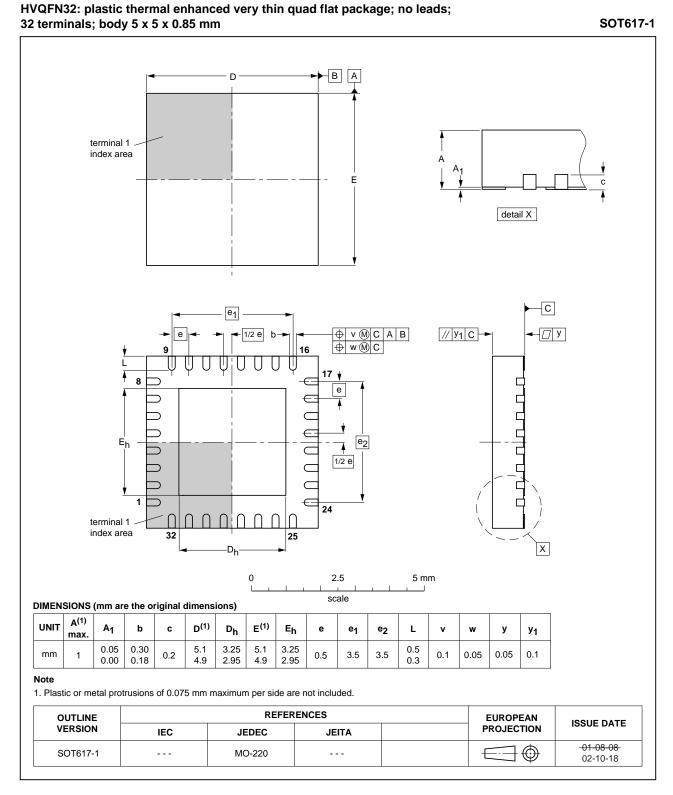

| PT5010A0HN/C1                 | HVQFN32 | plastic thermal enhanced very thin quad flat package; no leads; 32 terminal; body $5 \times 5 \times 0.85$ mm | SOT617-1 |  |  |  |

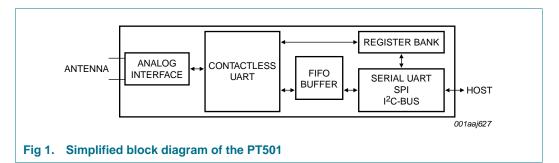

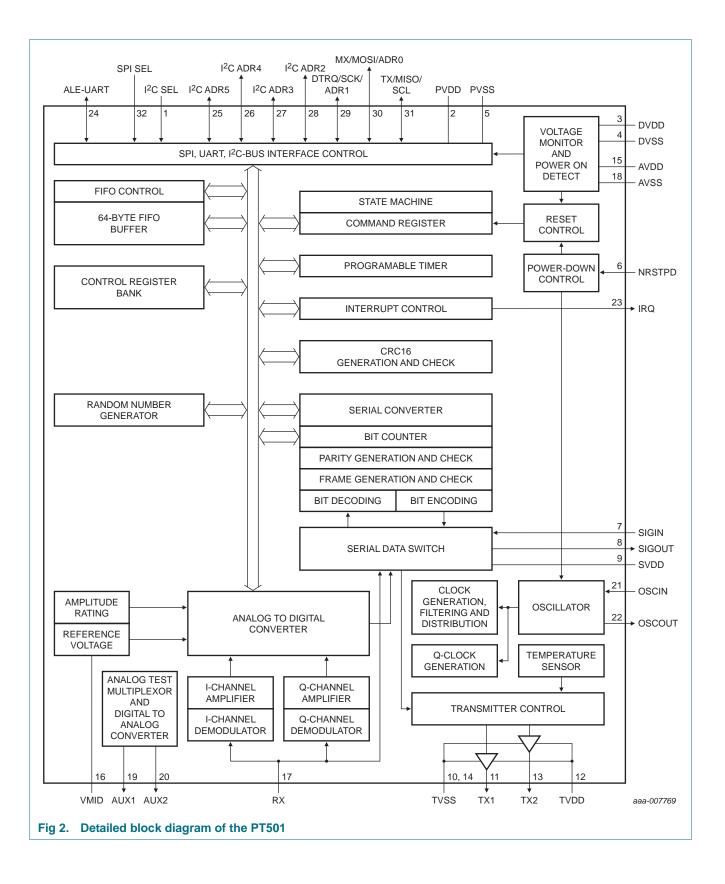

## 6. Block diagram

The analog interface handles the modulation and demodulation of the analog signals according to the Card operation mode and NFCIP-1 mode communication scheme.

The RF level detector detects the presence of an external RF-field delivered by the antenna to the RX pin.

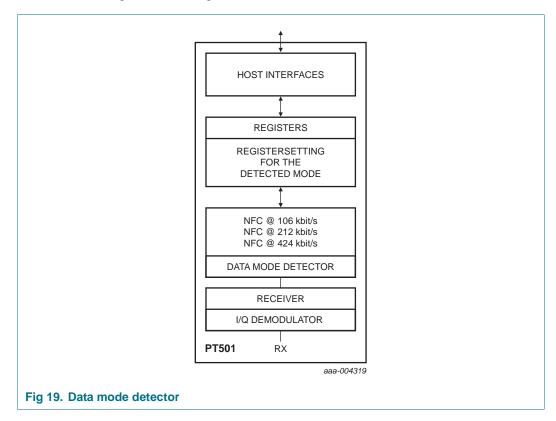

The Data mode detector detects a ISO/IEC 14443-A, FeliCa or NFCIP-1 mode in order to prepare the internal receiver to demodulate signals, which are sent to the PT501.

The communication (S<sup>2</sup>C) interface provides digital signals to support communication for transfer speeds above 424 kbit/s and digital signals to communicate to a secure IC.

The contactless UART manages the protocol requirements for the communication protocols in cooperation with the host. The FIFO buffer ensures fast and convenient data transfer to and from the host and the contactless UART and vice versa.

Various host interfaces are implemented to meet different customer requirements.

## **NXP Semiconductors**

# **PT501**

#### Universal NFC card emulation and NFC peer-to-peer solution

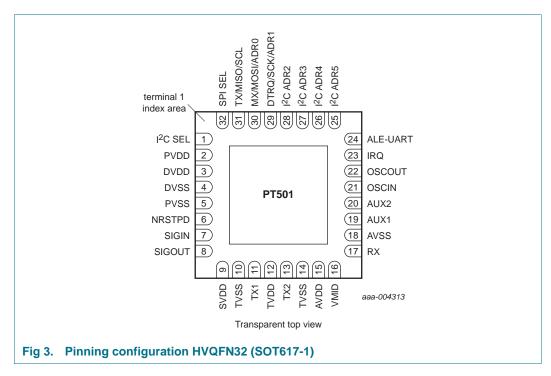

## 7. Pinning information

## 7.1 Pinning

## Universal NFC card emulation and NFC peer-to-peer solution

## 7.2 Pin description

| Pin | Symbol                | Туре | Description                                                                                                                                                                                                                                    |

|-----|-----------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | I <sup>2</sup> CSEL   | I    | Address Line, see Table 110 on page 47                                                                                                                                                                                                         |

| 2   | PVDD                  | PWR  | Pad power supply                                                                                                                                                                                                                               |

| 3   | DVDD                  | PWR  | Digital Power Supply                                                                                                                                                                                                                           |

| 4   | DVSS                  | PWR  | Digital Ground                                                                                                                                                                                                                                 |

| 5   | PVSS                  | PWR  | Pad power supply ground                                                                                                                                                                                                                        |

| 6   | NRSTPD                | I    | <b>Not Reset and Power Down:</b> When LOW, internal current sinks are switched off, the oscillator is inhibited, and the input pads are disconnected from the outside world. With a positive edge on this pin the internal reset phase starts. |

| 7   | SIGIN                 | I    | Communication Interface Input: accepts a digital, serial data stream                                                                                                                                                                           |

| 8   | SIGOUT                | 0    | Communication Interface Output: delivers a serial data stream                                                                                                                                                                                  |

| 9   | SVDD                  | PWR  | S2C Pad Power Supply: provides power to the S <sup>2</sup> C pads                                                                                                                                                                              |

| 10  | TVSS                  | PWR  | Transmitter Ground: supplies the output stage of TX1 and TX2                                                                                                                                                                                   |

| 11  | TX1                   | 0    | Transmitter 1: modulates the 13.56 MHz energy carrier                                                                                                                                                                                          |

| 12  | TVDD                  | PWR  | Transmitter Power Supply: supplies the output stage of TX1 and TX2                                                                                                                                                                             |

| 13  | TX2                   | 0    | Transmitter 2: modulates the 13.56 MHz energy carrier                                                                                                                                                                                          |

| 14  | TVSS                  | PWR  | Transmitter Ground: supplies the output stage of TX1 and TX2                                                                                                                                                                                   |

| 15  | AVDD                  | PWR  | Analog Power Supply                                                                                                                                                                                                                            |

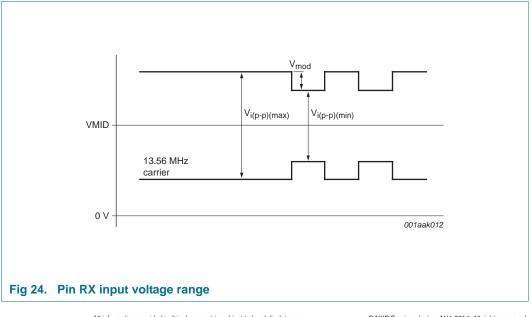

| 16  | VMID                  | PWR  | Internal Reference Voltage: This pin delivers the internal reference voltage.                                                                                                                                                                  |

| 17  | RX                    | I    | Receiver Input                                                                                                                                                                                                                                 |

| 18  | AVSS                  | PWR  | Analog Ground                                                                                                                                                                                                                                  |

| 19  | AUX1                  | 0    | Auxiliary Outputs: These pins are used for testing.                                                                                                                                                                                            |

| 20  | AUX2                  | 0    |                                                                                                                                                                                                                                                |

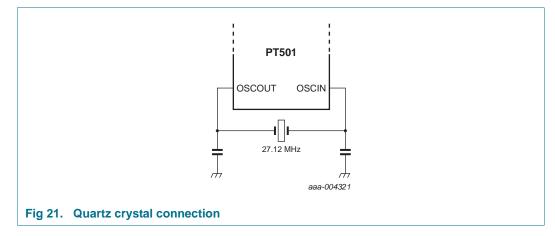

| 21  | OSCIN                 | I    | <b>Crystal Oscillator Input:</b> input to the inverting amplifier of the oscillator. This pin is also the input for an externally generated clock (27.12 MHz = $f_{osc}$ ).                                                                    |

| 22  | OSCOUT                | 0    | Crystal Oscillator Output: Output of the inverting amplifier of the oscillator.                                                                                                                                                                |

| 23  | IRQ                   | 0    | Interrupt Request: output to signal an interrupt event                                                                                                                                                                                         |

| 24  | ALE-UART              | I    | Address Latch Enable: signal to latch AD0 to AD5 into the internal address latch when HIGH.                                                                                                                                                    |

| 25  | I <sup>2</sup> C ADR5 | I/O  | see Table 110 on page 47                                                                                                                                                                                                                       |

| 26  | I <sup>2</sup> C ADR4 | I/O  | see Table 110 on page 47                                                                                                                                                                                                                       |

| 27  | I <sup>2</sup> C ADR3 | I/O  | see Table 110 on page 47                                                                                                                                                                                                                       |

| 28  | I <sup>2</sup> C ADR2 | I/O  | see Table 110 on page 47                                                                                                                                                                                                                       |

| 29  | DTRQ/SCK/ADR1         | I/O  | see Table 110 on page 47                                                                                                                                                                                                                       |

| 30  | MX/MOSI/ADR0          | I/O  | see Table 110 on page 47                                                                                                                                                                                                                       |

| 31  | TX/MISO/SCL           | I/O  | see Table 110 on page 47                                                                                                                                                                                                                       |

| 32  | SPI SEL               | I    | Address Line                                                                                                                                                                                                                                   |

## 8. Functional description

PT501 transceiver IC supports the following operating modes:

- Card Operation mode supporting ISO/IEC 14443A/MIFARE and FeliCa scheme

- NFCIP-1 mode

The modes support different transfer speeds and modulation schemes. The following chapters will explain the different modes in detail.

All indicated modulation indices and modes in this chapter are system parameters. This means that beside the IC settings a suitable antenna tuning is required to achieve the optimum performance.

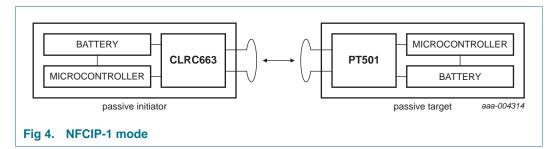

## 8.1 NFCIP-1 mode

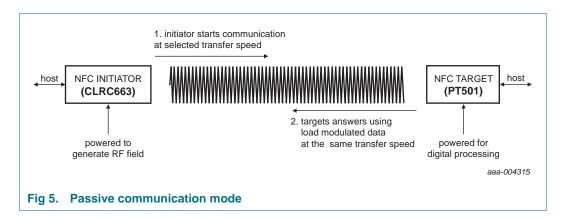

The NFCIP-1 communication differentiates between an active and a passive Communication mode.

- Active Communication mode means both the initiator and the target are using their own RF field to transmit data.

- Passive Communication mode means that the target answers to an initiator command in a load modulation scheme. The initiator is active in terms of generating the RF field.

- Initiator: generates RF field at 13.56 MHz and starts the NFCIP-1 communication

- Target: responds to initiator command either in a load modulation scheme in Passive Communication mode or using a self generated and self modulated RF field for Active Communication mode.

The PT501 only supports the Passive Communication Mode as a Target and can use transfer speeds at 106 kbit/s, 212 kbit/s and 424 kbit/s.

Passive Communication mode means that the target (PT501) answers to an initiator command in a load modulation scheme. The initiator (e.g. CLRC663) is generating the RF field.

1501

#### Table 4. Communication overview for Passive communication mode

| Communication direction        | 106 kbit/s                                                               | 212 kbit/s                                          | 424 kbit/s |

|--------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------|------------|

| Initiator $\rightarrow$ Target | According to ISO/IEC 14443A 100<br>% ASK, Modified Miller Coded          | According to FeliCa, 8-30 %<br>ASK Manchester Coded |            |

| Target $\rightarrow$ Initiator | According to ISO/IEC 14443A subcarrier load modulation, Manchester Coded | According to Fel<br>ASK Mancheste                   |            |

The contactless UART of PT501 and a dedicated host controller are required to handle the NFCIP-1 protocol.

Transfer Speeds above 424 kbit/s are not defined in the NFCIP-1 standard.

## 8.1.1 NFCIP-1 framing and coding

#### Table 5. Framing and coding overview

| Transfer speed | Framing and Coding                            |

|----------------|-----------------------------------------------|

| 106 kbit/s     | According to the ISO/IEC 14443A/MIFARE scheme |

| 212 kbit/s     | According to the FeliCa scheme                |

| 424 kbit/s     | According to the FeliCa scheme                |

## 8.1.2 NFCIP-1 protocol support

The NFCIP-1 protocol is not completely described in this document. For detailed explanation of the protocol refer to the NFCIP-1 standard. However the datalink layer is according to the following policy:

- Speed shall not be changed while continuum data exchange in a transaction.

- Transaction includes initialization and anticollision methods and data exchange (in continuous way, meaning no interruption by another transaction).

## 8.2 Card operation mode

The PT501 offers the possibility to operate as an active card. The card supports the ISO/IEC 14443-A as well as the FeliCa compliant protocol.

## 8.3 ISO/IEC 14443-A Card operation mode

### Table 6. ISO/IEC 14443-A Card operation mode

| Communication direction           |                           | ISO/IEC 14443A/ MIFARE     |

|-----------------------------------|---------------------------|----------------------------|

|                                   | transfer speed            | 106 kbit/s                 |

| reader/writer $\rightarrow$ PT501 | Modulation on reader side | 100 % ASK                  |

|                                   | bit coding                | Modified Miller            |

|                                   | Bitlength                 | (128/13.56) μs             |

| $PT501 \rightarrow reader/writer$ | Modulation on PT501 side  | subcarrier load modulation |

|                                   | subcarrier frequency      | 13.56 MHz/16               |

|                                   | bit coding                | Manchester coding          |

As the PT501 does not have a UID as defined in ISO/IEC 14443, it is not possible to emulate any cards with Unique Identifier. The product has no CRYPTO1 implemented, as such the emulation of a e.g. MIFARE Classic is not possible.

## 8.4 FeliCa Card operation mode

## Table 7. FeliCa Card operation mode

| Communication direction            |                               | FeliCa                     | FeliCa Higher<br>transfer speeds |

|------------------------------------|-------------------------------|----------------------------|----------------------------------|

|                                    | Transfer speed                | 212 kbit/s                 | 424 kbit/s                       |

| reader/writer $\rightarrow$        | Modulation on reader side     | 8-30 % ASK                 | 8-30 % ASK                       |

| PT501                              | bit coding                    | Manchester Coding          | Manchester Coding                |

|                                    | Bitlength                     | (64/13.56) μs              | (32/13.56) μs                    |

| $PT501 \rightarrow reader/$ writer | Load modulation on PT501 side | > 12 % ASK load modulation | > 12 % ASK load modulation       |

|                                    | bit coding                    | Manchester coding          | Manchester coding                |

# 9. PT501 register SET

## 9.1 PT501 registers overview

#### Table 8. PT501 registers overview

| Addr<br>(hox) | Register Name  | Function                                                                           |  |  |

|---------------|----------------|------------------------------------------------------------------------------------|--|--|

| (hex)         | nd and Status  |                                                                                    |  |  |

|               | RFU            | Deserved for Euture Lies                                                           |  |  |

| 00            | _              | Reserved for Future Use                                                            |  |  |

| 01            |                | Starts and stops command execution                                                 |  |  |

| 02            | CommlEnReg     | Controls bits to enable and disable the passing of Interrupt Requests              |  |  |

| 03            | DivlEnReg      | Controls bits to enable and disable the passing of Interrupt<br>Requests           |  |  |

| 04            | CommIRqReg     | Contains Interrupt Request bits                                                    |  |  |

| 05            | DivIRqReg      | Contains Interrupt Request bits                                                    |  |  |

| 06            | ErrorReg       | Error bits showing the error status of the last command executed                   |  |  |

| 07            | Status1Reg     | Contains status bits for communication                                             |  |  |

| 08            | Status2Reg     | Contains status bits of the receiver and transmitter                               |  |  |

| 09            | FIFODataReg    | In- and output of 64 byte FIFO-buffer                                              |  |  |

| 0A            | FIFOLevelReg   | Indicates the number of bytes stored in the FIFO                                   |  |  |

| 0B            | WaterLevelReg  | Defines the level for FIFO under- and overflow warning                             |  |  |

| 0C            | ControlReg     | Contains miscellaneous Control Registers                                           |  |  |

| 0D            | RFU            | Reserved for future use                                                            |  |  |

| 0E            | CollReg        | Defines the first bit collision detected on the RF interface                       |  |  |

| 0F            | RFU            | Reserved for future use                                                            |  |  |

| Comma         | nd             |                                                                                    |  |  |

| 10            | RFU            | Reserved for Future Use                                                            |  |  |

| 11            | ModeReg        | Defines general modes for transmitting and receiving                               |  |  |

| 12            | TxModeReg      | Defines the data rate and framing during transmission                              |  |  |

| 13            | RxModeReg      | Defines the data rate and framing during receiving                                 |  |  |

| 14            | TxControlReg   | Controls the logical behavior of the antenna driver pins TX1 and TX2               |  |  |

| 15            | TxAutoReg      | Controls the setting of the antenna drivers                                        |  |  |

| 16            | TxSelReg       | Selects the internal sources for the antenna driver                                |  |  |

| 17            | RxSelReg       | Selects internal receiver settings                                                 |  |  |

| 18            | RxThresholdReg | Selects thresholds for the bit decoder                                             |  |  |

| 19            | DemodReg       | Defines demodulator settings                                                       |  |  |

| 1A            | RFU            | Reserved for Future Use                                                            |  |  |

| 1B            | FelNFC2Reg     | Defines the length of the valid range for the receive package                      |  |  |

| 1C            | MifNFCReg      | Controls the communication in ISO/IEC 14443/MIFARE and NFC target mode at 106 kbit |  |  |

| 1D            | ManualRCVReg   | Allows manual fine tuning of the internal receiver                                 |  |  |

| 1E            | RFU            | Reserved for Future Use                                                            |  |  |

Product data sheet COMPANY PUBLIC

PT501

© NXP Semiconductors N.V. 2014. All rights reserved.

| Addr<br>(hex) | Register Name Function |                                                                                                   |  |  |

|---------------|------------------------|---------------------------------------------------------------------------------------------------|--|--|

| 1F            | SerialSpeedReg         | Selects the speed of the serial UART interface                                                    |  |  |

| Config        | uration                |                                                                                                   |  |  |

| 20            | RFU                    | Reserved for Future Use                                                                           |  |  |

| 21            | CRCResultReg           | Shows the actual MSB and LSB values of the CRC calculation                                        |  |  |

| 22            |                        |                                                                                                   |  |  |

| 23            | GsNOffReg              | Selects the conductance of the antenna driver pins TX1 and TX2 for modulation, shall be set to 3F |  |  |

| 24            | RFU                    | Reserved for Future Use                                                                           |  |  |

| 25            | TxBitPhaseReg          | Adjust the TX bit phase at 106 kbit                                                               |  |  |

| 26            | RFCfgReg               | Configures the receiver gain and RF level, sets delay of the load maximum carrier modulation      |  |  |

| 27            | RFU                    | Reserved for Future Use                                                                           |  |  |

| 28            | RFU                    | Reserved for Future Use                                                                           |  |  |

| 29            | RFU                    | Reserved for Future Use                                                                           |  |  |

| 2A            | TModeReg               | Defines settings for the internal timer                                                           |  |  |

| 2B            | TPrescalerReg          |                                                                                                   |  |  |

| 2C            | TReloadReg             | Describes the 16-bit timer reload value                                                           |  |  |

| 2D            |                        |                                                                                                   |  |  |

| 2E            | TCounterValReg         | Shows the 16-bit actual timer value                                                               |  |  |

| 2F            |                        |                                                                                                   |  |  |

| TestRe        | gister                 |                                                                                                   |  |  |

| 30            | RFU                    | Reserved for Future Use                                                                           |  |  |

| 31            | TestSel1Reg            | General test signal configuration                                                                 |  |  |

| 32            | TestSel2Reg            | General test signal configuration and PRBS control                                                |  |  |

| 33            | TestPinEnReg           |                                                                                                   |  |  |

| 34            | RFU                    | Reserved for Future Use                                                                           |  |  |

| 35            | TestBusReg             | Shows the status of the internal testbus                                                          |  |  |

| 36            | AutoTestReg            | Controls the digital selftest                                                                     |  |  |

| 37            | VersionReg             | Shows the version                                                                                 |  |  |

| 38            | AnalogTestReg          | Controls the pins AUX1 and AUX2                                                                   |  |  |

| 39            | TestDAC1Reg            | Defines the test value for the TestDAC1                                                           |  |  |

| 3A            | TestDAC2Reg            | Defines the test value for the TestDAC2                                                           |  |  |

| 3B            | TestADCReg             | Shows the actual value of ADC I and Q                                                             |  |  |

| 3C-F          | RFTReg                 | Reserved for production tests                                                                     |  |  |

Table 8.

PT501 registers overview ...continued

## 9.1.1 Register bit behavior

Depending on the functionality of a register, the access conditions and value to the register can vary. In principle bits with same behavior are grouped in common registers. In Table 9 the access conditions are described.

| Abbreviation | Behavior       | Description                                                                                                                                                                                                                                                                                                                                    |

|--------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| r/w          | read and write | These bits can be written and read by the $\mu$ -Controller. Since<br>they are used only for control means, there content is not<br>influenced by internal state machines, e.g. the<br>PageSelect-Register may be written and read by the<br>$\mu$ -Controller. It will also be read by internal state machines, but<br>never changed by them. |

| dy           | dynamic        | These bits can be written and read by the $\mu$ -Controller.<br>Nevertheless, they may also be written automatically by internal state machines, e.g. the Command-Register changes its value automatically after the execution of the actual command.                                                                                          |

| r            | read only      | These registers hold bits, which value is determined by internal states only, e.g. the CRCReady bit can not be written from external but shows internal states.                                                                                                                                                                                |

| w            | write only     | Reading these registers returns always ZERO.                                                                                                                                                                                                                                                                                                   |

| -            | not defined    | Access is not defined.                                                                                                                                                                                                                                                                                                                         |

| RFU          | -              | These registers are reserved for future use.<br>The value is not fixed.                                                                                                                                                                                                                                                                        |

| RFT          | -              | These registers are reserved for production tests and shall not be changed.                                                                                                                                                                                                                                                                    |

Table 9.

Behavior of register bits and its designation

## 9.2 Register description

## 9.2.1 Command and status

## 9.2.1.1 CommandReg

Starts and stops command execution.

## Table 10. CommandReg register (address 01h); reset value: 20h, 00100000b

|                  | 7 | 6 | 5      | 4          | 3  | 2    | 1    | 0  |

|------------------|---|---|--------|------------|----|------|------|----|

|                  | 0 | 0 | RcvOff | Power Down |    | Comr | mand |    |

| Access<br>Rights | - | - | r/w    | dy         | dy | dy   | dy   | dy |

## Table 11. Description of CommandReg bits

| Bit    | Symbol    | Description                                                                                                                                                                                              |

|--------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 to 6 | -         | Reserved for future use.                                                                                                                                                                                 |

| 5      | RcvOff    | Set to 1, the analog part of the receiver is switched off.                                                                                                                                               |

| 4      | PowerDown | Set to 1, Soft Power-down mode is entered.                                                                                                                                                               |

|        |           | Set to 0, the PT501 starts the wake up procedure. During this procedure this bit still shows a 1. A 0 indicates that the PT501 is ready for operations; see <u>Section 15.2 "Soft power-down mode"</u> . |

|        |           | Note: The bit Power Down cannot be set, when the command SoftReset has been activated.                                                                                                                   |

| 3 to 0 | Command   | Activates a command according to the Command Code. Reading this register shows, which command is actually executed (see <u>Section 18.3</u> "PT501 command overview").                                   |

## 9.2.1.2 CommlEnReg

Control bits to enable and disable the passing of interrupt requests.

## Table 12. CommIEnReg register (address 02h); reset value: 80h, 1000000b

|                  | 7      | 6     | 5     | 4       | 3          | 2          | 1      | 0        |

|------------------|--------|-------|-------|---------|------------|------------|--------|----------|

|                  | IRqInv | TxlEn | RxIEn | IdleIEn | HiAlertIEn | LoAlertIEn | ErrlEn | TimerIEn |

| Access<br>Rights | r/w    | r/w   | r/w   | r/w     | r/w        | r/w        | r/w    | r/w      |

#### Table 13. Description of CommIEnReg bits

| Bit | Symbol  | Description                                                                                                                                                                                                                                                                                  |

|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | IRqInv  | Set to 1, the signal on pin IRQ is inverted with respect to bit IRq in the register Status1Reg. Set to 0, the signal on pin IRQ is equal to bit IRq. In combination with bit IRqPushPull in register DivIEnReg, the default value of 1 ensures, that the output level on pin IRQ is 3-state. |

| 6   | TxIEn   | Allows the transmitter interrupt request (indicated by bit TxIRq) to be propagated to pin IRQ.                                                                                                                                                                                               |

| 5   | RxIEn   | Allows the receiver interrupt request (indicated by bit RxIRq) to be propagated to pin IRQ.                                                                                                                                                                                                  |

| 4   | IdleIEn | Allows the idle interrupt request (indicated by bit IdleIRq) to be propagated to pin IRQ.                                                                                                                                                                                                    |

Product data sheet COMPANY PUBLIC

PT501

© NXP Semiconductors N.V. 2014. All rights reserved.

Table 13.

Description of CommlEnReg bits ...continued

| Bit | Symbol     | Description                                                                                        |

|-----|------------|----------------------------------------------------------------------------------------------------|

| 3   | HiAlertIEn | Allows the high alert interrupt request (indicated by bit HiAlertIRq) to be propagated to pin IRQ. |

| 2   | LoAlertIEn | Allows the low alert interrupt request (indicated by bit LoAlertIRq) to be propagated to pin IRQ.  |

| 1   | ErrlEn     | Allows the error interrupt request (indicated by bit ErrIRq) to be propagated to pin IRQ.          |

| 0   | TimerlEn   | Allows the timer interrupt request (indicated by bit TimerIRq) to be propagated to pin IRQ.        |

## 9.2.1.3 DivlEnReg

Control bits to enable and disable the passing of interrupt requests.

### Table 14. DivIEnReg register (address 03h); reset value: 00h, 0000000b

|                  | 7           | 6 | 5 | 4           | 3       | 2      | 1       | 0        |

|------------------|-------------|---|---|-------------|---------|--------|---------|----------|

|                  | IRQPushPull | 0 | 0 | SiginActIEn | ModelEn | CRCIEn | RFOnIEn | RFOffIEn |

| Access<br>Rights | r/w         | - | - | r/w         | r/w     | r/w    | r/w     | r/w      |

## Table 15. Description of DivlEnReg bits

| Bit    | Symbol      | Description                                                                                        |  |  |  |  |  |

|--------|-------------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7      | IRQPushPull | Set to 1, the pin IRQ works as standard CMOS output pad.                                           |  |  |  |  |  |

|        |             | Set to 0, the pin IRQ works as open drain output pad.                                              |  |  |  |  |  |

| 6 to 5 | 0           | Is set to 0.                                                                                       |  |  |  |  |  |

| 4      | SiginActIEn | Allows the SIGIN active interrupt request to be propagated to pin IRQ.                             |  |  |  |  |  |

| 3      | ModelEn     | Allows the mode interrupt request (indicated by bit ModeIRq) to be propagated to pin IRQ.          |  |  |  |  |  |

| 2      | CRCIEn      | Allows the CRC interrupt request (indicated by bit CRCIRq) to be propagated to pin IRQ.            |  |  |  |  |  |

| 1      | RfOnIEn     | Allows the RF field on interrupt request (indicated by bit RfOnIRq) to be propagated to pin IRQ.   |  |  |  |  |  |

| 0      | RfOfflEn    | Allows the RF field off interrupt request (indicated by bit RfOffIRq) to be propagated to pin IRQ. |  |  |  |  |  |

## 9.2.1.4 CommIRqReg

Contains Interrupt Request bits.

#### Table 16. CommIRqReg register (address 04h); reset value: 14h, 00010100b

|                  | 7    | 6     | 5     | 4       | 3          | 2          | 1      | 0        |

|------------------|------|-------|-------|---------|------------|------------|--------|----------|

|                  | Set1 | TxlRq | RxIRq | IdleIRq | HiAlertIRq | LoAlertIRq | ErrlRq | TimerIRq |

| Access<br>Rights | w    | dy    | dy    | dy      | dy         | dy         | dy     | dy       |

#### Table 17. Description of CommlRqReg bits

All bits in the register CommIRqReg shall be cleared by software.

| Bit | Symbol     | Description                                                                                                                                                                                     |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Set1       | Set to 1, Set1 defines that the marked bits in the register CommIRqReg are set.                                                                                                                 |

|     |            | Set to 0, Set1 defines, that the marked bits in the register CommIRqReg are cleared.                                                                                                            |

| 6   | TxIRq      | Set to 1 immediately after the last bit of the transmitted data was sent out.                                                                                                                   |

| 5   | RxIRq      | Set to 1 when the receiver detects the end of a valid datastream.                                                                                                                               |

|     |            | If the bit RxNoErr in register RxModeReg is set to 1, bit RxIRq is only set to 1 when data bytes are available in the FIFO.                                                                     |

| 4   | IdleIRq    | Set to 1, when a command terminates by itself e.g. when the CommandReg changes its value from any command to the Idle Command.                                                                  |

|     |            | If an unknown command is started, the CommandReg changes its content to the idle state and the bit IdleIRq is set. Starting the Idle Command by the $\mu$ -Controller does not set bit IdleIRq. |

| 3   | HiAlertIRq | Set to 1, when bit HiAlert in register Status1Reg is set. In opposition to HiAlert, HiAlertIRq stores this event and can only be reset as indicated by bit Set1.                                |

| 2   | LoAlertIRq | Set to 1, when bit LoAlert in register Status1Reg is set. In opposition to LoAlert, LoAlertIRq stores this event and can only be reset as indicated by bit Set1.                                |

| 1   | ErrlRq     | Set to 1 if any error bit in the Error Register is set.                                                                                                                                         |

| 0   | TimerIRq   | Set to 1 when the timer decrements the TimerValue Register to zero.                                                                                                                             |

## 9.2.1.5 DivIRqReg

Contains Interrupt Request bits

#### Table 18. DivIRqReg register (address 05h); reset value: XXh, 000X00XXb

|                  | 7    | 6 | 5 | 4  | 3       | 2      | 1       | 0        |

|------------------|------|---|---|----|---------|--------|---------|----------|

|                  | Set2 | 0 | 0 | 0  | ModelRq | CRCIRq | RFOnIRq | RFOffIRq |

| Access<br>Rights | w    | - | - | dy | dy      | dy     | dy      | dy       |

#### Table 19. Description of DivIRqReg bits

All bits in the register DivIRqReg shall be cleared by software.

| Bit    | Symbol   | Description                                                                                                                                                                                                         |

|--------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | Set2     | Set to 1, Set2 defines that the marked bits in the register DivIRqReg are set.                                                                                                                                      |

|        |          | Set to 0, Set2 defines, that the marked bits in the register DivIRqReg are cleared                                                                                                                                  |

| 6 to 5 | 0        | Is set to 0.                                                                                                                                                                                                        |

| 4      | 0        | Is set to 0.                                                                                                                                                                                                        |

| 3      | ModelRq  | Set to 1, when the mode has been detected by the Data mode detector.                                                                                                                                                |

|        |          | The Data mode detector can only be activated by the AutoColl command and is terminated automatically having detected the Communication mode. The Data mode detector is automatically restarted after each RF Reset. |

| 2      | CRCIRq   | Set to 1, when the CRC command is active and all data are processed.                                                                                                                                                |

| 1      | RFOnIRq  | Set to 1, when an external RF field is detected.                                                                                                                                                                    |

| 0      | RFOffIRq | Set to 1, when a present external RF field is switched off.                                                                                                                                                         |

## 9.2.1.6 ErrorReg

Error bit register showing the error status of the last command executed.

## Table 20. ErrorReg register (address 06h); reset value: 00h, 0000000b

|                  | 7     | 6   | 5   | 4          | 3       | 2      | 1         | 0           |

|------------------|-------|-----|-----|------------|---------|--------|-----------|-------------|

|                  | WrErr | RFU | RFU | BufferOvfl | CollErr | CRCErr | ParityErr | ProtocolErr |

| Access<br>Rights | r     | r   | r   | r          | r       | r      | r         | r           |

#### Table 21. Description of ErrorReg bits

| Bit | Symbol      | Description                                                                                                                                                                                                                                                                  |

|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | WrErr       | Set to 1, when data is written into FIFO by the host controller during<br>the AutoColl command or if data is written into FIFO by the host<br>controller during the time between sending the last bit on the RF<br>interface and receiving the last bit on the RF interface. |

| 6   | RFU         | Reserved for Future Use                                                                                                                                                                                                                                                      |

| 5   | RFU         | Reserved for Future Use                                                                                                                                                                                                                                                      |

| 4   | BufferO∨fl  | Set to 1, if the host controller or a PT501's internal state machine (e.g. receiver) tries to write data into the FIFO-bufferFIFO-buffer although the FIFO-buffer is already full.                                                                                           |

| 3   | CollErr     | Set to 1, if a bit-collision is detected. It is cleared automatically at receiver start-up phase. This bit is only valid during the bitwise anticollision at 106 kbit. During communication schemes at 212 and 424 kbit this bit is always set to 1.                         |

| 2   | CRCErr      | Set to 1, if bit RxCRCEn in register RxModeReg is set and the CRC calculation fails. It is cleared to 0 automatically at receiver start-up phase.                                                                                                                            |

| 1   | ParityErr   | Set to 1, if the parity check has failed. It is cleared automatically at receiver start-up phase. Only valid for ISO/IEC 14443A or NFCIP-1 communication at 106 kbit.                                                                                                        |

| 0   | ProtocolErr | Set to 1, if one out of the following cases occur:                                                                                                                                                                                                                           |

|     |             | <ul> <li>Set to 1 if the SOF is incorrect. It is cleared automatically at<br/>receiver start-up phase. The bit is only valid for 106 kbit.</li> </ul>                                                                                                                        |

|     |             | • During the AutoColl command, bit ProtocolErr is set to 1, if the bit Initiator in register ControlReg is set to 1.                                                                                                                                                         |

|     |             | • Set to 1, if the Miller Decoder detects 2 pulses below the minimum time according to the ISO/IEC 14443A definitions.                                                                                                                                                       |

## 9.2.1.7 Status1Reg

Contains status bits of the CRC, Interrupt and FIFO-buffer.

### Table 22. Status1Reg register (address 07h); reset value: XXh, X100X01Xb

|                  | 7        | 6     | 5        | 4   | 3        | 2    | 1       | 0       |

|------------------|----------|-------|----------|-----|----------|------|---------|---------|

|                  | RFFreqOK | CRCOk | CRCReady | IRq | TRunning | RFOn | HiAlert | LoAlert |

| Access<br>Rights | r        | r     | r        | r   | r        | r    | r       | r       |

#### Table 23. Description of Status1Reg bits

| Bit | Symbol   | Description                                                                                                                                                                                                                                                                                                |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | RFFreqOK | Indicates if the frequency detected at the RX pin is in the range of 13.56 MHz.                                                                                                                                                                                                                            |

|     |          | Set to 1, if the frequency at the RX pin is in the range 12 MHz < RX pin frequency < 15 MHz.                                                                                                                                                                                                               |

|     |          | Note: The value of RFFreqOK is not defined if the external RF frequency is in the range from 9 to 12 MHz or in the range from 15 to 19 MHz.                                                                                                                                                                |

| 6   | CRCOk    | Set to 1, if the CRC Result is zero. For data transmission and reception the bit CRCOk is undefined (use CRCErr in register ErrorReg). CRCOk indicates the status of the CRC co-processor, during calculation the value changes to ZERO, when the calculation is done correctly, the value changes to ONE. |

| 5   | CRCReady | Set to 1, when the CRC calculation has finished. This bit is only valid for the CRC co-processor calculation using the command CalcCRC.                                                                                                                                                                    |

| 4   | IRq      | This bit shows, if any interrupt source requests attention (with respect to the setting of the interrupt enable bits, see register CommIEnReg and DivIEnReg).                                                                                                                                              |

| 3   | TRunning | Set to 1, if the PT501's timer unit is running, e.g. the timer will decrement the TCounterValReg with the next timer clock.                                                                                                                                                                                |

|     |          | Note: In the gated mode the bit TRunning is set to 1, when the timer is enabled by the register bits. This bit is not influenced by the gated signal.                                                                                                                                                      |

| 2   | RFOn     | Set to 1, if an external RF field is detected. This bit does not store the state of the RF field.                                                                                                                                                                                                          |

| 1   | HiAlert  | Set to 1, when the number of bytes stored in the FIFO-buffer fulfills the following equation: $HiAlert = (64 - FIFOLength) \le WaterLevel$<br>Example:                                                                                                                                                     |

|     |          | FIFOLength = 60, WaterLevel = $4 \rightarrow$ HiAlert = 1                                                                                                                                                                                                                                                  |

|     |          | FIFOLength = 59, WaterLevel = $4 \rightarrow$ HiAlert = 0                                                                                                                                                                                                                                                  |

| 0   | LoAlert  | Set to 1, when the number of bytes stored in the FIFO-buffer fulfills the following equation: $LoAlert = FIFOLength \leq WaterLevel$                                                                                                                                                                       |

|     |          | Example:                                                                                                                                                                                                                                                                                                   |

|     |          | $FIFOLength = 4, WaterLevel = 4 \rightarrow LoAlert = 1$                                                                                                                                                                                                                                                   |

|     |          | FIFOLength = 5, WaterLevel = $4 \rightarrow \text{LoAlert} = 0$                                                                                                                                                                                                                                            |

## 9.2.1.8 Status2Reg

Contains status bits of the Receiver, Transmitter and Data mode detector.

## Table 24. Status2Reg register (address 08h); reset value: 00h, 0000000b

|                  | 7   | 6                       | 5 | 4               | 3   | 2    | 1     | 0   |

|------------------|-----|-------------------------|---|-----------------|-----|------|-------|-----|

|                  | RFU | I <sup>2</sup> CForceHS | 0 | TargetActivated | RFU | Mode | em St | ate |

| Access<br>Rights | r/w | r/w                     | - | dy              | dy  | r    | r     | r   |

#### Table 25. Description of Status2Reg bits

| Bit    | Symbol                  | Descrip          | otion                                                                                                                                                                        |

|--------|-------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | RFU                     | Reserve          | ed for Future Use                                                                                                                                                            |

| 6      | I <sup>2</sup> CForceHS | High-sp          | It filter settings. Set to 1, the $I^2C$ input filter is set to the eed mode independent of the $I^2C$ protocol. Set to 0, the $I^2C$ er is set to the used $I^2C$ protocol. |

| 5      | 0                       | Is set to        | 0.                                                                                                                                                                           |

| 4      | TargetActivated         | Shall be         | e set to 1                                                                                                                                                                   |

| 3      | RFU                     | Reserve          | ed for Future Use                                                                                                                                                            |

| 2 to 0 | Modem State             | Modem<br>machine | State shows the state of the transmitter and receiver state es.                                                                                                              |

|        |                         | Value            | Description                                                                                                                                                                  |

|        |                         | 000              | IDLE                                                                                                                                                                         |

|        |                         | 001              | Wait for StartSend in register BitFramingReg                                                                                                                                 |

|        |                         | 010              | TxWait: Wait until RF field is present, if the bit TxWaitRF is set to 1. The minimum time for TxWait is defined by the TxWaitReg register.                                   |

|        |                         | 011              | Sending                                                                                                                                                                      |

|        |                         | 100              | RxWait: Wait until RF field is present, if the bit RxWaitRF is set to 1. The minimum time for RxWait is defined by the RxWaitReg register.                                   |

|        |                         | 101              | Wait for data                                                                                                                                                                |

|        |                         | 110              | Receiving                                                                                                                                                                    |

#### 9.2.1.9 FIFODataReg

In- and output of 64 byte FIFO-buffer.

#### Table 26. FIFODataReg register (address 09h); reset value: XXh, XXXXXXXb

|                  | 7  | 6        | 5  | 4  | 3  | 2  | 1  | 0  |

|------------------|----|----------|----|----|----|----|----|----|

|                  |    | FIFOData |    |    |    |    |    |    |

| Access<br>Rights | dy | dy       | dy | dy | dy | dy | dy | dy |

#### Table 27. Description of FIFODataReg bits

| Bit    | Symbol   | Description                                                                                                                                                             |

|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 to 0 | FIFOData | Data input and output port for the internal 64 byte FIFO-buffer. The FIFO-buffer acts as parallel in/parallel out converter for all serial data stream in- and outputs. |

## 9.2.1.10 FIFOLevelReg

Indicates the number of bytes stored in the FIFO.

#### Table 28. FIFOLevelReg register (address 0Ah); reset value: 00h, 0000000b

|                  | 7           | 6 | 5 | 4 | 3         | 2 | 1 | 0 |

|------------------|-------------|---|---|---|-----------|---|---|---|

|                  | FlushBuffer |   |   |   | FIFOLevel |   |   |   |

| Access<br>Rights | W           | r | r | r | r         | r | r | r |

#### Table 29. Description of FIFOLevelReg bits

| Bit    | Symbol      | Description                                                                                                                                                                    |

|--------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | FlushBuffer | Set to 1, this bit clears the internal FIFO-buffer's read- and write-pointer and the bit BufferOvfl in the register ErrReg immediately. Reading this bit will always return 0. |

| 6 to 0 | FIFOLevel   | Indicates the number of bytes stored in the FIFO-buffer. Writing to the FIFODataReg increments, reading decrements the FIFOLevel.                                              |

## 9.2.1.11 WaterLevelReg

Defines the level for FIFO under- and overflow warning.

#### Table 30. WaterLevelReg register (address 0Bh); reset value: 08h, 00001000b

|                  | 7 | 6 | 5   | 4   | 3     | 2     | 1   | 0   |

|------------------|---|---|-----|-----|-------|-------|-----|-----|

|                  | 0 | 0 |     |     | Water | Level |     |     |

| Access<br>Rights | - | - | r/w | r/w | r/w   | r/w   | r/w | r/w |

#### Table 31. Description of WaterLevelReg bits

| Bit    | Symbol     | Description                                                                                                                                                        |

|--------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 to 6 | 0          | Is set to 0.                                                                                                                                                       |

| 5 to 0 | WaterLevel | This register defines a warning level to indicate a FIFO-buffer over- or underflow:                                                                                |

|        |            | The bit HiAlert in Status1Reg is set to 1, if the remaining number of bytes in the FIFO-buffer space is equal or less than the defined number of WaterLevel bytes. |

|        |            | The bit LoAlert in Status1Reg is set to 1, if equal or less than WaterLevel bytes are in the FIFO.                                                                 |

|        |            | Note: For the calculation of HiAlert and LoAlert see Table 23                                                                                                      |

#### 9.2.1.12 ControlReg

Miscellaneous control bits.

#### Table 32. ControlReg register (address 0Ch); reset value: 00h, 0000000b

|                  | 7        | 6         | 5             | 4 | 3 | 2 | 1        | 0 |

|------------------|----------|-----------|---------------|---|---|---|----------|---|

|                  | TStopNow | TStartNow | WrNFCIDtoFIFO | 0 | 0 | R | xLastBit | S |

| Access<br>Rights | w        | w         | dy            | - | - | r | r        | r |

## Table 33. Description of ControlReg bits

| Bit    | Symbol        | Description                                                                                                                                                                      |

|--------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | TStopNow      | Set to 1, the timer stops immediately.                                                                                                                                           |

|        |               | Reading this bit will always return 0.                                                                                                                                           |

| 6      | TStartNow     | Set to 1 starts the timer immediately.                                                                                                                                           |

|        |               | Reading this bit will always return 0.                                                                                                                                           |

| 5      | WrNFCIDtoFIFO | Set to 1, the internal stored NFCID (10 bytes) is copied into the FIFO.<br>The NFC ID an be configured using the command <u>Section 18.3.1.2</u><br>"Config command" on page 70. |

|        |               | Afterwards the bit is cleared automatically. This is needed to provide the 'name' of the card (e.g. UID). This is needed for card operation.                                     |

| 4      | 0             | Is set to 0.                                                                                                                                                                     |

| 3      | 0             | Is set to 0.                                                                                                                                                                     |

| 2 to 0 | RxLastBits    | Shows the number of valid bits in the last received byte. If zero, the whole byte is valid.                                                                                      |

Product data sheet COMPANY PUBLIC

## 9.2.1.13 CollReg

Defines the first bit collision detected on the RF interface.

#### Table 34. CollReg register (address 0Eh); reset value: XXh, 101XXXXb

|                  | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------------|-----|---|---|---|---|---|---|---|

|                  | 1   | 0 | 1 |   |   | х |   |   |

| Access<br>Rights | r/w | - | r | r | r | r | r | r |

#### Table 35. Description of CollReg bits

| Bit    | Symbol | Description                       |

|--------|--------|-----------------------------------|

| 7      | 1      | Shall be set to 1.                |

| 6      | 0      | Shall be set to 0.                |

| 5      | 1      | Shall be set to 1.                |

| 4 to 0 | x      | These bits cannot be interpreted. |

## 9.2.2 Communication

## 9.2.2.1 ModeReg

Defines general mode settings for transmitting and receiving.

## Table 36. ModeReg register (address 11h); reset value: 3Bh, 00111011b

|                  | 7        | 6          | 5   | 4   | 3   | 2          | 1    | 0     |

|------------------|----------|------------|-----|-----|-----|------------|------|-------|

|                  | MSBFirst | DetectSync | RFU | RFU | RFU | ModeDetOff | CRCF | reset |

| Access<br>Rights | r/w      | r/w        | r/w | r/w | r/w | r/w        | r/w  | r/w   |

#### Table 37. Description of ModeReg bits

| Table 57. |            | moderteg bits                                                                                                                                                                                          |                                                                                                                                                                                                                                         |  |  |  |  |

|-----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

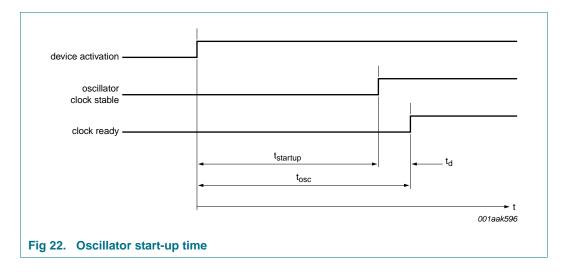

| Bit       | Symbol     | Descript                                                                                                                                                                                               | ion                                                                                                                                                                                                                                     |  |  |  |  |