### **ON Semiconductor**

### Is Now

To learn more about onsemi™, please visit our website at www.onsemi.com

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/ or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application,

# Integrated Driver and MOSFET with Integrated Current Monitor

### NCP303152

### **Description**

The NCP303152 integrates a MOSFET driver, high-side MOSFET and low-side MOSFET into a single package.

The driver and MOSFETs have been optimized for high-current DC-DC buck power conversion applications. The NCP303152 integrated solution greatly reduces package parasitics and board space compared to a discrete component solution.

### **Features**

- Capable of Average Currents up to 50 A

- Capable of 80 A (10 ms) Peak Current

- 80 A Packaged-Level UIS Tested to Improve Robustness

- 30 V / 30 V Breakdown Voltage MOSFETs for Higher Long Term Reliability

- High-Performance, Universal Footprint, Copper-Clip 5 mm x 6 mm PQFN Package

- Capable of Switching at Frequencies up to 1 MHz

- Compatible with 3.3 V or 5 V PWM Input

- Responds Properly to 3-level PWM Inputs

- Precise Current Monitoring

- Integrated Temperature Monitoring (TMON)

- Option for Zero Cross Detection with 3-level PWM

- Internal Bootstrap Diode

- Catastrophic Fault Detection

- Thermal Flag (OTP) for Over-Temperature Condition

- Over-Current Protection FAULT (OCP)

- Under-Voltage Lockout (UVLO) on VCC and PVCC

- Under-Voltage Protection FAULT on Boot-SW

- These Devices are Pb-Free and are RoHS Compliant

### **Applications**

- Desktop & Notebook Microprocessors

- Graphic Cards

- Routers and Switches

### ON Semiconductor®

www.onsemi.com

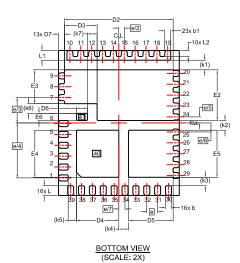

PQFN39 MN SUFFIX CASE 483BF

### MARKING DIAGRAM

0

NCP 303152 AWLYYWW

NCP303152 = Specific Device Code

A = Assembly Location

WL = Wafer Lot YY = Year WW = Work Week

### **ORDERING INFORMATION**

| Device         | Package             | Shipping <sup>†</sup> |

|----------------|---------------------|-----------------------|

| NCP303152MNTWG | PQFN39<br>(Pb-Free) | 3000 / Tape &<br>Reel |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

### **DIAGRAMS**

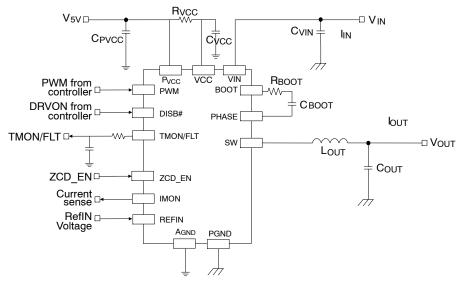

Figure 1. Application Schematic

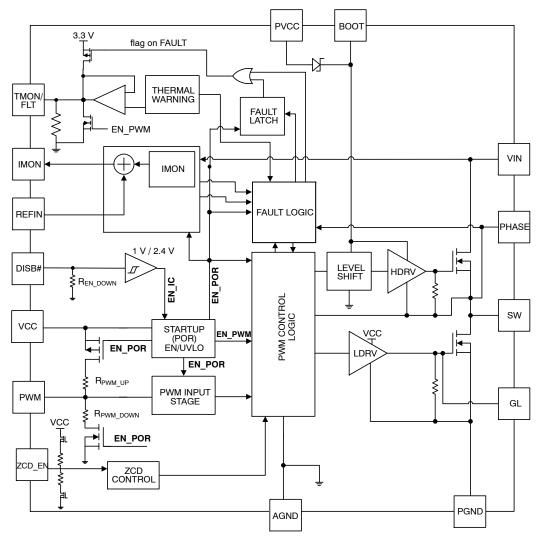

Figure 2. Block Diagram

### **PINOUT DIAGRAM**

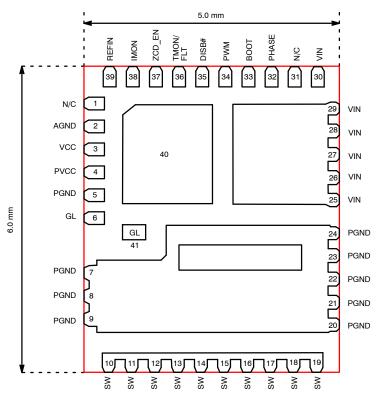

Figure 3. Top View

**Table 1. PIN LIST AND DESCRIPTIONS**

| Pin No.    | Symbol   | Description                                                                                                                                                                                                                                       |

|------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | NC       | No connect.                                                                                                                                                                                                                                       |

| 2          | AGND     | Analog Ground for the analog portions of the IC and for substrate.                                                                                                                                                                                |

| 3          | VCC      | Power Supply input for all analog control functions                                                                                                                                                                                               |

| 4          | PVCC     | Power Supply input for LS Gate Driver and Boot Diode.                                                                                                                                                                                             |

| 5, 40      | PGND     | Reserved for PVCC de-coupling capacitor return.                                                                                                                                                                                                   |

| 6, 41      | GL       | Low-Side Gate Monitor.                                                                                                                                                                                                                            |

| 7-9, 20-24 | PGND     | Power ground connection for Power Stage high current path.                                                                                                                                                                                        |

| 10–19      | SW       | Switching node junction between high-and low-side MOSFETs                                                                                                                                                                                         |

| 25–30      | VIN      | Input Voltage to Power Stage.                                                                                                                                                                                                                     |

| 31         | NC       | No connect.                                                                                                                                                                                                                                       |

| 32         | PHASE    | Return Connection for BOOT capacitor.                                                                                                                                                                                                             |

| 33         | воот     | Supply for high–side MOSFET gate driver. A capacitor from BOOT to PHASE supplies the charge to turn on the n–channel high side MOSFET. During the freewheeling interval (LS MOSFET on) the high side capacitor is recharged by an internal diode. |

| 34         | PWM      | PWM input to gate driver IC.                                                                                                                                                                                                                      |

| 35         | DISB#    | DISB# = LOW disables most blocks inside IC. DISB# = HIGH enables all blocks inside IC.                                                                                                                                                            |

| 36         | TMON/FLT | Temperature and FAULT Reporting Pin. Pin sources a (PTAT) voltage of 0.6 V at 0°C with an 8 mV/°C slope when no module FAULT is present. In the event of a module FAULT, this pin pulls HIGH to an internal driver IC rail = 3.0 V typical.       |

| 37         | ZCD_EN   | Zero Current Detection Function Enable                                                                                                                                                                                                            |

| 38         | IMON     | Current Monitor Output (output is referenced to REFIN) – 5 μA/A                                                                                                                                                                                   |

| 39         | REFIN    | Referenced voltage used for IMON feature. DC input voltage supplied by external source (not generated on SPS driver IC)                                                                                                                           |

Table 2. ABSOLUTE MAXIMUM RATINGS (Electrical Information – all signals referenced to PGND unless noted otherwise)

| Symbol                                           |                                                                                                                                                    | Parameter                          |      |                       | Unit |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------|-----------------------|------|

| V <sub>CC</sub>                                  | Supply Voltage                                                                                                                                     | Referenced to AGND                 | -0.3 | 6                     | V    |

| $PV_{CC}$                                        | Drive Voltage                                                                                                                                      | Referenced to AGND                 | -0.3 | 6                     | V    |

| V <sub>DISB#</sub>                               | Enable / Disable                                                                                                                                   | Referenced to AGND                 | -0.3 | V <sub>CC</sub> + 0.3 | V    |

| $V_{PWM}$                                        | PWM Signal Input                                                                                                                                   | Referenced to AGND                 | -0.3 | V <sub>CC</sub> + 0.3 | V    |

| V <sub>ZCD_EN</sub>                              | ZCD Mode Input                                                                                                                                     | Referenced to AGND                 | -0.3 | V <sub>CC</sub> + 0.3 | V    |

| $V_{GL}$                                         | Low Gate Test Pin                                                                                                                                  | Referenced to AGND                 | -0.3 | V <sub>CC</sub> + 0.3 | V    |

| V <sub>IMON</sub>                                | Current Monitor Output                                                                                                                             | Referenced to AGND                 | -0.3 | V <sub>CC</sub> + 0.3 | V    |

| $V_{REFIN}$                                      | Referenced Voltage Input                                                                                                                           | Referenced to AGND                 | -0.3 | V <sub>CC</sub> + 0.3 | V    |

| V <sub>TMON/FLT</sub>                            | Thermal Monitor                                                                                                                                    | Referenced to AGND                 | -0.3 | V <sub>CC</sub> + 0.3 | V    |

| V <sub>IN</sub>                                  | Power Input                                                                                                                                        | Referenced to PGND, AGND           | -0.3 | 30                    | V    |

| V <sub>VIN - PHASE</sub> V <sub>IN</sub> - Phase |                                                                                                                                                    | Referenced to PGND, AGND (DC Only) | -0.3 | 30                    | V    |

|                                                  |                                                                                                                                                    | Referenced to PGND, AC < 5 ns      | -5   | 36                    |      |

| V <sub>PHASE</sub>                               | Phase Referenced to PGND, AGND (DC Only)                                                                                                           |                                    | -0.3 | 30                    | V    |

|                                                  |                                                                                                                                                    | Referenced to PGND, AC < 5 ns      | -15  | 30                    |      |

| V <sub>SW</sub>                                  | Switch Node Input                                                                                                                                  | Referenced to PGND, AGND (DC Only) | -0.3 | 30                    | V    |

|                                                  |                                                                                                                                                    | Referenced to PGND, AC < 5 ns      | -7   | 36                    |      |

| V <sub>BOOT</sub>                                | Bootstrap Supply                                                                                                                                   | Referenced to AGND                 | -0.3 | 32                    | V    |

| V <sub>BOOT_PHASE</sub>                          | Boot to PHASE Voltage                                                                                                                              | DC Only                            | -0.3 | 7                     | V    |

|                                                  |                                                                                                                                                    | AC < 5 ns                          | -0.3 | 9                     |      |

| TJ                                               | Maximum Junction Temperature                                                                                                                       |                                    |      | +150                  | °C   |

| UIS                                              | Unclamped Inductive Single–Pulse Avalanche Energy, High–Side FET ( $T_J$ Switching = 25°C, $V_{CC}/V_{GS}$ = 5 V, L = 0.5 $\mu$ H, $I_L$ = 80 ApK) |                                    | -    | 2.15                  | mJ   |

| ESD                                              | Electrostatic Discharge                                                                                                                            | Human Body Model, JESD22-A114      | 2000 |                       | V    |

|                                                  | Protection                                                                                                                                         | Charged Device Model, JESD22-C101  | 1000 |                       |      |

|                                                  | •                                                                                                                                                  | •                                  |      |                       |      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

**Table 3. THERMAL INFORMATION**

| Rating                              | Symbol                        | Value       | Unit |

|-------------------------------------|-------------------------------|-------------|------|

| Thermal Resistance (Note 1)         | R <sub>0J-Lead</sub> (Note 2) | 0.8         | °C/W |

|                                     | $R_{\theta J-CaseTop}$        | 13.1        | °C/W |

|                                     | $R_{\theta J-Ambient}$        | 16          | °C/W |

| Operating Ambient Temperature Range | T <sub>A</sub>                | -40 to +125 | °C   |

| Maximum Storage Temperature Range   | T <sub>STG</sub>              | -55 to +150 | °C   |

| Moisture Sensitivity Level          | MSL                           | 1           |      |

Mounted on 2S2P test board with 0 LFM at T<sub>A</sub> = 25°C.

Measured at PGND Pad (Pins 20 – 24).

### **Table 4. RECOMMENDED OPERATING CONDITIONS**

| Parameter                       | Pin Name                           | Conditions                                                                                              | Min | Тур | Max | Unit |

|---------------------------------|------------------------------------|---------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Supply Voltage Range            | V <sub>CC</sub> , PV <sub>CC</sub> |                                                                                                         | 4.5 | 5.0 | 5.5 | V    |

| Conversion Voltage              | V <sub>IN</sub>                    |                                                                                                         | 4.5 | 19  | 20  | V    |

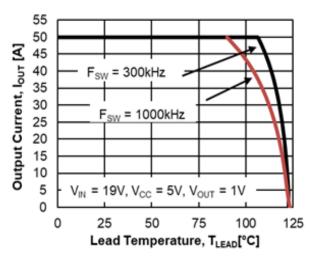

| Continuous Output Current       |                                    | F <sub>SW</sub> = 1 MHz, V <sub>IN</sub> = 19 V, V <sub>OUT</sub> = 1.0 V, T <sub>A</sub> = 25°C        | _   | _   | 45  | Α    |

| (Note 3)                        |                                    | F <sub>SW</sub> = 300 kHz, V <sub>IN</sub> = 19 V, V <sub>OUT</sub> = 1.0 V, T <sub>A</sub> = 25°C      | _   | _   | 50  | Α    |

| Peak Output Current<br>(Note 3) |                                    | $F_{SW}$ = 500 kHz, $V_{IN}$ = 19 V, $V_{OUT}$ = 1.0 V,<br>Duration = 10 ms, Period = 1 s, $T_A$ = 25°C | _   | -   | 80  | Α    |

| Junction Temperature            |                                    |                                                                                                         | -40 | -   | 125 | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

3. Mounted on ON Semiconductor evaluation board. See page 24 for board details.

Table 5. ELECTRICAL CHARACTERISTICS ( $V_{CC} = 5.0 \text{ V}$ ,  $V_{IN} = 19 \text{ V}$ ,  $V_{DISB\#} = 2.0 \text{ V}$ ,  $C_{VCC} = 0.1 \text{ }\mu\text{F}$  unless specified otherwise) Min/Max values are valid for the temperature range  $-40^{\circ}\text{C} \leq T_{J} \leq 125^{\circ}\text{C}$  unless noted otherwise, and are guaranteed by test, design or statistical correlation.

| Parameter                                                              | Symbol                        | Conditions                                                                                | Min  | Тур  | Max  | Unit |

|------------------------------------------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------|------|------|------|------|

| BASIC OPERATION                                                        | •                             |                                                                                           |      | •    | •    |      |

| No switching                                                           |                               | DISB# = 5 V, PWM = 0 V                                                                    | -    | 8    | _    | mA   |

| Disabled                                                               |                               | DISB# = 0 V, SW = 0 V                                                                     | -    | 120  | -    | μΑ   |

| UVLO Threshold                                                         | V <sub>UVLO</sub>             | VCC rising                                                                                | 3.8  | 4.1  | 4.2  | V    |

| UVLO Hysteresis                                                        | UVLO_ <sub>Hyst</sub>         |                                                                                           | -    | 0.17 | -    | V    |

| POR Delay to Enable IC                                                 | T <sub>D_POR</sub>            | VCC UVLO rising to internal PWM enable                                                    | -    | -    | 125  | μs   |

| DISB# INPUT                                                            |                               | •                                                                                         |      |      | •    |      |

| Pull-Down Resistance                                                   |                               |                                                                                           | _    | 130  | -    | kΩ   |

| High-Level Input Voltage                                               | V <sub>UPPER</sub>            |                                                                                           | 2.7  | _    | -    | V    |

| Low-Level Input Voltage                                                | V <sub>LOWER</sub>            |                                                                                           | _    | _    | 0.65 | V    |

| Enable Propagation Delay                                               |                               | PWM=GND, Delay Between EN from<br>LOW to HIGH to GL from LOW to HIGH<br>- Slow EN Setting | 16   | 26   | 32   | μs   |

| Disable Propagation Delay                                              |                               | PWM=GND, Delay Between EN from<br>HIGH to LOW to GL from HIGH to LOW<br>- Fast EN setting | -    | 43   | 109  | ns   |

| PWM INPUT (T <sub>A</sub> = 25°C, V <sub>CC</sub> / P <sub>VCC</sub> = | = 5 V, f <sub>SW</sub> = 1 MH | z, I <sub>OUT</sub> = 10 A)                                                               |      | •    | •    |      |

| Input High Voltage                                                     | V <sub>PWM_HI</sub>           |                                                                                           | 2.35 | 2.45 | 2.55 | V    |

| Mid-State Voltage Upper Threshold                                      | V <sub>TRI_HI</sub>           |                                                                                           | 2.05 | 2.2  | 2.3  | V    |

| Mid-State Voltage Lower Threshold                                      | V <sub>TRI_LO</sub>           |                                                                                           | 0.9  | 1.0  | 1.1  | V    |

| Input Low Voltage                                                      | V <sub>PWM_LO</sub>           |                                                                                           | 0.65 | 0.75 | 0.85 | V    |

| Pull-Up Impedance                                                      | R <sub>UP_PWM</sub>           |                                                                                           | _    | 21   | -    | kΩ   |

| Pull-Down Impedance                                                    | R <sub>DOWN_PWM</sub>         |                                                                                           | _    | 10   | -    | kΩ   |

| 3-State Open Voltage                                                   | V <sub>PWM_HIZ</sub>          |                                                                                           | 1.4  | 1.65 | 1.85 | V    |

| Non-overlap Delay, Leading Edge                                        | T <sub>DEADON</sub>           | GL <= 0.5 V to SW>1.2 V,<br>PWM Transition 0→1                                            | -    | 7    | _    | ns   |

| Non-overlap Delay, Trailing Edge                                       | T <sub>DEADOFF</sub>          | SW <= 1.2 V to GL>=0.5 V,<br>PWM Transition 1→0                                           | -    | 6    | -    | ns   |

| PWM Propagation Delay, Rising                                          | T <sub>PD_PHGLL</sub>         | PWM Going HIGH to GL Going LOW,<br>V <sub>IH_PWM</sub> to 90% GL                          | -    | 17   | 20   | ns   |

| PWM Propagation Delay, Falling                                         | T <sub>PD_PLGHL</sub>         | PWM Going LOW to GH Going LOW,<br>V <sub>IL_PWM</sub> to 90% GH                           | -    | 26   | 30   | ns   |

| Exiting PWM Mid-state Propagation<br>Delay, Mid-to-Low                 | T <sub>PWM_EXIT_L</sub>       | PWM (from Tri-State) going LOW to GL going HIGH, V <sub>IL_PWM</sub> to 10% GL            | -    | 20   | 30   | ns   |

| Exiting PWM Mid-state Propagation<br>Delay, Mid-to-High                | T <sub>PWM_EXIT_H</sub>       | PWM (from Tri-State) going HIGH to<br>SW going HIGH, V <sub>IH_PWM</sub> to 10% SW        | -    | 27   | 30   | ns   |

| PWM High to 3-State hold Off Time                                      | T <sub>D_HOLDOFF1</sub>       | PWM Going High to HS Going Off                                                            | 20   | 43   | 50   | ns   |

| PWM Low to 3-State hold Off Time                                       | T <sub>D_HOLDOFF2</sub>       | PWM Going Low to LS Going Off                                                             | 20   | 36   | 50   | ns   |

| HS minimal turn on time                                                | T <sub>ON_MIN_HS</sub>        | SW gate rising 10% to falling 10%                                                         | -    | 37   | -    | ns   |

| LS minimal turn on time                                                | T <sub>ON_MIN_LS</sub>        | LS gate rising 10% to falling 10%                                                         | -    | 33   | -    | ns   |

| HS minimal turn off time                                               | T <sub>OFF_MIN_HS</sub>       | SW gate falling 10% to rising 10%                                                         | -    | 31   | -    | ns   |

| LS minimal turn off time                                               | T <sub>OFF MIN LS</sub>       | LS gate falling 10% to rising 10%                                                         | _    | 51   | -    | ns   |

Table 5. ELECTRICAL CHARACTERISTICS ( $V_{CC} = 5.0 \text{ V}$ ,  $V_{IN} = 19 \text{ V}$ ,  $V_{DISB\#} = 2.0 \text{ V}$ ,  $C_{VCC} = 0.1 \text{ }\mu\text{F}$  unless specified otherwise) Min/Max values are valid for the temperature range  $-40^{\circ}\text{C} \leq T_{J} \leq 125^{\circ}\text{C}$  unless noted otherwise, and are guaranteed by test, design or statistical correlation.

| Parameter                                          | Symbol                                            | Conditions                                                                                                          | Min   | Тур   | Max   | Unit  |

|----------------------------------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| FAULT FLAG OUTPUT VOLTAGE/CU                       | RRENT                                             |                                                                                                                     |       |       |       |       |

| FAULT Report Output Voltage                        | V <sub>FAULT</sub>                                |                                                                                                                     | 2.85  | -     | -     | V     |

| Fault Report Delay time                            | T <sub>DFAULT</sub>                               |                                                                                                                     | -     | 100   | -     | ns    |

| IMON                                               |                                                   |                                                                                                                     |       |       |       |       |

| HS off to LS On Blanking Stop Time                 | T <sub>BLANK_HSOFF</sub>                          | IMON Blanking Time for PWM transition 1→0                                                                           | _     | 90    | -     | ns    |

| LS Off to HS on Blanking Stop Time                 | T <sub>BLANK</sub> _HSON                          | IMON Blanking Time for PWM transition 0→1                                                                           | _     | 70    | -     | ns    |

| IMON Amplifier Gain BW                             | BW <sub>IMON</sub>                                | $L = 150 \text{ nH}, V_{\text{IN}} = 19 \text{ V}, V_{\text{OUT}} = 1.0 \text{ V}, f_{\text{SW}} = 800 \text{ kHz}$ | -     | 5     | -     | MHz   |

| IMON Propagation Delay Time                        | T <sub>DELAY</sub>                                | $L = 150 \text{ nH}, V_{IN} = 19 \text{ V}, V_{OUT} = 1.0 \text{ V}, f_{SW} = 800 \text{ kHz}, IMON to IL}$         | _     | 60    | -     | ns    |

| IMON OPERATING RANGE ( TA = TJ                     | = -40°C to 125°C                                  | c, V <sub>CC</sub> = 4.5 V to 5.5 V, V <sub>IN</sub> = 4.5 – 20 V)                                                  |       |       |       |       |

| Dynamic range at IMON pin                          | V <sub>IMON</sub>                                 |                                                                                                                     | 0.6   | -     | 2.3   | ٧     |

| IMON ACCURACY (T <sub>A</sub> = 25°C to 125°       | C, V <sub>CC</sub> /P <sub>VCC</sub> = 5          | V, V <sub>IN</sub> = 19 V) (Note 4)                                                                                 |       |       |       |       |

| I <sub>MON_SLOPE</sub>                             | I <sub>MON_SLOPE</sub>                            | I <sub>OUT</sub> = -10 A to 40 A                                                                                    | 4.75  | 5.00  | 5.25  | μΑ/Α  |

| V <sub>IMON_10A</sub>                              | $R_{IMON} = 1 \text{ k}\Omega$<br>resistor placed | I <sub>OUT</sub> = 10 A, Voltage is Referenced to<br>REFIN Pin                                                      | 46.5  | 50    | 53.5  | mV    |

| V <sub>IMON_20A</sub>                              | from IMON to<br>REFIN.<br>Current Monitor         | I <sub>OUT</sub> = 20 A, Voltage is Referenced to<br>REFIN Pin                                                      | 95    | 100   | 105   | mV    |

| V <sub>IMON_30A</sub>                              | Voltage<br>(V <sub>IMON-REFIN</sub> )             | I <sub>OUT</sub> = 30 A, Voltage is Referenced to<br>REFIN Pin                                                      | 142.5 | 150   | 157.5 | mV    |

| V <sub>IMON_40A</sub>                              |                                                   | I <sub>OUT</sub> = 40 A, Voltage is Referenced to<br>REFIN Pin                                                      | 190   | 200   | 210   | mV    |

| BOOTSTRAP DIODE                                    |                                                   |                                                                                                                     |       |       |       |       |

| Forward Voltage                                    | V <sub>F</sub>                                    | Forward Bias Current = 10 mA                                                                                        | -     | 350   | -     | mV    |

| Breakdown Voltage                                  | V <sub>R</sub>                                    |                                                                                                                     | 30    | -     | -     | V     |

| LOW-SIDE DRIVER                                    |                                                   |                                                                                                                     |       |       |       |       |

| Output Impedance, Sourcing                         | R <sub>SOURCE_GL</sub>                            | Source Current = 100 mA                                                                                             | -     | 0.64  | -     | Ω     |

| Output Impedance, Sinking                          | R <sub>SINK_GH</sub>                              | Sink Current = 100 mA                                                                                               | -     | 0.29  | -     | Ω     |

| THERMAL MONITOR VOLTAGE                            | •                                                 |                                                                                                                     | •     | •     |       | •     |

| V <sub>TMON_25C</sub>                              | Thermal                                           | $T_A = T_J = 25^{\circ}C$                                                                                           | -     | 0.800 | -     | V     |

| V <sub>TMON_125C</sub>                             | Monitor Voltage                                   | T <sub>A</sub> = T <sub>J</sub> = 125°C                                                                             | -     | 1.600 | -     | V     |

| V <sub>TMON_</sub> SLOPE                           | _                                                 |                                                                                                                     | -     | 8     | -     | mV/°C |

| ISOURCE_TMON                                       | TMON Source<br>Current                            | 5 VCC, 25°C                                                                                                         | -     | 850   | -     | μΑ    |

| I <sub>SINK_TMON</sub>                             | TMON Sink<br>Current                              | 5 VCC, 25°C                                                                                                         | -     | 40    | -     | μΑ    |

| OVER-TEMPERATURE WARNING FA                        | AULT                                              | •                                                                                                                   |       | •     |       |       |

| Over-Temperature Warning Accuracy                  |                                                   | Driver IC Temperature                                                                                               | _     | 140   | -     | °C    |

| OTW Hysteresis                                     |                                                   | Driver IC Temperature                                                                                               | -     | 15    | -     | °C    |

| HS CYCLE-BY-CYCLE POSITIVE I-L                     | IMIT                                              | •                                                                                                                   |       | •     |       |       |

| I-limit comparator input-output propagation delay. | t <sub>D_ILimit</sub> -COMP                       | Input Signal = 380 mV,<br>dv/dt = 0.2 mV/nsec.                                                                      | _     | 60    | -     | ns    |

| Over-Current Limit                                 | I <sub>LIM</sub>                                  |                                                                                                                     | 74    | 80    | 86    | Α     |

### **Table 5. ELECTRICAL CHARACTERISTICS**

$(V_{CC} = 5.0 \text{ V}, V_{IN} = 19 \text{ V}, V_{DISB\#} = 2.0 \text{ V}, C_{VCC} = 0.1 \text{ } \mu\text{F} \text{ unless specified otherwise}) \text{ Min/Max values are valid for the temperature range } -40^{\circ}\text{C} \leq T_{J} \leq 125^{\circ}\text{C} \text{ unless noted otherwise, and are guaranteed by test, design or statistical correlation.}$

| Parameter                          | Symbol                | Conditions | Min  | Тур  | Max  | Unit |  |

|------------------------------------|-----------------------|------------|------|------|------|------|--|

| HS CYCLE-BY-CYCLE POSITIVE I-LIMIT |                       |            |      |      |      |      |  |

| OCP Hysteresis                     | I <sub>LIM_HYS</sub>  |            | _    | 8    | _    | Α    |  |

| NEGATIVE OVER-CURRENT (NOCE        | ) FAULT               |            |      |      |      |      |  |

| NOCP Trip LOW Level                | I <sub>NOCP_LOW</sub> |            | _    | -50  | _    | Α    |  |

| ZCD_EN INPUT                       |                       |            |      |      |      |      |  |

| Pull-Up Impedance                  | R <sub>UP_PWM</sub>   |            | _    | 21   | _    | kΩ   |  |

| Pull-Down Impedance                | R <sub>DOWN_PWM</sub> |            | _    | 10   | _    | kΩ   |  |

| 3-State Open Voltage               | V <sub>PWM_HIZ</sub>  |            | 1.4  | 1.65 | 1.85 | ٧    |  |

| ZCD_EN input Voltage High          | V <sub>ZCD_HI</sub>   |            | 2.25 | 2.4  | 2.55 | ٧    |  |

| ZCD_EN input Voltage Mid-state     | V <sub>ZCD_MID</sub>  |            | 1.4  | _    | 2.0  | ٧    |  |

| ZCD_EN input Voltage Low           | V <sub>ZCD_LO</sub>   |            | 0.7  | 0.8  | 0.95 | V    |  |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

<sup>4.</sup> Imon performance is guaranteed by independent ATE testing of High-side and Low-side slope and offset

### **MOSFET TYPICAL CHARACTERISTICS**

(Tests at T<sub>A</sub> = 25°C, unless otherwise specified)

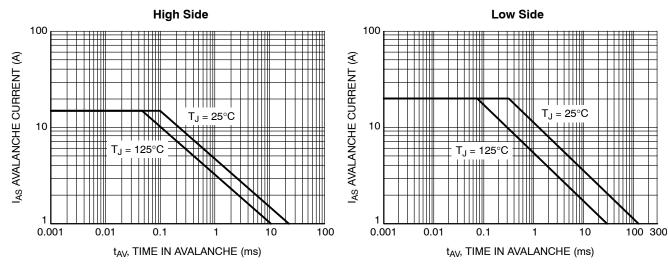

Figure 4. Highside FET Unclamped Inductive Switching Capability

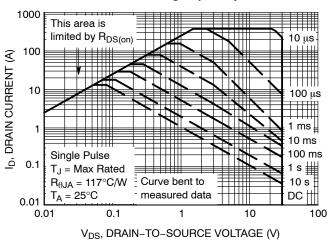

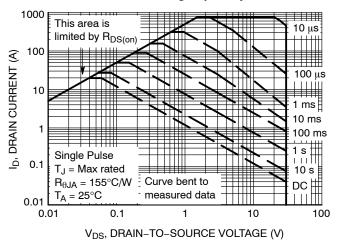

Figure 6. Highside FET Forward Biased Safe Operating Area

Figure 5. Lowside FET Unclamped Inductive Switching Capability

Figure 7. Lowside FET Forward Biased Safe Operating Area

### **TYPICAL CHARACTERISTICS**

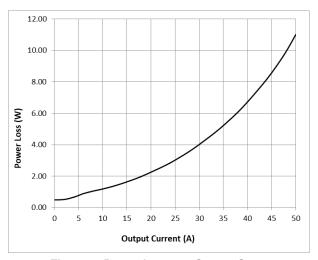

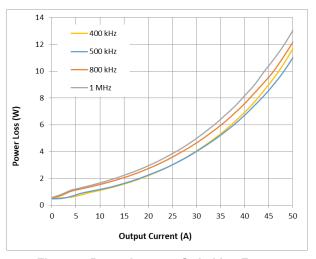

Figure 8. Power Loss vs. Output Current

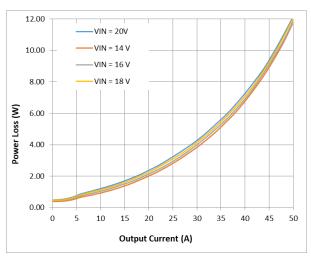

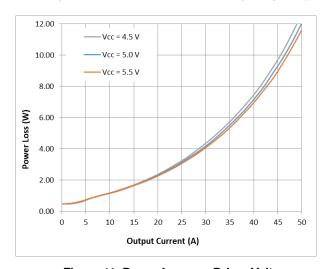

Figure 10. Power Loss vs. Input Voltage

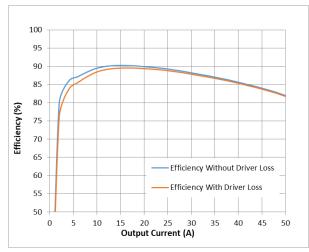

Figure 12. Efficiency vs. Output Load

Figure 9. Power Loss vs. Switching Frequency

Figure 11. Power Loss vs. Driver Voltage

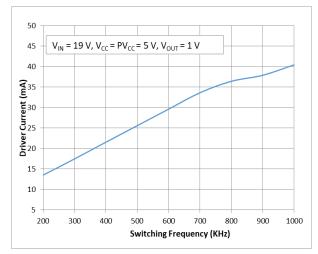

Figure 13. Driver Supply Current vs. Switching Frequency

### TYPICAL CHARACTERISTICS

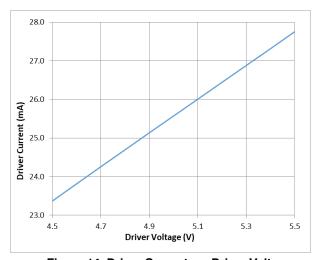

Figure 14. Driver Current vs. Driver Voltage

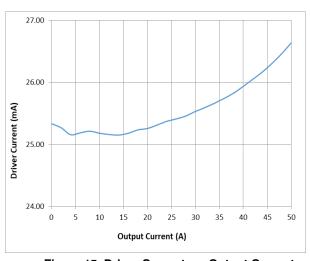

Figure 15. Driver Current vs. Output Current

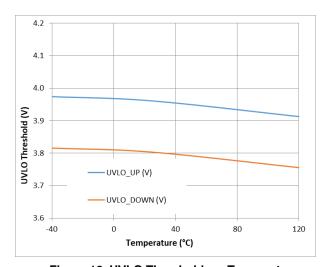

Figure 16. UVLO Threshold vs. Temperature

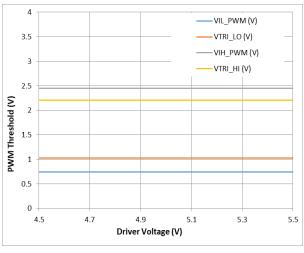

Figure 17. PWM Threshold vs. Driver Voltage

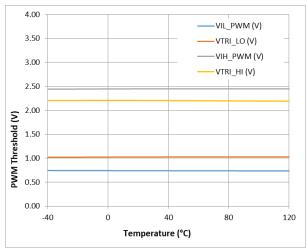

Figure 18. PWM Threshold vs. Temperature

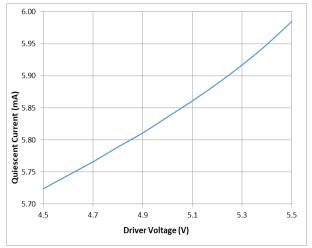

Figure 19. Quiescent Current vs. Driver Voltage

### **TYPICAL CHARACTERISTICS**

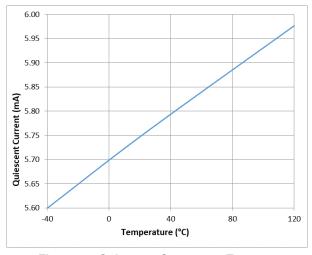

Figure 20. Quiescent Current vs. Temperature

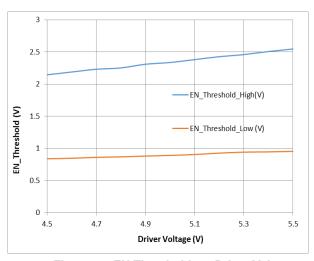

Figure 21. EN Threshold vs. Driver Voltage

Figure 22. EN Threshold vs. Temperature

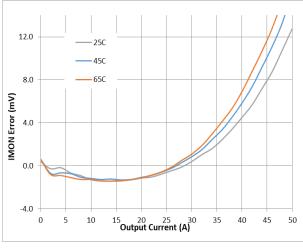

Figure 23. I<sub>MON</sub> Accuracy vs. Temperature

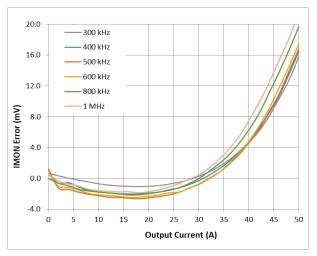

Figure 24. I<sub>MON</sub> Accuracy vs. Switching Frequency

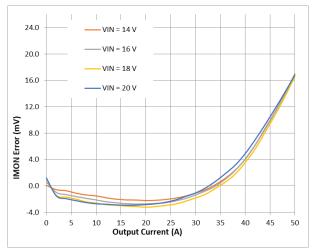

Figure 25.  $I_{MON}$  Accuracy vs. Input Voltage

### **TYPICAL CHARACTERISTICS**

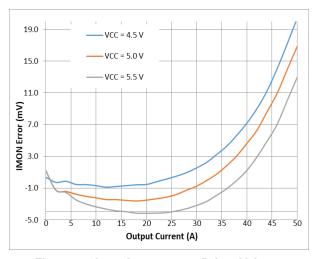

Figure 26. I<sub>MON</sub> Accuracy vs. Driver Voltage

Figure 27. Continuous Current Derating

### **FUNCTIONAL DESCRIPTION**

The SPS NCP303152 is a driver plus MOSFET module optimized for the synchronous buck converter topology. A PWM input signal is required to properly drive the high–side and the low–side MOSFETs. The part is capable of driving speed up to 1 MHz.

### **DISB# and UVLO**

The SPS NCP303152 is enabled by both DISB# pin input signal and  $V_{\rm CC}$  UVLO. Table 6 summarizes the enable and disable logics. With DISB# low and VCC UVLO, SPS is fully shut down. If VCC is ready but DISB# is low, SPS goes into sleep mode with very low Quiescent current, where only critical circuitry are alive. The part should also read fuses/program itself during this state.

**Table 6. UVLO AND DRIVER STATE**

| VCC<br>UVLO | DISB#  | Driver State                                                      |

|-------------|--------|-------------------------------------------------------------------|

| 0           | X      | Full driver shutdown (GH, GL=0), requires 40 $\mu s$ for start–up |

| 1           | 0      | Partial driver shutdown (GH, GL=0), requires 30 μs for startup    |

| 1           | 1      | Enabled (GH/GL follow PWM)                                        |

| Х           | Open/0 | Disabled (GH, GL=0)                                               |

NCP303152 needs 40  $\mu s$  time to go from fully shutdown mode to power ready mode. The time is 30  $\mu s$  to go from partial shutdown mode to power ready mode. Before power is ready, FAULT pin is strongly pulled low with a 50  $\Omega$  resistor. As a result, FAULT pin can also be used as a power ready indicator.

### Zero Current Detect Enable Input (ZCD EN)

The ZCD\_EN pin is a logic input pin with an internal voltage divider connected to VCC.

When ZCD\_EN is set low, the NCP303152 will operate in synchronous rectifier (PWM) mode. This means that negative current can flow in the LS MOSFET if the load current is less than 1/2 delta current in the inductor. When ZCD\_EN is set high, Zero Current Detect PWM (ZCD\_PWM) mode will be enabled.

With ZCD\_EN set high, if PWM falls to less than VPWM\_HI, but stays above VPWM\_LO, GL will go high after the non-overlap delay, and stay high for the duration of the ZCD Blanking time. Once this timer has elapsed, VSW will be monitored for zero current, and GL will be pulled low when zero current is detected.

With ZCD\_EN set mid (open), if the PWM goes to low, GL will go high after the non-overlap delay, and stay high for the duration of the ZCD Blanking time. Once this timer has elapsed, VSW will be monitored for zero current, and GL will be pulled low when zero current is detected.

### **PWM**

The PWM Input pin is a tri-state input used to control the HS MOSFET ON/OFF state. It also determines the state of the LS MOSFET. See Table 7 for logic operation with ZCD EN.

There is a minimum PWM pulse width, typical at 37 ns (SW gate rising 10% to falling 10%), if the PWM input pulse width is shorter than that, the driver will extend the pulse width to 37 ns. If the PWM input is shorter than 5 ns, the driver will ignore it.

**Table 7. LOGIC TABLE**

|       | INPUT TRUTH TABLE |                  |   |     |  |  |  |

|-------|-------------------|------------------|---|-----|--|--|--|

| DISB# | ZCD_EN            | ZCD_EN PWM GH GL |   |     |  |  |  |

| L     | Х                 | Х                | L | L   |  |  |  |

| Н     | Н                 | Н                | Н | L   |  |  |  |

| Н     | Н                 | L                | L | Н   |  |  |  |

| Н     | Н                 | MID              | L | ZCD |  |  |  |

| Н     | L                 | Н                | Н | L   |  |  |  |

| Н     | L                 | L                | L | Н   |  |  |  |

| Н     | L                 | MID              | L | L   |  |  |  |

| Н     | MID               | Н                | Н | L   |  |  |  |

| Н     | MID               | L                | L | ZCD |  |  |  |

| Н     | MID               | MID              | L | L   |  |  |  |

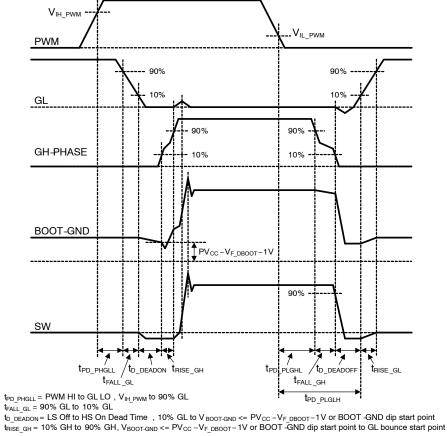

$\begin{array}{l} t_{PD\_PLGHL} = PWM\ LO\ to\ GH\ LO\ \ , V_{IL\_PWM}\ to\ 90\%\ GH\ or\ BOOT\ -GND\ decrease\ start\ point\ \ , \ t_{PD\_PLGLH}\ -t_{D\_DEADOFF}\ -t_{FALL\_GH} \\ t_{FALL\_GH} = 90\%\ GH\ to\ 10\%\ GH\ to\ 10\%\ GH\ to\ 10\%\ GH\ to\ 90\%\ V_{SW}\ or\ GL\ dip\ start\ point\ to\ 10\%\ GL \\ t_{RISE\_GL} = 10\%\ GL\ to\ 90\%\ GL \\ t_{RISE\_GL} = 10\%\ GL\ to\ 90\%\ GL \\ t_{PD\_PLGLH} = PWM\ LO\ to\ GL\ HI\ \ , V_{IL\_PWM}\ to\ 10\%\ GL \\ \end{array}$

Figure 28. PWM Timing Diagram

## For Use with Controllers with 3-State PWM and No Zero Current Detection Capability:

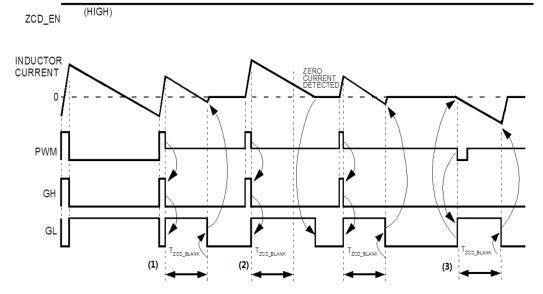

This section describes operation with controllers that are capable of 3 states in their PWM output and relies on the NCP303152 to conduct zero current detection during discontinuous conduction mode (DCM).

The ZCD\_EN pin needs to either be set to 5 V or left disconnected. The NCP303152 has an internal voltage divider connected to VCC that will set ZCD\_EN to the logic mid state if this pin is left disconnected.

### A. When ZCD EN is set to high.

To operate the buck converter in continuous conduction mode (CCM), PWM needs to switch between the logic high and low states. To enter into DCM, PWM needs to be switched to the mid-state. Whenever PWM transitions to mid-state, GH turns off and GL turns on. GL stays on for the duration of the ZCD blanking timers. Once this timer expires, the NCP303152 monitors the inductor current and

turns GL off when the inductor current exceeds the ZCD threshold. By turning off the LS FET, the body diode of the LS FET allows any positive current to go to zero but prevents negative current from conducting.

There are three scenarios:

- 1. PWM from high to mid, Inductor current goes to zero before the ZCD blanking timer, GL is on and current goes to negative until the timer expires.

- PWM from high to mid,

ZCD blanking timer expires before inductor current goes to zero, GL is on until inductor current reaches zero.

- 3. PWM from mid to low to mid,

ZCD blanking timer starts when PWM goes from

mid to low, GL turns on. After PWM goes back to

mid, driver will wait for the timer to expire to turn

off GL.

Figure 29. Timing Diagram - 3-state PWM Controller, No ZCD (a)

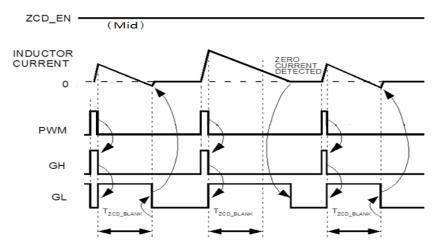

### B. When ZCD\_EN is set to mid (open).

With this setting, NCP303152 monitors the inductor current when PWM goes from high to low and turns off the GL when the inductor current exceeds the ZCD threshold.

Figure 30. Timing Diagram - 3-state PWM Controller, No ZCD (b)

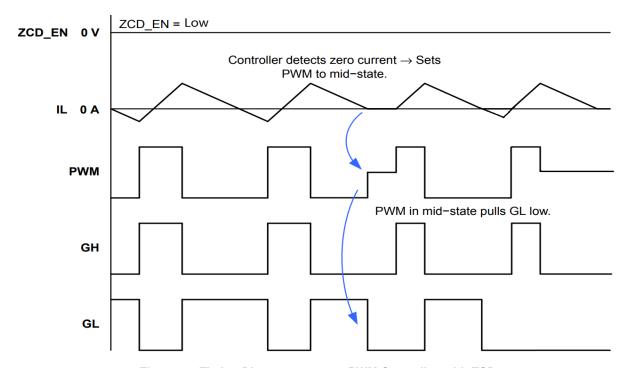

## For Use with Controllers with 3-State PWM and Zero Current Detection Capability:

This section describes operation with controllers that are capable of 3 PWM output levels and have zero current detection during discontinuous conduction mode (DCM). The ZCD EN pin needs to be pulled low.

To operate the buck converter in continuous conduction mode (CCM), PWM needs to switch between the logic high and low states. During DCM, the controller is responsible for detecting when zero current has occurred, and then notifying the NCP303152 to turn off the LS FET. When the controller detects zero current, it needs to set PWM to mid-state, which causes the NCP303152 to pull both GH and GL to their off states without delay.

Figure 31. Timing Diagram - 3-state PWM Controller, with ZCD

### **Power Sequence**

NCP303152 requires four (4) input signals to conduct normal switching operation: VIN, VCC, PWM, and DISB#. All combinations of power sequences are available. The below example of a power sequence is for a reference application design:

• From no input signals

-> VCC On: Typical 5 VDC

-> DISB# HIGH: Typical 5 VDC

-> VIN On: Typical 19 VDC

-> PWM Signaling: 3.3 V HIGH/ 0 V LOW

The VIN pins are tied to the system main DC power rail.

The DISB# pin can be tied to the VCC rail with an external pull-up resistor and it will maintain HIGH once the VCC rail turns on. Or the DISB# pin can be directly tied to the PWM controller for other purposes.

### **High-Side Driver**

The high-side driver (HDRV) is designed to drive a floating N-channel MOSFET (Q1). The bias voltage for the high-side driver is developed by a bootstrap supply circuit, consisting of the internal Schottky diode and external bootstrap capacitor (C<sub>BOOT</sub>). During startup, the SW node is held at PGND, allowing CBOOT to charge to VCC through the internal bootstrap diode. When the PWM input goes HIGH, HDRV begins to charge the gate of the high-side MOSFET (internal GH pin). During this transition, the charge is removed from the CBOOT and delivered to the gate of Q1. As Q1 turns on, SW rises to V<sub>IN</sub>, forcing the BOOT pin to V<sub>IN</sub> + V<sub>BOOT</sub>, which provides sufficient V<sub>GS</sub> enhancement for Q1. To complete the switching cycle, Q1 is turned off by pulling HDRV to SW. CBOOT is then recharged to VCC when the SW falls to PGND. HDRV output is in phase with the PWM input. The high-side gate is held LOW when the driver is disabled or the PWM signal is held within the 3-state window for longer than the 3-state hold-off time,  $t_{D\ HOLD-OFF}$

### Low-Side Driver

The low-side driver (LDRV) is designed to drive the gate-source of a ground referenced low R<sub>DS(ON)</sub> N-channel MOSFET (Q2). The bias for LDRV is internally connected between VCC and PGND. When the driver is enabled, the driver's output is 180° out of phase with the PWM input. When the driver is disabled, LDRV is held LOW.

### Dead-Times

The driver IC design ensures minimum MOSFET dead times, while eliminating potential shoot-through (cross-conduction) currents. To ensure optimal module efficiency, body diode conduction times must be reduced to the low nano-second range during CCM and DCM operation. Delay circuitry is added to prevent gate overlap during both the low-side MOSFET off to high-side MOSFET on transition and the high-side MOSFET off to low-side MOSFET on transition.

### **Boot Capacitor Refresh**

NCP303152 monitors the low Boot–SW voltage. If DISB# and VCC are ready, but the voltage across the boot capacitor voltage is lower than 3.1 V, NCP303152 ignores the PWM input signal and starts the boot refresh circuit. The boot refresh circuit turns on the low side MOSFET with a  $100~\text{ns}{\sim}200~\text{ns}$  narrow pulse in every  $7{\sim}14~\mu\text{s}$  until Boot–SW voltage is above 3.6 V.

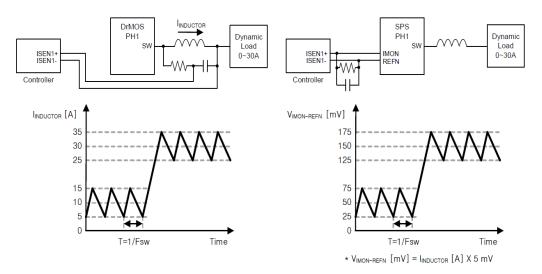

### **Current Monitor (IMON)**

The SPS current monitor accurately senses high-side and low-side MOSFET currents. The currents are summed together to replicate the output filter inductor current. The signal is reported from the SPS module in the form of a 5  $\mu$ A/A current signal ( $I_{IMON-REFIN}$ ). The IMON signal will be referenced to an externally supplied signal (REFIN) and differentially sensed by an external analog/ digital PWM controller.

The motivation for the IMON feature is to replace the industry standard output filter DCR sensing, or output current sense using an external precision resistor. Both techniques are lossy and lead to reduced system efficiency. Inductor DCR sensing is also notoriously inaccurate for low value DCR inductors. Figure 32 shows a comparison between conventional inductor DCR sensing and the unique IMON feature.

The accuracy on IMON signal is ±5% from 10 A to 40 A output current. For the SPS module, parameters that can affect IMON accuracy are tightly controlled and trimmed at the MOSFET/IC production stage. The user can easily incorporate the IMON feature and accuracy replacing the traditional current sensing methods in multi-phase applications.

Figure 32. DrMOS with Inductor DCR Sensing vs. SPS with IMON

### Fault Flag (FAULT)

The TMON / FAULT pin on NCP303152 is a thermal monitor output in normal operation. Before power is ready, TMON pin is strongly pulled low with a 50 ohm resistor. As a result, it can be used as a power ready indicator. Also, this pin is used as a module FAULT flag pin if there is OCP, Boot UVLO, or OTP.

The TMON pin output is a Proportional to Absolute Temperature (PTAT) voltage sourced signal referenced to AGND when no module FAULT is present. It will typically output 0.6~V at  $0^{\circ}$ C and 1.8~V at  $150^{\circ}$ C with  $8~mV/^{\circ}$ C typical slope.

TMON pins from multiple SPS modules (used in multi-phase topologies) can be tied together to share a common thermal bus. Operating with this configuration will force the thermal bus signal to report the highest voltage output TMON signal to the controller (highest temperature). The TMON output has a low output impedance when sourcing current and a high output impedance when sinking current.

The TMON signal reported from the module pin is a buffered version of an internal TMON signal. Configuring the SPS module to share a common thermal bus will still permit each module to safely monitor its own temperature since the internal TMON signal is unaffected by the common thermal bus configuration.

An over temperature event is considered catastrophic in nature. OTW raises fault flag HIGH once it exceeds 140°C

temperature. Driver still responds to PWM commands. Once the IC falls below 125°C, fault flag is cleared internally by driver IC.

### **Over-Current Protection (OCP)**

The NCP303152 has cycle-by-cycle over-current protection. If current exceeds the OCP threshold, HS FET is gated off regardless of PWM command. HS FET cannot be gated on again until the current is less than the OCP threshold with a hysteresis.

Fault flag will be pulled HIGH after 10 consecutive cycle-by-cycle OCPs are detected. Fault flag will clear once OCP is NOT detected. Module never shuts down nor does it disable HDRV/LDRV (but driver will still truncate HS on time when PWM=HIGH and ILIM is detected).

### Negative-OCP

The NCP303152 can detect large negative inductor current and protect the low side MOSFET. Once this Negative current threshold is detected the driver module takes control and truncates LS on–time pulse (LS FET is gated off regardless of PWM command). The driver will stay in this state till one of two things happen 1) 200 ns expires in which case if the PWM pin is commanding the driver to turn on LS, the driver will respond and NOCP will again be monitored 2) PWM commands HS on in which case the driver will immediately turn on HS regardless of the 200 ns Timer.

### APPLICATION INFORMATION

### **Decoupling Capacitor for VCC**

For the supply input (VCC pin), local decoupling capacitor is required to supply the peak driving current and to reduce noise during switching operation. Use at least 0.68  $\sim 2.2~\mu\text{F}/$  0402  $\sim 0603/$  X5R  $\sim$  X7R multi-layer ceramic capacitor for the power rail. Keep this capacitor close to the VCC pin and AGND copper planes. If it needs to be located on the bottom side of board, put through–hole vias on each pad of the decoupling capacitor to connect the capacitor pad on bottom with VCC pin on top.

The supply voltage range on VCC is  $4.5 \text{ V} \sim 5.5 \text{ V}$ , typically 5 V for normal applications.

### **Bootstrap Circuit**

The bootstrap circuit uses a charge storage capacitor ( $C_{BOOT}$ ). A bootstrap capacitor of 0.1 ~ 0.22  $\mu F/$  0402 ~ 0603/ X5R ~ X7R is usually appropriate for most switching applications. A series bootstrap resistor may be needed for specific applications to lower high–side MOSFET switching speed. The boot resistor is required when the SPS is switching above 15 V  $V_{IN}$ ; when it is effective at controlling  $V_{SW}$  overshoot. RBOOT value from 2.2 to 6  $\Omega$  is typically recommended to reduce excessive voltage spike and ringing on the SW node. A higher  $R_{BOOT}$  value can cause lower efficiency due to high switching loss of high–side MOSFET.

Do not add a capacitor or resistor between the BOOT pin and GND.

It is recommended to add a PCB place holder for a small size  $1~nF \sim 1~\mu F$  capacitor close to the REFIN pin and AGND to reduce switching noise injection.

It is also recommended to add a small  $10 \sim 47$  pF capacitor in parallel with the IMON resistor from IMON to REFIN. This capacitor can help reduce switching noise coupling onto the IMON signal. The place of the IMON resistor and cap should be close to the controller, not the SPS to improve the sensing accuracy.

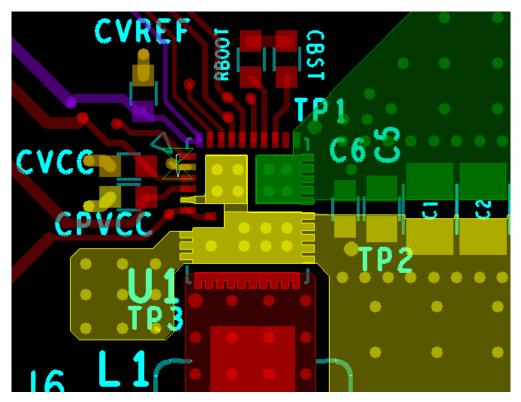

### **PCB Layout Guideline**

All of the high-current paths; such as VIN, SW, VOUT, and GND coppers; should be short and wide for low parasitic inductance and resistance. This helps achieve a more stable and evenly distributed current flow, along with enhanced heat radiation and system performance.

Input ceramic bypass capacitors must be close to the VIN and PGND pins. This reduces the high-current power loop inductance and the input current ripple induced by the power MOSFET switching operation.

An output inductor should be located close to the NCP303152 to minimize the power loss due to the SW copper trace. Care should also be taken so the inductor dissipation does not heat the SPS.

PowerTrench<sup>®</sup> MOSFETs are used in the output stage and are effective at minimizing ringing due to fast switching. In most cases, no RC snubber on SW node is required. If a snubber is used, it should be placed close to the SW and PGND pins. The resistor and capacitor of the snubber must

be sized properly to not generate excessive heating due to high power dissipation.

Decoupling capacitor on VCC and BOOT capacitor should be placed as close as possible to the VCC ~ AGND and BOOT ~ PHASE pin pairs to ensure clean and stable power supply. Their routing traces should be wide and short to minimize parasitic PCB resistance and inductance.

The board layout should include a placeholder for small–value series boot resistor on BOOT  $\sim$  PHASE. The boot–loop size, including series  $R_{BOOT}$  and  $C_{BOOT}$ , should be as small as possible.

A boot resistor may be required and it is effective to control the high-side MOSFET turn-on slew rate and SW voltage overshoot.  $R_{BOOT}$  can improve noise operating margin in synchronous buck designs that may have noise issues due to ground bounce or high positive and negative  $V_{SW}$  ringing. Inserting a boot resistance lowers the SPS module efficiency. Efficiency versus switching noise must be considered.  $R_{BOOT}$  values from 0.5  $\Omega$  to 6.0  $\Omega$  are typically effective in reducing  $V_{SW}$  overshoot.

The VIN and PGND pins handle large current transients with frequency components greater than 100 MHz. If possible, these pins should be connected directly to the VIN and board GND planes. The use of thermal relief traces in series with these pins is not recommended since this adds extra parasitic inductance to the power path. This added inductance in series with either the VIN or PGND pin degrades system noise immunity by increasing positive and negative V<sub>SW</sub> ringing.

PGND pad and pins should be connected to the GND copper plane with multiple vias for stable grounding. Poor grounding can create a noisy and transient offset voltage level between PGND and AGND. This could lead to faulty operation of gate driver and MOSFETs.

Ringing at the BOOT pin is most effectively controlled by close placement of the boot capacitor. Do not add any additional capacitors between BOOT to PGND. This may lead to excess current flow through the BOOT diode, causing high power dissipation.

Put multiple vias on the VIN and VOUT copper areas to interconnect top, inner, and bottom layers to evenly distribute current flow and heat conduction. Do not put too many vias on the SW copper to avoid extra parasitic inductance and noise on the switching waveform. As long as efficiency and thermal performance are acceptable, place only one SW node copper on the top layer and put no vias on the SW copper to minimize switch node parasitic noise. Vias should be relatively large and of reasonably low inductance. Critical high–frequency components; such as R<sub>BOOT</sub>, C<sub>BOOT</sub>, RC snubber, and bypass capacitors; should be located as close to the respective SPS module pins as possible on the top layer of the PCB. If this is not feasible, they can be placed on the board bottom side and their pins connected from bottom to top through a network of low–inductance vias.

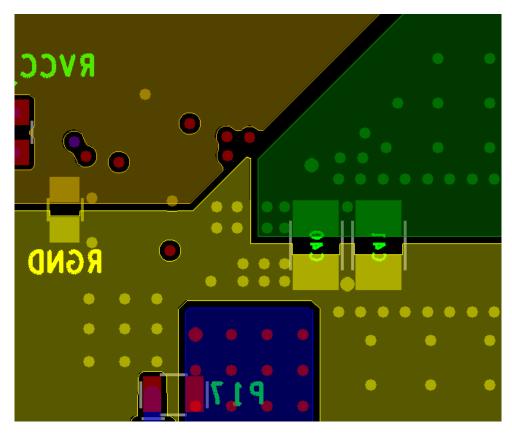

### **PCB Layout Guideline (Continued)**

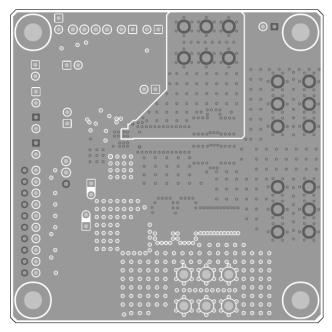

Figure 33. Layout Example – Top View

Figure 34. Layout Example – Bottom Layer

### **Evaluation Board Information**

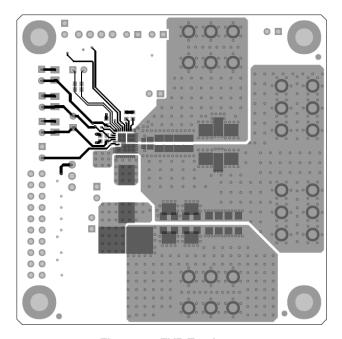

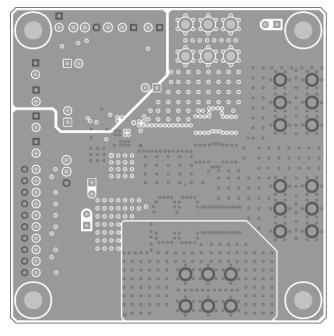

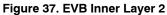

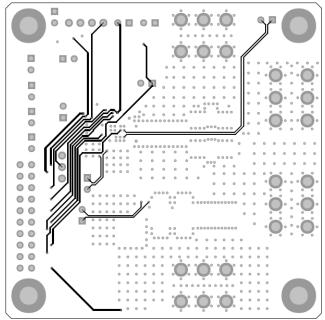

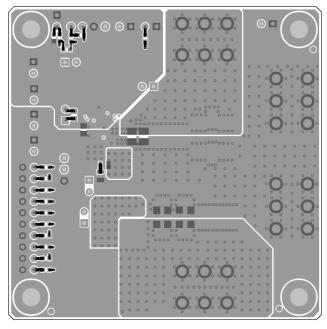

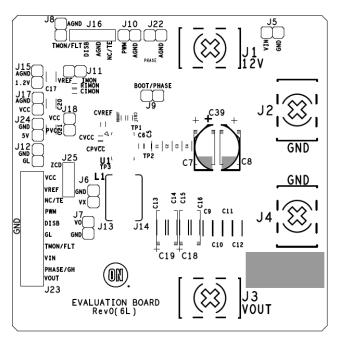

The NCV303150 evaluation board (EVB) is 70 mm x 70 mm with 6 total layers. All layers have a 2-oz. copper finish.

00000000 0000

00

Figure 35. EVB Top Layer

Figure 36. EVB Inner Layer 1

Figure 38. EVB Inner Layer 3

### **Evaluation Board Information**

Figure 39. EVB Inner Layer 4

Figure 40. EVB Bottom Layer

Figure 41. EVB Silkscreen Top

Figure 42. EVB Bottom Layer

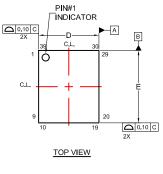

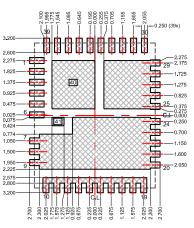

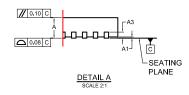

### PACKAGE DIMENSIONS

# **PQFN39 5x6, 0.45P**CASE 483BF ISSUE B

LAND PATTERN RECOMMENDATION\*

\*FOR ADDITIONAL INFORMATION ON OUR PB-FREE STRATEGY AND SOLDERING DETAILS, PLEASE DOWNLOAD THE ON SEMICONDUCTOR SOLDERING AND MOUNTING TECHNIQUES REFERENCE MANUAL, SOLDERRIMD.

### NOTES: UNLESS OTHERWISE SPECIFIED

- A) DOES NOT FULLY CONFORM TO JEDEC REGISTRATION MO-220, DATED MAY/2005.

- B) ALL DIMENSIONS ARE IN MILLIMETERS.

C) DIMENSIONS DO NOT INCLUDE BURRS

OR MOLD FLASH. MOLD FLASH OR

BURRS DOES NOT EXCEED 0.10MM.

- D) DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

| 13WE 114.5W-1994. |          |             |       |  |  |  |

|-------------------|----------|-------------|-------|--|--|--|

|                   | MIL      | MILLIMETERS |       |  |  |  |

| DIM               | MIN.     | NOM.        | MAX.  |  |  |  |

| Α                 | 0.70     | 0.75        | 0.80  |  |  |  |

| A1                | 0.00     | -           | 0.05  |  |  |  |

| <b>A</b> 3        | 0.15     | 0.20        | 0.25  |  |  |  |

| b                 | 0.20     | 0.25        | 0.30  |  |  |  |

| b1                | 0.20     | 0.25        | 0.30  |  |  |  |

| D                 | 4.90     | 5.00        | 5.100 |  |  |  |

| D2                | 4.40     | 4.50        | 4.60  |  |  |  |

| D3                | 1.25     | 1.35        | 1.45  |  |  |  |

| D4                | 1.65     | 1.75        | 1.85  |  |  |  |

| D5                | 1.75     | 1.85        | 1.95  |  |  |  |

| D6                | 0.35     | 0.45        | 0.55  |  |  |  |

| D7                | 0.15     | 0.25        | 0.35  |  |  |  |

| E                 | 5.90     | 6.00        | 6.10  |  |  |  |

| E2                | 2.00     | 2.10        | 2.20  |  |  |  |

| E3                | 1.30     | 1.40        | 1.50  |  |  |  |

| E4                | 1.85     | 1.95        | 2.05  |  |  |  |

| E5                | 1.85     | 1.95        | 2.05  |  |  |  |

| E6                | 0.20     | 0.30        | 0.40  |  |  |  |

| е                 | 0        | .450 BS     | С     |  |  |  |

| e/2               | 0        | .225 BS     | C     |  |  |  |

| e/3               | 1        | .050 BS     | 0     |  |  |  |

| e/4               | 2        | .275 BS     | С     |  |  |  |

| e/5               |          | .250 BS     |       |  |  |  |

| e/6               | 0        | .375 BS     | С     |  |  |  |

| e/7               | 0        | .255 BS     | С     |  |  |  |

| L                 | 0.30     | 0.40        | 0.50  |  |  |  |

| L1                | 0.30     | 0.40        | 0.50  |  |  |  |

| L2                | 0.15     | 0.25        | 0.35  |  |  |  |

| k1                |          | 0.40 REF    |       |  |  |  |

| k2                |          | 0.40 REF    |       |  |  |  |

| k3                | 0.35 REF |             |       |  |  |  |

| k4                | 0.40 REF |             |       |  |  |  |

| k5                | (        | 0.35 REF    |       |  |  |  |

| k6                |          | 0.40 REF    | =     |  |  |  |

| k7                | (        | 0.40 REF    |       |  |  |  |

|                   |          |             |       |  |  |  |

POWERTRENCH is registered trademark of Semiconductor Components Industries, LLC. Intel is a registered trademark of Intel Corporation.

ON Semiconductor and the are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor and see no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and

### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

ON Semiconductor Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative