## FLEXMOS™ 7x Half-bridge **MOSFET Pre-driver**

The NCV7547 programmable seven channel half-bridge MOSFET pre-driver is one of a family of FLEXMOS automotive grade products for driving logic-level NMOS FETs. The product is controllable by a combination of serial SPI and CMOS-compatible parallel inputs. An internal power-on reset provides controlled power up. A reset input allows external re-initialization and a failsafe input allows the device to be safely disabled in the event of system upset.

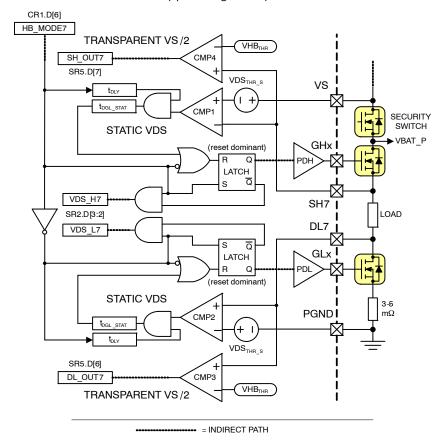

Each channel independently monitors its external MOSFETs' drain-source voltages for fault conditions. Overload detection thresholds are SPI-selectable and the product allows different detection thresholds for each channel.

The FLEXMOS family of products offers application scalability through choice of external MOSFETs.

#### **Features**

- Supports Functional Safety Compliance

- 7 Half-bridge Pre-drivers for External Logic-level NMOS FETs

- One Channel with Separated High-side & Low-side Pre-drivers Configurable as a Half-bridge or as Independent Pre-drivers

- Integrated Charge Pump for:

- ♦ High-side Gate Drive

- Switched Reverse Battery Protection

- 5 V CMOS Compatible I/O:

- 16-bit SPI Interface for Control and Diagnosis

- Reset and Failsafe Inputs

- 4 PWM Control Inputs

- Programmable:

- Slew Rate Control

- Overload Protection Thresholds

- Low Quiescent Current

- Wettable Flanks Pb–free Packaging

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

#### **Benefits**

Scalable to Load by Choice of External MOSFET

## ON Semiconductor®

www.onsemi.com

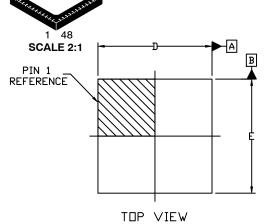

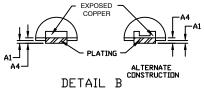

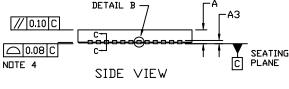

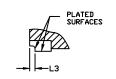

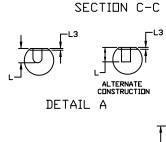

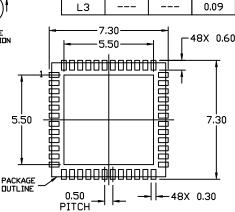

QFNW48 7x7, 0.5P CASE 484AJ

#### **MARKING DIAGRAM**

$\bigcirc$ ON NCV7547 **AWLYYWW**

NCV7547 = Specific Device Code = Assembly Location

WL = Wafer Lot VV = Year WW = Work Week = Pb-Free Package

## **ORDERING INFORMATION**

| Device       | Package             | Shipping <sup>†</sup> |

|--------------|---------------------|-----------------------|

| NCV7547MWTXG | QFN-48<br>(Pb-Free) | 2500 / Tape &<br>Reel |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

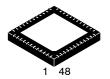

Figure 1. Block Diagram

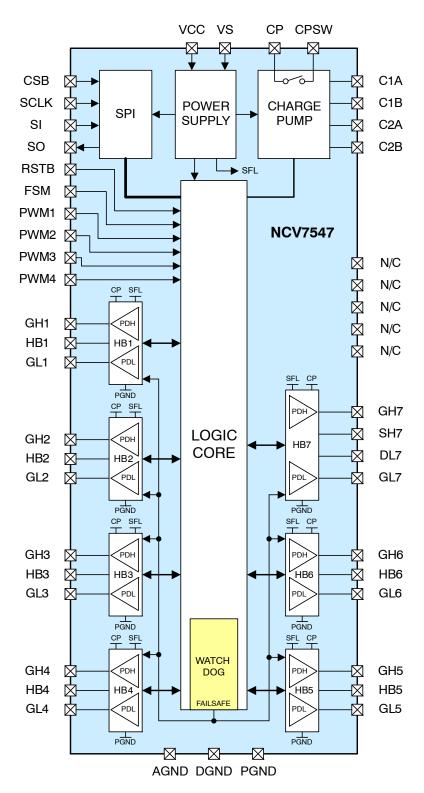

Figure 2. Application Diagram

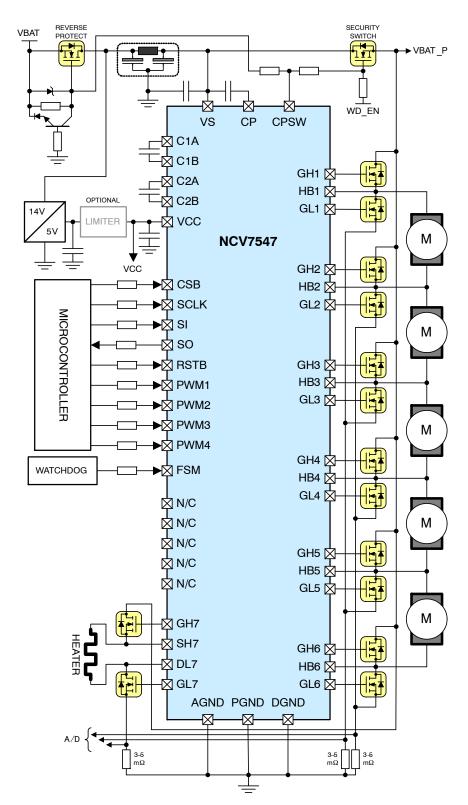

## PACKAGE PIN DESCRIPTION

| Pin    | Label        | Function                       | Description                                                                                                                                                                                                 |

|--------|--------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 48 PII | N QFN EXPOSE | D PAD PACKAGE                  |                                                                                                                                                                                                             |

| 42     | VS           | Main Power Supply              | Main high-power device supply (battery) input; VDS sense reference node for the half-bridge high-side drivers. An external ceramic bypass capacitor shall be connected between VS and GND close to the pin. |

| 36     | VCC          | Logic Supply                   | SPI block and internal logic and low power (analog) supply input. An external ceramic bypass capacitor shall be connected between VCC and GND close to the pin.                                             |

| 24     | AGND         | Signal Ground                  | Low power return path; reference for the analog circuitry.                                                                                                                                                  |

| 25     | DGND         | Digital Ground                 | Low power return path; reference for the digital circuitry.                                                                                                                                                 |

| 13     | PGND         | Power Ground                   | High power return path; reference for the half-bridge drivers; VDS sense reference node for the half-bridge low-side drivers.                                                                               |

| 45     | C1A          | Charge Pump                    | Switching nodes for external ceramic charge pumping capacitors 1 & 2.                                                                                                                                       |

| 46     | C1B          | Switch Node                    |                                                                                                                                                                                                             |

| 47     | C2A          | ]                              |                                                                                                                                                                                                             |

| 48     | C2B          | 1                              |                                                                                                                                                                                                             |

| 43     | СР           | Charge Pump<br>Output          | Charge pump output; an external ceramic buffer capacitor shall be connected between CP and VS to provide stable output voltage during transient noise on VS.                                                |

| 44     | CPSW         | Charge Pump<br>Switched Output | Switched charge pump output; activates external reverse battery and security power MOSFET switches via SPI.                                                                                                 |

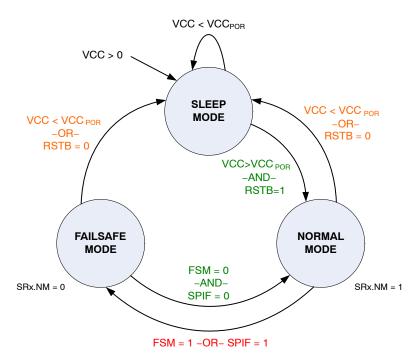

| 29     | RSTB         | Wake Input                     | Digital input with falling edge digital de–glitch and pull–down resistor; active low master reset; the device is in wake state when the pin is high.                                                        |

| 34     | FSM          | Fail-safe Input                | Digital input with symmetrical digital de-glitch and pull-down resistor; active high fail-safe mode (can be set via an external watchdog circuit).                                                          |

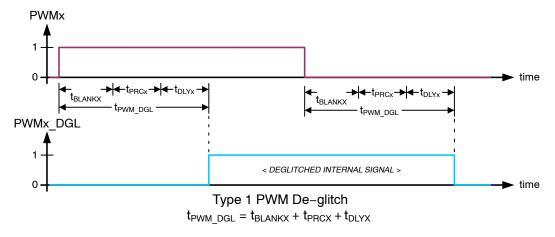

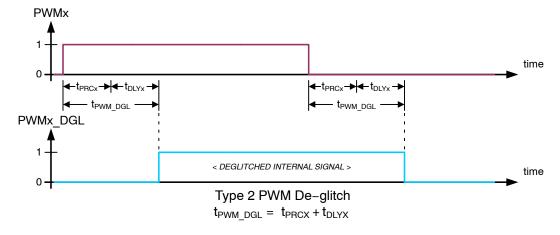

| 33     | PWM1         | PWM Inputs                     | Digital inputs with symmetrical adaptive digital de-glitch and pull-down resistor; provide                                                                                                                  |

| 32     | PWM2         | 1                              | PWM signals to the half-bridge pre-drivers.                                                                                                                                                                 |

| 31     | PWM3         | 1                              |                                                                                                                                                                                                             |

| 30     | PWM4         | 1                              |                                                                                                                                                                                                             |

| 26     | CSB          | SPI Chip Select                | Digital input with pull-up resistor; active low chip select.                                                                                                                                                |

| 27     | SCLK         | SPI Clock                      | Digital input with pull-down resistor.                                                                                                                                                                      |

| 28     | SI           | SPI Serial Input               | Digital input with pull-down resistor.                                                                                                                                                                      |

| 35     | SO           | SPI Serial Output              | Digital tri-state output with high-side path protection to prevent VCC back-bias in the event of an external voltage regulator failure or short to VS.                                                      |

| 2      | GH1          | High-side                      | High-side pre-drivers with pull-down resistor to HBx switch nodes; gate drive for external                                                                                                                  |

| 5      | GH2          | Pre-driver<br>Output           | logic-level N-MOS FETs.                                                                                                                                                                                     |

| 8      | GH3          | 1                              |                                                                                                                                                                                                             |

| 11     | GH4          | 1                              |                                                                                                                                                                                                             |

| 15     | GH5          |                                |                                                                                                                                                                                                             |

| 18     | GH6          | <u> </u>                       |                                                                                                                                                                                                             |

| 3      | HB1          | Half-bridge                    | Monitoring inputs for external half-bridge switches 1:6 with pull-down resistor to AGND;                                                                                                                    |

| 6      | HB2          | Switch Node                    | high-side MOSFET source node; low-side MOSFET drain node.                                                                                                                                                   |

| 9      | HB3          | ]                              |                                                                                                                                                                                                             |

| 12     | HB4          | ]                              |                                                                                                                                                                                                             |

| 16     | HB5          |                                |                                                                                                                                                                                                             |

| 19     | HB6          | ]                              |                                                                                                                                                                                                             |

## **PACKAGE PIN DESCRIPTION**

| Pin   | Label                         | Function                       | Description                                                                                                     |  |  |  |  |  |  |

|-------|-------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 48 PI | 8 PIN QFN EXPOSED PAD PACKAGE |                                |                                                                                                                 |  |  |  |  |  |  |

| 1     | GL1                           | Low-side<br>Pre-driver         | Low-side pre-drivers with pull-down resistor to PGND;<br>gate drive for external logic-level N-MOS FETs.        |  |  |  |  |  |  |

| 4     | GL2                           | Output                         | gate drive for external logic-level N-INIOS FETS.                                                               |  |  |  |  |  |  |

| 7     | GL3                           |                                |                                                                                                                 |  |  |  |  |  |  |

| 10    | GL4                           |                                |                                                                                                                 |  |  |  |  |  |  |

| 14    | GL5                           |                                |                                                                                                                 |  |  |  |  |  |  |

| 17    | GL6                           |                                |                                                                                                                 |  |  |  |  |  |  |

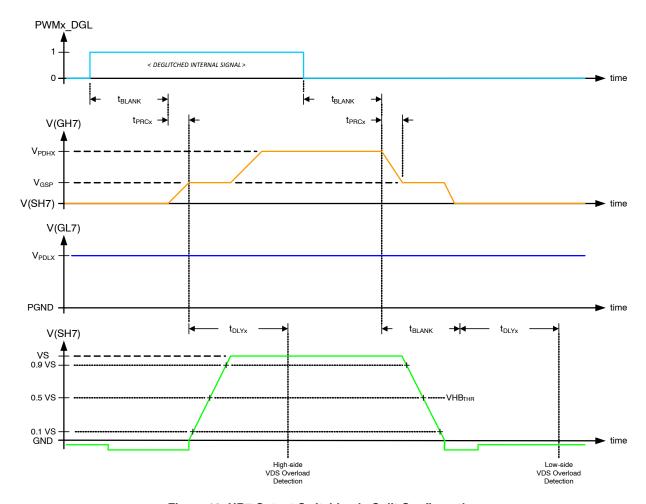

| 22    | GH7                           | High-side Pre-driver<br>Output | High-side pre-driver with pull-down resistor to SH7 input; gate drive for external logic-level N-MOS FETs.      |  |  |  |  |  |  |

| 23    | SH7                           | High-side<br>Source Node       | Monitoring input for external high-side switch 7 with pull-down resistor to AGND; high-side MOSFET source node. |  |  |  |  |  |  |

| 21    | DL7                           | Low-side<br>Drain Node         | Monitoring input for external low-side switch 7 with pull-down resistor to AGND; low-side MOSFET drain node.    |  |  |  |  |  |  |

| 20    | GL7                           | Low-side Pre-driver<br>Output  | Low-side pre-driver with pull-down resistor to PGND; gate drive for external logic-level N-MOS FETs.            |  |  |  |  |  |  |

| 41    | N/C                           | -                              | No internal connection.                                                                                         |  |  |  |  |  |  |

| 40    | N/C                           |                                |                                                                                                                 |  |  |  |  |  |  |

| 39    | N/C                           |                                |                                                                                                                 |  |  |  |  |  |  |

| 38    | N/C                           |                                |                                                                                                                 |  |  |  |  |  |  |

| 37    | N/C                           |                                |                                                                                                                 |  |  |  |  |  |  |

|       | EP                            | Exposed Pad                    | Connect to GND.                                                                                                 |  |  |  |  |  |  |

Figure 3. 32 Pin 5 x 5 mm Exposed Pad Pin-out (Top View)

## MAXIMUM RATINGS (Except as noted, voltages are with respect to AGND = DGND = PGND = GND.)

|                    | Rating                                                           | Symbol                       | Value                    | Unit |

|--------------------|------------------------------------------------------------------|------------------------------|--------------------------|------|

| VS Supply          | DC: 2 min @ 25°C<br>AC: ISO7637 Pulse 5b, 400 ms @ 25°C          | VS <sub>MAX</sub>            | -0.3 to 28<br>40         | V    |

| VCC Supply         |                                                                  | VCC <sub>MAX</sub>           | -0.3 to 7.0              | V    |

| Output Voltage:    | CP, CPSW<br>SO                                                   | $V\_OUT_{MAX} \ V\_SO_{MAX}$ | -0.3 to 40<br>-0.3 to 20 | V    |

| Input Voltage:     | FSM, C1A, C1B, C2A, C2B                                          | V_IN <sub>MAX1</sub>         | -0.3 to 40               | V    |

| Input Voltage (Cla | mped): HBx, SH7, DL7                                             | V_IN <sub>MAX2</sub>         | –1.0 to 40               | V    |

| Input Voltage:     | CSB, SCLK, SI, RSTB, PWMx                                        | V_IN <sub>MAX3</sub>         | -0.3 to 20               | V    |

| Input Current (Cla | mped): CSB, SCLK, SI, RSTB, FSM, PWMx, GHx, GLx                  | I_IN <sub>MAX</sub>          | ± 5.0                    | mA   |

| Junction Temperat  | ure                                                              | $T_J$                        | -40 to 150               | °C   |

| Storage Temperat   | ure                                                              | T <sub>STG</sub>             | -55 to 150               | °C   |

| Peak Reflow Solde  | ering Temperature: Lead-free 60 to 150 seconds at 217°C (Note 1) | T <sub>PK</sub>              | 260                      | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### **ATTRIBUTES**

| Characteristic                                                                        | Symbol               | Value           | Unit |

|---------------------------------------------------------------------------------------|----------------------|-----------------|------|

| ESD Capability:                                                                       | V <sub>ESD_HBM</sub> |                 |      |

| Human Body Model per AEC-Q100-002                                                     | _                    |                 |      |

| All pins                                                                              |                      | ≥ ± 2.0         | kV   |

| VS, HBx, SH7, DL7                                                                     |                      | ≥ ± 4.0         | kV   |

| Charged Device Model per AEC-Q100-011                                                 | V <sub>ESD CDM</sub> |                 |      |

| All Pins                                                                              | _                    | ≥ ± 500         | V    |

| Corner Pins                                                                           |                      | ≥ ± <b>7</b> 50 | V    |

| Moisture Sensitivity (Note 1)                                                         | MSL                  | 1               | _    |

| Package Thermal Resistance – Still-air, P <sub>IN</sub> = 1 W (Uniform Power Density) |                      |                 | °C/W |

| Junction–to–Ambient, Rθ <sub>JA</sub> (Note 2)                                        | $R\theta_{JA}$       | 61.7            |      |

| (Note 3)                                                                              | $R\theta_{JA}$       | 37.5            |      |

| Junction–to–Exposed Pad, RΨ <sub>JPAD</sub>                                           | $R\Psi_JPAD$         | 10.8            |      |

<sup>2.</sup> Based on JESD51-3, 1.2 mm thick FR4, 2S0P PCB, 1 oz. signal, 4 thermal vias to 28 x 28 mm 1 oz. spreader on bottom layer.

## **RECOMMENDED OPERATING CONDITIONS**

| Parameter                                          | Symbol               | Min | Max               | Unit |

|----------------------------------------------------|----------------------|-----|-------------------|------|

| Main Power Supply Voltage                          | VS <sub>OP</sub>     | 7.0 | 18.0              | V    |

| Logic Power Supply Voltage                         | VCC <sub>OP</sub>    | 4.5 | 5.5               | V    |

| Logic High Input Voltage                           | V <sub>IN_HIGH</sub> | 3.5 | VCC <sub>OP</sub> | V    |

| Logic Low Input Voltage                            | V <sub>IN_LOW</sub>  | 0   | 1.5               | V    |

| Half-bridge Output PWM Rate                        | f <sub>PWM</sub>     | -   | 25                | kHz  |

| Charge Pump Capacitors (C1, C2, CCP)               | -                    | 220 | 4700              | nF   |

| SPI Clock Frequency                                | f <sub>SCLK</sub>    | 0.1 | 2.5               | MHz  |

| Startup Delay at VCC Power-On Reset (POR) (Note 4) | t <sub>RESET</sub>   | =   | 200               | μs   |

| Ambient Still-Air Operating Temperature            | T <sub>A</sub>       | -40 | 125               | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

<sup>1.</sup> See or download ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D

<sup>3.</sup> Based on JESD51-7, 1.2 mm thick FR4, 1S2P PCB, 1 oz. signal, 4 thermal vias to 76 x 76 mm 1 oz. internal spreader planes.

<sup>4.</sup> Minimum wait time until device is ready to accept serial input data.

## **PARAMETRIC TABLES**

## **ELECTRICAL CHARACTERISTICS**

$(4.5 \text{ V} \leq \text{VCC} \leq 5.5 \text{ V}, 7.0 \text{ V} \leq \text{VS} \leq 18 \text{ V}, \text{ RSTB} = \text{VCC}, \text{ CR1.D[10]} = 1, -40^{\circ}\text{C} \leq \text{T}_{J} \leq 150^{\circ}\text{C}, \text{ unless otherwise specified.}) \text{ (Note 5)}$

| •                                                      | •                                       | , , , , , , , , , , , , , , , , , , , ,                                                                                                                  |        | •             | , ,    |          |

|--------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|--------|----------|

| Characteristic                                         | Symbol                                  | Conditions                                                                                                                                               | Min    | Тур           | Max    | Unit     |

| VS SUPPLY                                              |                                         |                                                                                                                                                          |        |               |        |          |

| Standby Current                                        | I <sub>VS_SBY</sub>                     | $\begin{aligned} &VS = 12.0 \text{V},  0  \leq  \text{VCC}  \leq  5.5   \text{V},  \text{RSTB} = 0, \\ &T_{\text{A}} = 25^{\circ}\text{C} \end{aligned}$ | -      | _             | 5.0    | μΑ       |

| Operating Current                                      | I <sub>VS_OP0</sub>                     | VCC = 5.0 V , RSTB = 1, T <sub>A</sub> = 25°C Default Settings at POR, SPI Inactive CR1.D[10]=0                                                          | -      | 1.6           | 5.0    | mA       |

|                                                        | I <sub>VS_OP1</sub>                     | CR1.D[10]=1                                                                                                                                              | =      | 20.3          | 25.0   | mA       |

| Under-voltage Lockout                                  | VS <sub>UVLO</sub>                      | VS decreasing, SR0.D[5] → 1                                                                                                                              | 4.5    | 5.0           | 5.5    | V        |

| Under-voltage Hysteresis                               | VS <sub>UVHY</sub>                      | $SR0.D[5] \rightarrow 0$ (after read status if VS > $VS_{UVLO+UVHY}$ )                                                                                   | 100    | 200           | _      | mV       |

| Under-voltage Filter Time                              | t <sub>UVDGL</sub>                      | VS decreasing                                                                                                                                            | 4.0    | 5.0           | 6.0    | μs       |

| Over-voltage Shutdown                                  | VS <sub>OVSDR</sub>                     | VS increasing, SR0.D[4] → 1                                                                                                                              | 19.0   | 20.0          | 21.0   | V        |

|                                                        | VS <sub>OVSDF</sub>                     | VS decreasing, SR0.D[4] → 0                                                                                                                              | 18.0   | 19.0          | 20.0   | V        |

| Over-voltage Hysteresis                                | VS <sub>OVHY</sub>                      | $SR0.D[4] \rightarrow 0$ (after read status if $VS < VS_{OV - OVHY}$ )                                                                                   | _      | 0.9           | =      | V        |

| Over-voltage Filter Time                               | t <sub>OVDGL</sub>                      | VS increasing                                                                                                                                            | 4.0    | 5.0           | 6.0    | μs       |

| VS PWM Threshold                                       | VS <sub>PWM</sub>                       | VS decreasing, SR0.D[7] → 1                                                                                                                              | 8.90   | 9.45          | 10.0   | V        |

| VS PWM Hysteresis                                      | VS <sub>PWM_HY</sub>                    | $SR0.D[7] \rightarrow 0$ and/or $SR0.D[6] \rightarrow 0$ (after read status if $VS > VS_{PWM + PWM\_HY}$ )                                               | -      | 100           | _      | mV       |

| VCC SUPPLY                                             |                                         |                                                                                                                                                          |        |               |        |          |

| Standby Current                                        | I <sub>VCC_SBY</sub>                    | VS = 12.0V, VCC = 5.5 V , RSTB = 0, T <sub>A</sub> = 25°C<br>Default Settings at POR, SPI Inactive                                                       | -      | _             | 5.0    | μΑ       |

| Operating Current                                      | I <sub>VCC_OP</sub>                     | VS = 12.0V, RSTB = 1, T <sub>A</sub> = 25°C                                                                                                              | -      | 8.0           | 12.0   | mA       |

| Power-On Reset Threshold                               | VCC <sub>PORR</sub>                     | VCC Increasing                                                                                                                                           | 3.71   | 4.10          | 4.49   | V        |

|                                                        | VCC <sub>PORF</sub>                     | VCC Decreasing                                                                                                                                           | 3.50   | 3.85          | 4.20   | V        |

| CHARGE PUMP                                            |                                         |                                                                                                                                                          |        |               |        |          |

|                                                        |                                         | C1 = C2 = 470 nF; CCP = 1000 nF                                                                                                                          |        |               |        |          |

| Switching Frequency                                    | f <sub>CP</sub>                         | Single-stage, complementary-phase topology                                                                                                               | 0.75   | 1.10          | 1.45   | MHz      |

| Spread Spectrum<br>Modulation Depth<br>Modulation Rate | CP <sub>MOD</sub><br>f <sub>CPMOD</sub> | (Note 6)                                                                                                                                                 | -<br>- | ±15.0<br>45.6 | -<br>- | %<br>kHz |

| Regulation Voltage                                     | CP <sub>REG</sub>                       | $V(CP, VS), VS > VS_{PWM}, 0 \le I(CP) \le 15 \text{ mA}$                                                                                                | 8.3    | 8.9           | 9.5    | V        |

| Startup Delay                                          | CP <sub>DLY</sub>                       | VS = 13V, I(CP) = no load (Note 6)<br>C1 = C2 = 470 nF, CCP = 1000 nF                                                                                    | _      | -             | 500    | μs       |

| Dropout Voltage                                        | CP <sub>DROP0</sub>                     | V(VS) - V(CP, VS), I(CP) = 10 mA, VS=9.4                                                                                                                 | -      | _             | 1.50   |          |

|                                                        | OD                                      | V(VS) - V(CP, VS), I(CP) = 15 mA,                                                                                                                        | -      | -             | 1.75   | V        |

|                                                        | CP <sub>DROP1</sub>                     | VS=10V and SR0.D[7] = 0 $T_J \ge 125^{\circ}C$                                                                                                           | -      | _             | 1.90   |          |

| Charge Pump Low Detection                              | CP <sub>LOW0</sub>                      | $V(CP, VS)$ decreasing, $VS > VS_{PWM}$ , $SR0.D[7] \rightarrow 1$                                                                                       | 7.3    | 8.0           | 8.8    | V        |

|                                                        | CP <sub>LOW1</sub>                      | Detection margin, CP <sub>LOW1</sub> = CP <sub>REG</sub> – CP <sub>LOW0</sub>                                                                            | 300    | -             | _      | mV       |

| Charge Pump Low Detection Filter Time                  | t <sub>CPL_DGL</sub>                    |                                                                                                                                                          | 120    | 150           | 180    | μs       |

| Charge Pump Low Hysteresis                             | CP <sub>LOW_HY</sub>                    | SR0.D[7] → 0<br>(after read status if V(CP,VS) > CP <sub>LOW+LOW HY</sub> )                                                                              | _      | 100           | _      | mV       |

<sup>5.</sup> Min/Max values are valid for the stated temperature range unless noted otherwise. Min/Max values are guaranteed by test, design or statistical correlation

<sup>6.</sup> No production test

<sup>7.</sup> These values, measured in production via test mode, result in values that are t<sub>SYNC</sub> longer than the stated values. The specification limits shall therefore be: (t<sub>CAL\_PCx</sub> Typ + t<sub>SYNC</sub> Typ) ±20%, (t<sub>CAL\_DLYx</sub> Typ + t<sub>SYNC</sub> Typ) ±20%, and (t<sub>DLYX</sub> Typ + t<sub>SYNC</sub> Typ) ±20%.

## **ELECTRICAL CHARACTERISTICS**

$(4.5 \text{ V} \le \text{VCC} \le 5.5 \text{ V}, 7.0 \text{ V} \le \text{VS} \le 18 \text{ V}, \text{ RSTB} = \text{VCC}, \text{ CR1.D}[10] = 1, -40^{\circ}\text{C} \le \text{T}_{J} \le 150^{\circ}\text{C}, \text{ unless otherwise specified.})$  (Note 5)

| Characteristic                         | Symbol                | Conditions                                                                          | Min          | Тур   | Max     | Unit |

|----------------------------------------|-----------------------|-------------------------------------------------------------------------------------|--------------|-------|---------|------|

| CHARGE PUMP                            |                       |                                                                                     | •            | •     | •       | •    |

| Charge Pump Fail Detection             | CP <sub>FAIL</sub>    | V(CP, VS) decreasing, SR0.D[6] → 1                                                  | 4.925        | 5.375 | 5.750   | V    |

| Charge Pump Fail Detection Filter Time | t <sub>CPF_DGL</sub>  |                                                                                     | 120          | 150   | 180     | μs   |

| Charge Pump Fail Hysteresis            | CP <sub>FAIL_HY</sub> | $SR0.D[6] \rightarrow 0$<br>(after read status if $V(CP,VS) > CP_{FAIL+FAIL\_HY}$ ) | -            | 100   | -       | mV   |

| Charge Pump Over-voltage<br>Detection  | CP <sub>OV</sub>      | VS increasing                                                                       | 28.0         | 30.25 | 32.5    | V    |

| Charge Pump Over-voltage<br>Hysteresis | CP <sub>OV_HYS</sub>  |                                                                                     | 0.5          | 1.0   | 2.0     | V    |

| CP Switch Resistance                   | R <sub>CPTOT</sub>    | *Guaranteed by Simulation*<br>8x CP switches in parallel, T <sub>A</sub> = 25°C     | -            | 1.5   | _       | Ω    |

| Switched CP Output Resistance          | R <sub>CPSW_ON</sub>  | CR1.D[9] = 1, I(CPSW) = 5 mA                                                        | -            | _     | 100     | Ω    |

| Switched CP Output Leakage             | CP <sub>SW_LKG</sub>  | CR1.D[9] = 0                                                                        | -1.0         | 0     | 1.0     | uA   |

| DIGITAL I/O                            |                       |                                                                                     |              |       |         |      |

| V <sub>IN_X</sub> High                 | $V_{INHX}$            | CSB, SCLK, SI, RSTB, FSM, PWMx                                                      | 3.5          | _     | _       | V    |

| V <sub>IN_X</sub> Low                  | $V_{INLX}$            | CSB, SCLK, SI, RSTB, FSM, PWMx                                                      | -            | -     | 1.5     | V    |

| Input Pull-down Resistance             | R <sub>PDX</sub>      | SCLK, SI, RSTB, FSM, PWMx, V <sub>INX</sub> = VCC                                   | 70           | 100   | 130     | kΩ   |

| Input Pull-up Resistance               | R <sub>PU</sub>       | CSB, V <sub>IN</sub> = 0V                                                           | 70           | 100   | 130     | kΩ   |

| Input Current                          | I <sub>INX</sub>      | $V_{INX}$ = 5.5V: SCLK, SI, RSTB, FSM, PWMx<br>$V_{INX}$ = 0V: CSB                  | _<br>-80     | 0     | 80<br>- | μΑ   |

| Input Leakage                          | I <sub>IN_LKG</sub>   | V <sub>INX</sub> = 0V: SCLK, SI, RSTB, FSM, PWMx<br>V <sub>INX</sub> = VCC: CSB     | -1.0         | 0     | 1.0     | μΑ   |

| Input Filter Time                      | t <sub>IN_DGL</sub>   | FSM input                                                                           | 8.0          | 10    | 12      | μS   |

| Reset De-glitch Time                   | t <sub>RST_DGL</sub>  | Minimum RSTB pulse (H $\rightarrow$ L $\rightarrow$ H) detected                     | 8.0          | -     | _       | μs   |

| Reset Assert Time                      | t <sub>WRST</sub>     | Minimum RSTB hold after H → L transition                                            | _            | 11    | 15      | μs   |

| SO Low Voltage                         | $V_{SOL}$             | I <sub>SINK</sub> = 1.0 mA                                                          | _            | _     | 0.4     | V    |

| SO High Voltage                        | V <sub>SOH</sub>      | I <sub>SOURCE</sub> = 1.0 mA                                                        | VCC -<br>0.4 | _     | -       | V    |

| SO Tri-State Leakage Current           | SO <sub>LKG</sub>     | CSB = VCC, SO = VCC/2                                                               | -1.0         | -     | 1.0     | μΑ   |

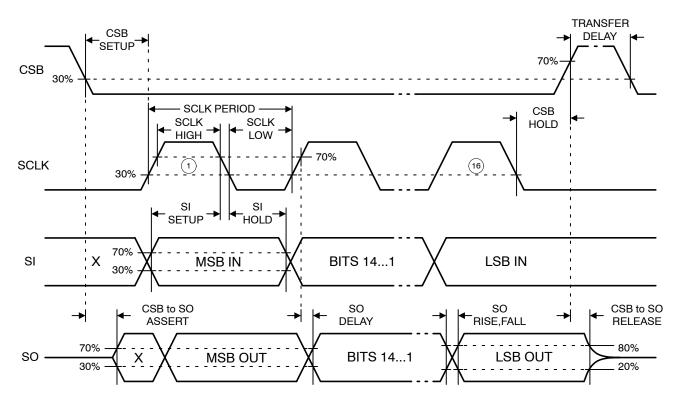

#### SERIAL PERIPHERAL INTERFACE (See Figure 4)

| VCC = 5.0V, FSCLK = 2.5 MHz, CLOAD = 80 pF, all timing is at 30% and 70% VCC unless otherwise specified. |                    |                                  |          |     |    |    |    |

|----------------------------------------------------------------------------------------------------------|--------------------|----------------------------------|----------|-----|----|----|----|

| SCLK Clock Period                                                                                        | t <sub>SCLK</sub>  |                                  |          | 400 | =  | =  | ns |

| SCLK High Time                                                                                           | t <sub>CLKH</sub>  | SCLK = 70% VCC to 70% VCC        |          | 200 | =  | =  | ns |

| SCLK Low Time                                                                                            | t <sub>CLKL</sub>  | SCLK = 30% VCC to 30% VCC        |          | 200 | =  | =  | ns |

| Maximum Input Capacitance                                                                                | C <sub>INX</sub>   | SCLK, SI                         | (Note 6) | =   | =  | 15 | pF |

| SI Setup Time                                                                                            | t <sub>SISU</sub>  | SI = 30% 70% to SCLK = 70% VCC   | (Note 6) | 25  | =  | =  | ns |

| SI Hold Time                                                                                             | t <sub>SIHD</sub>  | SCLK = 30% to SI = 30%   70% VCC | (Note 6) | 25  | =  | =  | ns |

| SO Rise Time                                                                                             | t <sub>SOR</sub>   | (20% V <sub>SO</sub> to 80% VCC) | (Note 6) | =   | 25 | 50 | ns |

| SO Fall Time                                                                                             | t <sub>SOF</sub>   | (80% V <sub>SO</sub> to 20% VCC) | (Note 6) | =   | =  | 50 | ns |

| CSB Setup Time                                                                                           | t <sub>CSBSU</sub> | CSB = 30% to SCLK = 30% VCC      | (Note 6) | 60  | =  | =  | ns |

| CSB Hold Time                                                                                            | t <sub>CSBHD</sub> | SCLK = 30% to CSB = 70% VCC      | (Note 6) | 75  | _  | =  | ns |

<sup>5.</sup> Min/Max values are valid for the stated temperature range unless noted otherwise. Min/Max values are guaranteed by test, design or statistical correlation

<sup>6.</sup> No production test

<sup>7.</sup> These values, measured in production via test mode, result in values that are t<sub>SYNC</sub> longer than the stated values. The specification limits shall therefore be: (t<sub>CAL\_PCx</sub> Typ + t<sub>SYNC</sub> Typ) ±20%, (t<sub>CAL\_DLYx</sub> Typ + t<sub>SYNC</sub> Typ) ±20%, and (t<sub>DLYx</sub> Typ + t<sub>SYNC</sub> Typ) ±20%.

## **ELECTRICAL CHARACTERISTICS**

$(4.5 \text{ V} \leq \text{VCC} \leq 5.5 \text{ V}, 7.0 \text{ V} \leq \text{VS} \leq 18 \text{ V}, \text{ RSTB} = \text{VCC}, \text{ CR1.D[10]} = 1, -40^{\circ}\text{C} \leq \text{T}_{J} \leq 150^{\circ}\text{C}, \text{ unless otherwise specified.}) \text{ (Note 5)}$

| Characteristic           | Symbol                                     | Conditions                                                                                           | Min | Тур | Max | Unit |  |  |

|--------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------|-----|-----|-----|------|--|--|

| SERIAL PERIPHERAL INTERF | SERIAL PERIPHERAL INTERFACE (See Figure 4) |                                                                                                      |     |     |     |      |  |  |

| CSB to SO Assert Time    | t <sub>SO_A</sub>                          | $ CSB = 30\% \ VCC \ to \ SO = 30\%   70\% \ VCC \\ RLOAD = 5 \ kΩ                                 $ | -   | 65  | 125 | ns   |  |  |

| CSB to SO Release Time   | t <sub>SO_R</sub>                          | CSB = 70% VCC to $SO = 20%  80%$ VCC/2<br>RLOAD = 5 kΩ (Note 6)                                      | -   | -   | 350 | ns   |  |  |

| SO Delay Time            | SO <sub>DLY</sub>                          | SCLK = 70% VCC to SO = 30% 70% (Note 6)                                                              | -   | 65  | 125 | ns   |  |  |

| Transfer Delay Time      | CS <sub>DLY</sub>                          | CSB rising edge to next falling edge. (Note 6)                                                       | ı   | -   | 1.0 | μs   |  |  |

## HALF-BRIDGE PRE-DRIVER OUTPUTS

|                                                        |                       | VS > VS <sub>PWM</sub>                                                          |       |      |       |    |

|--------------------------------------------------------|-----------------------|---------------------------------------------------------------------------------|-------|------|-------|----|

| On-state Drive Voltage                                 | V <sub>PDHX</sub>     | High-side, V <sub>PDHX</sub> = H = V(GHx, HBx) or V(GHX, SH7), No External Load | 8.3   | _    | 9.5   | V  |

|                                                        | V <sub>PDLX</sub>     | Low-side, V <sub>PDLX</sub> = H =V(GLx, PGND),<br>No External Load              | 8.1   | =    | 9.8   | V  |

| High-side driver Gate-source<br>Clamp Positive Voltage | V <sub>GSX_CLPH</sub> | V(GHx, HBx), V(GH7, SH7), I <sub>CLMP</sub> = 3.0 mA                            | 14.0  | _    | 18.0  | V  |

| High-side driver Source-gate Clamp Negative Voltage    | V <sub>SGX_CLPH</sub> | V(HBx, GHx), V(SH7, GH7), I <sub>CLMP</sub> = -2.0 mA                           | -20.0 | _    | -16.0 | V  |

| Low-side driver Gate-source<br>Clamp Positive Voltage  | V <sub>GSX_CLPL</sub> | V(GLx, PGND), I <sub>CLMP</sub> = 10 mA                                         | 11.5  | _    | 15.0  | V  |

| Low-side driver Gate-source<br>Clamp Negative Voltage  | V <sub>GSX_CLN</sub>  | V(GLx, PGND), I <sub>CLMP</sub> = -1.0 mA                                       | -1.0  | _    | _     | V  |

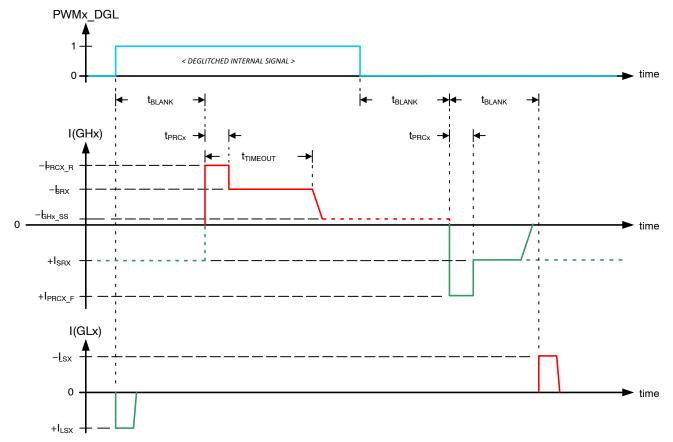

| Gate Drive Timeout                                     | t <sub>TIMEOUT</sub>  | $I_{GHx} \le I_{GHx\_SS}$                                                       | 16    | 20   | 24    | μs |

| Gate Drive Timeout Current                             | I <sub>GHx_SS</sub>   | V(GHx, HBx) or V(GHx, SH7) = 0 V, t > t <sub>TIMEOUT</sub>                      | -1.2  | -1.0 | -0.8  | mA |

| Gate-source Pull-down<br>Resistor                      | R <sub>GSX</sub>      | R(GHx, HBx), R(GHx, SH7), R(GLx, PGND)                                          | 70    | _    | 130   | kΩ |

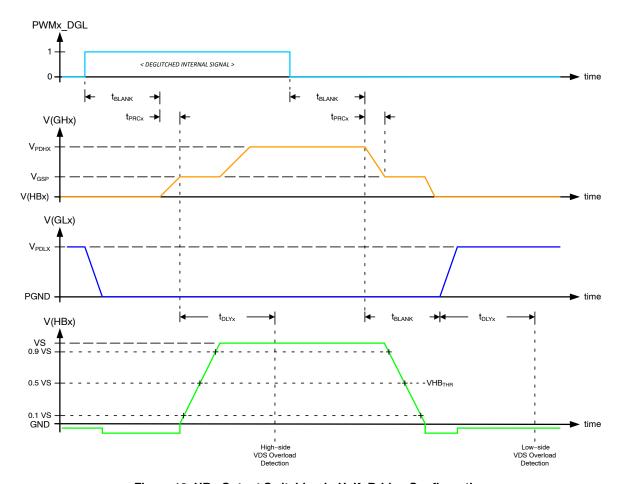

| Cross Conduction Blank Time                            |                       | BLANKx[1:0] = 0x00                                                              | 0.8   | 1.0  | 1.2   |    |

| Ollin Olin                                             | ١.                    | BLANKx[1:0] = 0x01                                                              | 1.6   | 2.0  | 2.4   |    |

| GHx, GLx                                               | <sup>t</sup> BLANKX   | BLANKx[1:0] = 0x02                                                              | 2.4   | 3.0  | 3.6   | μs |

|                                                        |                       | BLANKx[1:0] = 0x03                                                              | 3.2   | 4.0  | 4.8   |    |

#### PRE-DRIVER SLOPE CONTROL

|                              |                     | VS > VS <sub>PWM</sub> |       |       |       |        |

|------------------------------|---------------------|------------------------|-------|-------|-------|--------|

| High-side Pre-charge Time    |                     | T_PCx[1:0] = 0x00      | 80    | 100   | 120   |        |

| GHx Rising and Falling Slope |                     | T_PCx[1:0] = 0x01      | 160   | 200   | 240   | ]      |

|                              | t <sub>PRCX</sub>   | T_PCx[1:0] = 0x02      | 240   | 300   | 360   | ns     |

|                              |                     | T_PCx[1:0] = 0x03      | 320   | 400   | 480   |        |

| High-side Pre-charge Current |                     | I_PCRx[2:0] = 0x00     | 1.23  | 1.50  | 1.77  |        |

| GHx Rising Slope             |                     | I_PCRx[2:0] = 0x01     | 4.52  | 5.25  | 5.99  |        |

| V(GHx) = 3.5 V               |                     | I_PCRx[2:0] = 0x02     | 7.42  | 8.63  | 9.84  |        |

|                              | ١,                  | I_PCRx[2:0] = 0x03     | 10.65 | 12.38 | 14.11 | ]<br>^ |

|                              | I <sub>PRCX_R</sub> | I_PCRx[2:0] = 0x04     | 14.19 | 16.50 | 18.81 | mA     |

|                              |                     | I_PCRx[2:0] = 0x05     | 17.42 | 20.25 | 23.09 |        |

|                              |                     | I_PCRx[2:0] = 0x06     | 20.64 | 24.00 | 27.36 |        |

|                              |                     | I_PCRx[2:0] = 0x07     | 24.19 | 28.13 | 32.07 |        |

- 5. Min/Max values are valid for the stated temperature range unless noted otherwise. Min/Max values are guaranteed by test, design or statistical correlation

- No production test

These values, measured in production via test mode, result in values that are t<sub>SYNC</sub> longer than the stated values. The specification limits shall therefore be: (t<sub>CAL\_PCx</sub> Typ + t<sub>SYNC</sub> Typ) ±20%, (t<sub>CAL\_DLYx</sub> Typ + t<sub>SYNC</sub> Typ) ±20%, and (t<sub>DLYX</sub> Typ + t<sub>SYNC</sub> Typ) ±20%.

## **ELECTRICAL CHARACTERISTICS**

$(4.5 \text{ V} \leq \text{VCC} \leq 5.5 \text{ V}, 7.0 \text{ V} \leq \text{VS} \leq 18 \text{ V}, \text{ RSTB} = \text{VCC}, \text{ CR1.D} \\ [10] = 1, -40^{\circ}\text{C} \leq \text{T}_{\text{J}} \leq 150^{\circ}\text{C}, \text{ unless otherwise specified.}) \text{ (Note 5)}$

| Characteristic                  | Symbol              | Conditions                              | Min      | Тур    | Max      | Unit  |

|---------------------------------|---------------------|-----------------------------------------|----------|--------|----------|-------|

| PRE-DRIVER SLOPE CONTRO         | DL                  |                                         |          |        |          |       |

| High-side Pre-charge Current    |                     | I_PCFx[2:0] = 0x00                      | 24.84    | 28.88  | 32.92    |       |

| GHx Falling Slope               |                     | I_PCFx[2:0] = 0x01                      | 30.64    | 35.63  | 40.62    |       |

| V(GHx) = (VS + 3.5) V           |                     | I_PCFx[2:0] = 0x02                      | 36.12    | 42.00  | 47.88    |       |

|                                 |                     | I_PCFx[2:0] = 0x03                      | 41.61    | 48.38  | 55.15    | 4     |

|                                 | I <sub>PRCX_F</sub> | I_PCFx[2:0] = 0x04                      | 47.41    | 55.13  | 62.85    | mA    |

|                                 |                     | I_PCFx[2:0] = 0x05                      | 52.89    | 61.50  | 70.11    |       |

|                                 |                     | I_PCFx[2:0] = 0x06                      | 58.38    | 67.88  | 77.38    |       |

|                                 |                     | I_PCFx[2:0] = 0x07                      | 64.18    | 74.63  | 85.08    |       |

| High-side Slew Current          |                     | SR_CTRLx[2:0] = 0x00                    | 1.23     | 1.50   | 1.77     |       |

| GHx Rising and Falling Slope    |                     | SR_CTRLx[2:0] = 0x01                    | 1.94     | 2.25   | 2.57     |       |

| Rising: $V(GHx) = (VS + 3.5) V$ |                     | SR_CTRLx[2:0] = 0x02                    | 2.91     | 3.38   | 3.85     |       |

| Falling: V(GHx) = 3.5 V         |                     | SR_CTRLx[2:0] = 0x03                    | 4.52     | 5.25   | 5.99     | 4     |

|                                 | I <sub>SRX</sub>    | SR_CTRLx[2:0] = 0x04                    | 6.78     | 7.88   | 8.98     | mA    |

|                                 |                     | SR_CTRLx[2:0] = 0x05                    | 10.00    | 11.63  | 13.26    |       |

|                                 |                     | SR_CTRLx[2:0] = 0x06                    | 14.84    | 17.25  | 19.67    |       |

|                                 |                     | SR_CTRLx[2:0] = 0x07                    | 21.93    | 25.50  | 29.07    |       |

| Low-side Drive Current          |                     | SR_CTRLx[2:0] = 0x00                    | 5.16     | 6.00   | 6.84     |       |

| GLx Rising and Falling slope    |                     | SR_CTRLx[2:0] = 0x01                    | 7.74     | 9.00   | 10.26    |       |

| V(GLx) = 3.5 V                  |                     | SR_CTRLx[2:0] = 0x02                    | 11.63    | 13.52  | 15.41    |       |

| . ,                             |                     | SR_CTRLx[2:0] = 0x03                    | 18.06    | 21.00  | 23.94    | 4     |

|                                 | I <sub>LSX</sub>    | SR_CTRLx[2:0] = 0x04                    | 27.11    | 31.52  | 35.93    | mA    |

|                                 |                     | SR_CTRLx[2:0] = 0x05                    | 40.01    | 46.52  | 53.03    |       |

|                                 |                     | SR_CTRLx[2:0] = 0x06                    | 59.34    | 69.00  | 78.66    |       |

|                                 |                     | SR_CTRLx[2:0] = 0x07                    | 87.72    | 102.00 | 116.28   |       |

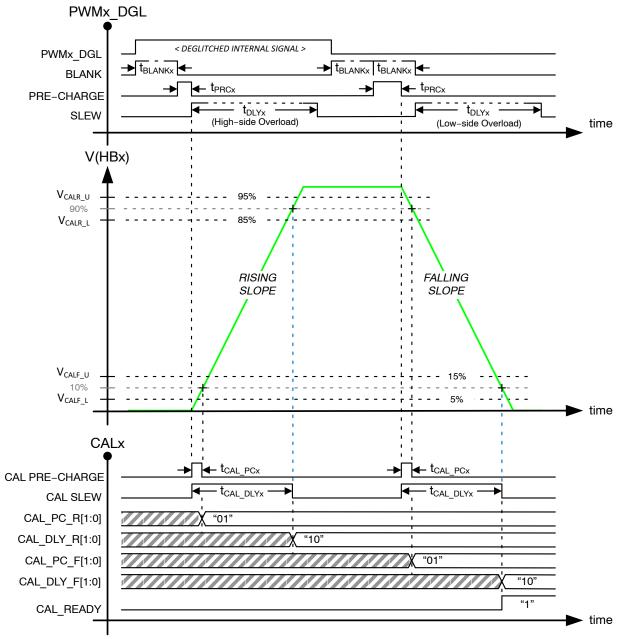

| SLOPE CONTROL CALIBRATI         | ON UNIT             |                                         |          |        |          |       |

| Slope Calibration Comparator    | V <sub>CALF_L</sub> | Falling slope window lower threshold    | 3.0      | 5.0    | 7.0      |       |

| Window Thresholds               | V <sub>CALF_U</sub> | Falling slope window upper threshold    | 13       | 15     | 17       | % VS  |

|                                 | V <sub>CALR_L</sub> | Rising slope window lower threshold     | 82       | 85     | 88       | % V3  |

|                                 | V <sub>CALR_U</sub> | Rising slope window upper threshold     | 92       | 95     | 98       |       |

| Comparator Propagation Delay    | t <sub>CAL_PD</sub> |                                         | -        | 62     | 100      | ns    |

| Sample Synchronization Delay    | t <sub>SYNC</sub>   | t <sub>SYNC</sub> = 2/f <sub>CORE</sub> | -        | 50     | =        | ns    |

| Calibration Pre-charge Time     |                     | CAL_PC[3:0] = 0x00                      |          | 50     |          |       |

| LIDy Diaina & Falling Clay      |                     | CAL_PC[3:0] = 0x01                      |          | 150    | ]        |       |

| HBx Rising & Falling Slope      | +                   | CAL_PC[3:0] = 0x02                      | (Noto 7) | 250    | (Note 7) | ns ns |

|                                 | tCAL_PCX            | CAL_PC[3:0] = 0x03                      | (Note 7) | 350    | (Note 7) |       |

|                                 |                     | CAL_PC[3:0] = 0x04                      |          | 450    | ]        |       |

|                                 |                     | CAL PC[3:0] = 0x05                      |          | 550    |          |       |

<sup>5.</sup> Min/Max values are valid for the stated temperature range unless noted otherwise. Min/Max values are guaranteed by test, design or statistical correlation

<sup>6.</sup> No production test

<sup>7.</sup> These values, measured in production via test mode, result in values that are t<sub>SYNC</sub> longer than the stated values. The specification limits shall therefore be: (t<sub>CAL\_PCx</sub> Typ + t<sub>SYNC</sub> Typ) ±20%, (t<sub>CAL\_DLYx</sub> Typ + t<sub>SYNC</sub> Typ) ±20%, and (t<sub>DLYx</sub> Typ + t<sub>SYNC</sub> Typ) ±20%.

## **ELECTRICAL CHARACTERISTICS**

$(4.5 \text{ V} \leq \text{VCC} \leq 5.5 \text{ V}, 7.0 \text{ V} \leq \text{VS} \leq 18 \text{ V}, \text{ RSTB} = \text{VCC}, \text{ CR1.D} \\ [10] = 1, -40^{\circ}\text{C} \leq \text{T}_{\text{J}} \leq 150^{\circ}\text{C}, \text{ unless otherwise specified.}) \text{ (Note 5)}$

| Characteristic                | Symbol                | Conditions          | Min      | Тур  | Max      | Unit  |

|-------------------------------|-----------------------|---------------------|----------|------|----------|-------|

| SLOPE CONTROL CALIBRAT        | ION UNIT              |                     |          |      |          |       |

| Calibration Pre-charge Time   |                       | CAL_PC[3:0] = 0x06  |          | 650  |          |       |

| 11D D:                        |                       | CAL_PC[3:0] = 0x07  |          | 750  |          |       |

| HBx Rising & Falling Slope    |                       | CAL_PC[3:0] = 0x08  |          | 850  | 1        |       |

|                               |                       | CAL_PC[3:0] = 0x09  |          | 950  | 1        |       |

|                               | 1.                    | CAL_PC[3:0] = 0x0A  |          | 1050 | (Note 7) |       |

|                               | t <sub>CAL_PCx</sub>  | CAL_PC[3:0] = 0x0B  | (Note 7) | 1150 |          | ns    |

|                               |                       | CAL_PC[3:0] = 0x0C  |          | 1250 | 1        |       |

|                               |                       | CAL_PC[3:0] = 0x0D  |          | 1350 | 1        |       |

|                               |                       | CAL_PC[3:0] = 0x0E  |          | 1450 | 1        |       |

|                               |                       | CAL_PC[3:0] = 0x0F  |          | 1550 | 1        |       |

| Calibration Delay Time        |                       | CAL_DLY[3:0] = 0x00 |          | 0.35 |          |       |

|                               |                       | CAL_DLY[3:0] = 0x01 |          | 0.55 | 1        |       |

| HBx Rising & Falling Slope    |                       | CAL_DLY[3:0] = 0x02 |          | 0.75 |          |       |

|                               |                       | CAL_DLY[3:0] = 0x03 |          | 0.95 |          |       |

|                               |                       | CAL_DLY[3:0] = 0x04 |          | 1.15 |          |       |

|                               |                       | CAL_DLY[3:0] = 0x05 |          | 1.35 |          |       |

|                               |                       | CAL_DLY[3:0] = 0x06 |          | 1.55 | 1        |       |

|                               | 1.                    | CAL_DLY[3:0] = 0x07 |          | 1.75 | 1        |       |

|                               | tCAL_DLYx             | CAL_DLY[3:0] = 0x08 | (Note 7) | 1.95 | (Note 7) | μS    |

|                               |                       | CAL_DLY[3:0] = 0x09 |          | 2.15 | 1        |       |

|                               |                       | CAL_DLY[3:0] = 0x0A |          | 2.35 | 1        |       |

|                               |                       | CAL_DLY[3:0] = 0x0B |          | 2.55 | 1        |       |

|                               |                       | CAL_DLY[3:0] = 0x0C |          | 2.75 | 1        |       |

|                               |                       | CAL_DLY[3:0] = 0x0D |          | 2.95 | 1        |       |

|                               |                       | CAL_DLY[3:0] = 0x0E |          | 3.15 | 1        |       |

|                               |                       | CAL_DLY[3:0] = 0x0F |          | 3.35 | 1        |       |

| HALF-BRIDGE DIAGNOSTICS       | 3                     |                     |          |      |          |       |

| VDS Monitor Thresholds        |                       | VDSx[2:0] = 0x00    | 263      | 300  | 337      |       |

|                               |                       | VDSx[2:0] = 0x01    | 356      | 400  | 444      |       |

| VDS = V(VS, HBx)              |                       | VDSx[2:0] = 0x02    | 445      | 500  | 555      |       |

| 120 (10,110)                  | VDC                   | VDSx[2:0] = 0x03    | 534      | 600  | 666      | m=\ / |

| - or-                         | VDS <sub>THRX</sub>   | VDSx[2:0] = 0x04    | 623      | 700  | 777      | mV    |

| VDC V/UDy CND\                |                       | VDSx[2:0] = 0x05    | 712      | 800  | 888      |       |

| VDS = V(HBx, GND)             |                       | VDSx[2:0] = 0x06    | 801      | 900  | 999      |       |

|                               |                       | VDSx[2:0] = 0x07    | 890      | 1000 | 1110     |       |

| VDS Monitor Filter Time       | t <sub>DGL_STAT</sub> |                     | 0.92     | 1.15 | 1.38     | μs    |

| VDS Monitor Propagation Delay |                       |                     | -        | 550  | 750      | ns    |

<sup>5.</sup> Min/Max values are valid for the stated temperature range unless noted otherwise. Min/Max values are guaranteed by test, design or statistical correlation

<sup>6.</sup> No production test

<sup>7.</sup> These values, measured in production via test mode, result in values that are t<sub>SYNC</sub> longer than the stated values. The specification limits shall therefore be: (t<sub>CAL\_PCx</sub> Typ + t<sub>SYNC</sub> Typ) ±20%, (t<sub>CAL\_DLYx</sub> Typ + t<sub>SYNC</sub> Typ) ±20%, and (t<sub>DLYx</sub> Typ + t<sub>SYNC</sub> Typ) ±20%.

## **ELECTRICAL CHARACTERISTICS**

$(4.5 \text{ V} \leq \text{VCC} \leq 5.5 \text{ V}, 7.0 \text{ V} \leq \text{VS} \leq 18 \text{ V}, \text{ RSTB} = \text{VCC}, \text{ CR1.D[10]} = 1, -40^{\circ}\text{C} \leq \text{T}_{J} \leq 150^{\circ}\text{C}, \text{ unless otherwise specified.)} \text{ (Note 5)}$

| ,                             | ,                   | , , ,                                                                       |           | '         | , ,       |      |

|-------------------------------|---------------------|-----------------------------------------------------------------------------|-----------|-----------|-----------|------|

| Characteristic                | Symbol              | Conditions                                                                  | Min       | Тур       | Max       | Unit |

| HALF-BRIDGE DIAGNOSTICS       |                     |                                                                             |           |           |           |      |

| VDS Overload Detection        |                     | T_DLYX[3:0] = 0x00                                                          |           | 1.05      |           |      |

| Delay Time                    |                     | T_DLYX[3:0] = 0x01                                                          |           | 1.65      | 1         |      |

| Rising or Falling Slope       |                     | T_DLYX[3:0] = 0x02                                                          |           | 2.25      | 1         |      |

|                               |                     | T_DLYX[3:0] = 0x03                                                          |           | 2.85      | 1         |      |

|                               |                     | T_DLYX[3:0] = 0x04                                                          |           | 3.45      | 1         |      |

|                               |                     | T_DLYX[3:0] = 0x05                                                          |           | 4.05      | 1         |      |

|                               |                     | T_DLYX[3:0] = 0x06                                                          |           | 4.65      | 1         |      |

|                               |                     | T_DLYX[3:0] = 0x07                                                          | <b>-</b>  | 5.25      | <b>1</b>  |      |

|                               | t <sub>DLYX</sub>   | T_DLYX[3:0] = 0x08                                                          | (Note 7)  | 5.85      | (Note 7)  | μS   |

|                               |                     | T_DLYX[3:0] = 0x09                                                          |           | 6.45      | 1         |      |

|                               |                     | T_DLYX[3:0] = 0x0A                                                          |           | 7.05      | 1         |      |

|                               |                     | T_DLYX[3:0] = 0x0B                                                          |           | 7.65      | 1         |      |

|                               |                     | T_DLYX[3:0] = 0x0C                                                          |           | 8.25      | 1         |      |

|                               |                     | T_DLYX[3:0] = 0x0D                                                          |           | 8.85      | 1         |      |

|                               |                     | T_DLYX[3:0] = 0x0E                                                          |           | 9.45      | 1         |      |

|                               |                     | T_DLYX[3:0] = 0x0F                                                          |           | 10.05     | 1         |      |

| HBx Input Resistance          | R <sub>HBX</sub>    | HBx, SH7, DL7 – Pull-down to AGND                                           | _         | 26        | -         | kΩ   |

| HBx Monitor Threshold         | VHB <sub>THR</sub>  |                                                                             | 45        | 50        | 55        | % VS |

| HBx Monitor Propagation Delay | t <sub>HBX_PD</sub> |                                                                             | _         | 1.0       | 2.0       | μs   |

| HBx Monitor Test Currents     | I <sub>TST</sub>    | CR0.HB_ENx = 0, HB1, HB3<br>source or sink, $10V \le VS \le 16V$            | ± 6.0     | ± 7.5     | ± 9.0     | mA   |

| WATCHDOG TIMER                |                     |                                                                             | •         |           |           | •    |

| Watchdog Timeout              | t <sub>WD</sub>     | CR1.D[8] = 0<br>CR1.D[8] = 1                                                | 20<br>400 | 25<br>500 | 30<br>600 | ms   |

| Core Clock Oscillator         | fCORE               |                                                                             | -         | 40        | -         | MHz  |

| THERMAL OVERLOAD (Note 6      |                     |                                                                             | •         |           | •         |      |

| Warning Threshold             | T <sub>OTW</sub>    | $T_J$ increasing, SR0.D[3] $\rightarrow$ 1                                  | 110       | 125       | 140       | °C   |

| Warning Hysteresis            | T <sub>OTW_HY</sub> | $SR0.D[3] \rightarrow 0$ (after read status if $T_J < T_{OTW-OTW\_HY}$ )    | -         | 20        | -         | °C   |

| Shutdown Threshold            | T <sub>OTS</sub>    | $T_J$ increasing, SR0.D[2] $\rightarrow$ 1, all outputs $\rightarrow$ OFF   | 150       | 170       | 190       | °C   |

| Shutdown Hysteresis           | T <sub>OTS_HY</sub> | $SR0.D[2] \rightarrow 0 \\ (after read status if T_J < T_{OTS} \_ OTS\_HY)$ | -         | 20        | -         | °C   |

| Shutdown Filter Time          | t <sub>OTDGL</sub>  |                                                                             | =         | 11.9      | =         | μs   |

|                               |                     | -                                                                           |           |           |           |      |

<sup>5.</sup> Min/Max values are valid for the stated temperature range unless noted otherwise. Min/Max values are guaranteed by test, design or statistical correlation

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

<sup>6.</sup> No production test

<sup>7.</sup> These values, measured in production via test mode, result in values that are t<sub>SYNC</sub> longer than the stated values. The specification limits shall therefore be: (t<sub>CAL\_PCx</sub> Typ + t<sub>SYNC</sub> Typ) ±20%, (t<sub>CAL\_DLYx</sub> Typ + t<sub>SYNC</sub> Typ) ±20%.

Figure 4. SPI Timing

## **DETAILED OPERATING DESCRIPTION**

#### **Power Supply**

The power supply block provides:

- all internal supply and reference voltages;

- all internal bias and reference currents;

- VCC power-on reset (POR) and VS under/over-voltage lockout signals.

The analog and power portions of the device (reference voltages/currents, charge pump, low-side gate drivers, etc.) are supplied from the VS terminal. Each of the low-side gate driver outputs (GLx) is supplied from VS via an individual buffer (source follower) with voltage limit functionality. The high-side gate driver outputs (GHx) are supplied from a regulated charge pump.

The logic core and the SPI communication interface are supplied from the VCC terminal in order to achieve a high frequency operation by use of external bypass capacitors. In case of breakdown of the external voltage regulator, the device can be protected by use of an external voltage limiter, which must limit the maximum voltage at the VCC terminal to VCC<sub>MAX</sub> (see § *MAXIMUM RATINGS*).

The outputs are disabled during device initialization at power-up via an interlock between VS and VCC and such that no control is available until after VCC > VCC<sub>PORR</sub> (see § *Electrical Characteristics: VCC Supply*). Reverse battery protection for VS and the VCC regulator is provided externally by the application (see Figure 2).

The device is initialized at power–up into a reduced power state (CR1.DRV EN = 0, see § SPI Control Set):

- the charge pump is disabled;

- all gate drive currents are disabled;

- gate pull-down structures are enabled;

- HBx diagnostic test currents are available (see § OFF-state Monitoring of Half-bridge Drivers).

The device is placed into a full power state when CR1.DRV\_EN = 1.

Multiple GND pins are used in order to avoid loss of GND due to a single-point failure, to improve ESD capability, and to improve the VDS overload protection performance of the device.

## **Charge Pump**

A regulated charge pump circuit in single–stage / complementary–phase configuration is implemented. The charge pump is sized to drive up 2 high–side drivers in PWM operation ( $f_{PWM} \le 25 \text{ kHz}$ )·

The topology utilizes 2 external pump capacitors and an external buffer capacitor (see Figure 2) to supply:

- the high-side gate driver outputs (GHx);

- an optional external reverse protection power MOSFET;

- an optional external security switch power MOSFET.

Table 1 gives suggested values for the external pump and buffer capacitors to support the charge pump DC loading while maintaining good transient response and regulation stability.

**Table 1. SUGGESTED CHARGE PUMP CAPACITORS**

| DC Load<br>(mA) | Pump Capacitors<br>C1, C2 (nF) | Buffer Capacitor<br>CCP (nF) |

|-----------------|--------------------------------|------------------------------|

| 1.0             | 100                            | 220                          |

| 7.5             | 220                            | 470                          |

| 15.0            | 470                            | 1000                         |

The device is initialized at power-up into a reduced power state and the charge pump disabled. The charge pump is controlled by SPI command via the CR1.DRV\_EN bit (see Table 7) and the charge pump is:

- disabled when CR1.DRV EN=0;

- enabled when CR1.DRV EN=1.

The optional external reverse protection and security switches are connected to the charge pump buffer capacitor through the switched charge pump (CPSW) output. The output is controlled by SPI command via the CR1.CP\_SW bit (see Table 7). The CPSW output is:

- disabled (the reverse and security MOSFETs are turned OFF) when CR1.CP SW=0;

- enabled (the reverse and security MOSFETs are turned ON) when CR1.CP SW=1.

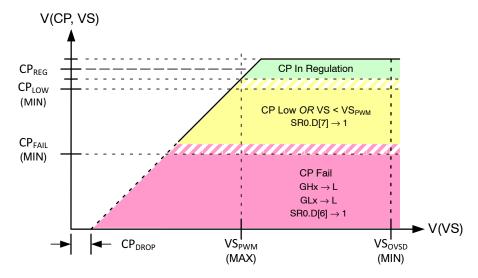

The charge pump is internally monitored to ensure safe operation of the charge pump circuit and the high-side driver outputs (see § *Protection and Diagnosis – Charge Pump Monitoring*). Due to the single stage configuration the charge pump provides the following output characteristics (see Figure 5, Figure 6, § *SPI Diagnosis Set* and § *Electrical Characteristics: Charge Pump*):

V(CP, VS) < CP<sub>FAIL</sub>

SR0.CPF → 1

the GHx and GLx outputs are shut down to prevent damage to the external power MOSFETs;

• VS < VS<sub>PWM</sub> SR0.CPL  $\rightarrow$  1

the CP output voltage follows the VS voltage (the regulation saturates) with a maximum drop voltage per the equation  $V(CP, VS) = VS - CP_{DROP}$ ;

- $CP_{FAIL} < V(CP, VS) < CP_{LOW}$  $SR0.CPL \rightarrow 1$

- VS<sub>PWM</sub> ≤ VS ≤ VS<sub>OVSDR</sub>

the charge pump delivers a regulated output voltage

V(CP, VS) = CP<sub>REG</sub> and PWM operation of the GHx outputs is allowed;

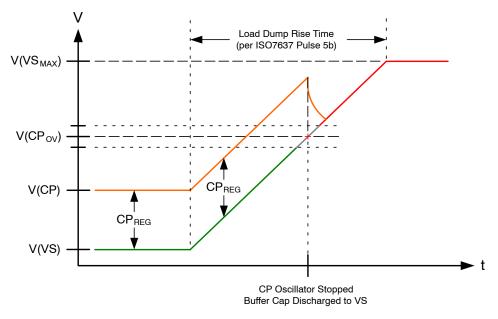

- VS<sub>OVSDF</sub> < VS < VS(CP<sub>OV</sub>)

the charge pump including the CPSW output is functional, but the GHx outputs are shut down;

- VS > VS(CP<sub>OV</sub>)

the charge pump is disabled and the charge pump buffer capacitor is discharged to VS in order to protect the device from destruction.

In the case of VS overvoltage, the charge pump automatically resumes normal operation when the VS voltage returns to below  $\mathrm{CP_{OV}}$ – $\mathrm{CP_{OV}}$ – $\mathrm{HYS}$ . In the case of VS < VS<sub>PWM</sub> or V(CP, VS) <  $\mathrm{CP_{LOW}}$  it should be considered for the microcontroller to adopt a PWM duty ratio management schema in order to minimize charge pump loading while ensuring smooth motor operation.

Figure 5. Charge Pump Characteristics

Figure 6. Charge Pump Overvoltage Behavior

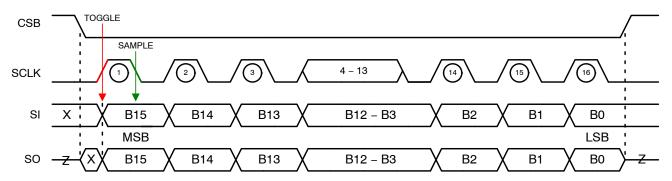

## **SPI Interface**

A full-duplex synchronous serial data transfer interface (SPI) is used to control the device and provide diagnosis during normal operation. Daisy chain capability of the interface is implemented in order to minimize circuit expenditure and communication efforts. The SPI protocol utilizes 16-bit data words (B15 = MSB). The idle state of SCLK is low and the SI data must be stable before the falling edge of SCLK ("legacy mode 1": CPOL=0, CPHA=1).

The interface consists of 4 I/O lines with 5V CMOS logic levels and termination resistors (see Figure 7, Figure 2):

- the active-low CSB enables the SPI interface;

- the SCLK pin clocks the internal shift registers of the device;

- the SI pin receives data of the input shift registers MSB first:

- the SO pin sends data of the output shift registers MSB first

The device offers the following SPI communication error checks in order to protect the application from unintended motor activation:

- protocol length error (modulo 16);

- no edges on SCLK during a CSB period;

- an undefined SPI command (not used bits must be set to logic 0);

- watchdog (WD) toggle (the internal watchdog bit (CRx.WD) must be toggled with each SPI message);

- WD timeout (the WD bit must be toggled before the internal watchdog timeout is reached).

An SI pin stuck-at condition during a CSB period is detected by a WD toggle error. A VCC under-voltage condition is directly blocking the complete SPI functionality via the VCC<sub>PORF</sub> signal.

The length of the watchdog timeout is SPI programmable (see § SPI Control Set and § Electrical Characteristics:

Watchdog Timer) in order to facilitate module boot loader programming. The timeout setting is controlled by the CR1.WD CFG bit:

- when CR1.WD\_CFG=0 (default setting) the WD timeout is t<sub>WD</sub> = 25 ms;

- when CR1.WD\_CFG=1 the WD timeout is t<sub>WD</sub> = 500 ms.

The first WD bit value sent after VCC POR or wake-up must be WD = 0 in the first frame, then WD = 1 in the next.

A correct communication is reported when bit SR0.SPIF = 0 and the device is in NORMAL MODE (NM) when bit SRx.NM = 1. The device enters FAILSAFE MODE immediately in the event of an SPI communication error (see § Operating Modes).

## Serial Data and SPI Register Structures

The input and output message formats of the implemented SPI protocol are as shown in the following tables. In the descriptions in the following sections, it is implied that the frame length is correct and that the WD bit has been properly toggled when sending and receiving SPI messages. Please also note that the SPI hardware protocol is a "frame-behind" response type, i.e. the requested data is delivered in the next frame.

#### **SPI Control Set**

The first 4 bits (D15 ... D12) serve as address bits, while 12 bits (D11 ... D0) are used as data bits. The D11 bit is the WD toggle bit: A SPI fail is detected if the bit is not toggled within the WD timeout. The D10 bit may be used as an extended address in some messages.

All Control Register (CRx) bits are initialized to logic 0 after a reset. The predefined value is off / inactive unless otherwise noted. The SPI control set (input data map) and input data structure prototype are shown in the following tables.

Note: SPI Legacy Mode 1; X=Don't Care, Z=Tri-State

Figure 7. SPI Communication Frame Format

## **Table 2. SPI INPUT DATA FORMAT**

|       | Command Input Message Format |         |                                     |     |     |                                |    |    |    |    |    |    |    |    |    |

|-------|------------------------------|---------|-------------------------------------|-----|-----|--------------------------------|----|----|----|----|----|----|----|----|----|

| MSB   | MSB LSB                      |         |                                     |     |     |                                |    |    |    |    |    |    |    |    |    |

| B15   | B14                          | B13     | B12                                 | B11 | B10 | B10 B9 B8 B7 B6 B5 B4 B3 B2 B1 |    |    |    |    |    |    |    | B1 | В0 |

| А3    | A2                           | A1      | A0                                  | WD  | D10 | D9                             | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 4-bit | REGISTI                      | ER ADDF | ADDRESS WATCH DOG 11-bit INPUT DATA |     |     |                                |    |    |    |    |    |    |    |    |    |

## Table 3. INPUT DATA STRUCTURE PROTOTYPE

|     | Input Data Prototype |     |    |    |    |    |    |    |    |    |    |    |  |

|-----|----------------------|-----|----|----|----|----|----|----|----|----|----|----|--|

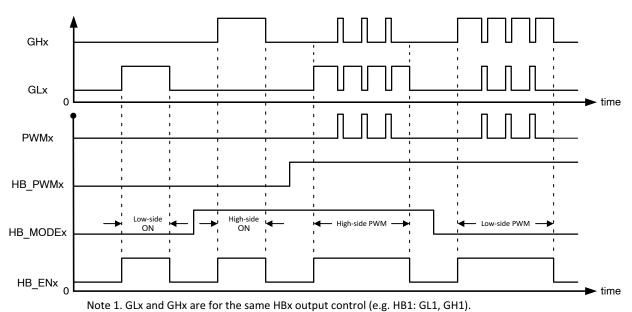

| CRx | WD                   | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |