D2982, FEBRUARY 1987 - REVISED AUGUST 1988

- Advanced LinCMOS™ Technology

- Self-Calibration Eliminates Expensive Trimming at Factory and Offset Adjustment in the Field

- 12-Bit Plus Sign Bipolar or 12-Bit Unipolar

- ±1/2 and ±1 LSB Linearity Error in Unipolar Configuration

- 10 μs Conversion Time (Mode 2) (clock = 2.6 MHz)

20 μs Conversion Time (Mode 1) (clock = 2.6 MHz)

- Compatible with All Microprocessors

- True Differential Analog Voltage Inputs

- 0 to 5 V Analog Voltage Range with Single 5-V Supply (Unipolar Configuration)

- -5 V to 5 V Analog Voltage Range with ±5-V Supplies (Bipolar Configuration)

- Low Power . . . 25 mW Maximum

- Replaces National Semiconductor ADC1205 and ADC1225 in Mode 1 Operation

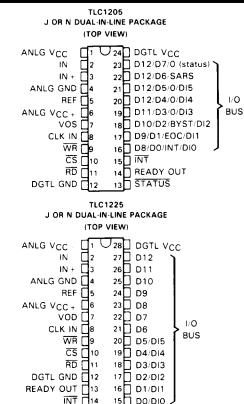

#### description

The TLC1205 and TLC1225 converters are manufactured with Texas Instruments highly efficient Advanced LinCMOS\*\* technology. Either of the TLC1205 or TLC1225 CMOS analog-to-digital converters can be operated as a unipolar or bipolar converter. A unipolar input (0 to 5 V) can be accommodated with a single 5-V supply; a bipolar input (-5 V to 5 V) requires the

addition of a 5-V negative supply. Conversion is performed via the successive-approximation method. The 24-pin TLC1205 outputs the converted data in two 8-bit bytes; the TLC1225 outputs the converted data in a parallel word and interfaces directly to a 16-bit data bus. Negative numbers are given in the two's complement data format. All digital signals are fully TTL and CMOS compatible.

These converters utilize a self-calibration technique by which seven of the internal capacitors in the capacitive ladder of the A/D conversion circuitry can be automatically or manually calibrated. If the converters are operated in Mode 1, one of the seven internal capacitors is calibrated during the first part of the conversion sequence. For example, one capacitor is calibrated during the first conversion. The next capacitor is calibrated during the second conversion. If the converters are operated in Mode 2, the internal capacitors are calibrated during a nonconversion, capacitor-calibrate cycle in which all seven of the internal capacitors are calibrated at the same time. A Mode 2 conversion requires only 10 µs (2.6 MHz clock) after the nonconversion, capacitor-calibrating cycle has been completed. The calibration or conversion cycle may be initiated at any time by issuing the proper address to the data bus. The self-calibrating techniques eliminate the need for expensive trimming of thin-film resistors at the factory and provide excellent performance at low cost.

Advanced LinCMOS is a trademark of Texas Instruments Incorporated

#### description (continued)

In Mode 1, these converters are replacements for National Semiconductor ADC1205 and ADC1225 integrated circuits. The Mode 1 conversion time for specified accuracy is 51 clock cycles. In the Mode 2 operation, these devices are no longer true replacements. However, the Mode 2 conversion time for specified accuracy is only 26 clock cycles.

The TLC1205AM, TLC1205BM, TLC1225AM, and TLC1225BM are characterized for operation over the full military temperature range of  $-55^{\circ}$ C to 125°C. The TLC1205AI, TLC1205BI, TLC1225AI, and TLC1225BI are characterized for operation from  $-40^{\circ}$ C to 85°C.

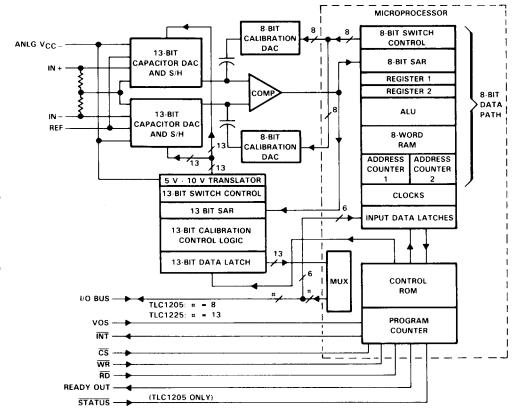

#### functional block diagram

#### operation description

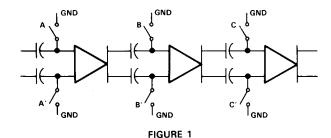

#### calibration of comparator offset

The following actions are performed to calibrate the comparator offset:

1. The IN+ and IN- inputs are internally shorted together in order that the comparator input is zero. A course comparator offset calibration is performed by storing the offset voltages of the interconnecting comparator stages on the coupling capacitors that connect the interconnecting stages. Refer to Figure 1. The storage of offset voltages is accomplished by closing all switches and then opening switches A and A', then switches B and B', and then C and C'. This process continues until all interconnecting stages of the comparator are calibrated. After this action, some of the comparator offset still remains uncalibrated.

An A/D conversion is done on the remaining offset with the 8-bit calibration DACs and 8-bit SAR and the result is stored in the RAM.

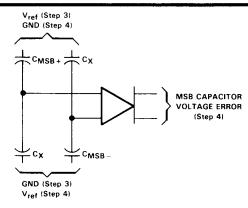

#### capacitor calibration of the ADC's capacitive ladder

The following actions are performed to calibrate capacitors in the 13-bit DACs that comprise the ADC's capacitive ladder:

- 1. The IN+ and IN- inputs are internally disconnected from the 13-bit capacitive DACs.

- 2. The most significant bit (MSB) capacitor is tied to REF, while the rest of the ladder capacitors are tied to GND. The A/D conversion result for the remaining comparator offset, obtained in Step 2 above, is retrieved from the RAM and is input to the 8-bit DACs.

- Step 1 of the Calibration of Comparator Offset sequence is performed. The 8-bit DAC input is returned to zero and the remaining comparator offset is then subtracted. Thus, the comparator offset is completely corrected.

- 4. Now the MSB capacitor is tied to GND, while the rest of the ladder capacitors, C<sub>X</sub>, are tied to REF. An MSB capacitor voltage error (see Figure 2) on the comparator output will occur if the MSB capacitor does not equal the sum of the other capacitors in the capacitive ladder. This error voltage is converted to an 8-bit word from which a capacitor error is computed and stored in the RAM.

- 5. The capacitor voltage error for the next most significant capacitor is calibrated by keeping the MSB capacitor grounded and then performing the above Steps 1-4 while using the next most significant capacitor in lieu of the MSB capacitor. The seven most significant capacitors can be calibrated in this manner.

FIGURE 2

#### analog-to-digital conversion

The following steps are performed in the analog-to-digital conversion process:

- Step 1 of the Calibration of Comparator Offset Sequence is performed. The A/D conversion result for the remaining comparator offset, which was obtained in Step 2 of the Calibration of Comparator Offset, is retrieved from the RAM and is input to the 8-bit DACs. Thus the comparator offset is completely corrected.

- 2. IN+ and IN- are sampled onto the 13-bit capacitive ladders.

- 3. The 13-bit analog-to-digital conversion is performed. As the successive-approximation conversion proceeds successively through the seven most significant capacitors, the error for each of these capacitors is recovered from the RAM and accumulated in a register. This register controls the 8-bit DACs so the total accumulated error for these capacitors is subtracted out during the conversion process.

| bsolute maximum ratings over operating free-air temperature range (unless otherwise noted) |

|--------------------------------------------------------------------------------------------|

| Supply voltage (ANLG VCC+ and DGTL VCC) (see Note 1)                                       |

| Supply voltage, ANLG VCC                                                                   |

| Control and Clock input voltage range                                                      |

| Analog input (IN+, IN-) voltage range,                                                     |

| $V_{l+}$ and $V_{l-}$                                                                      |

| Reference voltage range, V <sub>ref</sub>                                                  |

| Mode select voltage range, Vos                                                             |

| Output voltage range                                                                       |

| Input current (per pin)                                                                    |

| Input current (per package)                                                                |

| Operating free-air temperature range:                                                      |

| TLC1205AM, TLC1205BM, TLC1225AM, TL1225BM                                                  |

| TLC1205AI, TLC1205BI, TLC1225AI, TLC1225BI                                                 |

| Storage temperature range65°C to 150°C                                                     |

| Lead temperature 1,6 mm (1/16 inch) from the case for 60 seconds: J package 300°C          |

| Lead temperature 1,6 mm (1/16 inch) from the case for 10 seconds: N package                |

NOTE 1: All analog voltages are referred to ANLG GND and all digital voltages are referred to DGTL GND.

## recommended operating conditions

|                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MIN                         | MAX                          | UNIT |  |

|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------------------|------|--|

|                                                                                                                     | ANLG V <sub>CC+</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4.5                         | 6                            |      |  |

| Supply voltage                                                                                                      | ANLG V <sub>CC</sub> -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -5.5                        | ANLG GND                     | V    |  |

|                                                                                                                     | DGTL V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.5                         | 6                            |      |  |

| High-level input voltage, $V_{IH}$ , all digital input ( $V_{CC} = 4.75 \text{ V to } 5.25 \text{ V}$ )             | s except CLK IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2                           |                              | ٧    |  |

| Low-level input voltage, $V_{1L}$ , all digital inputs ( $V_{CC} = 4.75 \text{ V to } 5.25 \text{ V}$ )             | except CLK IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                             | 0.8                          | ٧    |  |

| Analog input valtage V V                                                                                            | Bipolar range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ANLG V <sub>CC</sub> - 0.05 | ANLG V <sub>CC+</sub> + 0.05 | V    |  |

| Analog input voltage, V <sub>I+</sub> , V <sub>I-</sub>                                                             | Unipolar range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ANLG GND - 0.05             | ANLG V <sub>CC+</sub> + 0.05 | ľ    |  |

| Clock input frequency, fclock                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.3                         | 2.6                          | MHz  |  |

| Clock duty cycle                                                                                                    | CONTRACTOR OF CO | 40%                         | 60%                          |      |  |

| Pulse duration, $\overline{\text{CS}}$ and $\overline{\text{WR}}$ both low, $t_{\text{W}}$ ( $\overline{\text{CS}}$ | ·WR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 50                          |                              | ns   |  |

| Setup time before WR† or CS†, t <sub>SU</sub>                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                             | 50                           | ns   |  |

| Hold time after WR↑ or CS↑, th                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                             | 50                           | ns   |  |

|                                                                                                                     | TLC1205AM, TLC1225AM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                             | 105                          |      |  |

| Constitute from air homes and the To                                                                                | TLC1205BM, TLC1225BM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -55                         | 125                          | °C   |  |

| Operating free-air temperature, TA                                                                                  | TLC1205AI, TLC1225AI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -40                         | 85                           |      |  |

|                                                                                                                     | TLC1205BI, TLC1225BI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -40                         | 85                           |      |  |

electrical characteristics over recommended operating free-air temperature range, ANLG  $VCC + DGTL\ VCC = V_{ref} = 5\ V$ , ANLG  $VCC - = -5\ V$  (for bipolar input range), ANLG  $VCC - = ANLG\ GND$  (for unipolar input range) (unless otherwise noted) (see Note 1)

|                  | PARAMETER                                  | TEST CON                                   | MIN                       | MAX | UNIT |      |

|------------------|--------------------------------------------|--------------------------------------------|---------------------------|-----|------|------|

| Vон              | High-level output voltage                  | DGTL V <sub>CC</sub> = 4.75 V              | $I_{O} = -1.8 \text{ mA}$ | 2.4 |      | ٧    |

|                  |                                            |                                            | $t_0 = -50  \mu A$        | 4.5 |      |      |

| VOL              | Low-level output voltage                   | DGTL $V_{CC} = 4.75 V$ ,                   | $I_O = 8 \text{ mA}$      |     | 0.4  | ·    |

| V <sub>T +</sub> | Clock positive-going threshold voltage     |                                            |                           | 2.7 | 3.5  | V    |

| V <sub>T</sub> _ | Clock negative-going threshold voltage     |                                            |                           | 1.4 | 2.1  | V    |

|                  |                                            | V <sub>T+</sub> min - V <sub>T-</sub> - ma | x                         | 0.6 | 0.6  | V    |

| V <sub>hys</sub> | Crock input hysteresis                     | V <sub>T+</sub> max - V <sub>T-</sub> min  |                           | 2.1 | *    |      |

| ref              | Input resistance, REF terminal             |                                            |                           | 1   | 10   | MΩ   |

| ΉΗ               | High-level input current                   | V <sub>I</sub> = 5 V                       |                           |     | 1    | μА   |

| hr               | Low-level input current                    | V <sub>1</sub> = 0                         |                           |     | - 1  | μΑ   |

| 1                | High-impedance-state                       | VO = 0                                     |                           |     | -3   | μΑ   |

| loz              | output leakage current                     | V <sub>O</sub> = 5 V                       |                           |     | 3    | μΛ   |

|                  | Output current                             | V <sub>O</sub> = 0<br>V <sub>O</sub> = 5 V |                           |     | -6   | mA   |

| 10               | Output current                             |                                            |                           |     | 8    | 1116 |

| DGTL ICC         | Supply current from DGTL VCC               | f <sub>Clk</sub> = 2.6 MHz,                | CS high                   | Ī   | 3    | mA   |

| ANLG ICC+        | Supply current from ANLG VCC+              | f <sub>Clk</sub> = 2.6 MHz,                | CS high                   |     | 3    | mA   |

| ANLG ICC-        | Supply current from ANLG V <sub>CC</sub> - | f <sub>Clk</sub> = 2.6 MHz,                | CS high                   |     | -3   | mA   |

|                  |                                            |                                            |                           |     |      |      |

NOTE 1: Bipolar input range is defined as:  $V_{j+} = -5.05 \text{ V}$  to +5.05 V,  $V_{j-} = -5.05 \text{ V}$  to +5.05 V, and  $V_{j+} = V_{j-} | \le 5.05 \text{ V}$ . The unipolar input voltage range is defined as:  $V_{j+} = -0.05 \text{ V}$  to 5.05 V,  $V_{j-} = -0.05 \text{ V}$  to 5.05 V, and  $V_{j+} = V_{j--} \le 5.05 \text{ V}$ .

operating characteristics over recommended operating free-air temperature range, ANLG  $V_{CC} + DGTL \ V_{CC} = V_{ref} = 5 \ V$ , ANLG  $V_{CC} - E - 5 \ V$  (for bipolar input range), ANLG  $V_{CC} - E - E \ V_{CC} - E \ V_{CC} - E - E \ V_{CC} - E \ V_{CC$

| PARAMETER        |                                                    |                       | TEST C                             | MIN MAX                                | UNIT  |        |

|------------------|----------------------------------------------------|-----------------------|------------------------------------|----------------------------------------|-------|--------|

|                  | Best-straight-line<br>linearity error (see Note 2) |                       | Unipolar input range               | TLC1205A, TLC1225A                     | ±1    |        |

|                  |                                                    |                       | Ompolar input range                | TLC1205B, TLC1225B                     | ±0.5  |        |

|                  |                                                    |                       | Dinelar input range                | Bipolar input range TLC1205A, TLC1225A |       | LSB    |

|                  |                                                    |                       | bipolal input range                | TLC1205B, TLC1225B                     | ±1.5  | 1      |

|                  | Zero error                                         |                       |                                    | ±0.5                                   | LSB   |        |

| -                | Adjusted positive ar                               | nd negative           | Unicolar input soons               |                                        |       |        |

|                  | full-scale error (see                              | Note 3)               | Unipolar input range               |                                        | ±1    | LSB    |

|                  | Adjusted positive ar                               | nd negative           | Bipolar input range                |                                        |       |        |

|                  | full-scale error (see                              | Note 4)               | Dipolar Imput range                |                                        | ±1    | LSB    |

|                  | Temperature coeffic                                | ient of gain          |                                    |                                        | 15    | ppm/°C |

|                  | Temperature coeffic                                | ient of offset point  |                                    |                                        | 1.5   | ppm/°C |

|                  |                                                    | Zero error            | ANLG V <sub>CC+</sub> = 5 V ± 5%,  |                                        | ±0.75 | i      |

| ksvs             | Supply voltage                                     | Positive and negative |                                    |                                        |       |        |

| ~5V5             | sensitivity                                        | full-scale error      | ANLG VCC = -5 V                    | ±0.75                                  | LSB   |        |

|                  |                                                    | Linearity error       | DGTL V <sub>CC</sub> = 5 V ± 5     | <b>%</b> o                             | ±0.25 |        |

| t <sub>C</sub>   | Conversion time                                    | Mode 1                |                                    |                                        | 62    | clock  |

| 'C               | (1/f <sub>Clk</sub> )                              | Mode 2                |                                    |                                        | 24    | cycles |

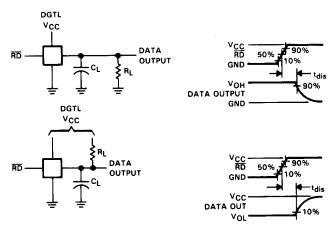

| ta               | Access time (delay from falling edge of            |                       | C <sub>1</sub> = 100 pF            |                                        |       |        |

| 'a               | CS RD to data outp                                 | ut)                   | C[ = 100 pr                        |                                        | 110   | ns     |

| t <sub>dis</sub> | Disable time, output (delay from rising            |                       | $R_L = 10 \text{ k}\Omega$ ,       | C <sub>L</sub> = 10 pF                 | 60    |        |

| aus              | edge of RD to high-                                | impedance state       | $R_L = 2 k\Omega$ , $C_L = 100 pF$ |                                        | 60    | ns     |

| td(READY)        | RD or WR to READ                                   | OUT delay             |                                    |                                        | 140   | ns     |

| td(INT)          | RD or WR to reset of                               | f INT delay           |                                    |                                        | 400   | ns     |

- NOTES: 2. Best-straight-linearity error is the difference between the actual analog value at the transition between any two adjacent steps and its ideal value, after offsset error and gain error have been adjusted to minimize the magnitude of the extreme values of this difference.

- 3. See section Positive and Negative Full-Scale Adjustment, Unipolar Inputs.

- 4. See section Positive and Negative Full-Scale Adjustment, Bipolar Inputs.

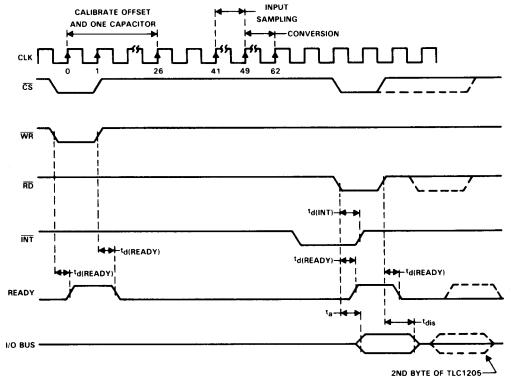

NOTE: The dashed lines in Figures 3.5 indicate additional control signalling, which is required for the TLC1205. This additional signalling is required because of the TLC1205's two-byte operation.

FIGURE 3. MODE 1 TIMING DIAGRAM

#### PARAMETER MEASUREMENT INFORMATION

FIGURE 6. LOAD CIRCUITS AND WAVEFORMS

#### PRINCIPLES OF OPERATION

The following information is categorized into Mode 1 and Mode 2 groupings to allow the designer to concentrate on a particular mode of interest.

### power-up calibration sequence

#### Mode 1

When the chip is powered-up, the internal capacitors are automatically calibrated as part of the power-up sequence. This initial calibration sequence requires 105 clock cycles. The chip will not perform an A/D conversion during this calibration sequence.

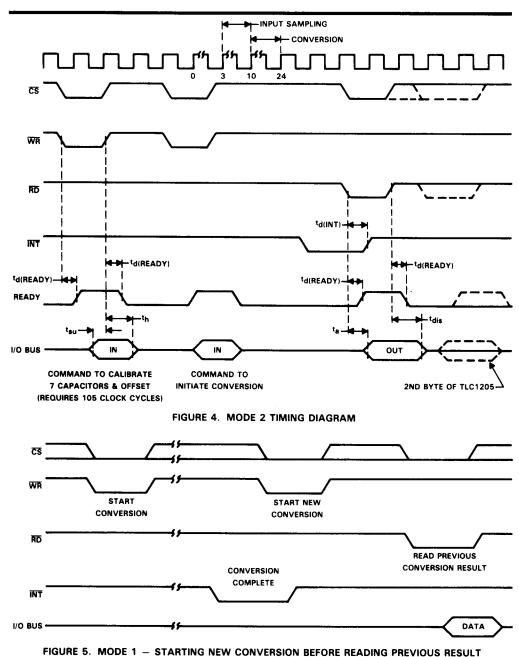

#### Mode 2

Power-Up calibration is not automatic and calibration is initiated by writing control words to the six least significant bits of the data bus. If addressed or initiated, conversion can begin after the first clock cycle. However, full A/D conversion accuracy is not established until after internal capacitor calibration.

## conversion start sequence

#### Mode 1

The conversion sequence is initiated when  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  are both low.

#### Mode 2

The writing of the conversion command word to the six least significant bits of the data bus, when either  $\overline{\text{CS}}$  or  $\overline{\text{WR}}$  goes high, initiates the conversion sequence.

#### analog sampling sequence

#### Mode 1

Sampling of the input signal occurs during clock cycles 41 thru 49 of the conversion sequence.

#### Mode 2

Sampling of the input signal occurs during clock cycles 3 thru 10 of the conversion sequence.

#### completed A/D conversion

When INT goes low, conversion is complete and the A/D result can be read. A new conversion can begin immediately.

#### Mode 1

The A/D conversion is complete at the end of clock cycle 62 of the conversion sequence.

#### Mode 2

The A/D conversion is complete at the end of clock cycle 24 of the conversion sequence.

## aborting a conversion in process and beginning a new conversion

#### Mode 1 and Mode 2

If a conversion is initiated while a conversion sequence is in process, the ongoing conversion will be aborted and a new conversion sequence will begin.

#### Mode 1

If the new conversion is started before the Analog Sampling begins (see Analog Sampling Sequence section and the Mode 1 Timing Diagram), the particular internal capacitor that was being calibrated during the aborted conversion sequence will be calibrated during the new conversion sequence. Otherwise, the next internal capacitor will be calibrated during the new conversion sequence.

#### reading the conversion result

#### TLC1205

Upon activating the required control signals to read the conversion result or status information, the appropriate pins are brought out of a high-impedance state and drive the data bus with the proper information. These pins are D12/D7/0 through D8/D0/INT/DI0.

If  $\overline{STATUS}$ ,  $\overline{CS}$ , and  $\overline{RD}$  are all low, status information can be read. The format of the conversion result and status information and the respective pins for output are presented in Table 1.

#### TABLE 1

|        |        |    |    | Ţ    |      |      | I/C  | BUS  |       |      |             |

|--------|--------|----|----|------|------|------|------|------|-------|------|-------------|

|        |        |    |    | D12/ | D12/ | D12/ | D12/ | D11/ | D10/  | D9/  | D8/         |

| BYTES  | STATUS | ĈŚ | RD | D7/  | D6/  | D5/  | D4/  | D3/  | D2/   | D1/  | <b>D0</b> / |

|        |        |    |    | 0    | SARS | 0/   | 0/   | 0/   | BYST/ | EOC/ | INT/        |

|        |        |    | 1  |      |      | DI5  | DI4  | DI3  | DI2   | DI1  | DIO         |

| MSB    | Н      | L  | L  | D12  | D12  | D12  | D12  | D11  | D10   | D9   | D8          |

| LSB    | н      | L  | ↑↓ | D7   | D6   | D5   | D4   | D3   | D2    | D1   | D0          |

| STATUS | L      | L  | L  | L    | SARS | L    | L    | L    | BYST  | EOC  | INT         |

The status information is described in Table 2.

#### **TABLE 2**

| STATUS<br>BIT | BIT DESCRIPTION                                                                                                                                                                                                                                                                                                                    | TO CLEAR BIT                                                                    |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| L             | The output has no meaning and is low.                                                                                                                                                                                                                                                                                              |                                                                                 |

| SARS          | A high indicates that conversion is in progress.                                                                                                                                                                                                                                                                                   |                                                                                 |

| BYST          | A low indicates that the next conversion result read will be the most significant conversion byte. A high indicates that the next conversion result read will be the least significant conversion byte. The BYST bit is toggled by reading the conversion result bytes. This bit can be cleared with a "status write" instruction. | By a "status write" or toggled by reading a conversion data byte.               |

| EOC           | A high indicates that conversion is complete and the conversion data has been transferred to the output latch.                                                                                                                                                                                                                     |                                                                                 |

| INT           | A high indicates that conversion is complete and the conversion data has been transferred to the output latch and is ready to read.                                                                                                                                                                                                | By reading a conversion data byte, reading the status byte, or a "status write" |

With  $\overline{STATUS}$  high, when  $\overline{CS}$  and  $\overline{RD}$  both go low, the most significant byte (MSB) of the conversion result can be read. Then by taking  $\overline{RD}$  high and back low, the least significant byte (LSB) of the conversion result can be read. Subsequently taking  $\overline{RD}$  high and low causes the alternate reading of the MSB and LSB of the conversion result.

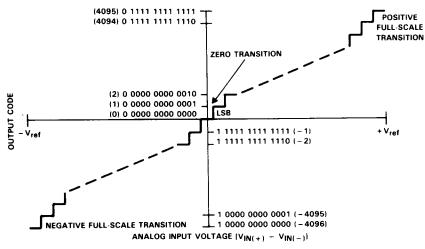

The format of the output is extended sign with 2's complement, right justified data. For both unipolar and bipolar cases, the sign bit D12 is low if  $V_{I+}-V_{I-}$  is positive and high if  $V_{I+}-V_{I-}$  is negative. The format of the conversion result and the respective output pins are presented in Table 2. The format of the conversion result and the respective pins for output are presented in Table 1.

#### TLC1225

When both  $\overline{CS}$  and  $\overline{RD}$  go low, all 13 bits of conversion data are output to the I/O bus. The format of the output is extended sign with 2's complement, right justified data. Unlike the TLC1205, the TLC1225 does not have internal status information or a  $\overline{STATUS}$  pin. For both unipolar and bipolar cases, the sign bit D12 is low if  $V_{I+} - V_{I-}$  is positive and high if  $V_{I+} - V_{I-}$  is negative.

#### general

#### reset INT

When reading the conversion data, the falling edge of the first low-going combination of  $\overline{CS}$  and  $\overline{RD}$  will reset  $\overline{INT}$ . The falling edge of the low-going combination of  $\overline{CS}$  and  $\overline{WR}$  will also reset  $\overline{INT}$ .

#### ready out

For high-speed microprocessors, READY OUT allows the TLC1205 and the TLC1225 to insert a wait state in the microprocessor's read cycle.

#### status write (TLC1205)

A status write resets the internal logic and status bits and aborts any conversion in process. A status write occurs when  $\overline{\text{CS}}$ ,  $\overline{\text{WR}}$ , and  $\overline{\text{STATUS}}$  are taken low.

#### reference voltage (Vref)

This voltage defines the range for  $|V_{1+} - V_{1-}|$ . When  $|V_{1+} - V_{1-}|$  equals  $V_{ref}$ , the highest conversion data value results. When  $|V_{1+} - V_{1-}|$  equals 0, the conversion data value is zero. Thus, for a given input, the conversion data changes ratiometrically with changes in  $V_{ref}$ .

#### Vos

This pin is a digital input and is used to select Mode 1 or Mode 2 operation. A logic low selects Mode 1; a logic high selects Mode 2.

In Mode 1, the ICs are true replacements for National Semiconductor's ADC1205 and ADC1225. The ADC1205 and ADC1225 use the VOS pin to adjust zero error. Since the zero error adjustment voltage is below the TLC1205's and TLC1225's maximum acceptable level for a logic low signal, the TLC1205 and TLC1225 ICs are true replacements. Even in Mode 1, the TLC1205's and TLC1225's converted data can be read earlier than the ADC1205's and ADC1225's.

#### calibration and conversion considerations

#### Mode 1

Calibration of the seven internal capacitors is an integral part of the A/D conversion. One of the seven internal capacitors is calibrated during the first part of the conversion sequence. For example, one of the capacitors is calibrated during the first conversion. The next capacitor is calibrated during the second conversion. After seven conversions, the pattern for calibrating the internal capacitors repeats. A conversion sequence requires 62 clock cycles.

A conversion is initiated by the low-going combination of  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$ . The conversion sequence is illustrated in the Mode 1 timing diagram.

#### Mode 2

Calibration of the internal capacitor and A/D conversion are two separate actions. Each action is independently initiated. Mode 2 conversion is much faster than Mode 1, since Mode 2 conversion is not accompanied by the calibration of internal capacitors. In Mode 2, a calibration command that calibrates all seven internal capacitors is normally issued first. A conversion command then initiates the A/D conversion without calibrating the internal capacitors. Subsequent conversions can be performed by issuing additional conversion commands. The calibration and conversion commands are totally independent from one another and can be initiated in any order. Calibration and conversion commands require 105 and 24 clock cycles, respectively.

The calibrate and conversion commands are initiated by writing control words on the six least significant bits of the data bus. These control words are written into the IC when either  $\overline{\text{CS}}$  or  $\overline{\text{WR}}$  goes high. The initiation of these commands is illustrated in the Mode 2 Timing Diagram. The bit patterns for the commands are shown in Table 3.

TABLE 3. MODE 2 CONVERSION COMMANDS

|                        |          | T   |     | REQUIRED NUMBER |     |     |     |                 |

|------------------------|----------|-----|-----|-----------------|-----|-----|-----|-----------------|

| COMMAND                | ČS + WR  | DI5 | D14 | DI3             | DI2 | DI1 | DIO | OF CLOCK CYCLES |

| Conversion             | <u>†</u> | Н   | L   | Х               | X   | X   | L   | 26              |

| Calibrate <sup>†</sup> | <b>†</b> | L   | X   | L               | L   | L   | L   | 105             |

<sup>†</sup>Calibration is lost when clock is stopped.

#### analog inputs

#### differential inputs provide common mode rejection

The differential inputs reduce common-mode noise. Common-mode noise is noise common to both IN+ and IN- inputs, such as 60-Hz noise. There is no time interval between the sampling of the IN+ and IN- so these inputs are truly differential. Thus, no conversion errors result from a time interval between the sampling of the IN+ and IN- inputs.

#### input bypass capacitors

Input bypass capacitors may be used for noise filtering. However, the charge on these bypass capacitors will be depleted during the input sampling sequence when the internal sampling capacitors are charged. Note that the charging of the bypass capacitors through the differential source resistances must keep pace with the charge depletion of the bypass capacitors during the input sampling sequence. Higher source resistances reduce the amount of charging current for the bypass capacitors. Also, note that fast, successive conversion will have the greatest charge depletion effect on the bypass capacitors. Therefore, the above phenomenon becomes more significant as source resistances and the conversion rate (i.e., higher clock frequency and conversion initiation rate) increase.

In addition, if the above phenomenon prevents the bypass capacitors from fully charging between conversions, voltage drops across the source resistances will result due to the ongoing bypass capacitor charging currents. The voltage drops will cause a conversion error. Also, the voltage drops increase with higher  $|V|_+ - V|_-$  values, higher source resistances, and lower charge on the bypass capacitors (i.e., faster conversion rate).

For low-source-resistance applications ( $R_{SOURCE} < 100~\Omega$ ), a 0.001- $\mu$ F bypass capacitor at the inputs will prevent pickup due to the series lead inductance of a long wire. A 100-ohm resistor can be placed between the capacitor and the output of an operational amplifier to isolate the capacitor from the operational amplifier.

#### input leads

The input leads should be kept as short as possible, since the coupling of noise and digital clock signals to the inputs can cause errors.

## power supply considerations

Noise spikes on the VCC lines can cause conversion error. Low-inductance tantalum capacitors ( $> 1 \mu F$ ) with short leads should be used to bypass ANLG VCC and DGTL VCC. A separate regulator for the TLC1205 or TLC1225 and other analog circuitry will greatly reduce digital noise on the supply line.

## positive and negative full-scale adjustment

## unipolar inputs

Apply a differential input voltage that is 0.5 LSB below the desired analog full-scale voltage (VFS) and adjust the magnitude of the REF input so that the output code is just changing from 0 1111 1111 1110 to 0 1111 1111 1111. If this transition is desired for a different input voltage, the reference voltage can be adjusted accordingly.

#### bipolar inputs

First, follow the procedure for the Unipolar case.

Second, apply a differential input voltage so that the digital output code is just changing from 1 0000 0000 0001 to 1 0000 0000 0000. Call this actual differential voltage Vx. The ideal differential voltage for this transition is:

$$-V_{FS} + \frac{V_{FS}}{8192}$$

(1)

The difference between the actual and ideal differential voltages is:

Delta =

$$V_X - (-V_{FS} + \frac{V_{FS}}{8192})$$

(2)

Then apply a differential input voltage of:

$$V_X - \frac{Delta}{2}$$

(3)

and adjust  $V_{ref}$  so the digital output code is just changing from 1 0000 0000 0001 to 1 0000 0000 0000. This procedure produces positive and negative full-scale transitions with symmetrical minimum error.

#### TYPICAL APPLICATIONS

FIGURE 7. TRANSFER CHARACTERISTIC

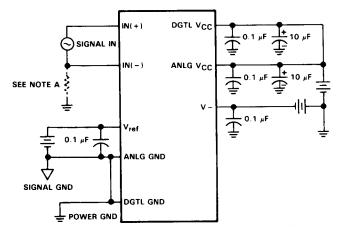

NOTE: A. The analog input must have some current return path to ANALOG GND.

B. Bypass capacitor leads must be as short as possible.

FIGURE 8. ANALOG CONSIDERATIONS

## **TYPICAL APPLICATIONS (Continued)**

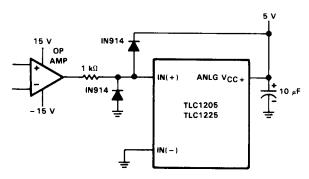

FIGURE 9. INPUT PROTECTION

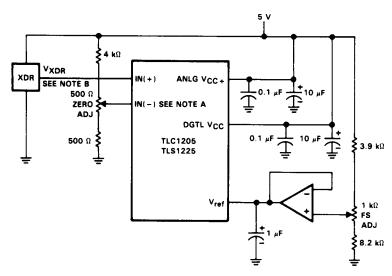

NOTE: A.  $V_{I-} = 0.15 \times ANLG \ V_{CC+}$ . B. 15% of ANALOG  $V_{CC} \le V_{XDR} \le 85\%$  of ANALOG  $V_{CC}$ .

FIGURE 10. OPERATING WITH RATIOMETRIC TRANSDUCERS