## **TC1130**

32-Bit Single-Chip Microcontroller

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All re-creations are done with the approval of the Original Component Manufacturer (OCM).

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

## **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-35835

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OCM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

Microcontrollers

Never stop thinking.

#### **Edition 2008-12**

Published by Infineon Technologies AG, St.-Martin-Strasse 53, 81669 München, Germany

© Infineon Technologies AG 2008.

All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as a guarantee of characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

## TC1130

32-Bit Single-Chip Microcontroller

## Microcontrollers

| TC1130 Da             | ta Sheet |                                     |      |

|-----------------------|----------|-------------------------------------|------|

| Revision H            | listory: | 2008-12                             | V1.1 |

| Previous V            | ersion:  | V1.0, 2005-02                       |      |

| Page                  | Subjects | (major changes since last revision) |      |

| 77, 78, 79<br>,81, 82 | Added "O | perating Conditons apply" statement |      |

Controller Area Network (CAN): License of Robert Bosch GmbH

#### **We Listen to Your Comments**

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

| Table of                                                                                                                                                                                                                                                            | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Page                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                                                                                                                                                                                                                                   | Summary of Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                            |

| 2<br>2.1<br>2.2<br>2.3<br>2.4                                                                                                                                                                                                                                       | General Device Information  Block Diagram  Logic Symbol  Pin Configuration  Pin Definitions and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3<br>4<br>5                                                                                                                                                                                  |

| 3<br>3.1<br>3.2<br>3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11<br>3.12<br>3.13<br>3.14<br>3.15<br>3.16<br>3.17<br>3.18<br>3.19<br>3.20<br>3.21<br>3.22<br>3.23<br>3.24<br>3.25<br>3.27<br>4 | Functional Description On-Chip Memories Address Map Memory Protection System Protection for Direct translation Protection for PTE based translation Memory Checker On-Chip Bus System Local Memory Bus (LMB) Flexible Peripheral Interconnect Bus (FPI) LFI LMB External Bus Unit Direct Memory Access (DMA) Interrupt System Parallel Ports Asynchronous/Synchronous Serial Interface (ASC) High-Speed Synchronous Serial Interface (SSC) Inter IC Serial Interface (IIC) Universal Serial Bus Interface (USB) MultiCAN Micro Link Serial Bus Interface (MLI) General Purpose Timer Unit (GPTU) Capture/Compare Unit 6 (CCU6) Ethernet Controller System Timer Watchdog Timer System Control Unit Boot Options Power Management System On-Chip Debug Support Clock Generation Unit Power Sequencing Identification Register Values  Electrical Parameters | . 20<br>. 21<br>. 27<br>. 28<br>. 29<br>. 29<br>. 30<br>. 31<br>. 35<br>. 37<br>. 38<br>. 41<br>. 45<br>. 50<br>. 52<br>. 54<br>. 50<br>. 62<br>. 63<br>. 64<br>. 65<br>. 70<br>. 71<br>. 72 |

| Table of | Contents                                     | Page  |

|----------|----------------------------------------------|-------|

| 4.1      | General Parameters                           | 74    |

| 4.1.1    | Parameter Interpretation                     | 74    |

| 4.1.2    | Absolute Maximum Rating                      | 75    |

| 4.1.3    | Operating Condition                          | 76    |

| 4.2      | DC Parameters                                | 77    |

| 4.2.1    | Input/Output Characteristics                 | 77    |

| 4.2.2    | Oscillator Characteristics                   | 78    |

| 4.2.3    | USB Characteristics                          | 79    |

| 4.2.3.1  | DC Electrical Characteristics                | 79    |

| 4.2.3.2  | Full Speed Electrical Characteristics        | 79    |

| 4.2.4    | IIC Characteristics                          | 81    |

| 4.2.5    | Power Supply Current                         | 82    |

| 4.3      | AC Parameters                                | 83    |

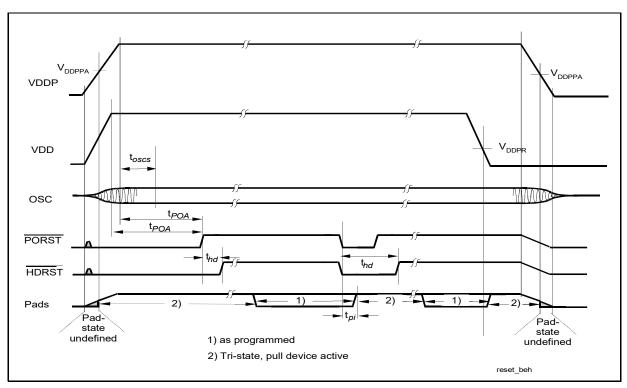

| 4.3.1    | Power, Pad and Reset Timing                  | 83    |

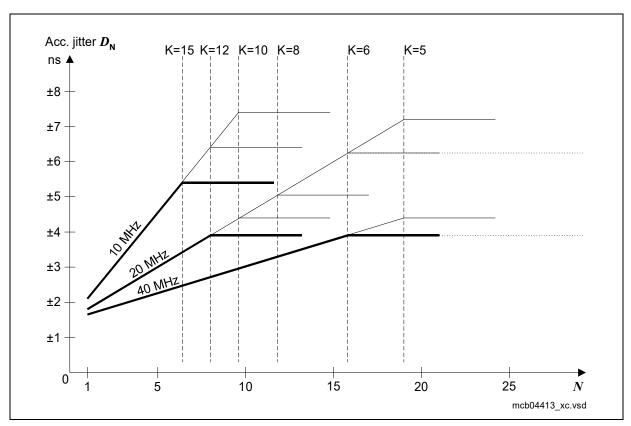

| 4.3.2    | PLL Parameters                               | 85    |

| 4.3.3    | AC Characteristics                           | 87    |

| 4.3.4    | Input Clock Timing                           | 88    |

| 4.3.5    | Port Timing                                  | 89    |

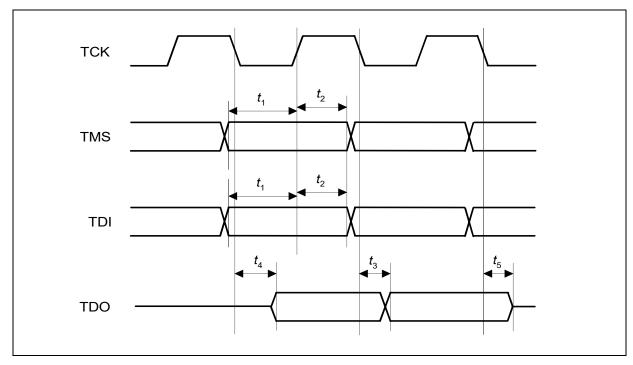

| 4.3.6    | Timing for JTAG Signals                      |       |

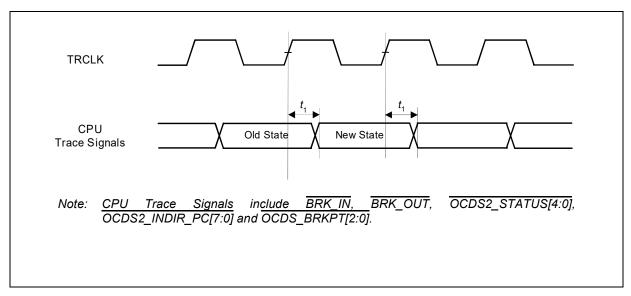

| 4.3.7    | Timing for OCDS Trace and Breakpoint Signals |       |

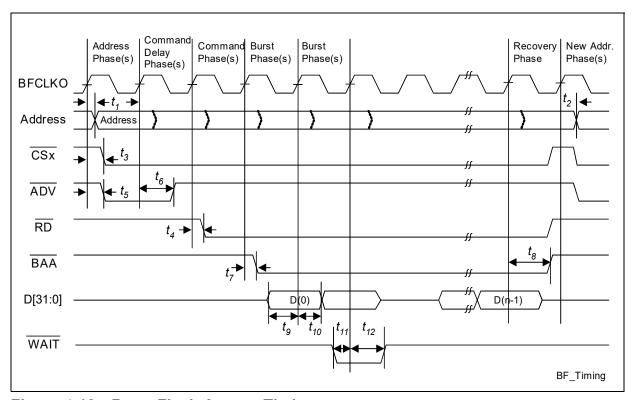

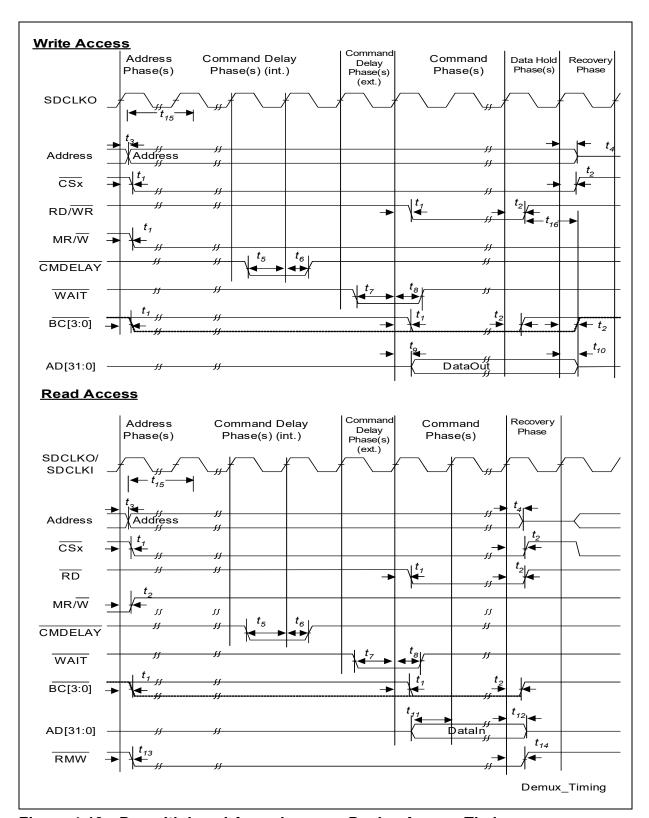

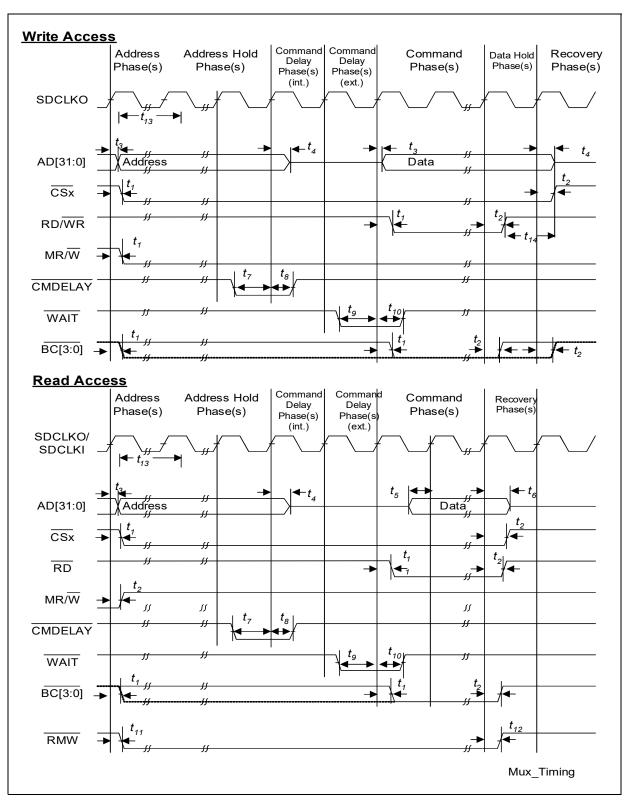

| 4.3.8    | EBU Timings                                  | 93    |

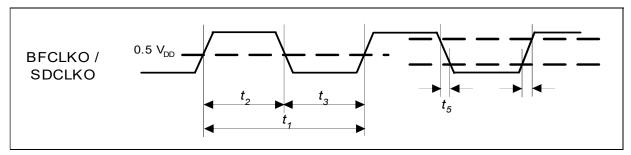

| 4.3.8.1  | SDCLKO Output Clock Timing                   | 93    |

| 4.3.8.2  | BFCLKO Output Clock Timing                   |       |

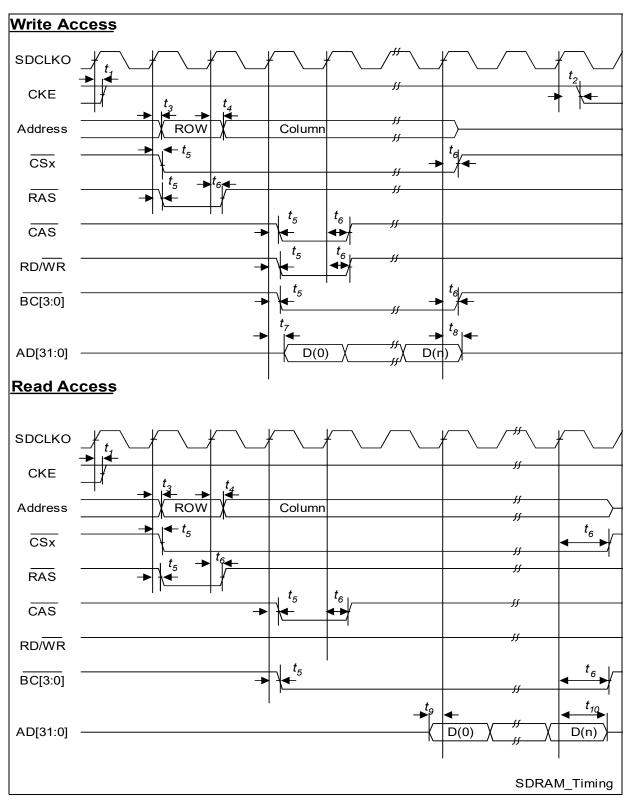

| 4.3.8.3  | Timing for SDRAM Access Signals              |       |

| 4.3.8.4  | Timing for Burst Flash Access Signals        |       |

| 4.3.8.5  | Timing for Demultiplexed Access Signals      |       |

| 4.3.8.6  | Timing for Multiplexed Access Signals        |       |

| 4.3.9    | Peripheral Timings                           |       |

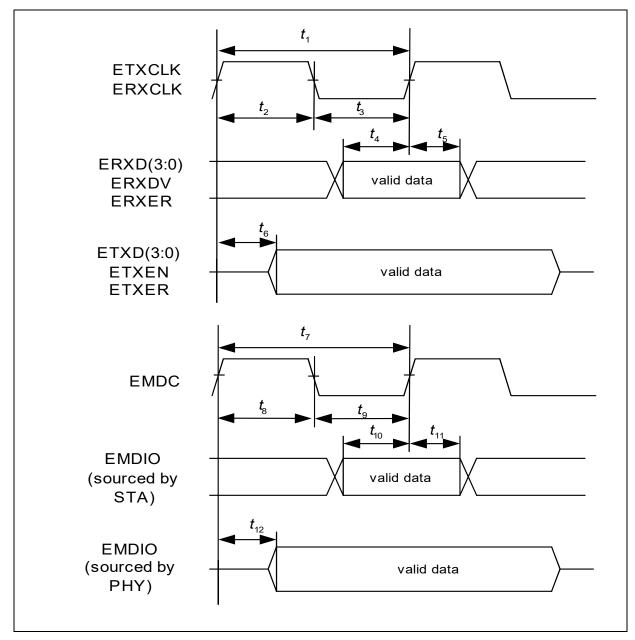

| 4.3.9.1  | Timing for Ethernet Signals                  |       |

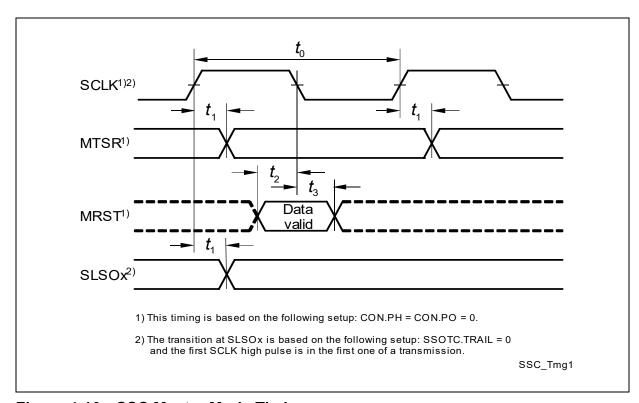

| 4.3.9.2  | SSC Master Mode Timing                       |       |

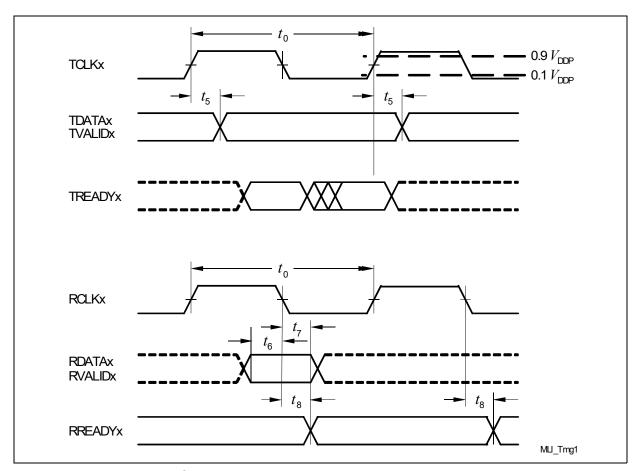

| 4.3.9.3  | MLI Interface Timing                         |       |

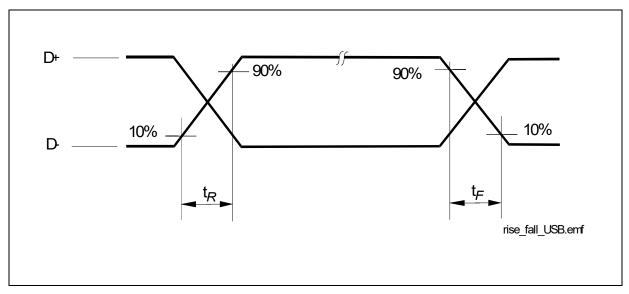

| 4.3.9.4  | Timing for USB Transceiver Signals           | . 106 |

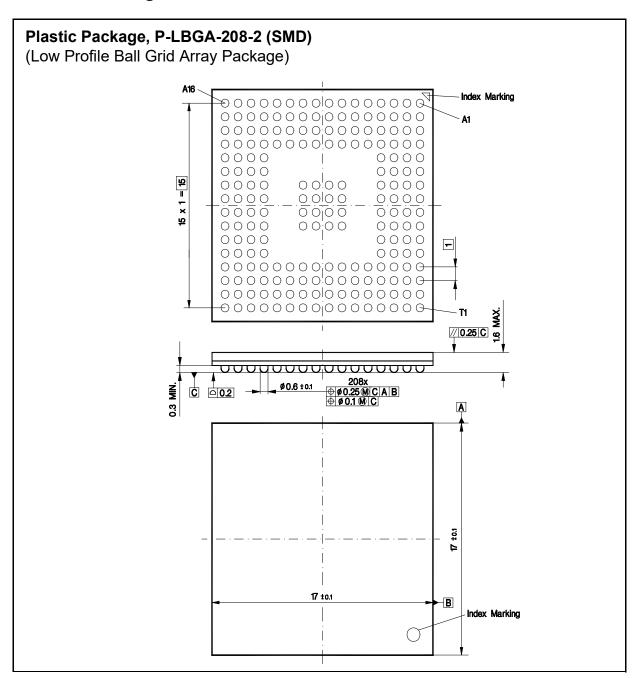

| 5        | Package Outline                              | . 107 |

## 32-Bit Single-Chip Microcontroller TriCore™ Family

TC1130

## 1 Summary of Features

- High Performance 32-bit TriCore<sup>™</sup> V1.3 CPU with 4-Stage Pipeline

- Floating Point Unit (FPU)

- Dual Issue super-scalar implementation

- MAC Instruction maximum triple issue

- Circular Buffer and bit-reverse addressing modes for DSP algorithms

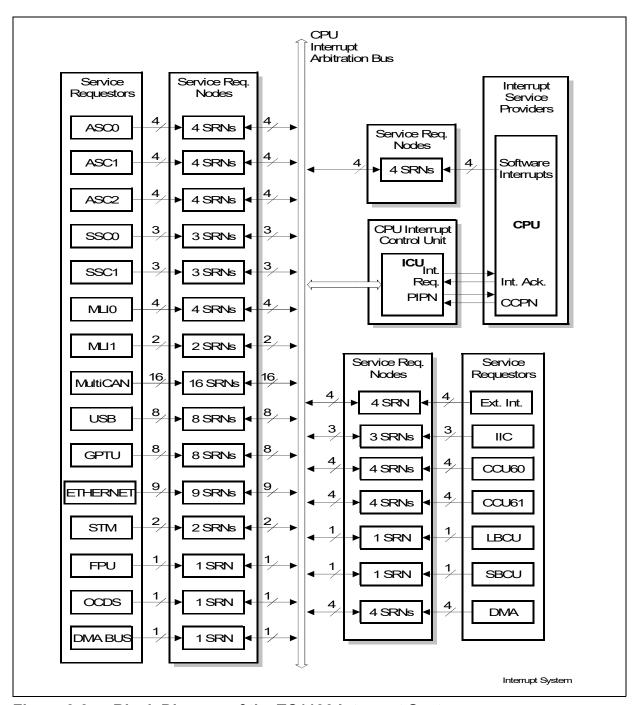

- Very fast interrupt response time

- Hardware controlled context switch for task switch and interrupts

- Memory Management Unit (MMU)

- On-chip Memory

- 28-Kbyte Data Memory (SPRAM)

- 32-Kbyte Code Memory (SPRAM)

- 16-Kbyte Instruction Cache (ICACHE)

- 4-Kbyte Data Cache (DCACHE)

- 64-Kbyte SRAM Data Memory Unit (DMU)

- 16-Kbyte Boot ROM

- On-chip Bus Systems

- 64-bit High Performance Local Memory Bus (LMB) for fast access between caches and on-local memories and FPI Interface

- On-chip Flexible Peripheral Interconnect Bus (FPI) for interconnections of functional units

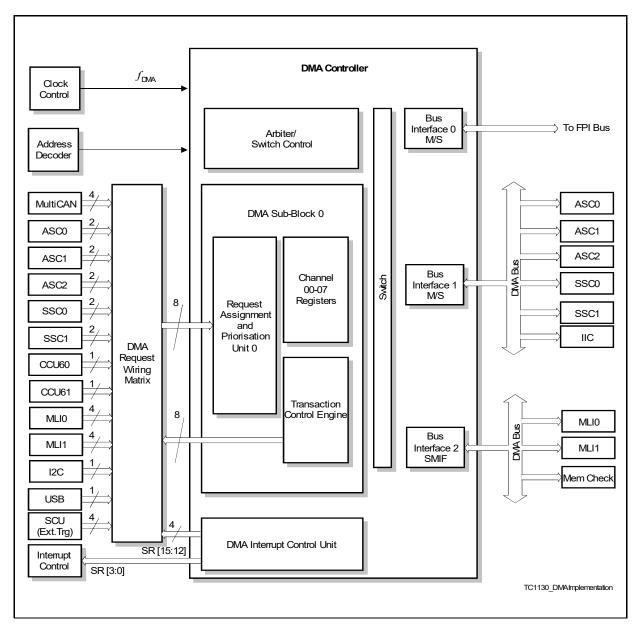

- DMA Controller with 8 channels for data transfer operations between peripheral units and memory locations

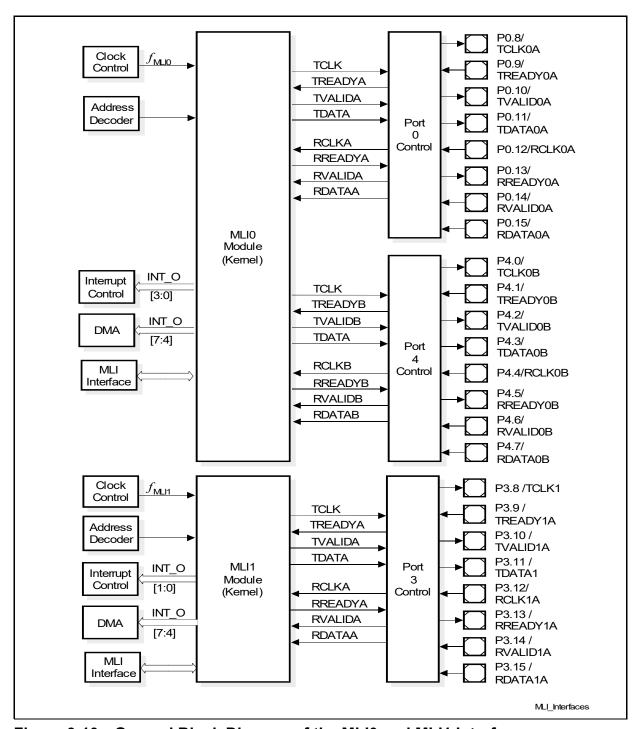

- Two high speed Micro Link Interfaces (MLI0/1) for controller communication and emulation

- Flexible External Bus Interface Unit (EBU) to access external data memories

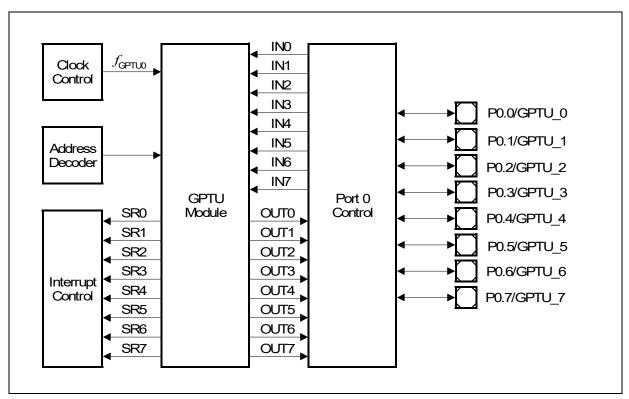

- One Multifunctional General Purpose Timer Unit (GPTU) with three 32-bit timer/ counters

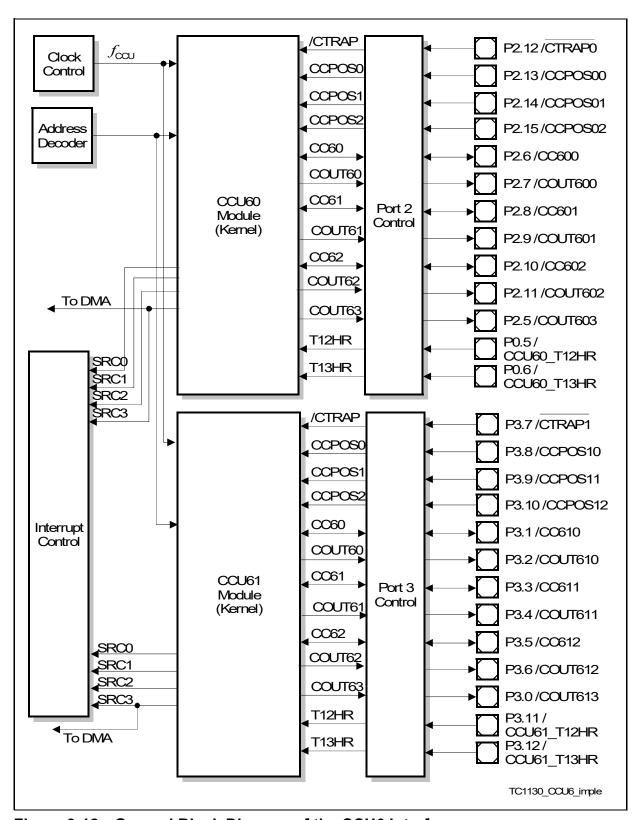

- Two Capture and Compare units (CCU60/1) for PWM signal generation, each with

- 3-channel, 16 bit Capture and Compare unit

- 1-channel, 16 bit Compare unit

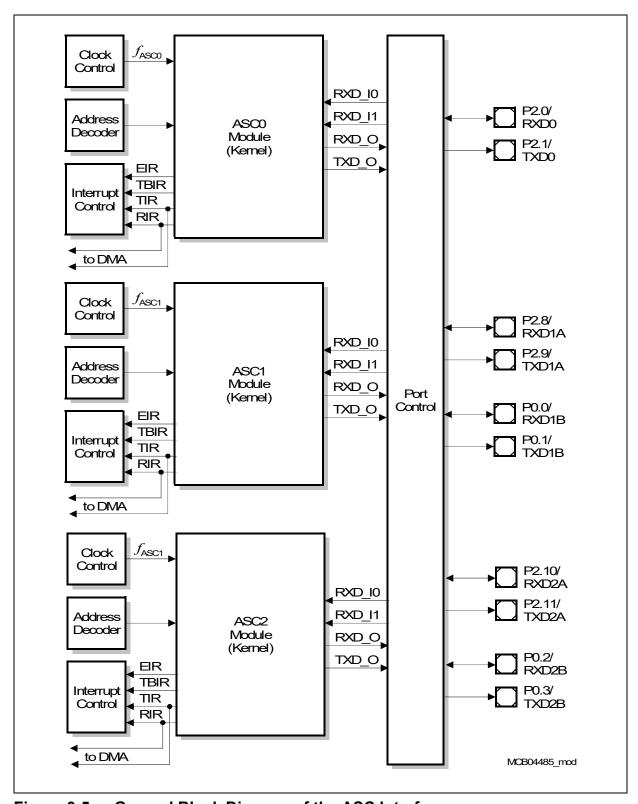

- Three Asynchronous/Synchronous Serial Channels (ASC0/1/2) with baud-rate generator, parity, framing and overrun error detection, support FIFO and IrDA data transmission

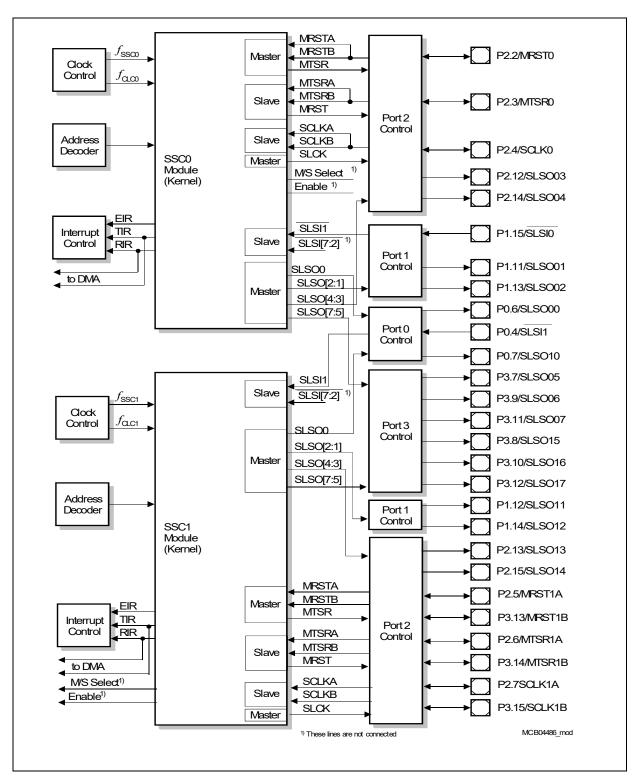

- Two High Speed Synchronous Serial Channels (SSC0/1) with programmable data length, FIFO support and shift direction

Data Sheet 1 V1.1, 2008-12

#### **Summary of Features**

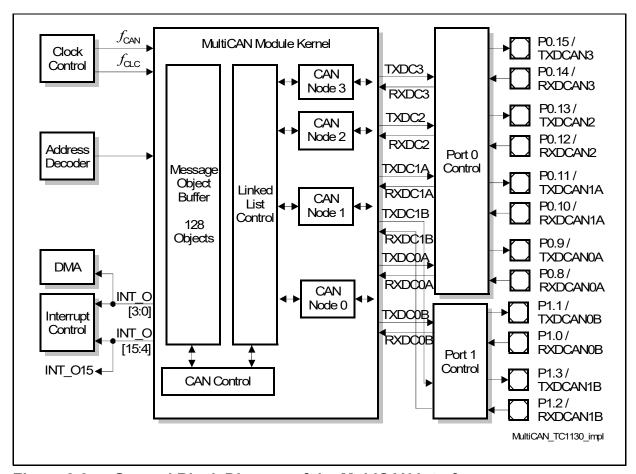

- One MultiCAN module with four CAN nodes and 128 message buffers for high efficiency data handling

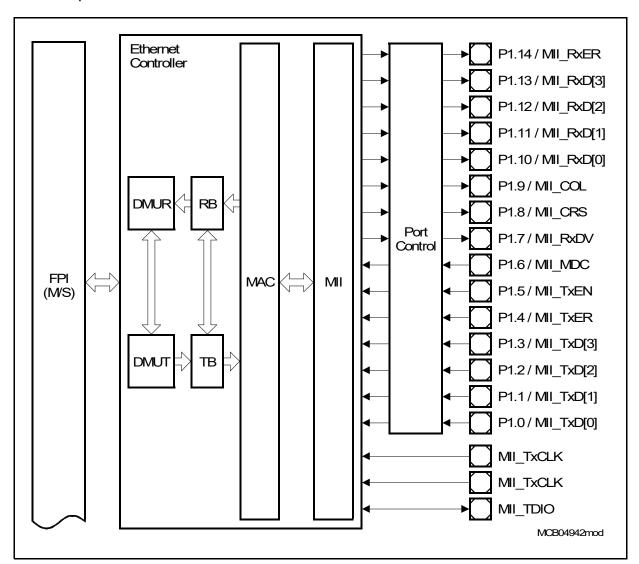

- Fast Ethernet Controller with 10/100 Mbit/sec MII-Based physical devices support

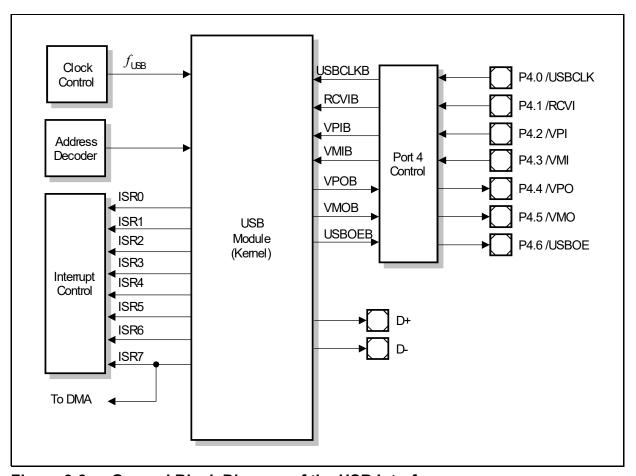

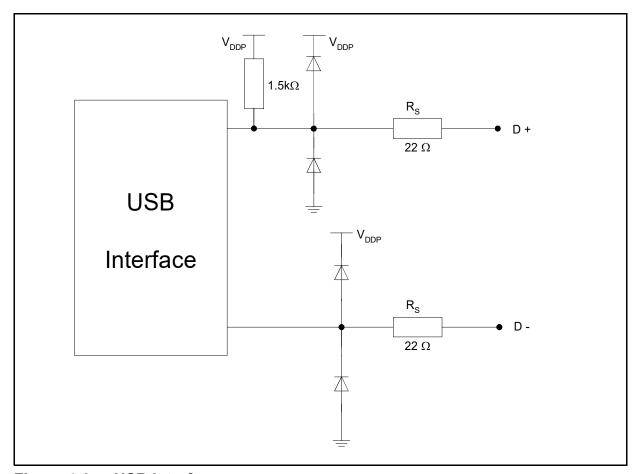

- USB module with compliance to USB Specification Revision 1.1, with support for 1.5 MBaud to 12 MBaud devices

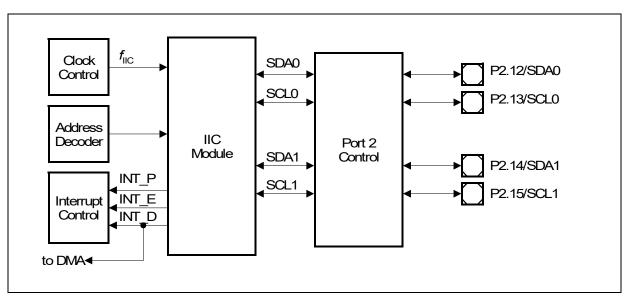

- Inter-IC (IIC) module with two physical IIC buses

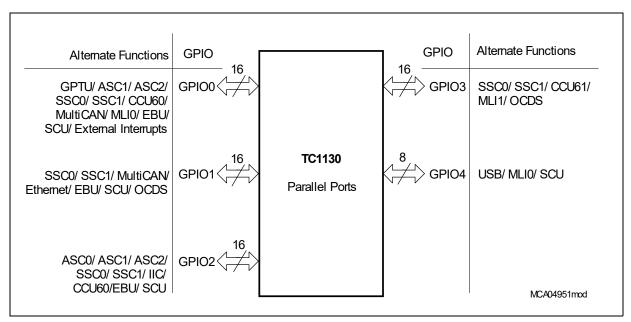

- Digital I/O ports with 3.3 V I/O capabilities

- Level 2 On-chip Debug Support

- Power Management System

- Clock Generation Unit with PLL

- Maximum CPU and Bus clock frequency at 150 MHz without MMU and 120 MHz with MMU

- Ambient temperature under bias: -40° to +85°C

- P-LBGA-208 package

## **2** General Device Information

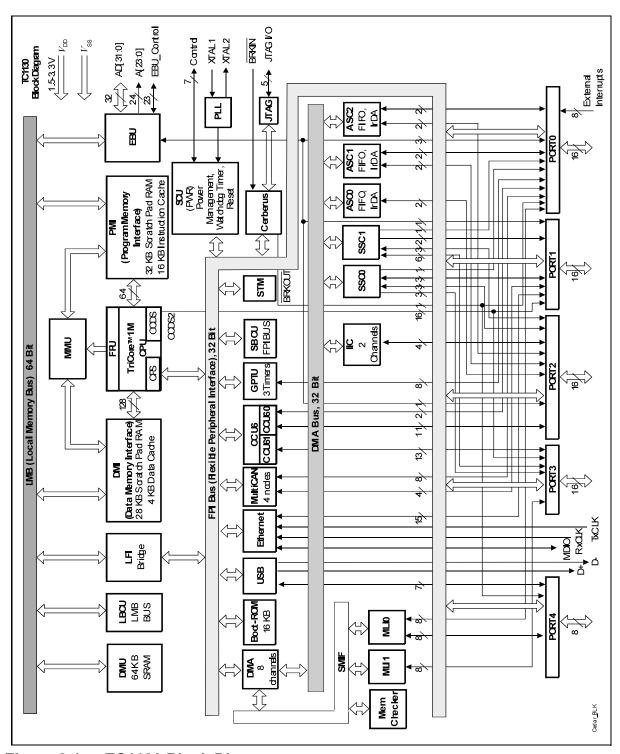

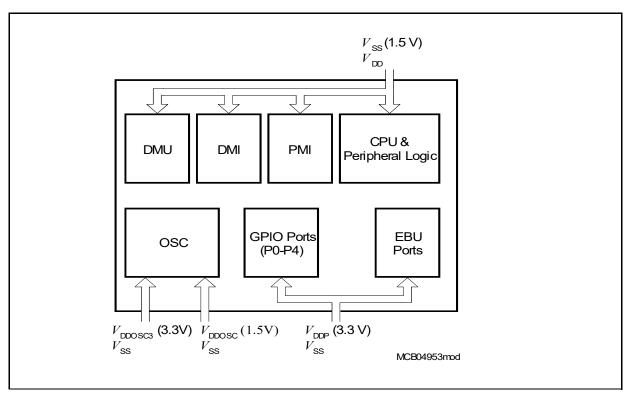

## 2.1 Block Diagram

Figure 2-1 TC1130 Block Diagram

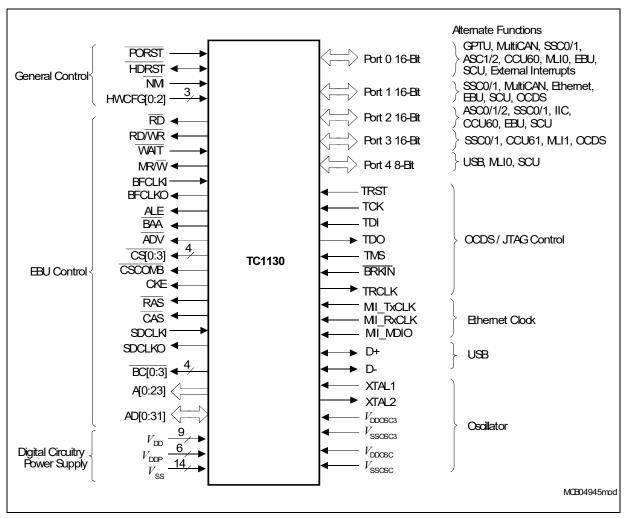

## 2.2 Logic Symbol

Figure 2-2 TC1130 Logic Symbol

## 2.3 Pin Configuration

|    | A            | В     | С     | D           |              | F     | G          | Н               | J              | K        | L                  | M          | N                 | P               | R                 | т                 |    |

|----|--------------|-------|-------|-------------|--------------|-------|------------|-----------------|----------------|----------|--------------------|------------|-------------------|-----------------|-------------------|-------------------|----|

| 16 | Reser<br>ved | P3.10 | P3.11 | P3.12       | P2.15        | P2.14 | P2.11      | P2.9            | P2.8           | P2.7     | V <sub>DDOS0</sub> | XTAL1      | XTAL2             | V <sub>DD</sub> | $V_{ m SS}$       | Reser<br>ved      | 16 |

| 15 | P3.0         | P3.1  | P3.8  | P3.2        | P3.3         | P3.6  | P3.5       | P3.9            | P3.15          | P2.12    | $V_{ m SS}$        | P0.3       | P2.4              | P0.1            | P0.9              | D-                | 15 |

| 14 | P1.9         | P1.10 | P1.11 | P1.14       | P1.13        | P1.15 | P3.4       | P3.7            | P3.14          | P2.13    | HW<br>ŒG1          | HW<br>CFG0 | P2.5              | P2.3            | P0.10             | D+                | 14 |

| 13 | P1.8         | P1.7  | P1.5  | $V_{DDP}$   | $V_{\rm SS}$ | P1.12 | $V_{DD}$   | $V_{SS}$        | $V_{DDP}$      | P3.13    | P2.10              | $V_{SS}$   | $V_{DDP}$         | P2.2            | P0.8              | TDI               | 13 |

| 12 | P1.6         | P1.3  | P1.1  | P1.2        |              |       |            |                 |                |          | ge Pi              | n          | P2.6              | P2.0            | P0.5              | так               | 12 |

| 11 | BAA          | ADV   | P1.4  | P1.0        |              | С     | onfig<br>f |                 | ion (t<br>C113 |          | iew)               |            | P0.0              | P2.1            | P0.4              | TRST              | 11 |

| 10 | A17          | A18   | A19   | A20         |              |       | $V_{DD}$   | Vss             | $V_{SS}$       | $V_{DD}$ |                    |            | P0.7              | P0.2            | P0.6              | ТΣ                | 10 |

| 9  | A16          | WAIT  | CS2   | <u>C</u> 80 |              |       | $V_{DD}$   | V <sub>SS</sub> | $V_{SS}$       | $V_{DD}$ |                    |            | P0.11             | P0.12           | P4.1              | TMS               | 9  |

| 8  | A15          | css   | AD0   | CS1         |              |       | $V_{DD}$   | Vss             | Vss            | $V_{DD}$ |                    |            | P0.14             | P0.13           | P4.0              | TRCLK             | 8  |

| 7  | BC3          | BC2   | AD1   | AD16        |              |       | $V_{DD}$   | Vss             | $V_{SS}$       | $V_{DD}$ |                    |            | P4.2              | P0.15           | P4.5              | NMI               | 7  |

| 6  | BC1          | AD2   | AD3   | RAS         |              | ,     |            |                 |                |          | -                  |            | P4.3              | P4.4            | P4.6              | HW<br>CFG2        | 6  |

| 5  | BC0          | AD17  | AD4   | CAS         |              |       |            |                 |                |          |                    |            | HDRS              | P4.7            | PORST             | BRKIN             | 5  |

| 4  | AD18         | AD 19 | AD20  | $V_{DDP}$   | $V_{SS}$     | AD28  | AD29       | $V_{DDP}$       | $V_{SS}$       | A14      | Œ                  | $V_{DDP}$  | $V_{\rm SS}$      | A23             | A22               | A21               | 4  |

| 3  | AD5          | AD21  | AD7   | AD25        | AD11         | AD12  | AD15       | AD30            | A10            | A11      | A12                | A13        | <u>CS</u><br>COMB | MR/W            | ALE               | RD <del>W</del> F | 3  |

| 2  | AD6          | AD22  | AD8   | AD9         | AD26         | AD27  | AD31       | AD14            | <b>A</b> 5     | A6       | A7                 | A8         | A9                | RD              | MII_<br>RXCLK     | MII_<br>TXCLK     | 2  |

| 1  | Reser<br>ved | AD23  | AD24  |             | BFCLKO       | AD10  | AD13       | acctiko         | SDOLKI         | AO       | A1                 | A2         | A3                | A4              | MII_<br>MDIO      | Reser<br>ved      | 1  |

|    | Α            | В     | С     | D           | E            | F     | G          | Н               | J              | K        | L                  | М          | N                 | Р               | R                 | Т                 |    |

|    |              |       |       |             |              |       |            |                 |                |          |                    |            |                   | MCI             | <del>-</del> 0495 | 0mod              |    |

Figure 2-3 TC1130 Pins: P-BGA-208 Package (top view)

#### 2.4 Pin Definitions and Functions

**Table 2-1** Pin Definitions and Functions

| Symbol       | Pin  | In<br>Out | PU/<br>PD <sup>1)</sup> | Functions         |                                                               |

|--------------|------|-----------|-------------------------|-------------------|---------------------------------------------------------------|

| P0           |      | I/O       |                         | Port 0            |                                                               |

|              |      |           |                         | Port 0 is a 16-bi | it bi-directional general purpose I/O port                    |

|              |      |           |                         | which can be a    | lternatively used for GPTU, MultiCAN,                         |

|              |      |           |                         | ASC1/2, SSC0      | /1, MLI0, EBU and SCU.                                        |

| P0.0         | N11  | I/O       | PUC                     | GPTU_0            | GPTU input/output line 0                                      |

|              |      | I/O       |                         | RXD1B             | ASC1 receiver input/output B                                  |

| P0.1         | P15  | I/O       | PUC                     | GPTU_1            | GPTU input/output line 1                                      |

|              |      | 0         |                         | TXD1B             | ASC1 transmitter output B                                     |

| P0.2         | P10  | I/O       | PUC                     | GPTU_2            | GPTU input/output line 2                                      |

|              |      | I/O       |                         | RXD2B             | ASC2 receiver input/output B                                  |

| P0.3         | M15  | I/O       | PUC                     | GPTU_3            | GPTU input/output line 3                                      |

|              |      | 0         |                         | TXD2B             | ASC2 transmitter output B                                     |

| P0.4         | R11  | I/O       | PUC                     | GPTU_4            | GPTU input/output line 4                                      |

|              |      |           |                         | SLSI1             | SSC1 Slave Select input                                       |

|              |      | 0         |                         | BREQ              | EBU Bus Request Output                                        |

| P0.5         | R12  | I/O       | PUC                     | GPTU_5            | GPTU input/output line 5                                      |

|              |      |           |                         | HOLD              | EBU Hold Request Input                                        |

|              |      |           |                         | l <del></del>     | CCU60 Timer 12 hardware run                                   |

| <b>D</b> 0.0 | D.40 | 0         | D. 10                   | BRKOUT_B          | OCDS Break Out B                                              |

| P0.6         | R10  | I/O       | PUC                     | GPTU_6            | GPTU input/output line 6                                      |

|              |      | I/O       |                         | HLDA              | EBU Hold Acknowledge Input/Output                             |

|              |      |           |                         | _                 | CCU60 Timer 13 hardware run                                   |

| D0.7         | NIAO | 0         | DUG                     | SLSO0_0           | SSC0 Slave Select output 0                                    |

| P0.7         | N10  | I/O       | PUC                     | GPTU_7            | GPTU input/output line 7                                      |

| D0 0         | D40  | 0         | DUG                     | SLSO1_0           | SSC1 Slave Select output 0                                    |

| P0.8         | R13  |           | PUC                     |                   |                                                               |

|              |      | 0         |                         | REQ0              | External Trigger Input 0 MLI0 transmit channel clock output A |

| P0.9         | R15  |           | PUC                     | TCLK0A            | •                                                             |

| P0.9         | KIS  | 0         | PUC                     | TREADY0A          | CAN node 0 transmitter output A                               |

|              |      |           |                         | REQ1              | MLI0 transmit channel ready input A                           |

| P0.10        | R14  |           | PUC                     |                   | External Trigger Input 1 CAN node 1 receiver input A          |

| F 0. 10      | 1114 |           | - 00                    | REQ2              | External Trigger Input 2                                      |

|              |      | 0         |                         | TVALID0A          | MLI0 transmit channel valid output A                          |

| P0.11        | N9   | 0         | PUC                     | TXDCAN1_A         | CAN node 1 transmitter output A                               |

| 1 0.11       | פוו  |           | 00                      | REQ3              | External Trigger Input 3                                      |

|              |      | 0         |                         | TDATA0A           | MLI0 transmit channel data output A                           |

|              |      |           |                         | IDAIAUA           | METO transmit oriannel data output A                          |

**Table 2-1 Pin Definitions and Functions** (cont'd)

| Symbol | Pin | In<br>Out | PU/<br>PD <sup>1)</sup> | Functions |                                     |

|--------|-----|-----------|-------------------------|-----------|-------------------------------------|

| P0.12  | P9  | I         | PUC                     | RXDCAN2   | CAN node 2 receiver input           |

|        |     | 1         |                         | RCLK0A    | MLI0 receive channel clock input A  |

|        |     | 1         |                         | REQ4      | External Trigger Input 4            |

| P0.13  | P8  | 0         | PUC                     | TXDCAN2   | CAN node 2 transmitter output       |

|        |     | 1         |                         | REQ5      | External Trigger Input 5            |

|        |     | 0         |                         | RREADY0A  | MLI0 receive channel ready output A |

| P0.14  | N8  | 1         | PUC                     | RXDCAN3   | CAN node 3 receiver input           |

|        |     | 1         |                         | REQ6      | External Trigger Input 6            |

|        |     | 1         |                         | RVALID0A  | MLI0 receive channel valid input A  |

| P0.15  | P7  | 0         | PUC                     | TXDCAN3   | CAN node 3 transmitter output       |

|        |     | 1         |                         | REQ7      | External Trigger Input 7            |

|        |     | I         |                         | RDATA0A   | MLI0 receive channel data input A   |

**Table 2-1 Pin Definitions and Functions** (cont'd)

| Symbol | Pin | In<br>Out | PU/<br>PD <sup>1)</sup> | Functions       |                                                       |

|--------|-----|-----------|-------------------------|-----------------|-------------------------------------------------------|

| P1     |     | I/O       |                         | Port 1          |                                                       |

|        |     |           |                         | Port 1 serves   | as 16-bit bi-directional general purpose              |

|        |     |           |                         | I/O port which  | can be used for input/output for Ethernet             |

|        |     |           |                         | controller, Mul | tiCAN, CAN, OCDS L2, SSC0/1, EBU                      |

|        |     |           |                         | and SCU.        |                                                       |

| P1.0   | D11 | 0         | PUC                     | MII_TXD0        | Ethernet controller transmit data                     |

|        |     |           |                         |                 | output line 0                                         |

|        |     | 1         |                         | RXDCAN0_B       | CAN node 0 receiver input B                           |

|        |     | 1         |                         | SWCFG0          | Software configuration 0                              |

|        |     | 0         |                         | OCDSA_0         | OCDS L2 Debug Line A0                                 |

| P1.1   | C12 | 0         | PUC                     | MII_TXD1        | Ethernet controller transmit data output line 1       |

|        |     | 1         |                         | SWCFG1          | Software configuration 1                              |

|        |     | 0         |                         | TXDCAN0_B       | CAN node 0 transmitter output B                       |

|        |     | 0         |                         | OCDSA_1         | OCDS L2 Debug Line A1                                 |

| P1.2   | D12 | 0         | PUC                     | MII_TXD2        | Ethernet controller transmit data output line 2       |

|        |     | 1         |                         | RXDCAN1_B       | CAN node 1 receiver input B                           |

|        |     | 1         |                         | SWCFG2          | Software configuration 2                              |

|        |     | 0         |                         | OCDSA_2         | OCDS L2 Debug Line A2                                 |

| P1.3   | B12 | 0         | PUC                     | MII_TXD3        | Ethernet controller transmit data output line 3       |

|        |     | 0         |                         | TXDCAN1 B       | CAN node 1 transmitter output B                       |

|        |     | 1         |                         | SWCFG3          | Software configuration 3                              |

|        |     | 0         |                         | OCDSA_3         | OCDS L2 Debug Line A3                                 |

| P1.4   | C11 | 0         | PUC                     | MII TXER        | Ethernet controller transmit error                    |

|        |     |           |                         | _               | output line                                           |

|        |     | 1         |                         | SWCFG4          | Software configuration 4                              |

|        |     | 0         |                         | OCDSA_4         | OCDS L2 Debug Line A4                                 |

| P1.5   | C13 | 0         | PUC                     | MII_TXEN        | Ethernet controller transmit enable output line       |

|        |     | 1         |                         | SWCFG5          | Software configuration 5                              |

|        |     | 0         |                         | OCDSA 5         | OCDS L2 Debug Line A5                                 |

| P1.6   | A12 | 0         | PUC                     | MII_MDC         | Ethernet controller management data clock output line |

|        |     | 1         |                         | SWCFG6          | Software configuration 6                              |

|        |     | 0         |                         | OCDSA_6         | OCDS L2 Debug Line A6                                 |

**Table 2-1 Pin Definitions and Functions** (cont'd)

| Symbol | Pin | In<br>Out | PU/<br>PD <sup>1)</sup> | Functions |                                                   |

|--------|-----|-----------|-------------------------|-----------|---------------------------------------------------|

| P1.7   | B13 | I         | PUC                     | MII_RXDV  | Ethernet Controller receive data valid input line |

|        |     | 1         |                         | SWCFG7    | Software configuration 7                          |

|        |     | 0         |                         | OCDSA_7   | OCDS L2 Debug Line A7                             |

| P1.8   | A13 | 1         | PUC                     | MII_CRS   | Ethernet Controller carrier input line            |

|        |     | 1         |                         | SWCFG8    | Software configuration 8                          |

|        |     | 0         |                         | OCDSA_8   | OCDS L2 Debug Line A8                             |

| P1.9   | A14 | I         | PUC                     | MII_COL   | Ethernet Controller collision input line          |

|        |     | 1         |                         | SWCFG9    | Software configuration 9                          |

|        |     | 0         |                         | OCDSA_9   | OCDS L2 Debug Line A9                             |

| P1.10  | B14 | I         | PUC                     | MII_RXD0  | Ethernet Controller receive data input line 0     |

|        |     | 1         |                         | SWCFG10   | Software configuration 10                         |

|        |     | 0         |                         | OCDSA_10  | OCDS L2 Debug Line A10                            |

| P1.11  | C14 | I         | PUC                     | MII_RXD1  | Ethernet Controller receive data input line 1     |

|        |     | 1         |                         | SWCFG11   | Software configuration 11                         |

|        |     | 0         |                         | OCDSA_11  | OCDS L2 Debug Line A1                             |

|        |     | 0         |                         | SLSO0_1   | SSC0 Slave Select output 1                        |

| P1.12  | F13 | I         | PUC                     | MII_RXD2  | Ethernet Controller receive data input line 2     |

|        |     | 1         |                         | SWCFG12   | Software configuration 12                         |

|        |     | 0         |                         | OCDSA_12  | OCDS L2 Debug Line A12                            |

|        |     | 0         |                         | SLSO1_1   | SSC1 Slave Select output 1                        |

| P1.13  | E14 | I         | PUC                     | MII_RXD3  | Ethernet Controller receive data input line 3     |

|        |     | 1         |                         | SWCFG13   | Software configuration 13                         |

|        |     | 0         |                         | OCDSA_13  | OCDS L2 Debug Line A13                            |

|        |     | 0         |                         | SLSO0_2   | SSC0 Slave Select output 2                        |

| P1.14  | D14 | I         | PUC                     | MII_RXER  | Ethernet Controller receive error input line      |

|        |     | 0         |                         | SLSO1 2   | SSC1 Slave Select output 2                        |

|        |     | 1         |                         | SWCFG14   | Software configuration 14                         |

|        |     | 0         |                         | OCDSA 14  | OCDS L2 Debug Line A14                            |

| P1.15  | F14 | I         | PUC                     | SLSI0     | SSC0 Slave Select Input                           |

|        |     | 0         |                         | RMW       | EBU Read Modify Write                             |

|        |     | 1         |                         | SWCFG15   | Software configuration 15                         |

|        |     | 0         |                         | OCDSA_15  | OCDS L2 Debug Line A15                            |

**Table 2-1 Pin Definitions and Functions** (cont'd)

| Symbol | Pin    | In<br>Out | PU/<br>PD <sup>1)</sup> | Functions        |                                                 |

|--------|--------|-----------|-------------------------|------------------|-------------------------------------------------|

| P2     |        | I/O       |                         | Port 2           |                                                 |

|        |        |           |                         | Port 2 is a 16-l | bit bi-directional general purpose I/O port     |

|        |        |           |                         |                  | alternatively used for ASC0/1/2, SSC0/1,        |

|        |        |           |                         |                  | EBU and SCU.                                    |

| P2.0   | P12    | I/O       | PUC                     | RXD0             | ASC0 receiver input/output line                 |

|        |        | 0         |                         | CSEMU            | EBU Chip Select Output for Emulator             |

|        |        |           |                         |                  | Region                                          |

| P2.1   | P11    | 0         | PUC                     | TXD0             | ASC0 transmitter output line                    |

|        |        | 1         |                         | TESTMODE         | Test Mode Select Input                          |

| P2.2   | P13    | I/O       | PUC                     | MRST0            | SSC0 master receive/slave transmit              |

|        |        |           |                         |                  | input/output                                    |

| P2.3   | P14    | I/O       | PUC                     | MTSR0            | SSC0 master transmit/slave receive input/output |

| P2.4   | N15    | I/O       | PUC                     | SCLK0            | SSC0 clock input/output line                    |

| P2.5   | N14    | 0         | PUC                     | COUT60_3         | CCU60 compare channel 3 output                  |

| 1 2.0  | 1,4,1, | 1/0       | 00                      | MRST1A           | SSC1 master receive/slave transmit              |

|        |        | "         |                         |                  | input/output A                                  |

| P2.6   | N12    | I/O       | PUC                     | CC60_0           | CCU60 input/output of capture                   |

| -      |        |           |                         |                  | compare channel 0                               |

|        |        | I/O       |                         | MTSR1A           | SSC1 master transmit/slave receive              |

|        |        |           |                         |                  | input/output A                                  |

| P2.7   | K16    | 0         | PUC                     | COUT60 0         | CCU60 output of capture/compare                 |

|        |        |           |                         | _                | channel 0                                       |

|        |        | I/O       |                         | SCLK1A           | SSC1 clock input/output line A                  |

| P2.8   | J16    | I/O       | PUC                     | CC60_1           | CCU60 input/output of capture/                  |

|        |        |           |                         |                  | compare channel 1                               |

|        |        | I/O       |                         | RXD1A            | ASC1 receiver input/output line A               |

| P2.9   | H16    | О         | PUC                     | COUT60_1         | CCU60 output of capture/compare channel 1       |

|        |        | 0         |                         | TXD1A            | ASC1 transmitter output line A                  |

| P2.10  | L13    | I/O       | PUC                     | CC60_2           | CCU60 input/output of capture/                  |

|        |        |           |                         | _                | compare channel 2                               |

|        |        | I/O       |                         | RXD2A            | ASC2 receiver input/output line A               |

| P2.11  | G16    | 0         | PUC                     | COUT60 2         | CCU60 output of capture/compare                 |

|        |        |           |                         | _                | channel 2                                       |

|        |        | 0         |                         | TXD2A            | ASC2 transmitter output line A                  |

| P2.12  | K15    | I/O       |                         | SDA0             | IIC Serial Data line 0                          |

|        |        | 1         |                         | CTRAP0           | CCU60 trap input                                |

|        |        | 0         |                         | SLSO0_3          | SSC0 Slave Select output 3                      |

**Table 2-1 Pin Definitions and Functions** (cont'd)

| Symbol | Pin | In<br>Out | PU/<br>PD <sup>1)</sup> | Functions |                            |

|--------|-----|-----------|-------------------------|-----------|----------------------------|

| P2.13  | K14 | I/O       |                         | SCL0      | IIC clock line 0           |

|        |     | 1         |                         | CCPOS0_0  | CCU60 Hall input signal 0  |

|        |     | 0         |                         | SLSO1_3   | SSC1 Slave Select output 3 |

| P2.14  | F16 | 1         |                         | CCPOS0_1  | CCU60 Hall input signal 1  |

|        |     | I/O       |                         | SDA1      | IIC Serial Data line 1     |

|        |     | 0         |                         | SLSO0_4   | SSC0 Slave Select output 4 |

| P2.15  | E16 | 1         |                         | CCPOS0_2  | CCU60 Hall input signal 2  |

|        |     | I/O       |                         | SCL1      | IIC clock line 1           |

|        |     | 0         |                         | SLSO1_4   | SSC1 Slave Select output 4 |

**Table 2-1 Pin Definitions and Functions** (cont'd)

| Symbol | Pin | In<br>Out | PU/<br>PD <sup>1)</sup> | Functions       |                                           |

|--------|-----|-----------|-------------------------|-----------------|-------------------------------------------|

| P3     |     | I/O       |                         | Port 3          |                                           |

|        |     |           |                         | Port 3 is a 16- | -bit bi-directional general purpose I/O   |

|        |     |           |                         | port which car  | be alternatively used for MLI1, CCU61,    |

|        |     |           |                         | SSC0/1 and C    | OCDS Level 2 debug lines.                 |

| P3.0   | A15 | 0         | PUC                     | OCDSB_0         | OCDS L2 Debug Line B0                     |

|        |     | 0         |                         | COUT61_3        | CCU61 compare channel 3 output            |

| P3.1   | B15 | 0         | PUC                     | OCDSB_1         | OCDS L2 Debug Line B1                     |

|        |     | I/O       |                         | CC61_0          | CCU61 input/output of capture/            |

|        |     |           |                         |                 | compare channel 0                         |

| P3.2   | D15 | 0         | PUC                     | OCDSB_2         | OCDS L2 Debug Line B2                     |

|        |     | 0         |                         | COUT61_0        | CCU61 output of capture/compare           |

|        |     |           |                         |                 | channel 0                                 |

| P3.3   | E15 | 0         | PUC                     | OCDSB_3         | OCDS L2 Debug Line B3                     |

|        |     | I/O       |                         | CC61_1          | CCU61 input/output of capture/            |

|        |     |           | _                       |                 | compare channel 1                         |

| P3.4   | G14 | 0         | PUC                     | OCDSB_4         | OCDS L2 Debug Line B4                     |

|        |     | 0         |                         | COUT61_1        | CCU61 output of capture/compare           |

|        |     |           |                         |                 | channel 1                                 |

| P3.5   | G15 | 0         | PUC                     | OCDSB_5         | OCDS L2 Debug Line B5                     |

|        |     | I/O       |                         | CC61_2          | CCU61 input/output of capture/            |

| D0 0   | E45 |           | DITO                    | 00000           | compare channel 2                         |

| P3.6   | F15 | 0         | PUC                     | OCDSB_6         | OCDS L2 Debug Line B6                     |

|        |     | 0         |                         | COUT61_2        | CCU61 output of capture/compare channel 2 |

| P3.7   | H14 | 0         | PUC                     | OCDSB 7         | OCDS L2 Debug Line B7                     |

|        |     | I         |                         | CTRAP1          | CCU61 trap input                          |

|        |     | 0         |                         | SLSO0_5         | SSC0 Slave Select output 5                |

| P3.8   | C15 | 0         | PUC                     | OCDSB_8         | OCDS L2 Debug Line B8                     |

|        |     | I         |                         | CCPOS1_0        | CCU61 Hall input signal 0                 |

|        |     | 0         |                         | TCLK1           | MLI1 transmit channel clock output        |

|        |     | 0         |                         | SLSO1_5         | SSC1 Slave Select output 5                |

| P3.9   | H15 | 0         | PUC                     | OCDSB_9         | OCDS L2 Debug Line B9                     |

|        |     | I         |                         | CCPOS1_1        | CCU61 Hall input signal 1                 |

|        |     | I         |                         | TREADY1         | MLI1 transmit channel ready input         |

|        |     | 0         |                         | SLSO0_6         | SSC0 Slave Select output 6                |

| P3.10  | B16 | 0         | PUC                     | OCDSB_10        | OCDS L2 Debug Line B10                    |

|        |     | I         |                         | CCPOS1_2        | CCU61 Hall input signal 2                 |

|        |     | 0         |                         | TVALID1         | MLI1 transmit channel valid output        |

|        |     | 0         |                         | SLSO1_6         | SSC1 Slave Select output 6                |

**Table 2-1 Pin Definitions and Functions** (cont'd)

| Symbol | Pin | In<br>Out | PU/<br>PD <sup>1)</sup> | Functions  |                                   |

|--------|-----|-----------|-------------------------|------------|-----------------------------------|

| P3.11  | C16 | 0         | PUC                     | OCDSB_11   | OCDS L2 Debug Line B11            |

|        |     | 0         |                         | TDATA1     | MLI1 transmit channel data output |

|        |     | 0         |                         | SLSO0_7    | SSC0 Slave Select output 7        |

|        |     | 1         |                         | CC61_T12HR | CCU61 Timer 12 hardware run       |

| P3.12  | D16 | 0         | PUC                     | OCDSB_12   | OCDS L2 Debug Line B12            |

|        |     | 1         |                         | RCLK1      | MLI1 receive channel clock input  |

|        |     | 0         |                         | SLSO1_7    | SSC1 Slave Select output 7        |

|        |     | 1         |                         | CC61_T13HR | CCU61 Timer 13 hardware run       |

| P3.13  | K13 | 0         | PUC                     | OCDSB_13   | OCDS L2 Debug Line B13            |

|        |     | 0         |                         | RREADY1    | MLI1 receive channel ready output |

|        |     | I/O       |                         | MRST1B     | SSC1 master receive/slave         |

|        |     |           |                         |            | transmit input/output B           |

| P3.14  | J14 | 0         | PUC                     | OCDSB_14   | OCDS L2 Debug Line B14            |

|        |     | 1         |                         | RVALID1    | MLI1 receive channel valid input  |

|        |     | I/O       |                         | MTSR1B     | SSC1 master transmit/slave        |

|        |     |           |                         |            | receive input/output B            |

| P3.15  | J15 | 0         | PUC                     | OCDSB_15   | OCDS L2 Debug Line B15            |

|        |     | 1         |                         | RDATA1     | MLI1 receive channel data input   |

|        |     | I/O       |                         | SCLK1B     | SSC1 clock input/output line B    |

**Table 2-1 Pin Definitions and Functions** (cont'd)

| Symbol | Pin | In<br>Out | PU/<br>PD <sup>1)</sup> | Functions                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                    |  |

|--------|-----|-----------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| P4     |     | I/O       |                         | Port 4 Port 4 is an 8-bit bi-directional general purpose I/O port which can be alternatively used for USB, MLI0 and                              |                                                                                                                                                                                                                                                                                                                                    |  |

| P4.0   | R8  | I<br>O    | PUC                     | SCU.<br>USBCLK<br>TCLK0B                                                                                                                         | 48 MHz input clock MLI0 transmit channel clock output B                                                                                                                                                                                                                                                                            |  |

| P4.1   | R9  | I<br>I    | PUC                     | RCVI<br>TREADY0B                                                                                                                                 | USB data input MLI0 transmit channel ready input B                                                                                                                                                                                                                                                                                 |  |

| P4.2   | N7  | ĺ         | PUC                     | VPI                                                                                                                                              | USB D+ CMOS level mirror of differential signal                                                                                                                                                                                                                                                                                    |  |

| P4.3   | N6  | O         | PUC                     | TVALID0B<br>VMI                                                                                                                                  | MLI0 transmit channel valid output B<br>USB D- CMOS level mirror of<br>differential signal                                                                                                                                                                                                                                         |  |

| P4.4   | P6  | 0         | PUC                     | TDATA0B<br>VPO<br>RCLK0B                                                                                                                         | MLI0 transmit channel data output B USB D+ CMOS level output MLI0 receive channel clock input B                                                                                                                                                                                                                                    |  |

| P4.5   | R7  | 0         | PUC                     | VMO<br>RREADY0B                                                                                                                                  | USB D- CMOS level output MLI0 receive channel ready output B                                                                                                                                                                                                                                                                       |  |

| P4.6   | R6  | 0         | PUC                     | USBOE<br>RVALID0B                                                                                                                                | Direction select for transmit or receive MLI0 receive channel valid input B                                                                                                                                                                                                                                                        |  |

| P4.7   | P5  | I<br>O    | PUC                     | RDATA0B<br>BRKOUT_A                                                                                                                              | MLI0 receive channel data input B<br>OCDS Break Out A                                                                                                                                                                                                                                                                              |  |

| HDRST  | N5  | I/O       | PUA                     | Assertion of the synchronous circuitry. This clock cycles. The internal reto a power-on wake-up rese                                             | eset Input/Reset Indication Output his bi-directional open-drain pin causes a reset of the chip through external pin must be driven for a minimum $4f_{\rm CPU}$ eset circuitry drives this pin in response h, hardware, watchdog and power-down t for a specific period of time. For a t, activation of this pin is programmable. |  |

| PORST  | R5  | I         | PUC                     | Power-on Reset Input A low level on PORST causes an asynchronous reset of the entire chip. PORST is a fully asynchronous level sensitive signal. |                                                                                                                                                                                                                                                                                                                                    |  |

| NMI    | Т7  | I         | PUC                     | A high-to-low                                                                                                                                    | le Interrupt Input<br>transition on this pin causes an<br>uest to the CPU.                                                                                                                                                                                                                                                         |  |

**Table 2-1 Pin Definitions and Functions** (cont'd)

| Symbol                     | Pin              | In<br>Out | PU/<br>PD <sup>1)</sup> | Functions                                                                                                                                                                                                                                                                                    |  |

|----------------------------|------------------|-----------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TRST                       | T11              | I         | PDC                     | JTAG Module Reset/Enable Input A low level at this pin resets and disables the JTAG module. A high level enables the JTAG module.                                                                                                                                                            |  |

| TCK                        | T12              | I         | PUC                     | JTAG Module Clock Input                                                                                                                                                                                                                                                                      |  |

| TDI                        | T13              | I         | PUC                     | JTAG Module Serial Data Input                                                                                                                                                                                                                                                                |  |

| TDO                        | T10              | 0         |                         | JTAG Module Serial Data Output                                                                                                                                                                                                                                                               |  |

| TMS                        | T9               | ı         | PUC                     | JTAG Module State Machine Control Input                                                                                                                                                                                                                                                      |  |

| TRCLK                      | T8               | 0         | _                       | Trace Clock for OCDS_L2 Lines                                                                                                                                                                                                                                                                |  |

| HWCFG0<br>HWCFG1<br>HWCFG2 | M14<br>L14<br>T6 |           | PUC<br>PUC<br>PDC       | Hardware Configuration Inputs The Configuration Inputs define the boot options of the TC1130 after a hardware invoked reset operation.                                                                                                                                                       |  |

| BRKIN                      | T5               | I         | PUC                     | OCDS Break Input A low level on this pin causes a break in the chip's execution when the OCDS is enabled. In addition, the level of this pin during power-on reset determines the boot configuration.                                                                                        |  |

| MII_<br>TXCLK              | T2               | I         | PDC                     | +                                                                                                                                                                                                                                                                                            |  |

| MII_<br>RXCLK              | R2               | I         | PDC                     | Ethernet Controller Receive Clock MII_RXCLK is a continuous clock. Its frequency is 25 MHz for 100 Mbit/sec operation, and 2.5 MHz for 10 Mbit/sec. MII_RXD[3:0], MII_RXDV and MII_EXER are driven by the PHY off the falling edge of MII_RXCLK and sampled on the rising edge of MII_RXCLK. |  |

| MII_<br>MDIO               | R1               | I/O       | PDA                     | Ethernet Controller Management Data Input/ Output When a read command is being executed, the data that is clocked out of the PHY will be presented on the input line. When the Core is clocking control or data onto the MII_MDIO line, the signal will carry the information.               |  |

| D+                         | T14              | I/O       |                         | USB D+ Data Line                                                                                                                                                                                                                                                                             |  |

**Table 2-1 Pin Definitions and Functions** (cont'd)

| Symbol                   | Pin                  | In<br>Out | PU/<br>PD <sup>1)</sup>  | Functions                                                                                                                                                                                              |

|--------------------------|----------------------|-----------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D-                       | T15                  | I/O       | _                        | USB D- Data Line                                                                                                                                                                                       |

| CS0<br>CS1<br>CS2<br>CS3 | D9<br>D8<br>C9<br>B8 | 0 0 0     | PUC<br>PUC<br>PUC<br>PUC | EBU Chip Select Output Line 0 EBU Chip Select Output Line 1 EBU Chip Select Output Line 2 EBU Chip Select Output Line 3 Each corresponds to a programmable region. Only one can be active at one time. |

| CSCOMB                   | N3                   | 0         | PUC                      | EBU Chip Select Output for combination function (Overlay Memory and Global)                                                                                                                            |

| SDCLKI                   | J1                   | I         |                          | SDRAM Clock Input (Clock Feedback)                                                                                                                                                                     |

| SDCLKO                   | H1                   | 0         |                          | SDRAM Clock Output Accesses to SDRAM devices are synchronized to this clock.                                                                                                                           |

| RAS                      | D6                   | 0         | PUC                      | EBU SDRAM Row Address Strobe Output                                                                                                                                                                    |

| CAS                      | D5                   | 0         | PUC                      | EBU SDRAM Column Address Strobe Output                                                                                                                                                                 |

| CKE                      | L4                   | 0         | PUC                      | EBU SDRAM Clock Enable Output                                                                                                                                                                          |

| BFCLKI                   | D1                   | I         |                          | Burst Flash Clock Input (Clock Feedback)                                                                                                                                                               |

| BFCLKO                   | E1                   | 0         |                          | Burst Flash Clock Output Accesses to Burst Flash devices are synchronized to this clock.                                                                                                               |

| RD                       | P2                   | 0         | PUC                      | EBU Read Control Line Output in master mode Input in slave mode                                                                                                                                        |

| RD/WR                    | Т3                   | 0         | PUC                      | EBU Write Control Line Output in master mode Input in slave mode                                                                                                                                       |

| WAIT                     | B9                   | I         | PUC                      | EBU Wait Control Line                                                                                                                                                                                  |

| ALE                      | R3                   | 0         | PDC                      | EBU Address Latch Enable Output                                                                                                                                                                        |

| MR/W                     | P3                   | 0         | PUC                      | EBU Motorola-style Read/Write Output                                                                                                                                                                   |

| BAA                      | A11                  | 0         | PUC                      | EBU Burst Address Advance Output                                                                                                                                                                       |

|                          |                      |           |                          | For advancing address in a Burst Flash access                                                                                                                                                          |

| ADV                      | B11                  | 0         | PUC                      | EBU Burst Flash Address Valid Output                                                                                                                                                                   |

**Table 2-1 Pin Definitions and Functions** (cont'd)

| Symbol | Pin | In<br>Out | PU/<br>PD <sup>1)</sup> | Functions                               |

|--------|-----|-----------|-------------------------|-----------------------------------------|

|        |     |           |                         | EBU Address/Data Bus Input/Output Lines |

| AD0    | C8  | I/O       | PUC                     | EBU Address/Data Bus Line 0             |

| AD1    | C7  | I/O       | PUC                     | EBU Address/Data Bus Line 1             |

| AD2    | B6  | I/O       | PUC                     | EBU Address/Data Bus Line 2             |

| AD3    | C6  | I/O       | PUC                     | EBU Address/Data Bus Line 3             |

| AD4    | C5  | I/O       | PUC                     | EBU Address/Data Bus Line 4             |

| AD5    | A3  | I/O       | PUC                     | EBU Address/Data Bus Line 5             |

| AD6    | A2  | I/O       | PUC                     | EBU Address/Data Bus Line 6             |

| AD7    | C3  | I/O       | PUC                     | EBU Address/Data Bus Line 7             |

| AD8    | C2  | I/O       | PUC                     | EBU Address/Data Bus Line 8             |

| AD9    | D2  | I/O       | PUC                     | EBU Address/Data Bus Line 9             |

| AD10   | F1  | I/O       | PUC                     | EBU Address/Data Bus Line 10            |

| AD11   | E3  | I/O       | PUC                     | EBU Address/Data Bus Line 11            |

| AD12   | F3  | I/O       | PUC                     | EBU Address/Data Bus Line 12            |

| AD13   | G1  | I/O       | PUC                     | EBU Address/Data Bus Line 13            |

| AD14   | H2  | I/O       | PUC                     | EBU Address/Data Bus Line 14            |

| AD15   | G3  | I/O       | PUC                     | EBU Address/Data Bus Line 15            |

| AD16   | D7  | I/O       | PUC                     | EBU Address/Data Bus Line 16            |

| AD17   | B5  | I/O       | PUC                     | EBU Address/Data Bus Line 17            |

| AD18   | A4  | I/O       | PUC                     | EBU Address/Data Bus Line 18            |

| AD19   | B4  | I/O       | PUC                     | EBU Address/Data Bus Line 19            |

| AD20   | C4  | I/O       | PUC                     | EBU Address/Data Bus Line 20            |

| AD21   | B3  | I/O       | PUC                     | EBU Address/Data Bus Line 21            |

| AD22   | B2  | I/O       | PUC                     | EBU Address/Data Bus Line 22            |

| AD23   | B1  | I/O       | PUC                     | EBU Address/Data Bus Line 23            |

| AD24   | C1  | I/O       | PUC                     | EBU Address/Data Bus Line 24            |

| AD25   | D3  | I/O       | PUC                     | EBU Address/Data Bus Line 25            |

| AD26   | E2  | I/O       | PUC                     | EBU Address/Data Bus Line 26            |

| AD27   | F2  | I/O       | PUC                     | EBU Address/Data Bus Line 27            |

| AD28   | F4  | I/O       | PUC                     | EBU Address/Data Bus Line 28            |

| AD29   | G4  | I/O       | PUC                     | EBU Address/Data Bus Line 29            |

| AD30   | H3  | I/O       | PUC                     | EBU Address/Data Bus Line 30            |

| AD31   | G2  | I/O       | PUC                     | EBU Address/Data Bus Line 31            |

| BC0    | A5  | 0         | PUC                     | EBU Byte Control Line 0                 |

| BC1    | A6  | 0         | PUC                     | EBU Byte Control Line 1                 |

| BC2    | B7  | 0         | PUC                     | EBU Byte Control Line 2                 |

| BC3    | A7  | 0         | PUC                     | EBU Byte Control Line 3                 |

**Table 2-1 Pin Definitions and Functions** (cont'd)

| Symbol                          | Pin        | In<br>Out | PU/<br>PD <sup>1)</sup> | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------|------------|-----------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                 |            |           |                         | EBU Address Bus Input/Output Lines                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| A0                              | K1         | 0         | PUC                     | EBU Address Bus Line 0                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A1                              | L1         | 0         | PUC                     | EBU Address Bus Line 1                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A2                              | M1         | 0         | PUC                     | EBU Address Bus Line 2                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <b>A3</b>                       | N1         | 0         | PUC                     | EBU Address Bus Line 3                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <b>A4</b>                       | P1         | 0         | PUC                     | EBU Address Bus Line 4                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

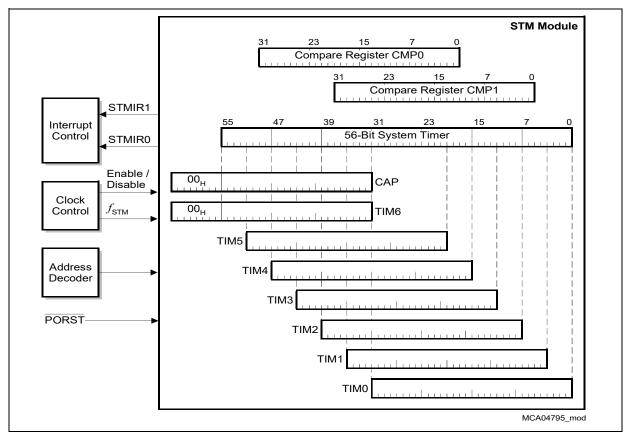

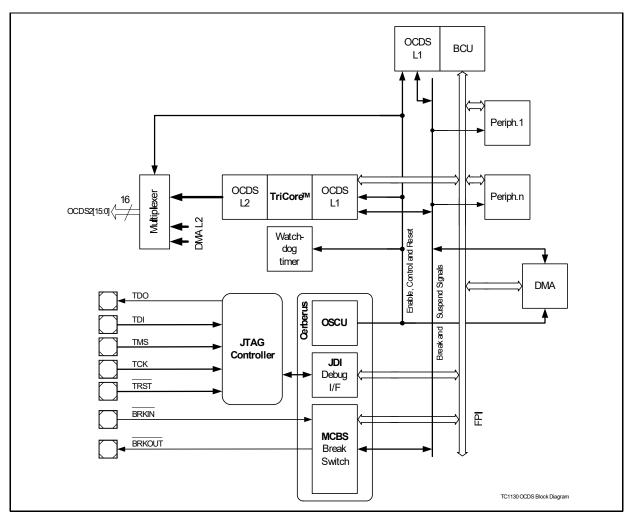

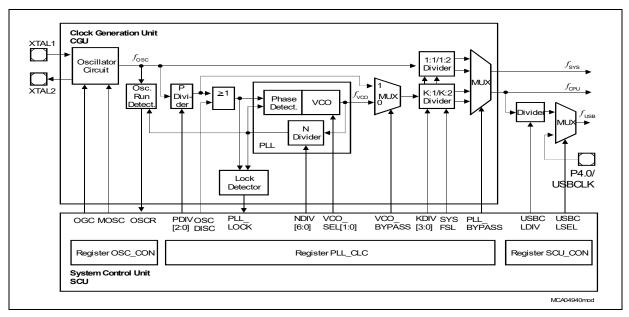

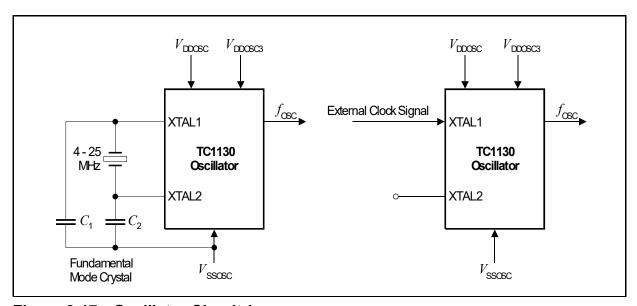

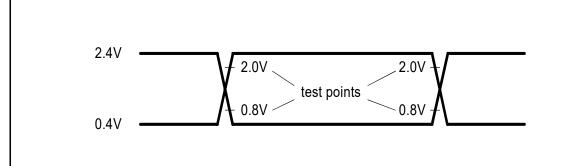

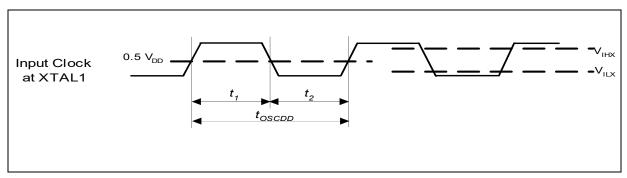

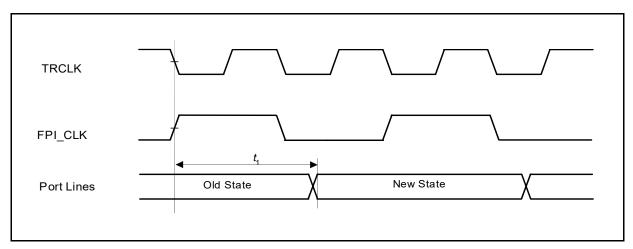

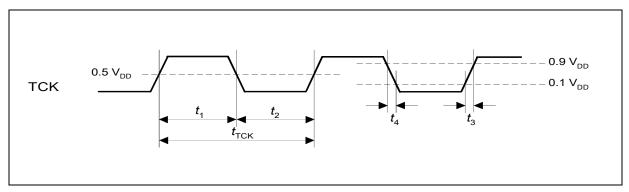

| A5                              | J2         | 0         | PUC                     | EBU Address Bus Line 5                                                                                                                                                                                                                                                                                                                                                                                                                                                         |