# Dual-Mode, Ka Band Upconverter with Integrated Fractional-N PLL and VCO

**Data Sheet**

# ADMV4530

### FEATURES

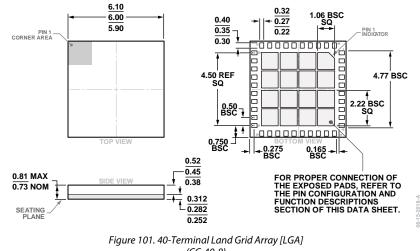

RF output frequency range: 27 GHz to 31 GHz Two upconversion modes Direct upconversion from differential baseband I/Q (I/Q mode) Single upper sideband upconversion (IF mode) 1 dB bandwidth: 500 MHz (I/Q mode) Input frequency range: 2 GHz to 3 GHz (IF mode) Matched, 50 Ω, single-ended RF output Matched, 50 Ω, single-ended IF input Programmable baseband I/Q common mode-voltage Sideband rejection and carrier feedthrough optimization Combined RF and IF gain dynamic range: 70 dB Programmable automatic IF gain control Programmable via 3-wire or 4-wire SPI 40-terminal, 6 mm × 6 mm, RoHS compliant LGA

#### **APPLICATIONS**

Satellite communication Point to point microwave communication

#### **GENERAL DESCRIPTION**

The ADMV4530 is a highly integrated upconverter with an inphase/quadrature (I/Q) mixer that is ideally suited for next generation Ka band satellite communications.

An integrated low phase noise, fractional-N phase-locked loop (PLL) with a voltage controlled oscillator (VCO) and internal 2× multiplier generate the necessary on-chip local oscillator (LO) signal for the I/Q mixer, eliminating the need for external frequency synthesis. The VCO uses an internal autocalibration routine that allows the PLL to select the necessary settings and locks in approximately 100 µs.

The single-ended reference input to the PLL operates up to 500 MHz and features internal reference dividers and a multiplier for added flexibility. Additionally, the phase frequency detector (PFD) comparison frequency can be up to 250 MHz for integer mode and 160 MHz for fraction-N mode.

The upconverter consists of an I/Q mixer that can operate in either I/Q mode with 500 MHz of bandwidth or in IF mode up to 3 GHz of bandwidth, which allows various radio architectures and backward compatibility with legacy systems.

Immediately following the I/Q mixer are stages of gain and variable attenuation. The configuration can achieve a minimum 1 dB compression point (P1dB) compression point of 19 dBm, eliminating the need for external stages of gain.

A programmable 4-wire serial port interface (SPI) allows adjustment of the quadrature phase for optimum sideband suppression. In addition, the SPI allows nulling of LO feedthrough in IF mode. In I/Q mode, the LO feedthrough can be nulled by applying external dc offset to the differential baseband I/Q inputs.

An IF automatic gain control (AGC) adjusts the IF variable gain amplifier (VGA) to compensate for input power variations. During normal operation, this AGC feature can be enabled or disabled via the SPI. When disabled during normal operation, the AGC feature only works on a test tone during power-down mode to track temperature variations.

The ADMV4530 upconverter comes in a RoHs compliant, 6 mm  $\times$  6 mm, 40-terminal land grid array (LGA) package. The ADMV4530 operates over the -40°C to +85°C case temperature range.

Rev. A

#### **Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2020 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

## **TABLE OF CONTENTS**

| Features 1                                    |

|-----------------------------------------------|

| Applications                                  |

| General Description                           |

| Revision History                              |

| Functional Block Diagram                      |

| Specifications                                |

| I/Q Mode 5                                    |

| IF Mode6                                      |

| Absolute Maximum Ratings 7                    |

| Thermal Resistance                            |

| ESD Caution7                                  |

| Pin Configuration and Function Descriptions   |

| Typical Performance Characteristics           |

| I/Q Mode                                      |

| IF Mode15                                     |

| Return Loss and Leakages                      |

| VCO and PLL22                                 |

| Upconverter M $\times$ N Spurious Performance |

| Theory of Operation                           |

| SPI Configuration                             |

| Register Map Sections27                       |

| Double Buffered Registers27                   |

| Start-Up Initialization Sequence27            |

| Frequency Update Sequence                     |

| Reference Input                               |

| N Counter                                     |

| INT, FRAC, MOD, and R Counter Relationship    |

| INT N Mode29                                  |

| Phase Frequency Detector and Charge Pump      |

| Loop Filter                                   |

### **REVISION HISTORY**

| 3/2020—Rev. 0 to Rev. A     |

|-----------------------------|

| Change to Data Sheet Title1 |

3/2020—Revision 0: Initial Version

| Charge Pump Current Setup 3           | 0 |

|---------------------------------------|---|

| Bleed Current (CP_BLEED) Setup        | 0 |

| MUXOUT                                | 1 |

| Digital Lock Detect 3                 | 1 |

| VCO Autocalibration                   | 1 |

| VCO Calibration Data Read Back 3      | 1 |

| VCO Calibration Data Manual Writing 3 | 1 |

| Autocalibration Lock Time 3           | 2 |

| Synthesizer Lock Timeout 3            | 2 |

| VCO Band Selection Time 3             | 2 |

| PLL Settling Time 3                   | 2 |

| Chip Temperature Read Back 3          | 2 |

| RF Output Driver                      | 3 |

| I/Q Mode Mixer Setup 3                | 3 |

| I/Q Mode LO Nulling                   | 3 |

| I/Q Mode Sideband Rejection Nulling   | 3 |

| IF Gain Control 3                     | 3 |

| IF Mode Mixer Setup 3                 | 3 |

| IF Mode LO Nulling 3                  | 4 |

| IF Mode Sideband Rejection Nulling 3  | 4 |

| Applications Information              | 5 |

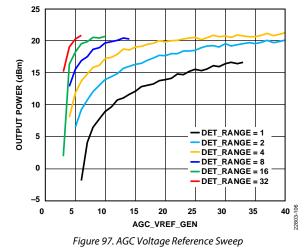

| IF AGC Configuration                  | 5 |

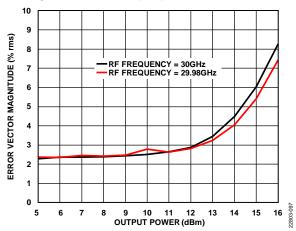

| Error Vector Magnitude Performance    | 5 |

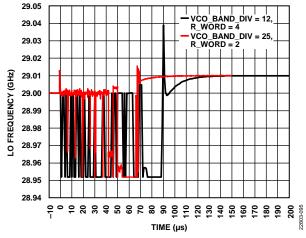

| PLL Lock Time in IF and I/Q Mode      | 6 |

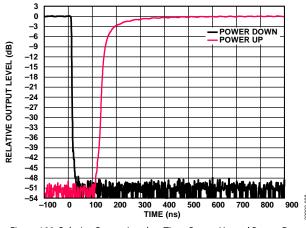

| Power Up and Down 3                   | 6 |

| Register Summary 3                    | 7 |

| Register Details 3                    | 9 |

| Outline Dimensions                    | 9 |

| Ordering Guide 5                      | 9 |

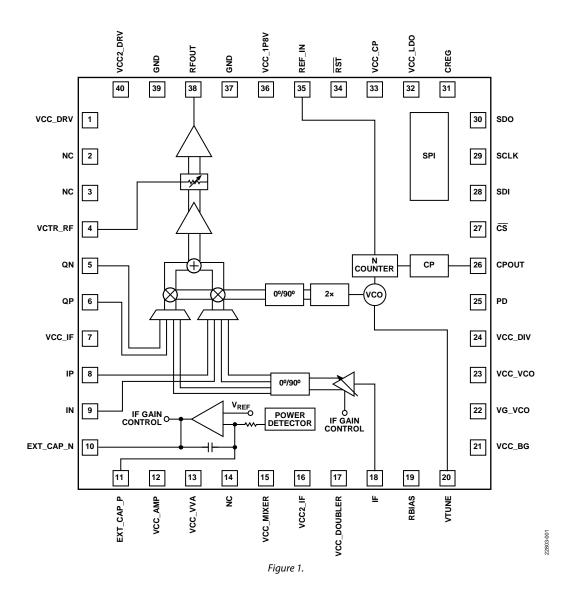

# FUNCTIONAL BLOCK DIAGRAM

## **SPECIFICATIONS**

$VCC\_DRV = VCC\_AMP = VCC2\_DRV = 4 V, VCC\_IF = VCC2\_IF = VCC\_VVA = VCC\_MIXER = VCC\_DOUBLER = VCC\_VCO = VCC\_DIV = VCC\_LDO = VCC\_CP = 3.3 V, VCC\_IP8V = 1.8 V, and T_A = 25^{\circ}C, unless otherwise noted.$

| Table 1. Parameter                     | Min  | Тур  | Max | Unit   | Test Conditions/Comments              |

|----------------------------------------|------|------|-----|--------|---------------------------------------|

| LO FREQUENCY RANGE                     | 25.6 | 19P  | 30  | GHz    |                                       |

| VCO                                    | 2010 |      |     | 0      |                                       |

| Frequency Range                        | 12.8 |      | 15  | GHz    |                                       |

| Voltage Range (V <sub>TUNE</sub> )     | 0.5  |      | 2.8 | V      |                                       |

| Tuning Sensitivity (K <sub>vco</sub> ) |      | 165  |     | MHz/V  | At VCO frequency                      |

| Open-Loop Phase Noise                  |      |      |     |        |                                       |

| 1 kHz Offset                           |      | -49  |     | dBc/Hz |                                       |

| 10 kHz Offset                          |      | -76  |     | dBc/Hz |                                       |

| 100 kHz Offset                         |      | -102 |     | dBc/Hz |                                       |

| 1 MHz Offset                           |      | -125 |     | dBc/Hz |                                       |

| 10 MHz Offset                          |      | -145 |     | dBc/Hz |                                       |

| 40 MHz Offset                          |      | -150 |     | dBc/Hz |                                       |

| PLL                                    |      |      |     |        |                                       |

| Reference Input                        |      |      |     |        |                                       |

| Voltage                                | 0    |      | 1.8 | V p-p  |                                       |

| Capacitance                            |      | 7    |     | pF     |                                       |

| Reference Frequency                    |      | 200  |     | MHz    |                                       |

| PFD Frequency                          |      |      |     |        |                                       |

| Integer Mode                           |      | 250  |     | MHz    |                                       |

| Fractional-N Mode                      |      | 160  |     | MHz    |                                       |

| PFD In Band Phase Noise                |      | -147 |     | dBc/Hz | PFD frequency ( $f_{PFD}$ ) = 200 MHz |

| Lock Detect                            |      |      |     |        |                                       |

| Locked                                 |      |      | 3.3 | V      |                                       |

| Unlocked                               | 0.1  | 0.3  | 0.5 | V      |                                       |

### I/Q MODE

I/Q frequency = 25 MHz, I/Q input power = -10 dBm, RF frequency = 29 GHz, 1 MHz tone spacing, upper sideband, R\_WORD = 2, CP\_CURRENT = 4.20 mA, REF\_IN power = 8 dBm, REF\_IN frequency = 200 MHz, loop filter bandwidth = 540 kHz, VCC\_DRV = VCC\_AMP = VCC2\_DRV = 4 V, VCC\_IF = VCC2\_IF = VCC\_VVA = VCC\_MIXER = VCC\_DOUBLER = VCC\_VCO = VCC\_DIV = VCC\_LDO = VCC\_CP = 3.3 V, VCC\_IP8V = 1.8 V, T\_A = 25°C, common-mode voltage (V<sub>CM</sub>) = 0.5 V, VCTR\_RF = 1.8 V, and board losses de-embedded to the device, unless otherwise noted.

| Table 2.                                   |     |      |     |        |                                                                                                      |

|--------------------------------------------|-----|------|-----|--------|------------------------------------------------------------------------------------------------------|

| Parameter                                  | Min | Тур  | Max | Unit   | Test Conditions/Comments                                                                             |

| OUTPUT FREQUENCY RANGE                     | 27  |      | 31  | GHz    |                                                                                                      |

| OUTPUT RETURN LOSS                         |     | -4   |     | dB     |                                                                                                      |

| RF GAIN                                    | 17  | 21   |     | dB     |                                                                                                      |

| Flatness                                   |     | ±1   |     | dB     |                                                                                                      |

| Dynamic Range                              |     | 30   |     | dB     |                                                                                                      |

| VCTR_RF Control                            |     |      |     |        |                                                                                                      |

| Range                                      | 0   |      | 1.8 | V      |                                                                                                      |

| Slope                                      |     | 32   |     | dB/V   | VCTR_RF = 0.6 V to 1.5 V                                                                             |

| 1 dB COMPRESSION POINT (P1dB)              | 17  | 19   |     | dBm    | Maximum gain                                                                                         |

| OUTPUT THIRD-ORDER DISTORTION (IP3)        |     | 29   |     | dBm    | Maximum gain, –10 dBm per tone, 1 MHz tone spacing                                                   |

| NOISE DENSITY                              |     | -139 |     | dBm/Hz | Maximum gain                                                                                         |

| OUTPUT SPURIOUS                            |     |      |     |        | Spurs at maximum gain                                                                                |

| Reference Spurs                            |     | -65  |     | dBm    |                                                                                                      |

| VCO Feedthrough                            |     | -75  |     | dBm    |                                                                                                      |

| 1 dB BANDWIDTH                             |     | 500  |     | MHz    | Per differential I and Q inputs                                                                      |

| I/Q COMMON-MODE VOLTAGE (V <sub>CM</sub> ) | 0   | 0.5  | 2.5 | V      |                                                                                                      |

| DIFFERENTIAL INPUT IMPEDANCE               |     | 100  |     | Ω      |                                                                                                      |

| SIDEBAND REJECTION                         |     | -27  |     | dBc    | Uncalibrated                                                                                         |

| LO TO RF LEAKAGE                           |     |      |     |        |                                                                                                      |

| Minimum Gain                               |     | -41  |     | dBm    | Uncalibrated                                                                                         |

| Maximum Gain                               |     | -15  |     | dBm    | Uncalibrated                                                                                         |

|                                            |     | -45  |     | dBm    | Calibrated                                                                                           |

| SUPPLY VOLTAGE                             |     |      |     |        |                                                                                                      |

|                                            | 3.8 | 4.0  | 4.2 | V      | VCC_DRV, VCC_AMP, and VCC2_DRV pins                                                                  |

|                                            | 3.2 | 3.3  | 3.4 | V      | VCC_IF, VCC2_IF, VCC_VVA, VCC_MIXER, VCC_DOUBLER, VCC_BG, VCC_VCO, VCC_DIV, VCC_LDO, and VCC_CP pins |

|                                            | 1.7 | 1.8  | 1.9 | V      | VCC_1P8V                                                                                             |

| SUPPLY CURRENT                             |     |      |     |        |                                                                                                      |

|                                            |     | 200  |     | mA     | VCC_DRV, VCC_AMP, and VCC2_DRV pins                                                                  |

|                                            |     | 320  |     | mA     | VCC_IF, VCC2_IF, VCC_VVA, VCC_MIXER, VCC_DOUBLER, VCC_BG, VCC_VCO, VCC_DIV, VCC_LDO, and VCC_CP pins |

|                                            |     | 2    |     | mA     | VCC_1P8V                                                                                             |

#### IF MODE

IF frequency = 2.7 GHz, IF power = -41 dBm, RF frequency = 29 GHz, 1 MHz tone spacing, upper sideband, R\_WORD = 4, CP\_CURRENT = 2.10 mA, REF\_IN power = 8 dBm, REF\_IN frequency = 200 MHz, loop filter bandwidth = 100 kHz, VCC\_DRV = VCC\_AMP = VCC2\_DRV = 4 V, VCC\_IF = VCC2\_IF = VCC\_VVA = VCC\_MIXER = VCC\_DOUBLER = VCC\_VCO = VCC\_DIV = VCC\_LDO = VCC\_CP = 3.3 V, VCC\_IP8V = 1.8 V, T<sub>A</sub> = 25°C, VCTR\_RF = 1.8 V, VCTR\_IF = 0 V, and board losses de-embedded to the device, unless otherwise noted. Note that VCTR\_IF is the voltage applied to the EXT\_CAP\_x pins.

| Table 3.               |     |      |     |        |                                                                                                      |  |  |

|------------------------|-----|------|-----|--------|------------------------------------------------------------------------------------------------------|--|--|

| Parameter              | Min | Тур  | Max | Unit   | Test Conditions/Comments                                                                             |  |  |

| OUTPUT FREQUENCY RANGE | 28  |      | 30  | GHz    |                                                                                                      |  |  |

| OUTPUT RETURN LOSS     |     | -4   |     | dB     |                                                                                                      |  |  |

| GAIN                   |     | 50   |     | dB     | VCTR_IF = 0 V                                                                                        |  |  |

| Flatness               |     | 0.25 |     | dB     | Within a bandwidth of 50 MHz                                                                         |  |  |

| Dynamic Range          |     | 70   |     | dB     | VCTR_RF and VCTR_IF combined dynamic range                                                           |  |  |

| VCTR_RF Control        |     |      |     |        |                                                                                                      |  |  |

| Range                  | 0   |      | 1.8 | V      |                                                                                                      |  |  |

| Slope                  |     | 32   |     | dB/V   | VCTR_RF = 0.6 V to 1.5 V                                                                             |  |  |

| VCTR_IF Control        |     |      |     |        |                                                                                                      |  |  |

| AGC Set Voltage        | 0   |      | 2.5 | V      | Accessed via SPI map                                                                                 |  |  |

| Range                  | 0   |      | 3.3 | V      | When bypassing AGC                                                                                   |  |  |

| Slope                  |     | -32  |     | dB/V   | VCTR_IF = 0.9 V to 2.2 V for both AGC or external                                                    |  |  |

| ·                      |     |      |     |        | control voltage                                                                                      |  |  |

| P1dB                   | 17  | 19   |     | dBm    | Maximum gain                                                                                         |  |  |

| OUTPUT IP3             |     | 29   |     | dBm    | Maximum gain, -41 dBm per tone, 1 MHz tone spacing                                                   |  |  |

| NOISE DENSITY          |     | -139 |     | dBm/Hz | Maximum gain                                                                                         |  |  |

| OUTPUT SPURIOUS        |     |      |     |        | Spurs at maximum gain                                                                                |  |  |

| Reference Spurs        |     | -65  |     | dBm    |                                                                                                      |  |  |

| VCO Feedthrough        |     | -75  |     | dBm    |                                                                                                      |  |  |

| LO TO RF LEAKAGE       |     | -10  |     | dBm    | Uncalibrated                                                                                         |  |  |

|                        |     | -35  |     | dBm    | Calibrated                                                                                           |  |  |

| SIDEBAND REJECTION     | -24 | -35  |     | dBc    | Uncalibrated                                                                                         |  |  |

| INPUT RANGE            |     |      |     |        |                                                                                                      |  |  |

| Frequency              | 2   | 2.5  | 3   | GHz    |                                                                                                      |  |  |

| Power                  |     |      | 0   | dBm    |                                                                                                      |  |  |

| INPUT RETURN LOSS      |     | 12   |     | dB     |                                                                                                      |  |  |

| SUPPLY VOLTAGE         |     |      |     |        |                                                                                                      |  |  |

|                        | 3.8 | 4.0  | 4.2 | V      | VCC_DRV, VCC_AMP, and VCC2_DRV pins                                                                  |  |  |

|                        | 3.2 | 3.3  | 3.4 | v      | VCC_IF, VCC2_IF, VCC_VVA, VCC_MIXER, VCC_DOUBLER,                                                    |  |  |

|                        |     |      |     |        | VCC_BG, VCC_VCO, VCC_DIV, VCC_LDO, and VCC_CP pins                                                   |  |  |

|                        | 1.7 | 1.8  | 1.9 | V      | VCC_1P8V                                                                                             |  |  |

| SUPPLY CURRENT         |     |      |     |        |                                                                                                      |  |  |

|                        |     | 190  |     | mA     | VCC_DRV, VCC_AMP, and VCC2_DRV pins                                                                  |  |  |

|                        |     | 470  |     | mA     | VCC_IF, VCC2_IF, VCC_VVA, VCC_MIXER, VCC_DOUBLER, VCC_BG, VCC_VCO, VCC_DIV, VCC_LDO, and VCC_CP pins |  |  |

|                        |     | 2    |     | mA     | VCC_1P8V                                                                                             |  |  |

#### Rev. A | Page 6 of 59

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 4.

| 1 abic 4.                                      |                       |

|------------------------------------------------|-----------------------|

| Parameter                                      | Rating                |

| VCC_DRV, VCC_AMP, and VCC2_DRV                 | 5 V                   |

| VCC_IF, VCC2_IF, VCC_VVA, VCC_MIXER,           | 4.3 V                 |

| VCC_DOUBLER, VCC_BG                            |                       |

| VCC_VCO, VCC_DIV, VCC_LDO, VCC_CP              | 3.6 V                 |

| VCC_1P8V                                       | 2.3 V                 |

| REF_IN to GND                                  | –0.3 V to +2.1 V      |

| Input Power                                    |                       |

| IF                                             | 10 dBm                |

| I/Q                                            | 5 dBm                 |

| Temperature                                    |                       |

| Junction                                       | 125°C                 |

| Lifetime at Maximum Junction (T <sub>J</sub> ) | 10 <sup>6</sup> hours |

| Operating Range                                | –40°C to +85°C        |

| Storage Range                                  | –55°C to +150°C       |

| Lead Range (Soldering 60 sec)                  | 260°C                 |

| Moisture Sensitivity Level (MSL) Rating        | MSL3                  |

| Electrostatic Discharge (ESD) Sensitivity      |                       |

| Human Body Model (HBM)                         | 1000 V                |

| Field Induced Charged Device                   | 1000 V                |

| Model (FICDM)                                  |                       |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.  $\theta_{JC}$  is the junction to case thermal resistance.

Only use  $\theta_{JA}$  and  $\theta_{JC}$  to compare the thermal performance of different packages when all test conditions listed are similar to JEDEC specifications. Otherwise, use  $\Psi_{JT}$  and  $\Psi_{JB}$  to calculate the device junction temperature using the following equations:

$$T_J = (P \times \Psi_{JT}) + T_{TOP} \tag{1}$$

where:

*P* is the total power dissipation in the chip (W).  $\Psi_{JT}$  is the junction to top thermal characterization number.

$T_{TOP}$  is package top temperature (°C).  $T_{TOP}$  is measured at the top center of the package.

$$T_J = (P \times \Psi_{JB}) + T_{BOARD} \tag{2}$$

where:

*P* is the total power dissipation in the chip (W).

$\Psi_{JB}$  is the junction to board thermal characterization number.  $T_{BOARD}$  is the board temperature measured on the midpoint of the longest side of the package, no more than 1 mm from the edge of the package body (°C).

As stated in JEDEC51-12, only use Equation 1 and Equation 2 when no heat sink or heat spreader is present. When a heat sink or heat spreader is added, use  $\theta_{JC\_TOP}$  or  $\theta_{JC\_BOT}$  to estimate or calculate the junction temperature.

#### Table 5. Thermal Resistance

| Package Type | $\boldsymbol{\theta}_{JC_BOT}^1$ | $\boldsymbol{\theta}_{JC_{TOP}}^{1}$ | Ψл  | $\Psi_{JB}$ | θ」   | Unit |

|--------------|----------------------------------|--------------------------------------|-----|-------------|------|------|

| CC-40-8      | 5.9                              | 12.8                                 | 3.0 | 8.5         | 28.2 | °C/W |

<sup>1</sup> See JEDEC Standard JESD51-2 for additional information on optimizing the thermal impedance.

#### ESD CAUTION

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

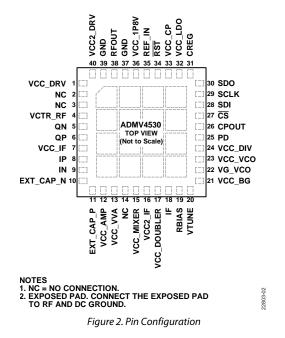

### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

#### **Table 6. Pin Function Descriptions**

| Pin No.    | Mnemonic                      | Description                                                                                                                                                                                                                           |

|------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 12, 40  | VCC_DRV, VCC_AMP,<br>VCC2_DRV | Supply Voltages for the RF Output Driver, 4.0 V. Place a 1 $\mu$ F decoupling capacitor close to each pin.                                                                                                                            |

| 2, 3, 14   | NC                            | No Connection.                                                                                                                                                                                                                        |

| 4          | VCTR_RF                       | RF Gain Control, 0 V to 1.8 V.                                                                                                                                                                                                        |

| 5, 6, 8, 9 | QN, QP, IP, IN                | Differential Quadrature Baseband Inputs. These 50 $\Omega$ differential impedance inputs can be common-mode dc biased from 0 V to 2.5 V.                                                                                              |

| 7, 16      | VCC_IF, VCC2_IF               | Supply Voltages for the IF and Baseband Inputs, 3.3 V. Place a 1 $\mu$ F decoupling capacitor close to each pin.                                                                                                                      |

| 10         | EXT_CAP_N                     | IF Gain Control Capacitor Negative Terminal. To adjust the IF gain manually, this pin must be driven externally when the AGC functionality is disabled, 0 V to 3.3 V. Note that VCTR_IF is the voltage applied to the EXT_CAP_x pins. |

| 11         | EXT_CAP_P                     | IF Gain Control Capacitor Positive Terminal. Note that VCTR_IF is the voltage applied to the EXT_CAP_x pins.                                                                                                                          |

| 13         | VCC_VVA                       | Supply Voltage for the Variable Gain Amplifier, 1.8 V. Place a 1 µF decoupling capacitor close to this pin.                                                                                                                           |

| 15         | VCC_MIXER                     | Supply Voltage for the Mixer, 3.3 V. Place a 1 µF decoupling capacitor close to this pin.                                                                                                                                             |

| 17         | VCC_DOUBLER                   | Supply Voltage for the Internal 2× Multiplier, 3.3 V. Place a 1 $\mu$ F decoupling capacitor close to this pin.                                                                                                                       |

| 18         | IF                            | IF Input. This pin has a 50 $\Omega$ input impedance.                                                                                                                                                                                 |

| 19         | RBIAS                         | Resistor Band Gap Reference Bias. Place a precision 680 $\Omega$ resistor to ground at this pin.                                                                                                                                      |

| 20         | VTUNE                         | VCO Tune Port, 0.5 V to 2.8 V. This pin is driven by the output of the loop filter.                                                                                                                                                   |

| 21         | VCC_BG                        | Supply Voltage for the Internal Band Gap, 3.3 V. Place a 1 µF decoupling capacitor close to this pin.                                                                                                                                 |

| 22         | VG_VCO                        | VCO Gate Decoupling. Place a 10 $\mu$ F decoupling capacitor at this pin.                                                                                                                                                             |

| 23         | VCC_VCO                       | Supply Voltage for the VCO, 3.3 V. Place a 1 $\mu$ F decoupling capacitor close to this pin.                                                                                                                                          |

| 24         | VCC_DIV                       | Supply Voltage for Fractional-N PLL, 3.3 V. Place a 1 µF decoupling capacitor close to this pin.                                                                                                                                      |

| Pin No. | Mnemonic | Description                                                                                                                                                                        |

|---------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25      | PD       | Power-Down, 3.3 V Logic. Active high.                                                                                                                                              |

| 26      | CPOUT    | Charge Pump Output. Connect this pin to VTUNE (Pin 20) through the loop filter.                                                                                                    |

| 27      | CS       | SPI Chip Select. 3.3 V logic. Active low.                                                                                                                                          |

| 28      | SDI      | SPI Data Input. 3.3 V logic.                                                                                                                                                       |

| 29      | SCLK     | SPI Clock. 3.3 V logic.                                                                                                                                                            |

| 30      | SDO      | SPI Data Output. 3.3 V logic.                                                                                                                                                      |

| 31      | CREG     | External Capacitor for the Low Dropout (LDO) Regulator Output. Place a 0.1 $\mu$ F decoupling capacitor close to this pin.                                                         |

| 32      | VCC_LDO  | Supply Voltage for the Internal LDO Regulator, 3.3 V. Place a 1 $\mu\text{F}$ decoupling capacitor close to this pin.                                                              |

| 33      | VCC_CP   | Supply Voltage for the Charge Pump, 3.3 V. Place a 1 µF decoupling capacitor close to this pin.                                                                                    |

| 34      | RST      | Reset. 3.3 V logic. Active low.                                                                                                                                                    |

| 35      | REF_IN   | PLL Reference Input. Apply an external reference signal to this pin with a 0.01 $\mu$ F, dc blocking capacitor. Refer to Figure 91 for the external reference input configuration. |

| 36      | VCC_1P8V | Supply Voltage for the SPI Block, 1.8 V. Place a 1 µF decoupling capacitor close to this pin.                                                                                      |

| 37, 39  | GND      | Ground. Connect these pins to RF and dc ground.                                                                                                                                    |

| 38      | RFOUT    | RF Output. This pin has a 50 $\Omega$ output impedance.                                                                                                                            |

|         | EPAD     | Exposed Pad. Connect the exposed pad to RF and dc ground.                                                                                                                          |

T<sub>A</sub> = +85°C T<sub>A</sub> = +25°C T<sub>A</sub> = -40°C

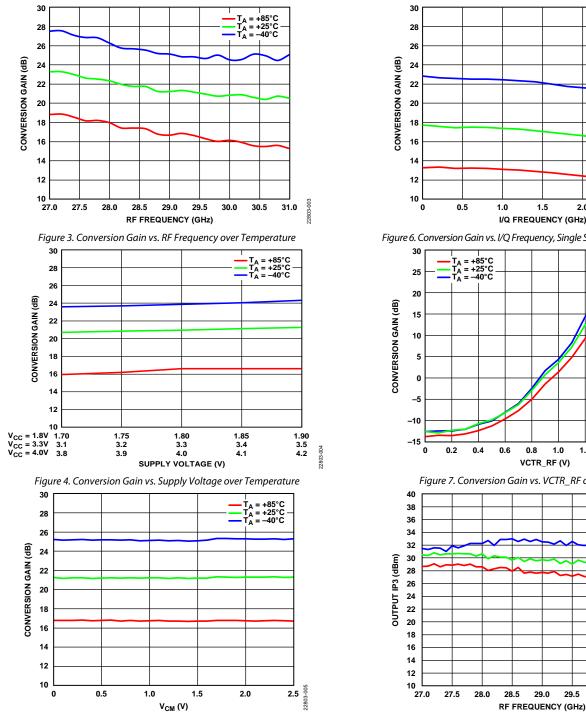

### TYPICAL PERFORMANCE CHARACTERISTICS I/Q MODE

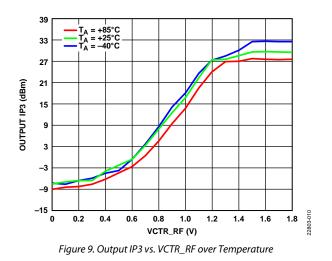

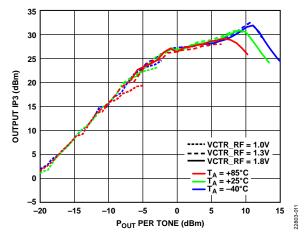

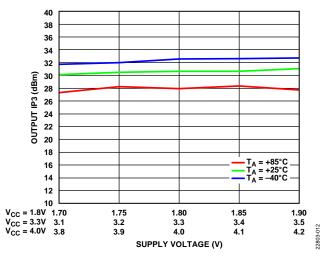

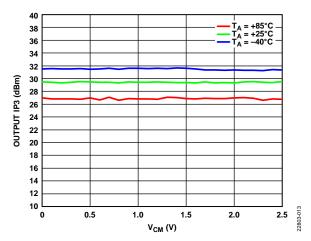

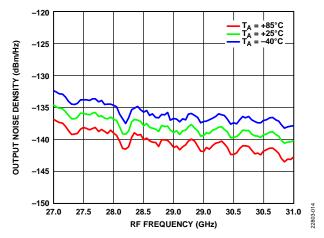

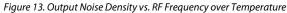

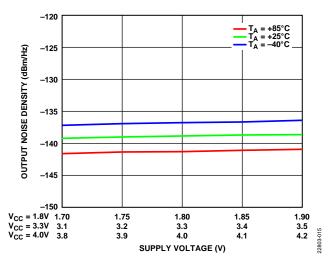

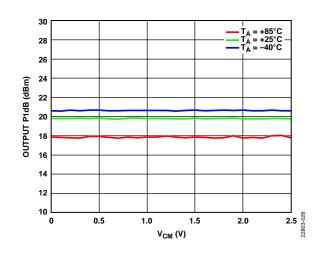

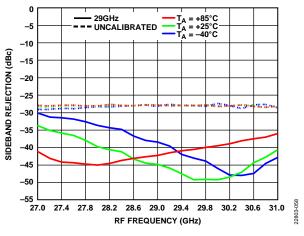

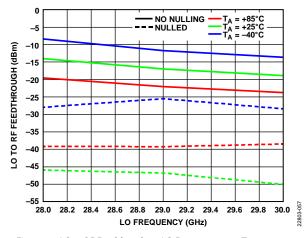

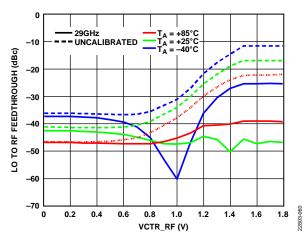

I/Q frequency = 25 MHz, I/Q input power = -10 dBm, RF frequency = 29 GHz, 1 MHz tone spacing, upper sideband, R\_WORD = 2, CP\_CURRENT = 4.20 mA, REF\_IN power = 8 dBm, REF\_IN frequency = 200 MHz, loop filter bandwidth = 540 kHz, VCC\_DRV = VCC\_AMP = VCC2\_DRV = 4 V, VCC\_IF = VCC2\_IF = VCC\_VVA = VCC\_MIXER = VCC\_DOUBLER = VCC\_VCO = VCC\_DIV = VCC\_LDO = VCC\_CP = 3.3 V, VCC\_1P8V = 1.8 V, T<sub>A</sub> = +25°C, -40°C, and +85°C, V<sub>CM</sub> = 0.5 V, VCTR\_RF = 1.8 V, and board losses de-embedded to the device, unless otherwise noted.

Figure 5. Conversion Gain vs. VCM over Temperature

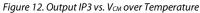

Figure 8. Output IP3 vs. RF Frequency over Temperature

30.0

30.5

2803-005

31.0

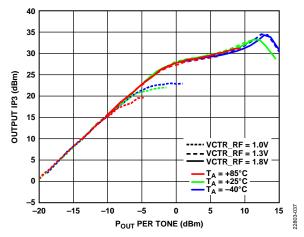

Figure 10. Output IP3 vs. Output Power (Pout) per Tone over Temperature

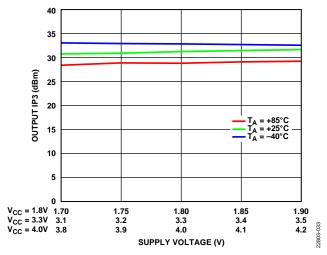

Figure 11. Output IP3 vs. Supply Voltage over Temperature

Figure 14. Output Noise Density vs. Supply Voltage over Temperature

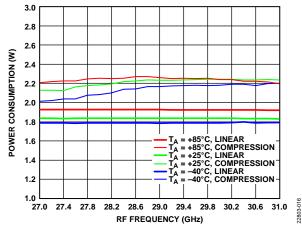

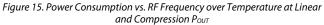

Figure 16. Power Consumption vs. POUT over Temperature

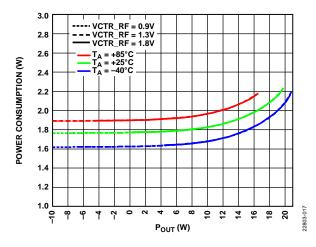

Figure 17. Output Noise Density vs. VCTR\_RF over Temperature

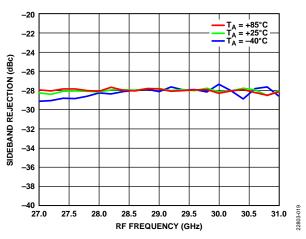

Figure 18. Sideband Rejection vs. RF Frequency over Temperature, Uncalibrated

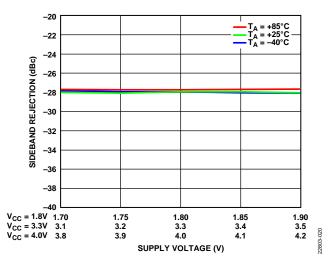

Figure 19. Sideband Rejection vs. Supply Voltage over Temperature, Uncalibrated

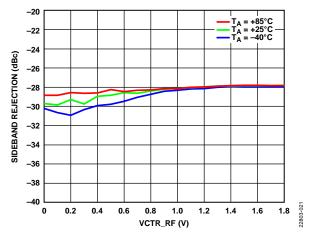

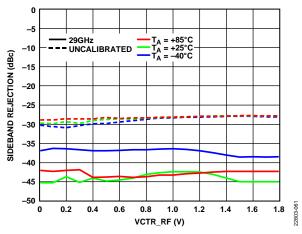

Figure 20. Sideband Rejection vs. VCTR\_RF over Temperature, Uncalibrated

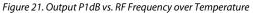

Figure 22. Output P1dB vs. Supply Voltage over Temperature

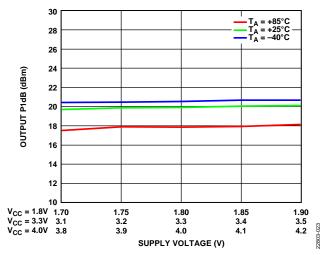

Figure 23. Sideband Rejection vs. V<sub>CM</sub> over Temperature, Uncalibrated

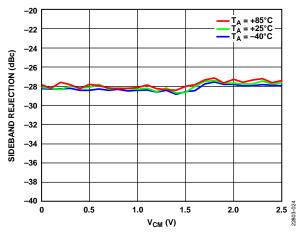

Figure 24. Output P1dB vs. VCTR\_RF over Temperature

Figure 25. Output P1dB vs.  $V_{CM}$  over Temperature

Figure 26. Sideband Rejection vs. RF Frequency over Temperature, Uncalibrated and Calibrated with RF Frequency = 29 GHz, VCTR\_RF = 1.8 V at  $T_A = 25$  °C, I/Q Mode

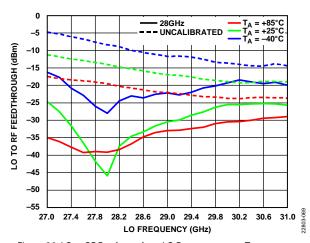

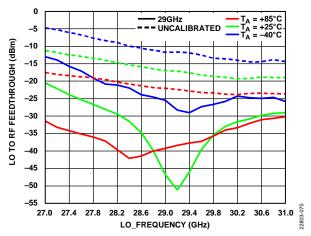

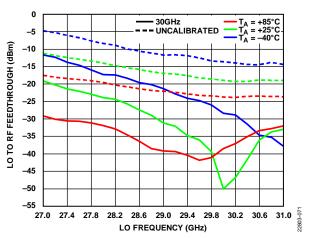

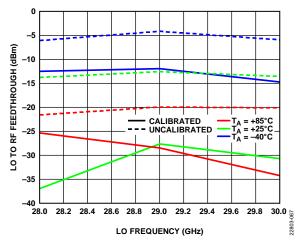

Figure 27. LO to RF Feedthrogh vs. LO Frequency over Temperature, Uncalibrated and Calibrated with LO Frequency = 28 GHz, 29 GHz, and 30 GHz, VCTR\_RF = 1.8 V at  $T_A = 25$ °C, I/Q Mode

Figure 28. LO to RF Feedthrogh vs. VCTR\_RF over Temperature, Uncalibrated and Calibrated with LO Frequency = 29 GHz at  $T_A = 25^{\circ}$ C, I/Q Mode

Figure 29. Sideband Rejection vs. VCTR\_RF over Temperature, Uncalibrated and Calibrated with RF Frequency = 29 GHz at  $T_A$  = 25°C, I/Q Mode

Figure 30. LO to RF Feethrough vs. LO Frequency, over Temperature, Not Calibrated and Calibrated with LO Frequency = 28 GHz at  $T_A = 25^{\circ}$ C, I/Q Mode

Figure 31. LO to RF Feethrough vs. LO Frequency, over Temperature, Not Calibrated and Calibrated with LO Frequency = 29 GHz at  $T_A = 25$  °C, I/Q Mode

Figure 32. LO to RF Feethrough vs. LO Frequency, over Temperature, Not Calibrated and Calibrated with LO Frequency = 30 GHz at  $T_A = 25 \degree$ C, I/Q Mode

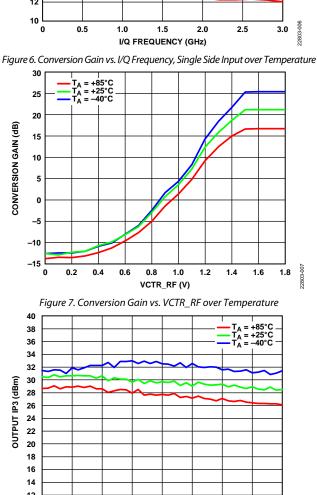

#### **IF MODE**

IF frequency = 2.7 GHz, IF power = -41 dBm, RF frequency = 29 GHz, 1 MHz tone spacing, upper sideband, R\_WORD = 4, CP\_CURRENT = 2.10 mA, REF\_IN power = 8 dBm, REF\_IN frequency = 200 MHz, loop filter bandwidth = 100 kHz, VCC\_DRV = VCC\_AMP = VCC2\_DRV = 4 V, VCC\_IF = VCC2\_IF = VCC\_VVA = VCC\_MIXER = VCC\_DOUBLER = VCC\_VCO = VCC\_DIV = VCC\_LDO = VCC\_CP = 3.3 V, VCC\_1P8V = 1.8 V, T<sub>A</sub> = +25°C, -40°C, and +85°C, VCTR\_RF = 1.8 V, VCTR\_IF = 0 V, and board losses de-embedded to the device, unless otherwise noted. Note that VCTR\_IF is the voltage applied to the EXT\_CAP\_x pins.

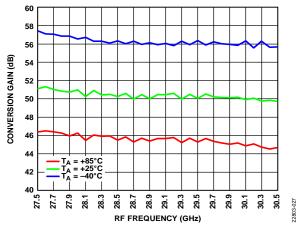

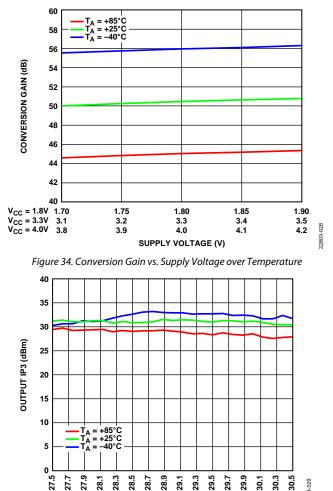

Figure 33. Conversion Gain vs. RF Frequency over Temperature

**RF FREQUENCY (GHz)** Figure 35. Output IP3 vs. RF Frequency over Temperature

30.1

22803-029

28.7

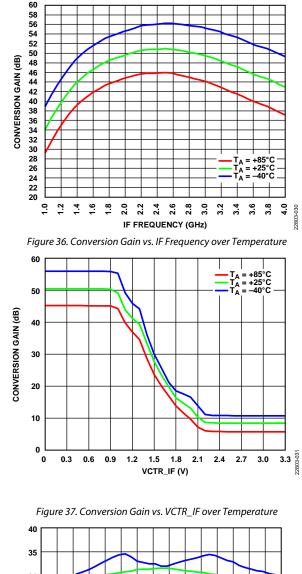

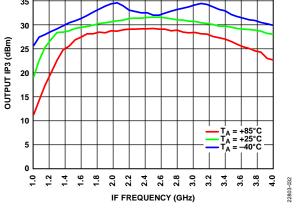

Figure 38. Output IP3 vs. IF Frequency over Temperature

Figure 39. Output IP3 vs. Supply Voltage over Temperature

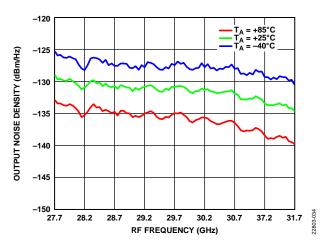

Figure 40. Output Noise Density vs. RF Frequency over Temperature

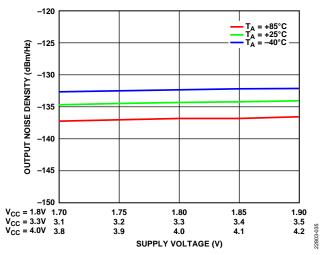

Figure 41. Output Noise Density vs. Supply Voltage over Temperature

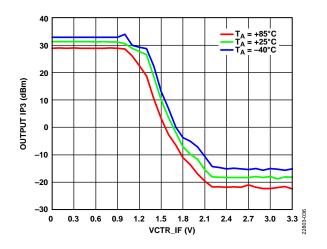

Figure 42. Output IP3 vs. VCTR\_IF over Temperature

Figure 43. Output IP3 vs. POUT per Tone over Temperature and VCTR\_RF

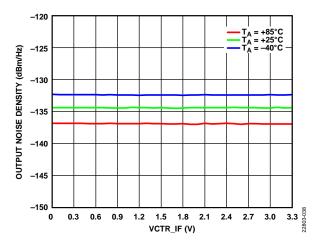

Figure 44. Output Noise Density vs. VCTR\_IF over Temperature

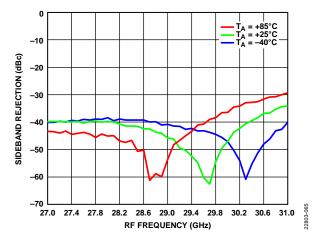

#### 0 T<sub>A</sub> = +85°C T<sub>A</sub> = +25°C T<sub>A</sub> = -40°C -10 SIDEBAND REJECTION (dBc) -20 -30 -40 -50 -60 -70 29.5 27.9 29.3 27.5 28.5 28.7 28.9 29.7 29.9 30.3 27.7 28.1 28.3 29.1 30.5 30.1 22803-039 **RF FREQUENCY (GHz)**

Figure 45. Sideband Rejection vs. RF Frequency over Temperature, Uncalibrated

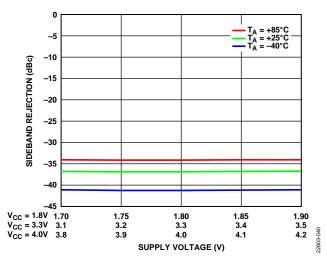

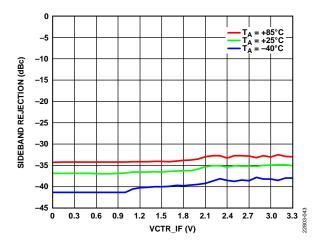

Figure 46. Sideband Rejection vs. Supply Voltage over Temperature, Uncalibrated

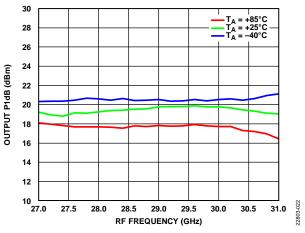

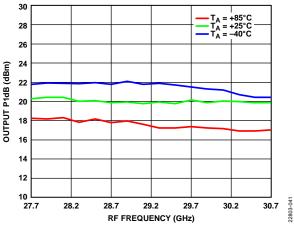

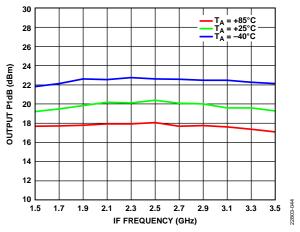

Figure 47. Output P1dB vs. RF Frequency over Temperature

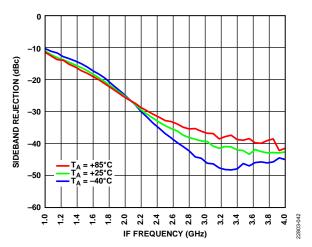

Figure 48. Sideband Rejection vs. IF Frequency over Temperature, Uncalibrated

Figure 49. Sideband Rejection vs. VCTR\_IF over Temperature, Uncalibrated

Figure 50. Output P1dB vs. IF Frequency over Temperature

#### Rev. A | Page 17 of 59

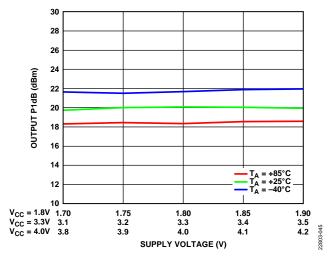

Figure 51. Output P1dB vs. Supply Voltage over Temperature

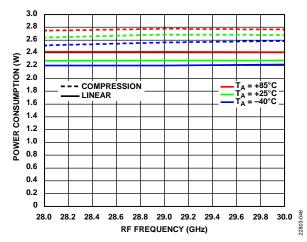

Figure 52. Power Consumption vs. RF Frequency over Temperature at Linear and Compression  $P_{OUT}$

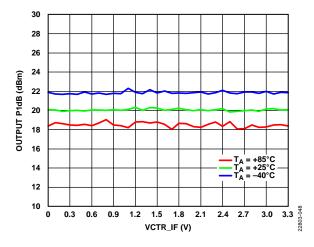

Figure 53. Output P1dB vs. VCTR\_IF over Temperature

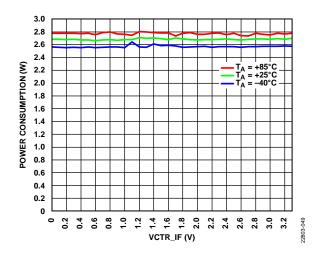

Figure 54. Power Consumption vs. VCTR\_IF over Temperature at Compression  $P_{OUT}$

Figure 55. Sideband Rejection vs. RF Frequency over Temperature, Calibrated with RF Frequency = 30 GHz, IF Mode, VCTR\_RF = 1.8 V,  $T_A = 25^{\circ}$ C

Figure 56. LO to RF Feethrough vs. LO Frequency, Calibrated at  $T_A = 25^{\circ}$ C and Not Calibrated, over Temperature

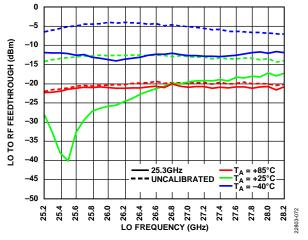

Figure 57. LO to RF Feethrough vs. LO Frequency, over Temperature, Not Calibrated and Calibrated with LO Frequency = 25.3 GHz at  $T_A = 25^{\circ}$ C, IF Mode

Figure 58. LO to RF Feethrough vs. LO Frequency, over Temperature, Not Calibrated and Calibrated with LO Frequency = 26.3 GHz at  $T_A = 25^{\circ}$ C, IF Mode

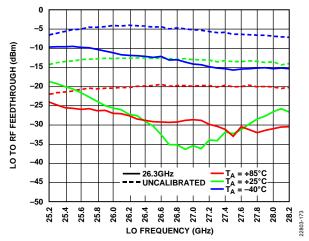

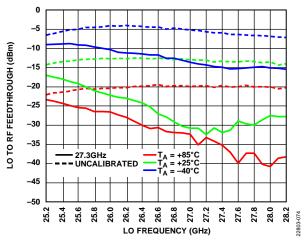

Figure 59. LO to RF Feethrough vs. LO Frequency, over Temperature, Not Calibrated and Calibrated with LO Frequency = 27.3 GHz at  $T_A = 25^{\circ}$ C, IF Mode

#### **RETURN LOSS AND LEAKAGES**

$VCC\_DRV = VCC\_AMP = VCC2\_DRV = 4 V, VCC\_IF = VCC2\_IF = VCC\_VVA = VCC\_MIXER = VCC\_DOUBLER = VCC\_VCO = VCC\_DIV = VCC\_LDO = VCC\_CP = 3.3 V, VCC\_1P8V = 1.8 V, T_A = +25^{\circ}C, -40^{\circ}C, and +85^{\circ}C, VCTR\_RF = 1.8 V, and VCTR\_IF = 0 V, unless otherwise noted.$

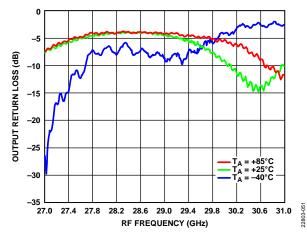

Figure 60. Output Return Loss vs. RF Frequency over Temperature

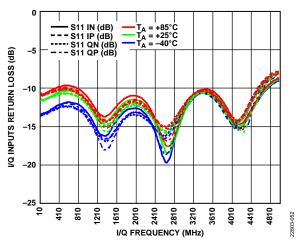

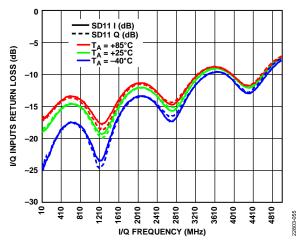

Figure 61. I/Q Inputs Return Loss vs. I/Q Frequency, Single-Ended over Temperature (S11 Is Return Loss)

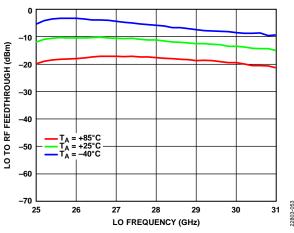

Figure 62. LO to RF Feedthrough vs. LO Frequency, Uncalibrated over Temperature

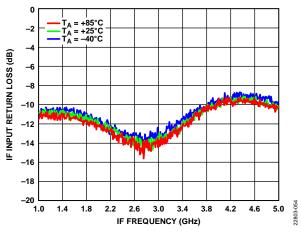

Figure 63. IF Input Return Loss vs. IF Frequency over Temperature

Figure 64. I/Q Inputs Return Loss vs. I/Q Frequency, Differential over Temperature (SD11 Is Differential Return Loss)

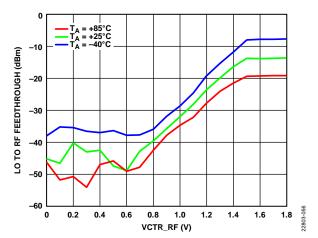

Figure 65. LO to RF Feedthrough vs. VCTR\_RF, Uncalibrated over Temperature, LO Frequency = 29 GHz

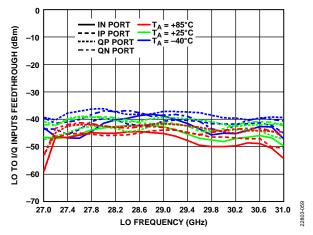

Figure 66. LO to I/Q Inputs Feedthrough vs. LO Frequency, Uncalibrated over Temperature

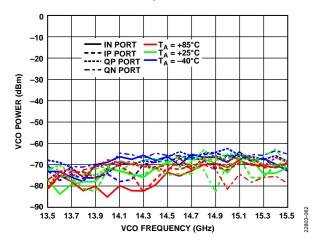

Figure 67. VCO Power vs. VCO Frequency over Temperature, Uncalibrated

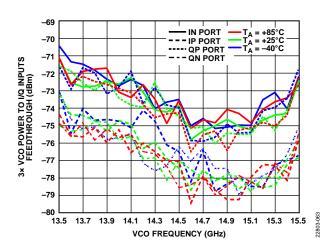

Figure 68. 3× VCO to I/Q Inputs Feedthrough vs. VCO Frequency over Temperature, Uncalibrated

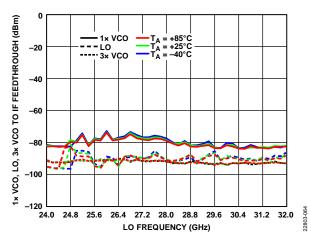

Figure 69. 1× VCO, LO, 3× VCO to IF Feedthrough vs. LO Frequency over Temperature

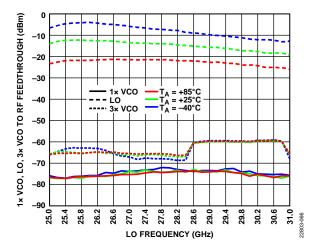

Figure 70. 1× VCO, LO, 3× VCO to RF Feedthrough vs. LO Frequency over Temperature, Uncalibrated

#### **VCO AND PLL**

$\label{eq:VCC_DRV} VCC\_AMP = VCC2\_DRV = 4 \ V, \ VCC\_IF = VCC2\_IF = VCC\_VVA = VCC\_MIXER = VCC\_DOUBLER = VCC\_VCO = VCC\_DIV = VCC\_LDO = VCC\_CP = 3.3 \ V, \ VCC\_1P8V = 1.8 \ V, \ REF\_IN \ power = 8 \ dBm, \ REF\_IN \ frequency = 200 \ MHz \ T_A = +25^{\circ}C, \ -40^{\circ}C, \ and \ +85^{\circ}C, \ VCTR\_RF = 1.8 \ V, \ and \ VCTR\_IF = 0 \ V, \ unless \ otherwise \ noted.$

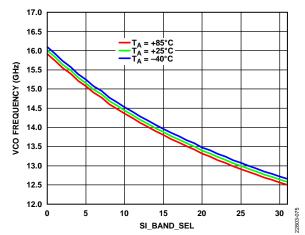

Figure 71. VCO Frequency vs. SI\_BAND\_SEL, Open Loop, over Temperature, VTUNE = 1.4 V

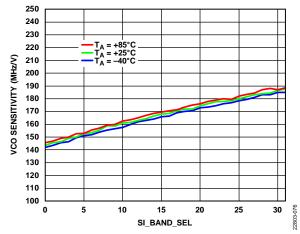

Figure 72. VCO Sensitivity vs. SI\_BAND\_SEL, Open Loop, over Temperatures, VTUNE = 1.4 V

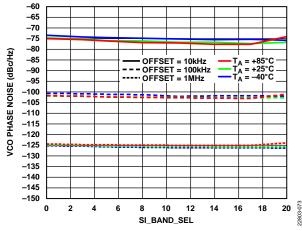

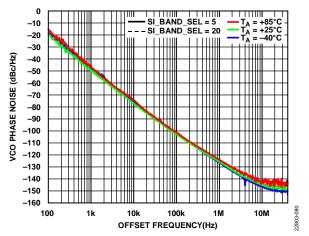

Figure 73. VCO Phase Noise vs. SI\_BAND\_SEL, over Temperature, Open Loop, VTUNE = 1.4 V

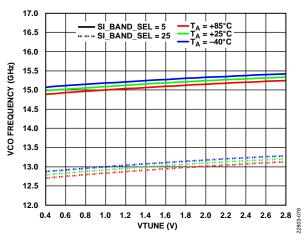

Figure 74. VCO Frequency vs. VTUNE, Open Loop over Temperature, SI\_BAND\_SEL = 5 and 25

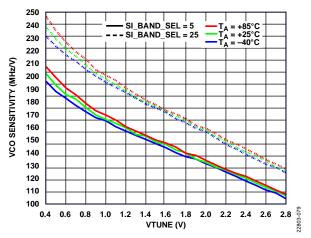

Figure 75. VCO Sensitivity vs. VTUNE, Open Loop over Temperature, SI\_BAND\_SEL = 5 and 25

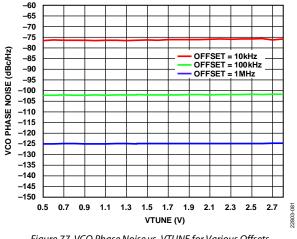

Figure 76. VCO Phase Noise vs. Offset Frequency over Temperature, Open Loop, VTUNE = 1.4 V, SI\_BAND\_SEL = 5 and 20

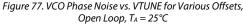

Figure 78. Phase Noise vs. Offset Frequency over Temperature, R\_WORD = 2, CP\_CURRENT = 4.2 mA, LO Frequency = 30 GHz

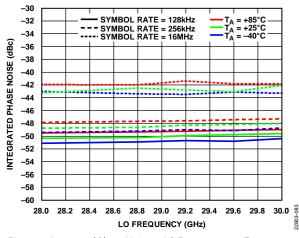

Figure 79. Integrated Phase Noise vs. LO Frequency over Temperature, R\_WORD = 2, CP\_CURRENT = 4.2 mA, Integrated from 1% to 50% of the Symbol Rate

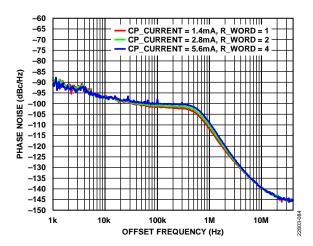

Figure 80. Phase Noise vs. Offset Frequency, LO Frequency = 27.2 GHz for Various CP\_CURRENT and R\_WORD Settings

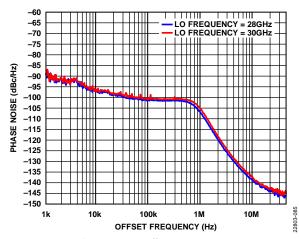

Figure 81. Phase Noise vs. Offset Frequency, R\_WORD = 2, CP\_CURRENT = 4.2 mA, LO Frequency = 28 GHz and 30 GHz

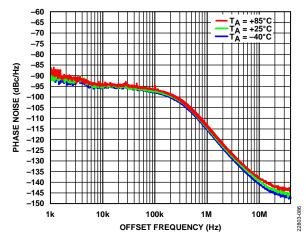

Figure 82. Phase Noise vs. Offset Frequency over Temperature, LO Frequency = 26.8 GHz, R\_WORD = 4, CP\_CURRENT = 2.1 mA

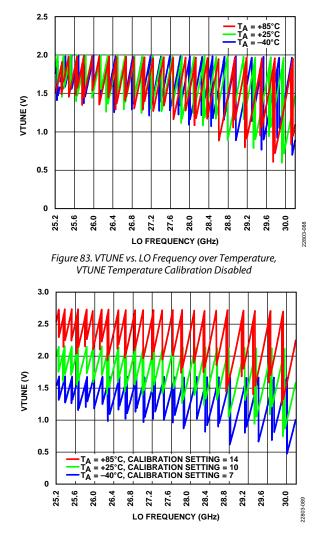

Figure 84. VTUNE vs. LO Frequency over Temperature and Various Calibration Settings, VTUNE Temperature Calibration Enabled

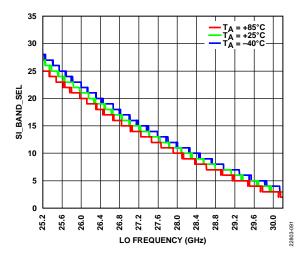

Figure 85. SI\_BAND\_SEL vs. LO Frequency over Temperature, VTUNE Temperature Calibration Disabled

Figure 86. SI\_BAND\_SEL vs. LO Frequency over Temperature and Various Calibration Settings, VTUNE Temperature Calibration Enabled

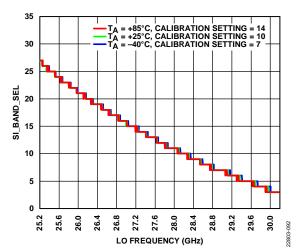

Figure 87. Reference Spurs vs. RF Frequency over Temperature, IF Mode,  $R_WORD = 4$ , CP\_CURRENT = 2.1 mA, VCTR\_IF = 0 V, P<sub>OUT</sub> = 10 dBm

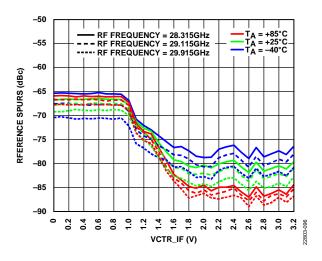

#### -50 T<sub>A</sub> = +85°C T<sub>A</sub> = +25°C T<sub>A</sub> = -40°C -55 -60 REFERENCE SPURS (dBc) -65 **MAMA** A -70 -75 -80 -85 -90 27.427 27.827 29.827 30.627 31.027 27.027 28.227 28.627 29.027 29.427 30.227 22803-094 RF FREQUENCY (GHz)

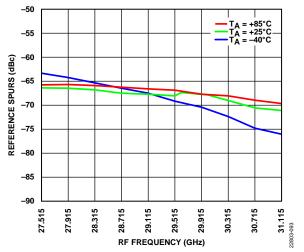

Figure 88. Reference Spurs vs. RF Frequency over Temperature, I/Q Mode,  $R_WORD = 2$ , CP\_CURRENT = 2.1 mA,  $P_{OUT} = 10 \text{ dBm}$

Figure 89. Reference Spurs vs. VCTR\_IF over Temperature and Various RF Frequencies, IF Mode, R\_WORD = 4, CP\_CURRENT = 2.1 mA

#### UPCONVERTER M × N SPURIOUS PERFORMANCE

Mixer spurious products are measured in dBc from the RF output power level.

For IF mode, spurious frequencies are calculated by

$|(M \times IF) + (N \times LO)|$

For I/Q mode, spurious frequencies are calculated by

$|(M \times I/Q) + (N \times LO)|$

#### IF Mode

IF frequency = 2715 MHz, RF frequency = 29 GHz, RF output power = 10 dBm, VCTR\_RF = 1.8 V, and VCTR\_IF = 0 V. N/A means not applicable.

|      |    | Ν×νο  |         |       |       |  |  |  |  |  |  |

|------|----|-------|---------|-------|-------|--|--|--|--|--|--|

|      |    | 0     | 0 1 2 3 |       |       |  |  |  |  |  |  |

|      | -2 | N/A   | -85.4   | -79.5 | -77.7 |  |  |  |  |  |  |

|      | -1 | N/A   | -84.1   | -36.9 | -79.0 |  |  |  |  |  |  |

| M×IF | 0  | -74.3 | -82.8   | -20.1 | -83.7 |  |  |  |  |  |  |

|      | +1 | -83.7 | -82.4   | 0.0   | -79.3 |  |  |  |  |  |  |

|      | +2 | -82.8 | -83.6   | -64.1 | -78.8 |  |  |  |  |  |  |

#### I/Q Mode

I/Q frequency = 25 MHz, RF frequency = 29 GHz, RF output power = 10 dBm, and VCTR\_RF = 1.8 V. N/A means not applicable.

|         |    | N × VCO |         |       |       |  |  |  |  |  |  |

|---------|----|---------|---------|-------|-------|--|--|--|--|--|--|

|         |    | 0       | 0 1 2 3 |       |       |  |  |  |  |  |  |

|         | -3 | N/A     | -100.1  | -69.5 | -84.9 |  |  |  |  |  |  |

|         | -2 | N/A     | -95.6   | -85.8 | -96.5 |  |  |  |  |  |  |

|         | -1 | N/A     | -91.8   | -27.6 | -88.0 |  |  |  |  |  |  |

| M × I/Q | 0  | N/A     | -89.4   | -31.3 | -80.9 |  |  |  |  |  |  |

|         | +1 | -76.1   | -84.1   | 0.0   | -94.4 |  |  |  |  |  |  |

|         | +2 | -96.9   | -94.6   | -51.2 | -92.4 |  |  |  |  |  |  |

|         | +3 | -94.4   | -98.3   | -64.0 | -93.0 |  |  |  |  |  |  |

### THEORY OF OPERATION

The ADMV4530 integrates a fractional-N PLL, VCO, internal 2× multiplier, and I/Q mixer. The fractional-N PLL locks the VCO to a precise reference input signal for low noise operation. The VCO signal is then multiplied by the internal 2× multiplier to generate the necessary LO signal for the I/Q mixer. The I/Q mixer can operate with either differential baseband I/Q inputs or a single-ended IF input. The functionality of the various blocks within the ADMV4530 follows within this section.

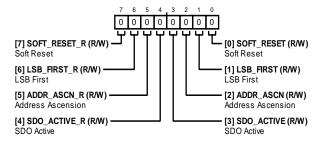

#### **SPI CONFIGURATION**

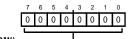

The SPI of the ADMV4530 allows configuration of the device for specific functions or operations via the 4-pin SPI port. This interface provides users with added flexibility and customization. The SPI consists of four control lines: SCLK, SDI, SDO, and  $\overline{\text{CS}}$ . The ADMV4530 protocol consists of a write/read bit followed by 15 register address bits and 8 data bits. The address field and data field are organized MSB first and end with the LSB.

For a write operation, set the MSB to 0, and for a read operation, set the MSB to 1. The write cycle must be sampled on the rising edge of SCLK. The 24 bits of the serial write address and data are shifted in on the SDI control line, MSB to LSB. The ADMV4530 input logic level for the write cycle supports a 3.3 V interface.

For a read cycle, the R/W bit and the 15 bits of address shift in on the rising edge of SCLK on the SDI control line. Then, 8 bits of serial read data shift out on the SDO control line, MSB first, on the falling edge of SCLK. The output logic level for a read cycle is 3.3 V. The output drivers of the SDO are enabled after the last rising edge of SCLK of the instruction cycle and remain active until the end of the read cycle. In a read operation, when  $\overline{\text{CS}}$  is deasserted, SDO returns to high impedance until the next read transaction. The  $\overline{\text{CS}}$  is active low and must be deasserted at the end of the write or read sequence.

An active low input on  $\overline{CS}$  starts and gates a communication cycle. The  $\overline{CS}$  pin allows more than one device to be used on the same serial communications lines. The SDO pin goes to a high impedance state when the  $\overline{CS}$  input is high. During the communication cycle, the chip select must stay low. The SPI communications protocol follows the Analog Devices, Inc., SPI standard. For more information, see the ADI-SPI Serial Control Interface Standard (Rev 1.0).

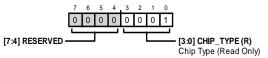

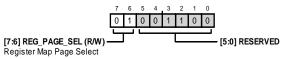

#### **REGISTER MAP SECTIONS**

The ADMV4530 consists of three register map sections. The first section spans from Register 0x000 through Register 0x00D and follows the standard Analog Devices SPI protocol, which includes protocol setup and device identification registers. The second register map section starts at Register 0x010 through Register 0x07C and contains all of the relevant PLL control registers. The third register map section starts at Register 0x100 through Register 0x119 and contains all of the mixer and baseband control registers. To read back the register values from the first

and third sections, the REG\_PAGE\_SEL bits in Register 0x117 must be set to 1, and to read back from the PLL section, the REG\_PAGE\_SEL bits in Register 0x117 must be set to 0.

#### **DOUBLE BUFFERED REGISTERS**

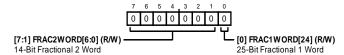

The PLL inside the ADMV4530 contains several double buffered bit fields that take effect only after a write to the lower portion of the N counter integer value (Register 0x010). This register applies any changes to these double buffered bit fields and initiates the autocalibration routine. The following is a list of the double buffered bit fields and their corresponding registers:

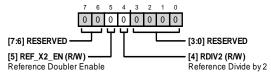

- REF\_X2\_EN (Register 0x022)

- RDIV2 (Register 0x022)

- R\_WORD (Register 0x01F)

- CP\_CURRENT (Register 0x01E)

- FRAC2WORD (Register 0x017 and Register 0x018)

- FRAC1WORD (Register 0x014 through Register 0x017)

- MOD2WORD (Register 0x019 and Register 0x01A)

- BIT\_INTEGER\_WORD (Register 0x010 and Register 0x011)

#### START-UP INITIALIZATION SEQUENCE

Upon powering up or resetting the ADMV4530, it is recommended to program the register map in reverse order, starting with the highest register number first. The reverse order ensures that the double buffered registers are programmed prior to initiating the autocalibration routine and that all PLL control settings are in their correct state. The recommended values of each register are shown in both the Register Summary section and the Register Details section. The following describes the recommended programming sequence:

- 1. Program Register 0x000 to a value of 0x18 to enable the SDO pin.

- 2. Program Register 0x117 to a value of 0x4C to enable reading from the mixer section of the register map.

- 3. Program Register 0x100 through Register 0x119 in reverse order based upon the desired mixer settings.

- 4. Program Register 0x117 to a value of 0x0C to enable reading from the PLL section of the register map.

- 5. Program Register 0x010 through Register 0x07C in reverse order based upon the desired PLL settings.

#### **FREQUENCY UPDATE SEQUENCE**

After the initialization sequence is performed, the output frequency can be updated by programming Register 0x010 through Register 0x01A in reverse order.

#### **REFERENCE INPUT**

Figure 91 shows the single-ended reference input stage. There is an internal reference multiply by 2 block (×2 doubler) that allows generation of higher fPFD. A higher fPFD is useful for improving overall system phase noise performance. Typically, doubling the fPFD improves the in band phase noise performance by up to 3 dBc/Hz. Use the REF X2 EN bit (Register 0x022, Bit 5) to enable the reference doubler, which toggles the SW1 switch, shown in Figure 91.

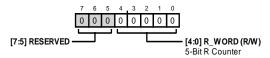

Following the reference doubler block, there are two frequency dividers: a 5-bit R counter (1 to 32 allowed) and a divide by 2 block. These dividers allow the input REF frequency to be divided down to produce lower fPFD that helps minimize fractional-N integer boundary spurs at the output.

Use the R\_WORD bits (Bits[4:0]) in Register 0x01F to set the R counter. If the R\_WORD = 1, the SW2 switch is in the position shown in Figure 91. Otherwise, the SW2 switch toggles to use the R counter. Additionally, R\_WORD = 0 corresponds to a divide by 32 value for the R counter. To enable the reference divide by 2 block, use the RDIV2 bit (Register 0x022, Bit 4) which toggles the SW3 switch, shown in Figure 91.

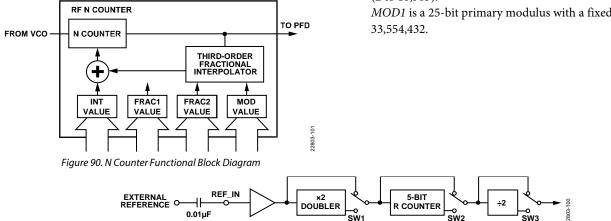

#### **N COUNTER**

The N counter allows a division ratio in the PLL feedback path from the VCO. Note that the VCO signal is multiplied by 2 to achieve the LO frequency at the input of the mixer. The division ratio is determined by using the Integer N (INT), fractional-N (FRAC), and modulus (MOD) values that this counter comprises. The applicable registers for setting the INT, FRAC, and MOD values are Register 0x010 to Register 0x01A.

Figure 91. Reference Input Path Block Diagram

#### INT, FRAC, MOD, AND R COUNTER RELATIONSHIP

The INT, FRAC, and MOD values, in conjunction with the reference path, make it possible to generate VCO frequencies spaced by fractions of the fPFD. To calculate fPFD, use the REF\_IN frequency and the reference path configuration parameters as follows:

$$f_{PFD} = REF\_IN \ Frequency \times \frac{1+D}{R \times (1+T)}$$

where:

*D* is the reference doubler bit (0 or 1).

*R* is the reference divide ratio of the binary, 5-bit

programmable counter (1 to 32).

*T* is the reference divide by 2 bit (0 or 1).

To calculate the VCO frequency ( $f_{VCO}$ ), use the following equation:

$$f_{VCO} = f_{LO}/2 = f_{PFD} \times N$$

where:

$f_{LO}$  is the frequency of the LO driving the mixer. *N* is the desired value of the N counter.

The N counter value is defined by the following:

$$N = INT + \frac{FRAC1 + \frac{FRAC2}{MOD2}}{MOD1}$$

where:

INT is the 16-bit integer value. When using the 4/5 prescaler, INT = 23 to 32,767, and when using the 8/9 prescaler, INT =75 to 65,535.

FRAC1 is the numerator of the primary modulus (0 to 33,554,431).

FRAC2 is the numerator of the 14-bit auxiliary modulus (0 to 16,383).

MOD2 is a programmable, 14-bit auxiliary fractional modulus (2 to 16,383).

*MOD1* is a 25-bit primary modulus with a fixed value of  $2^{25}$  =

These calculations result in a low frequency resolution with no residual frequency error. To apply the previous equation, perform the following steps:

- 1. Calculate N by dividing  $f_{VCO}/f_{PFD}$ . The integer value of this number forms INT.

- 2. Subtract INT from the full N value.

- 3. Multiply the remainder by 2<sup>25</sup>. The integer value of this number forms FRAC1.

- 4. Calculate MOD2 based on the channel spacing (f<sub>CHSP</sub>) by using the following equation:

$$MOD2 = (f_{PFD}/(GCD(f_{PFD}, f_{CHSP})))$$

#### where:

$f_{CHSP}$  is the desired channel spacing frequency. GCD( $f_{PFD}$ ,  $f_{CHSP}$ ) is the greatest common divisor of the PFD frequency and the channel spacing frequency.

5. Calculate FRAC2 by using the following equation:

$FRAC2 = ((N - INT) \times 2^{25} - FRAC1) \times MOD2$

The FRAC2 and MOD2 fraction result in outputs with zero frequency error for channel spacing when the following is true:

$(f_{PFD}/(GCD(f_{PFD}, f_{CHSP})) = MOD2 < 16,383$

If zero frequency error is not required, the MOD1 and MOD2 denominators operate together to create a 39-bit resolution modulus.

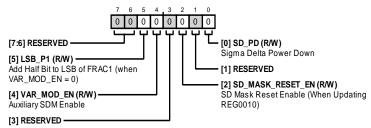

#### INT N MODE

When FRAC1 and FRAC2 are equal to 0, the synthesizer operates in Integer N mode. It is recommended to set the SD\_PD bit (Register 0x02B, Bit 0) to 1 to disable the  $\Sigma$ - $\Delta$  modulators (SDMs), which improves the in band phase noise and reduces any additional  $\Sigma$ - $\Delta$  noise.

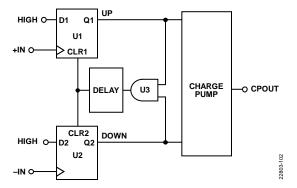

#### PHASE FREQUENCY DETECTOR AND CHARGE PUMP

The phase frequency detector takes inputs from the R counter and N counter to produce an output that is proportional to the phase and frequency differences between these counters. This proportional information is then output to a charge pump circuit that generates current to drive an external loop filter that is then used to appropriately increase or decrease the VTUNE tuning voltage.

Figure 92 shows a simplified schematic of the phase frequency detector and charge pump. Note that the phase frequency detector includes a fixed delay element that is used to ensure that there is no dead zone in the phase frequency detector transfer function for consistent reference spur levels.

Figure 92. Phase Frequency Detector and Charge Pump Simplified Schematic

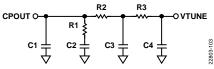

#### LOOP FILTER

Defining a loop filter for a PLL is dependent on several dynamics, such as the  $f_{PFD}$ , the N counter value, the  $K_{VCO}$ , and the selected charge pump current ( $I_{CP}$ ). A higher  $f_{PFD}$  has the advantage of lowering in band phase noise performance at the expense of integer boundary spur levels when operating in fractional-N mode. Consequently, a lower  $f_{PFD}$  can allow the PLL to operate in integer N mode, which can eliminate integer boundary spurs at the expense of higher in band phase noise performance. Given the trade-offs, care must be taken with frequency planning and  $f_{PFD}$  selection to ensure the appropriate in band phase noise performance is met with acceptable spur levels for the end application.

The loop filter, as implemented using one of the ADMV4530 evaluation boards (see the Ordering Guide section), is a thirdorder passive filter, as shown in Figure 93. The filter is designed with the following simulation input parameters:  $f_{PFD} = 100$  MHz,  $K_{VCO} = 155$  MHz/V,  $f_{VCO} = 15$  GHz, and  $I_{CP} = 4.2$  mA. The resulting loop filter bandwidth and phase margin are 540 kHz and 55°, respectively, for the following component values: C1 = 150 pF, C2 = 15 nF, C3 = 20 pF, C4 = do not install (DNI), R1 = 910  $\Omega$ , R2 = 910  $\Omega$ , and R3 = 0  $\Omega$ . For additional guidance with loop filter simulations on the ADMV4530, contact Analog Devices for Technical Support.

#### **CHARGE PUMP CURRENT SETUP**

For a specifically designed loop filter, set the  $I_{CP}$  by adjusting the CP\_CURRENT value in Bits[7:4], Register 0x01E. Calculate  $I_{CP}$  by using the following the equation:

$I_{CP} = (CP\_CURRENT + 1) \times 350 \ \mu A$

where CP\_CURRENT is an integer value (0 to 15).

The default value for a 100 MHz  $f_{PFD}$  for CP\_CURRENT = 11, which yields a current of 4.2 mA. The applicable range is 0.35 mA to 5.6 mA, with 0.35 mA steps.

To change the  $f_{PFD}$ , if no change has been made to the existing loop filter components, it is recommended to scale  $I_{CP}$  by using the following equation:

$$I_{CP(NEW)} = \frac{I_{CP(DEFAULT)} \times f_{PFD(DEFAULT)}}{f_{PFD(NEW)}}$$

where:

$I_{CP (NEW)}$  is the new desired I<sub>CP</sub>.  $I_{CP (DEFAULT)}$  is the default I<sub>CP</sub>.  $f_{PFD (DEFAULT)}$  is the default f<sub>PFD</sub>.  $f_{PFD (NEW)}$  is the new desired f<sub>PFD</sub>.

When  $I_{CP(NEW)}$  is obtained, the CP\_CURRENT value in Bits[7:4], Register 0x01E, can be updated by using the following rounding function:

$$CP\_CURRENT = \text{ROUND}\left(\frac{I_{CP(NEW)}}{350\,\mu\text{A}}\right) - 1$$

where ROUND is the mathematical round function.

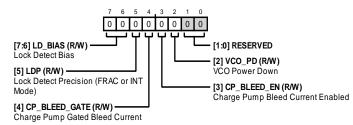

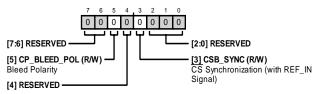

#### **BLEED CURRENT (CP\_BLEED) SETUP**

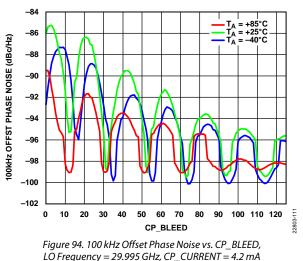

The charge pump includes a binary scaled bleed current ( $I_{BLEED}$ ) that is set by using the CP\_BLEED value in Register 0x026. The bleed current introduces a slight phase offset in the phase frequency detector to improve integer boundary spurs and phase noise when operating in fractional-N mode. To enable the bleed current for fractional-N mode, set CP\_BLEED\_EN = 1 (Register 0x027, Bit 3). For integer mode, CP\_BLEED\_EN must be set to 0.

Generally, the optimum bleed current value is 115 (431.25  $\mu$ A), and this value provides optimal performance for most applications. However, there can be additional performance improvements by empirically determining the appropriate bleed current value from the actual measurements for the intended application. The applicable range is 0  $\mu$ A to 956.25  $\mu$ A with 3.75  $\mu$ A steps.

$I_{BLEED} = CP\_BLEED \times 3.75 \ \mu A$

where *CP\_BLEED* is an integer value (0 to 255).

Figure 94 shows an example of 100 kHz offset phase noise vs. CP\_BLEED.

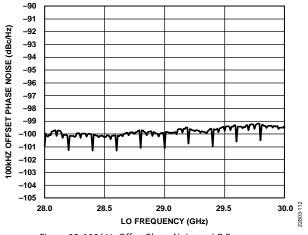

Figure 95 is an example of 100 kHz offset phase noise vs. LO frequency with a CP\_BLEED value of 115 (431.25  $\mu$ A). The CP\_CURRENT was 4.2 mA and the LO frequency step size was 10 MHz. At each integer boundary, the CP\_BLEED was disabled, resulting in approximately –1 dBc/Hz improvement.

Figure 95. 100 kHz Offset Phase Noise vs. LO Frequency, CP\_BLEED = 115, CP\_CURRENT = 4.2 mA

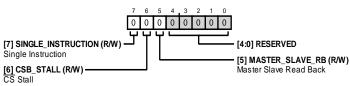

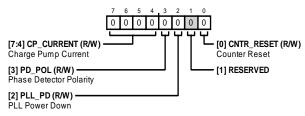

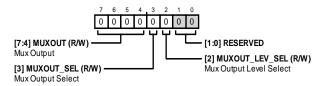

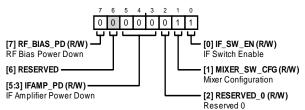

#### MUXOUT

The output multiplexer on the ADMV4530 allows the user to access various internal signals on the chip. The MUXOUT bit field (Register 0x020, Bits[7:4]) shown in Table 30 lists the available signals. When MUXOUT\_SEL (Register 0x20, Bit 3) is set to 1, the MUXOUT signal is present on the SDO output pin. Otherwise, the SDO pin is configured for SPI data output.

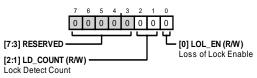

#### **DIGITAL LOCK DETECT**

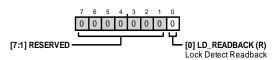

A digital lock detect function is available on the SDO pin when both the MUXOUT and MUXOUT\_SEL bits are set to 1. The digital lock detect function is also available by reading the LD\_READBACK bit (Register 0x07C, Bit 0). A logic high indicates that the digital lock detect has declared the PLL is locked.

The digital lock detect function has some adjustable settings in Register 0x027 and Register 0x028. The LD\_BIAS and LDP bits adjust an internal precision window and the LD\_COUNT bits adjust the consecutive cycle count to declare PLL lock. It is recommended to keep the settings listed in the register map. For special applications, contact Analog Devices Technical Support for guidance on adjusting these settings.

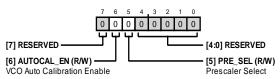

#### **VCO AUTOCALIBRATION**

The internal VCO uses an internal autocalibration routine that optimizes the VCO settings for a particular frequency and allows the PLL to lock in approximately 100 µs after the lower portion of the N counter integer value (Register 0x010) is programmed. For nominal applications, maintain the autocalibration default values in the register map (Register 0x030 to Register 0x034).

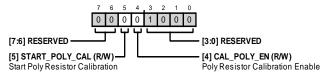

For applications where it is desirable to bypass the autocalibration routine, there are two necessary procedures. First, generate a lookup table of the resultant VCO calibration data (core and band parameters) for each desired VCO frequency. Second, bypass the autocalibration routine and manually write the lookup table values. Generate a new table for every chip because each chip is unique.

#### **VCO CALIBRATION DATA READ BACK**

To read back the VCO calibration data, load the required registers, let the device lock using autocalibration, and read the VCO parameters for each frequency. It is important to ensure that autocalibration has completed before readback. Reading back values before autocalibration has completed results in incorrect values being read. The bits used for read back include the following:

- Register 0x033, Bits[7:5], VCO\_FSM\_READBACK

- Register 0x06E, Bits[4:0], VCO\_DATA\_READBACK

- Register 0x06F, Bit 0, VCO\_DATA\_READBACK

The VCO\_FSM\_READBACK bits set what data is sent to the VCO\_DATA\_READBACK bits.

To read the VCO parameters, take the following steps:

- 1. Program the device to lock at the desired frequency by using the autocalibration feature. Users must wait for the device to lock.

- 2. Set VCO\_FSM\_READBACK = 1 to allow readback of the VCO band and the core.

- 3. Read Register 0x06F, Bit 0 to read back the current VCO core. The ADMV4530 has only one VCO core. Therefore, this value must always be 1.

- 4. Read Register 0x06E, Bits[4:0] to read back the VCO band.

Repeat Step 1 through Step 4 for each required frequency to build a lookup table of values.

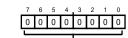

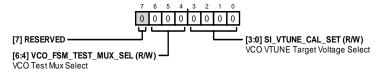

#### VCO CALIBRATION DATA MANUAL WRITING

The VCO parameters for each required frequency force the device to the target frequency core and band without the use of autocalibration.

The bits used for writing to the VCO parameters include the following:

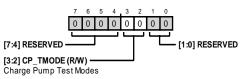

- Register 0x034, Bits[7:5], VCO\_FSM\_TEST\_MODES

- Register 0x037, Bits[7:0], SI\_BAND\_SEL

- Register 0x038, Bits[7:4], SI\_VCO\_SEL

To write the VCO parameters, take the following steps:

- 1. At power-up, set up the serial port interface and initialize the device as necessary for normal operation.

- 2. Set AUTOCAL\_EN = 0 (Register 0x012, Bit 6) to disable autocalibration.

- 3. Set VCO\_FSM\_TEST\_MODES = 010 to overwrite the VCO core and band.

- 4. Program the registers, except Register 0x010, as required for the target frequency. This step is frequency dependent.

- 5. Set SI\_VCO\_SEL = 1. Even though the ADMV4530 has only one VCO core, it is still necessary to program this bit because this bit tells the internal finite state machine to enable the VCO.

- 6. Set SI\_BAND\_SEL to the desired band from the previously generated lookup table.

- 7. Write to Register 0x010. When this register is written to, the device locks to the new frequency.

Repeat Step 4 through Step 7 as required for setting the appropriate VCO frequency.

#### **AUTOCALIBRATION LOCK TIME**

The PLL lock time divides into a number of settings. The total lock time for changing frequencies is the sum of three separate times: synthesizer lock, VCO band selection, and PLL settling.

#### SYNTHESIZER LOCK TIMEOUT

The synthesizer lock timeout ensures that the VCO calibration digital-to-analog converter (DAC), which forces the VCO tune voltage ( $V_{VTUNE}$ ), has settled to a steady value for the band select circuitry. The SYNTH\_LOCK\_TIMEOUT and the TIMEOUT bits select the length of time the DAC is allowed to settle to the final voltage before the VCO calibration process continues to the next phase (VCO band selection). The PFD frequency is the clock for this logic, and the duration is set by using the following equation:

$(SYNTH\_LOCK\_TIMEOUT \times 1024 + TIMEOUT)/f_{PFD}$

where:

*SYNTH\_LOCK\_TIMEOUT* is programmed in Bits[4:0], Register 0x033.

*TIMEOUT* is programmed in Bits[7:0], Register 0x031 and Bits[1:0], Register 0x032.

The calculated time must be greater than or equal to 20  $\mu s.$

For the SYNTH\_LOCK\_TIMEOUT bits, the minimum value is 2, and the maximum value is 31.

For TIMEOUT, the minimum value is 2, and the maximum value is 1023.

#### VCO BAND SELECTION TIME

Use the VCO\_BAND\_DIV bits (Bits[7:0], Register 0x030) and the  $f_{PFD}$  to generate the VCO band selection clock ( $f_{BSC}$ ) as follows:

$f_{BSC} = (f_{PFD}/VCO\_BAND\_DIV)$

The calculated frequency must be less than 4 MHz.

Note that 16 clock cycles are required for one VCO core and band calibration step and the total band selection process takes 11 steps, resulting in the following equation:

$11 \times (16 \times VCO\_BAND\_DIV/f_{PFD})$

The minimum value for VCO\_BAND\_DIV is 1, and the maximum value is 255.

#### PLL SETTLING TIME

The time taken for the loop to settle is inversely proportional to the low-pass filter bandwidth.

#### **CHIP TEMPERATURE READ BACK**

Chip temperature readback can provide information regarding system temperature, which is useful for system compensation.

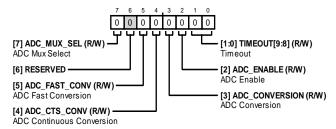

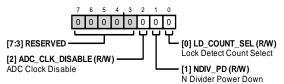

The ADMV4530 includes an analog-to-digital converter (ADC) that enables reading the chip temperature. The ADC clock (ADC\_CLK) is generated from the phase frequency detector clock ( $f_{PFD}$ ) with the following equations:

$$ADC\_CLK = \frac{f_{PFD}}{\left(\left(ADC\_CLK\_DIV \times 4\right) + 2\right)}$$

where ADC\_CLK\_DIV is stored in Register 0x035.

A valid reference signal is required to complete a conversion. Target 100 kHz for ADC\_CLK and calculate ADC\_CLK\_DIV with the following equation:

$$ADC\_CLK\_DIV = ceiling\left(\frac{\left(\left(\frac{f_{PFD}}{100,000}\right) - 2\right)}{4}\right)$$

If ADC\_CLK\_DIV is greater than 255, set these bits to 255.

The bits used for temperature readback are the following:

- Register 0x032, Bit 2, ADC\_ENABLE

- Register 0x032, Bit 3, ADC\_CONVERSION

- Register 0x033, Bits[7:5], VCO\_FSM\_READBACK

- Register 0x06E, Bits[7:0], VCO\_DATA\_READBACK[7:0]

- Register 0x073, Bit 2, ADC\_CLK\_DISABLE

To read back the temperature, take the following steps:

- 1. Set ADC\_ENABLE = 1 to enable the ADC.

- 2. Set ADC\_CONVERSION = 1 to perform an ADC conversion.

- 3. Wait 16 ADC\_CLK cycles.

- 4. Set VCO\_FSM\_READBACK = 101 (skip this step if it is already set).

- 5. Read the VCO\_DATA\_READBACK bits in Register 0x06E to read back the raw ADC output that corresponds to the chip temperature (RAW\_TEMP).

- 6. Set ADC\_CONVERSION = 0 to disable the conversion.

- Set ADC\_ENABLE = 0 to disable the ADC, which prevents any spurs generated by the ADC clock. Similarly, the ADC\_CLK\_DISABLE bit can disable the ADC clock.

Perform Step 1 and Step 2 separately. However, Step 6 and Step 7 can be completed together.

To calculate the approximate chip temperature in Celsius (°C), use the following equation:

$Chip \ Temperature = -100^{\circ}\text{C} + RAW\_TEMP$

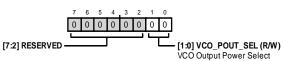

### **RF OUTPUT DRIVER**

As shown in the functional block diagram (see Figure 1), the ADMV4530 incorporates two driver stages along with a voltage variable attenuator (VVA) in the RF output section of the chip. The VCTR\_RF pin (Pin 4) is connected to the VVA, which adjusts the RF output gain. The voltage range for the VCTR\_RF pin is 0 V to 1.8 V, with a positively sloping linear region between 0.6 V to 1.5 V, as shown in Figure 7. The typical slope within linear region is 32 dB/V.

### I/Q MODE MIXER SETUP

In baseband quadrature modulation mode, the input impedance of the baseband pins (IN, IP, QN, and QP) are 100  $\Omega$  differential. These inputs can be driven with a dc-coupled 100  $\Omega$  differential source. IN and IP are the differential baseband I inputs, and QN and QP are the differential baseband Q inputs. These inputs can operate from a common-mode voltage range of 0 V to 2.5 V. When operating in I/Q mode, program the following registers:

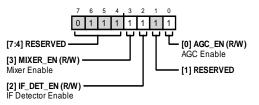

- Register 0x100 = 0x3A

- Register 0x101 = 0x78

- Register 0x102 = 0x11

- Register 0x103 = 0x5D (for  $0.5 V V_{CM}$ )

- Register 0x106 to 0x109 = 0x7F

- Register 0x115 = 0x88

When  $V_{CM}$  changes, program Register 0x103 by using the following formulas for each mode.

In I/Q mode, for  $V_{\rm CM}$  = 0.0 V to 1.5 V, set

$MIXER_VCM = \text{ROUND}(23.8 \times V_{CM} + 80.7).$

In I/Q mode, for  $V_{\rm CM}$  = 1.5 V to 2.5 V, set

$MIXER_VCM = \text{ROUND}(23.8 \times V_{CM} + 1.3).$

The I/Q mode default for  $V_{CM} = 0.5$  V is MIXER\_VCM = 93 = 0x5D.

#### I/Q MODE LO NULLING

To perform LO nulling in I/Q mode, apply a differential dc offset on the I and Q inputs. Note that LO nulling is a two-step process. When LO nulling is done on the I side, keep the Q side at  $V_{\text{CM}}$ , and when LO nulling is done on the Q side, the I side must be kept at V<sub>CM</sub> or at the determined value in the first step. The optimal LO null is when settings from the I side and the Q side are combined. It is important to keep V<sub>CM</sub> constant. Therefore, when a dc offset is applied on the negative input  $(V_{\text{CMN}})$ , the same offset must be applied on the positive input  $(V_{\text{CMP}})$  in the opposite direction (V\_{\text{CMP}} \pm dc offset and V\_{\text{CMN}} \mp dc offset) to allow the average VCM to hold constant to coincide with the value programmed in Register 0x103. LO nulling at a single point is optimal at that particular frequency and temperature, and the absolute level (dBm) of the LO to RF feedthrough remains the same across gain settings using the VCTR\_RF input.

For example, it is possible to null LO down to -50 dBm with VCTR\_RF = 1.8 V, depending on the resolution of the dc offset applied and the temperature (as shown in Figure 27 and Figure 28), where LO nulling = 29 GHz. When LO nulling = 29 GHz, the LO to RF feedthrough is <-20 dBm over temperature, and the frequency range is from 28 GHz to 30 GHz.

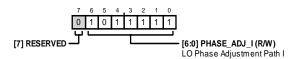

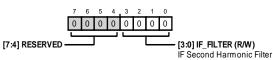

#### I/Q MODE SIDEBAND REJECTION NULLING

In I/Q mode, use Register 0x104 or Register 0x105 to perform sideband rejection nulling. Each register has 128 settings, Bits[6:0]. Single frequency nulling allows sideband rejection to null down to -45 dBc for a particular frequency. The sideband rejection degrades to -35 dBc if the frequency or temperature changes (shown in Figure 26 and Figure 29).

#### **IF GAIN CONTROL**

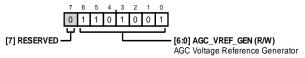

As shown in the functional block diagram (see Figure 1), the ADMV4530 incorporates an IF amplifier with analog gain control. The analog voltage for this IF amplifier can either be provided by the internal AGC loop or by applying an external VCTR\_IF voltage to the EXT\_CAP\_N (Pin 10). The voltage range for the IF amplifier gain control is 0 V to 3.3 V, with a negatively sloping linear region between 0.9 V and 2.2 V, as shown in Figure 37. The typical slope within linear region is -32 dB/V.

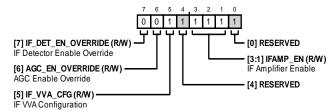

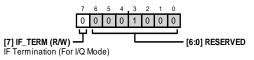

#### IF MODE MIXER SETUP

The ADMV4530 features the ability to upconvert a real IF input anywhere from 2 GHz to 3 GHz. When operating in IF mode program the following registers:

- Register 0x100 = 0x03

- Register 0x101 = 0x7D

- Register 0x102 = 0x3F

- Register 0x103 = 0x5B (this register sets  $V_{CM}$  in IF mode)

- Register 0x104 to 0x109 = 0x5F

- Register 0x115 = 0x08

When  $V_{CM}$  changes, program Register 0x103 by using the following formula:

*MIXER\_VCM* = ROUND(0.3 × (128 – *TARGET\_MIXER\_DC\_OFFSET*) + 80.7)

where *TARGET\_MIXER\_DC\_OFFSET* is the value programmed into Register 0x106 to Register 0x109.

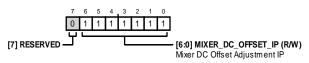

#### **IF MODE LO NULLING**

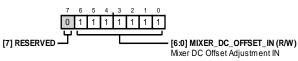

LO nulling is performed in IF mode in a similar fashion as in I/Q mode. However, dc offset is applied through Register 0x106 to Register 0x109. Use Register 0x106 and Register 0x107 to force a dc offset on the I side, and use Register 0x108 and Register 0x109 to force a dc offset on the Q side. It is important to sweep the I and Q registers simultaneously in opposite direction so that the following are true:

(*MIXER\_DC\_OFFSET\_IP* + *MIXER\_DC\_OFFSET\_IN*)/2 = *TARGET\_MIXER\_DC\_OFFSET*

(*MIXER\_DC\_OFFSET\_QP* + *MIXER\_DC\_OFFSET\_QN*)/2 = *TARGET\_MIXER\_DC\_OFFSET*

As in I/Q mode, LO nulling is two-step process. When LO nulling on the I side, keep the Q side at the

TARGET\_MIXER\_DC\_OFFSET. When LO nulling on the Q side, keep the I side at the TARGET\_MIXER\_DC\_OFFSET, or at the determined value from the first step. The optimal null is achieved when both settings are combined. The recommended