## Description

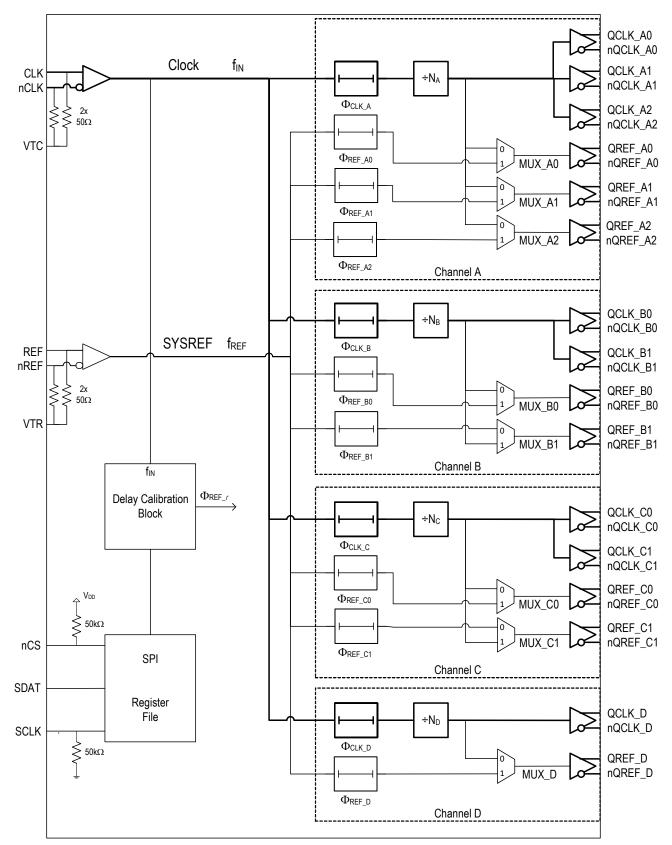

The 8V79S680 is a fully integrated, clock and SYSREF signal fanout buffer for JESD204B applications. It is designed as a high-performance clock and converter synchronization solution for wireless base station radio equipment boards with JESD204B subclass 0, 1, and 2 compliance. The main function of the device is the distribution and fanout of high-frequency clocks and low-frequency system reference signals generated by a JESB204B clock generator such as the IDT 8V19N480, extending its fanout capabilities and providing additional phase-delay.

The 8V79S680 is optimized to deliver very low phase noise clocks and precise, phase-adjustable SYSREF synchronization signals as required in GSM, WCDMA, LTE, LTE-A radio board implementations. Low-skew outputs, low device-to-device skew characteristics and fast output rise/fall times help the system design to achieve deterministic clock and SYSREF phase relationship across devices.

The device distributes the input clock (CLK) and JESD204B SYSREF signals (REF) to four fanout channels. In each channel, both input clock and SYSREF signals are fanned-out to multiple clock (QCLK) and SYSREF (QREF) outputs. Clock signals can be frequency-divided in each channel. Configurable phase-delay circuits are available for both clock and SYSREF signals. The propagation delays in all signal paths are fully deterministic to support fixed phase relationships between clock and SYSREF signals within one device. Clock divider can be bypassed for low-latency clock paths. The device facilitates synchronization between frequency dividers within the device and across multiple devices, removing phase ambiguity introduced in dividers between power and configuration cycles.

Each channel supports clock frequencies up to 3GHz. In an alternative configuration, for instance JESD204B subclass 0 and 2, the SYSREF (QREF) outputs can be configured as regular clock outputs adding additional clock fanout to the device.

All outputs are very flexible in amplitude configuration, output signal termination and allow both DC and AC coupling. Outputs can be disabled and powered-down when not used. The SYSREF output pre-bias feature supports prevention of power-on glitches and enables AC-coupling of the system synchronization signals.

The device is configured through a 3-wire SPI serial interface. The device is packaged in a lead-free (RoHS 6) 64-lead VFQFPN package. The extended temperature range supports wireless infrastructure, telecommunication and networking end equipment requirements. The device is a member of the high-performance clock family from IDT.

# **Typical Applications**

- JESD204B low phase noise clock and SYSREF signal distribution

- Supports JESD204 subclass 0, 1 and 2

- Clock distribution device for jitter-sensitive ADC and DAC circuits

- Wireless infrastructure

- Radar and imaging

- Instrumentation and medical

## Features

- Supports high-speed, low phase noise converter clocks

- Distribution, fanout, phase-delay of clock and SYSREF signals

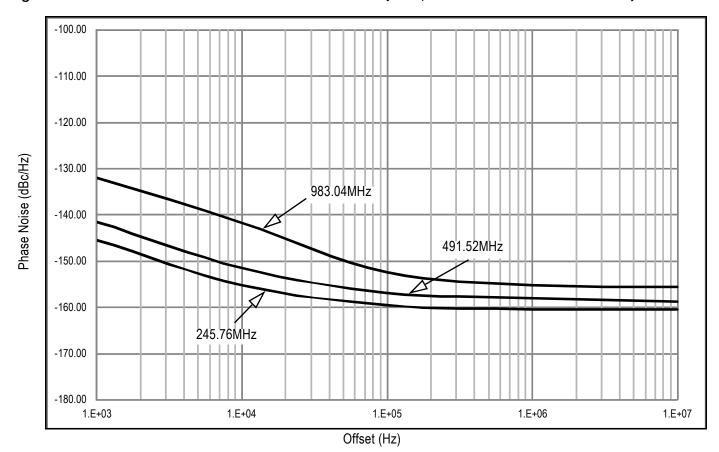

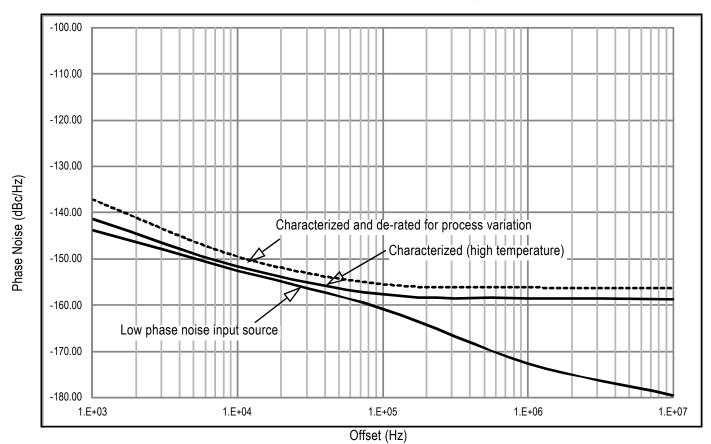

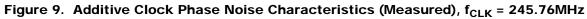

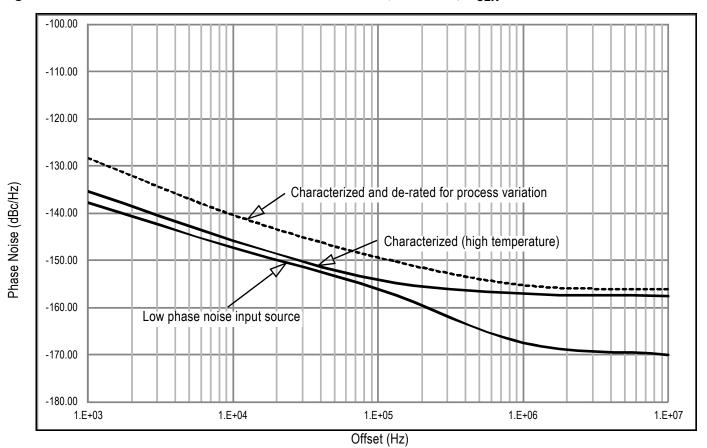

- Very low output noise floor: -158.8dBc/Hz noise floor (245.76MHz)

- Supports clock frequencies up to 3GHz, including clock output frequencies of 983.04MHz, 491.52MHz, 245.76MHz, and 122.88MHz

- 4 output channels with a total of 16 differential outputs, organized in:

- 8 dedicated clock outputs

- 8 outputs configurable as SYSREF outputs with individual phase delay stages, or configurable as additional clock outputs

- Each channel contains:

- Frequency dividers: ÷1, ÷2, ÷4, ÷6, ÷8, ÷12, ÷16

- Clock phase delay circuits

- Clock phase delay circuits

- Clock: delay unit is the clock period; 256 steps

- SYSREF: Configurable precision phase delay circuits: 8 steps of 131ps, 262ps, 393ps, or 524ps

- Flexible differential outputs:

- LVDS/LVPECL configurable

- Amplitude configurable

- Power-down modes for unused outputs

- Supports DC and AC coupling

- QREF (SYSREF) output pre-bias feature to prevent glitches when turning output on or off

- Supply voltage:

- 3.3V core and signal I/O

- 1.8V Digital control SPI I/O (3.3V-tolerant inputs)

- 64 VFQFPN package (9 × 9 × 0.85 mm)

- Ambient temperature range: -40°C to +85°C

## Contents

| Description                                                            |     |

|------------------------------------------------------------------------|-----|

| Typical Applications                                                   | . 1 |

| Features                                                               | . 1 |

| Contents                                                               | . 2 |

| Block Diagram                                                          | . 3 |

| Pin Assignments.                                                       | . 4 |

| Pin Descriptions                                                       | . 5 |

| Principles of Operation                                                | . 7 |

| Overview                                                               | . 7 |

| Signal Flow                                                            | . 7 |

| Clock Channel Divider                                                  | . 7 |

| Phase Delay                                                            |     |

| Delay Calibration Block (DCB)                                          | . 8 |

| QCLK to SYSREF Phase Alignment                                         | 10  |

| Differential Outputs                                                   | 11  |

| Device Startup, Reset, and Synchronization                             | 13  |

| Changing Frequency Dividers and Phase Delay Values                     | 13  |

| SPI Interface                                                          | 14  |

| Register Descriptions                                                  | 16  |

| Channel and Clock Output Registers                                     | 19  |

| QREF Output State Registers                                            | 21  |

| SYSREF Control Registers                                               | 24  |

| General Control Registers                                              | 26  |

| Electrical Characteristics                                             | 28  |

| Absolute Maximum Ratings                                               | 28  |

| Pin Characteristics                                                    | 28  |

| DC Characteristics                                                     | 29  |

| AC Characteristics                                                     | 32  |

| Additive Clock Phase Noise Characteristics                             | 35  |

| Application Information.                                               | 41  |

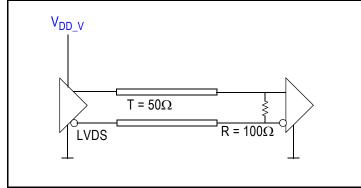

| Termination for QCLK_y, QREF_r LVDS Outputs (STYLE = 0)                | 41  |

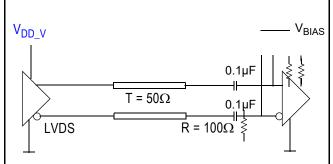

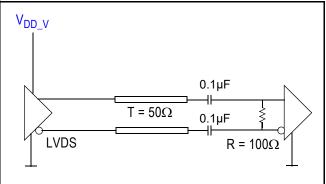

| AC Termination for QCLK_y, QREF_r LVDS Outputs (STYLE = 0)             | 41  |

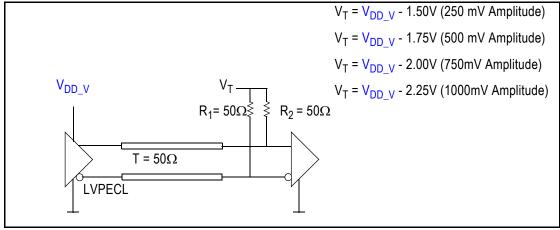

| Termination for QCLK_y, QREF_r LVPECL Outputs (STYLE = 1)              | 42  |

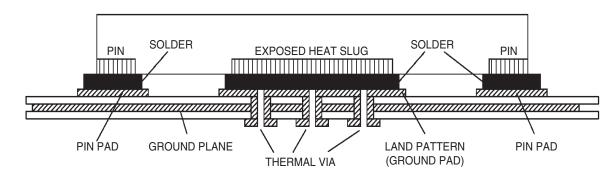

| Package Exposed Pad Thermal Release Path                               | 42  |

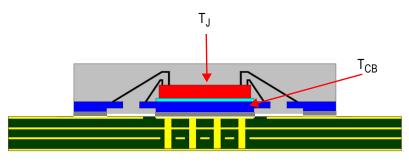

| Thermal Characteristics                                                | 43  |

| Case Temperature Considerations                                        | 43  |

| Example Calculation for Junction Temperature (TJ): TJ = TCB + YJB x PD | 44  |

| Package Outline Drawings                                               |     |

| Ordering Information                                                   |     |

| Marking Diagram                                                        | 44  |

| Glossary                                                               |     |

| Revision History                                                       |     |

|                                                                        |     |

## **Block Diagram**

Figure 1. Block Diagram

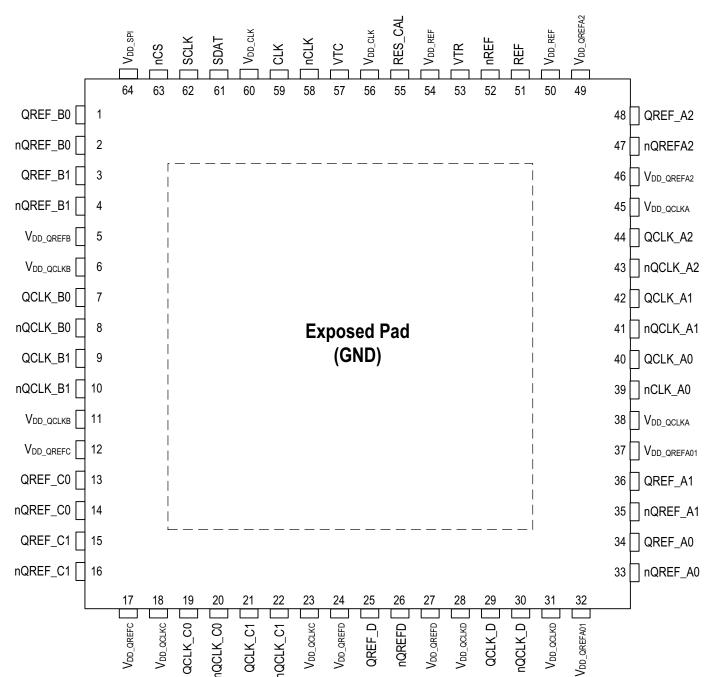

## **Pin Assignments**

Figure 2. Pin Assignments 9 x 9 x 0.85 mm 64-VFQFPN Package (Top View)

## **Pin Descriptions**

### Table 1. Pin Descriptions

| Number    | Name                    | Type <sup>[a]</sup> | Description                                                                                                                                  |

|-----------|-------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1,<br>2   | QREF_B0,<br>nQREF_B0    | Output              | Differential SYSREF/clock output QREF_B0. LVDS style for SYSREF operation, configurable LVPECL/LVDS style and amplitude for clock operation. |

| 3,<br>4   | QREF_B1,<br>nQREF_B1    | Output              | Differential SYSREF/clock output QREF_B1. LVDS style for SYSREF operation, configurable LVPECL/LVDS style and amplitude for clock operation. |

| 5         | V <sub>DD_QREFB</sub>   | Power               | Positive supply voltage (3.3V) for the QREF_B[1:0] outputs.                                                                                  |

| 6         | V <sub>DD_QCLKB</sub>   | Power               | Positive supply voltage (3.3V) for the QCLK_B[1:0] outputs.                                                                                  |

| 7,<br>8   | QCLK_B0,<br>nQCLK_B0    | Output              | Differential clock output QCLK_B0. Configurable LVPECL/LVDS style and amplitude.                                                             |

| 9,<br>10  | QCLK_B1,<br>nQCLK_B1    | Output              | Differential clock output QCLK_B1. Configurable LVPECL/LVDS style and amplitude.                                                             |

| 11        | V <sub>DD_QCLKB</sub>   | Power               | Positive supply voltage (3.3V) for the QCLK_B[1:0] outputs.                                                                                  |

| 12        | V <sub>DD_QREFC</sub>   | Power               | Positive supply voltage (3.3V) for the QREF_C[1:0] outputs.                                                                                  |

| 13,<br>14 | QREF_C0,<br>nQREF_C0    | Output              | Differential SYSREF/clock output QREF_C0. LVDS style for SYSREF operation, configurable LVPECL/LVDS style and amplitude for clock operation. |

| 15,<br>16 | QREF_C1,<br>nQREF_C1    | Output              | Differential SYSREF/clock output QREF_C1. LVDS style for SYSREF operation, configurable LVPECL/LVDS style and amplitude for clock operation. |

| 17        | V <sub>DD_QREFC</sub>   | Power               | Positive supply voltage (3.3V) for the QREF_C[1:0] outputs.                                                                                  |

| 18        | V <sub>DD_QCLKC</sub>   | Power               | Positive supply voltage (3.3V) for the QCLK_C[1:0] outputs.                                                                                  |

| 19,<br>20 | QCLK_C0,<br>nQCLK_C0    | Output              | Differential clock output QCLK_C0. Configurable LVPECL/LVDS style and amplitude.                                                             |

| 21,<br>22 | QCLK_C1,<br>nQCLK_C1    | Output              | Differential clock output QCLK_C1. Configurable LVPECL/LVDS style and amplitude.                                                             |

| 23        | V <sub>DD_QCLKC</sub>   | Power               | Positive supply voltage (3.3V) for the QCLK_C[1:0] outputs.                                                                                  |

| 24        | V <sub>DD_QREFD</sub>   | Power               | Positive supply voltage (3.3V) for the QREF_D outputs.                                                                                       |

| 25,<br>26 | QREF_D,<br>nQREF_D      | Output              | Differential SYSREF/clock output QREF_D. LVDS style for SYSREF operation, configurable LVPECL/LVDS style and amplitude for clock operation.  |

| 27        | V <sub>DD_QREFD</sub>   | Power               | Positive supply voltage (3.3V) for the QREF_D outputs.                                                                                       |

| 28        | V <sub>DD_QCLKD</sub>   | Power               | Positive supply voltage (3.3V) for the QCLK_D outputs.                                                                                       |

| 29,<br>30 | QCLK_D,<br>nQCLK_D      | Output              | Differential clock output QCLK_D. Configurable LVPECL/LVDS style and amplitude.                                                              |

| 31        | V <sub>DD_QCLKD</sub>   | Power               | Positive supply voltage (3.3V) for the QCLK_D outputs.                                                                                       |

| 32        | V <sub>DD_QREFA01</sub> | Power               | Positive supply voltage (3.3V) for the QREF_A[1:0] outputs.                                                                                  |

| 33,<br>34 | nQREF_A0,<br>QREF_A0    | Output              | Differential SYSREF/clock output QREF_A0. LVDS style for SYSREF operation, configurable LVPECL/LVDS style and amplitude for clock operation. |

| 35,<br>36 | nQREF_A1,<br>QREF_A1    | Output              | Differential SYSREF/clock output QREF_A1. LVDS style for SYSREF operation, configurable LVPECL/LVDS style and amplitude for clock operation. |

| 37        | V <sub>DD_QREFA01</sub> | Power               | Positive supply voltage (3.3V) for the QREF_A[1:0] outputs.                                                                                  |

| 38        | V <sub>DD_QCLKA</sub>   | Power               | Positive supply voltage (3.3V) for the QCLK_A[2:0] outputs.                                                                                  |

#### Table 1. Pin Descriptions (Cont.)

| Number              | Name                   | Туре             | <sub>)</sub> [a] | Description                                                                                                                                                                                                  |

|---------------------|------------------------|------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 39,<br>40           | nQCLK_A0,<br>QCLK_A0   | Output           |                  | Differential clock output QCLK_A0. Configurable LVPECL/LVDS style and amplitude.                                                                                                                             |

| 41,<br>42           | nQCLK_A1,<br>QCLK_A1   | Output           |                  | Differential clock output QCLK_A1. Configurable LVPECL/LVDS style and amplitude.                                                                                                                             |

| 43,<br>44           | nQCLK_A2,<br>QCLK_A2   | Output           |                  | Differential clock output QCLK_A2. Configurable LVPECL/LVDS style and amplitude.                                                                                                                             |

| 45                  | V <sub>DD_QCLKA</sub>  | Power            |                  | Positive supply voltage (3.3V) for the QCLK_A[2:0] outputs.                                                                                                                                                  |

| 46                  | V <sub>DD_QREFA2</sub> | Power            |                  | Positive supply voltage (3.3V) for the QREF_A2 output.                                                                                                                                                       |

| 47,<br>48           | nQREF_A2,<br>QREF_A2   | Output           |                  | Differential SYSREF/clock output QREF_A2. LVDS style for SYSREF operation, configurable LVPECL/LVDS style and amplitude for clock operation.                                                                 |

| 49                  | V <sub>DD_QREFA2</sub> | Power            |                  | Positive supply voltage (3.3V) for the QREF_A2 output.                                                                                                                                                       |

| 50                  | V <sub>DD_REF</sub>    | Power            |                  | Positive supply voltage (3.3V) for the differential SYSREF input REF, nREF                                                                                                                                   |

| 51, 52              | REF, nREF              | Input            |                  | SYSREF inverting and non-inverting differential input. Compatible with LVPECL and LVDS signals. REF and nREF are internally $50\Omega$ terminated to the VTR pin                                             |

| 53                  | VTR                    | -                |                  | Internal termination for the differential clock input REF, nREF. Both REF and nREF inputs are internally terminated 50 $\Omega$ to this pin. See input termination information in Application Information.   |

| 54                  | V <sub>DD_REF</sub>    | Power            |                  | Positive supply voltage (3.3V) for the differential SYSREF input REF, nREF                                                                                                                                   |

| 55                  | RES_CAL                | Analog           |                  | Connect a 2.8 k $\Omega$ (1%) resistor to GND for output current calibration.                                                                                                                                |

| 56                  | V <sub>DD_CLK</sub>    | Power            |                  | Positive supply voltage (3.3V) for the differential device clock input CLK, nCLK.                                                                                                                            |

| 57                  | VTC                    | -                |                  | Internal termination for the differential clock input CLK, nCLK. Both CLK and nCLK inputs are internally $50\Omega$ terminated to the VTR pin. See input termination information in Application Information. |

| 58, 59              | nCLK, CLK              | Input            |                  | Device clock inverting and non-inverting differential clock input. Compatible with LVPECL and LVDS signals. CLK and nCLK are internally terminated to VTC through $50\Omega$ .                               |

| 60                  | V <sub>DD_CLK</sub>    | Power            |                  | Positive supply voltage (3.3V) for the differential device clock input CLK, nCLK.                                                                                                                            |

| 61                  | SDAT                   | Input/<br>Output |                  | Serial Control Port SPI Mode Data Input and Output. 1.8V LVCMOS/LVTTL interface levels. 3.3V tolerant when input.                                                                                            |

| 62                  | SCLK                   | Input            | PD               | Serial Control Port SPI Mode Clock Input. 1.8V LVCMOS/LVTTL interface levels. 3.3V-tolerant when input.                                                                                                      |

| 63                  | nCS                    | Input            | PU               | Serial Control Port SPI Chip Select Input. 1.8V LVCMOS/LVTTL interface levels and 3.3V tolerant.                                                                                                             |

| 64                  | V <sub>DD_SPI</sub>    | Power            |                  | Positive supply voltage (3.3V) for the SPI interface.                                                                                                                                                        |

| Exposed<br>Pad (EP) | GND                    | Power            |                  | Ground supply voltage (GND) and ground return path. Connect to board GND (0V).                                                                                                                               |

[a] Internal pull-up (PU) and pull-down (PD) resistors are indicated in parentheses. See Table 22 for values.

# **Principles of Operation**

### Overview

The 8V79S680 is a JESD204B Fanout Buffer with Configurable Phase Delay. The device supports the division, phase-delay and distribution of high-frequency clocks (input: CLK, nCLK) and the fanout and phase-delay of low-frequency synchronization (SYSREF) signals (input: REF/nREF). Clock and SYSREF signal paths are independent and are organized in channels, with each channel consisting of several clock and SYSREF outputs. Outputs are configurable with support for LVPECL, LVDS and four amplitude settings. Individual channels and unused circuit blocks support a powered-down state for reduced power consumption operation. The register map, accessible through a SPI interface with read-back capability controls the main device settings.

## Signal Flow

The device offers four channels with the names A, B, C and D. Each channel supports individual frequency-division, phase-delay and fan-out functions of the input clock to a total of eight QCLK\_y clock outputs; each channel also distributes the SYSREF input signal to multiple QREF\_r outputs with individual per-output phase delay capability.

The central clock distribution ensures low skew clock outputs within each channel; outputs are synchronous across channels (independent on the divider setting) on the incident rising clock edge for all outputs with equal phase delay settings.

SYSREF output are synchronous with each other for equal phase-delay settings. QCLK\_y and QREF\_r outputs will be phase-locked to each other if the CLK and REF inputs are phase-locked. The phase-delay capability in each signal path can be used to establish repeatable and deterministic clock to SYSREF phase relationships at the outputs.

The CLK and QREF signal paths are optimized for channel isolation. allowing high-speed clocks of 983.04MHz, 1474.56MHz or 1966.08MHz (up to 3GHz) and lower-speed SYSREF signals at e.g. 7.68MHz or 9.6MHz with a minimum of signal crosstalk and spurious signals.

## **Clock Channel Divider**

Each of the four independent frequency dividers  $N_A$ - $N_D$  can be individually set to the divider values  $\div 1$ ,  $\div 2$ ,  $\div 4$ ,  $\div 6$ ,  $\div 8$ ,  $\div 12$ ,  $\div 16$ . The dividers are synchronous and have an equal propagation delay on the incident edge. See Table 2 for the supported frequency divider settings.

| N <sub>A-D</sub> | Clock Divider                         |

|------------------|---------------------------------------|

| 000              | ÷1<br>Divider bypass and powered down |

| 001              | ÷2                                    |

| 010              | ÷4                                    |

| 011              | ÷6                                    |

| 100              | ÷8                                    |

| 101              | ÷12                                   |

| 110              | ÷16                                   |

| 111              | Not defined                           |

#### Table 2. N<sub>A-D</sub> Frequency Divider Settings

## Phase Delay

Output phase delay is independently supported on each clock channel and each SYSREF output. The delay unit of the clock channel phase-delay circuits  $\Phi_{CLK}$  is a function of the frequency  $f_{IN}$  applied to CLK input: 1 ÷  $f_{IN}$ .

The delay unit of the SYSREF phase-delay circuits  $\Phi_{REF_r}$  is a function of an internal oscillator frequency  $f_{DCO}$  and the DLC multiplier setting. The oscillator is fully self-contained and located in delay calibration block (DCB). At startup, this oscillator is calibrated with the input frequency  $f_{IN}$  as reference. After the calibration, the oscillator is turned-off to save power and to eliminate noise. See Table 3 for details on the delay unit, number of available steps and the delay range.

Table 3. Delay Circuit Characteristics

| Delay Circuit                | Unit                                   | Steps | Range                                       |

|------------------------------|----------------------------------------|-------|---------------------------------------------|

| Clock channel $\Phi_{CLK_x}$ | 1 ÷ f <sub>IN</sub>                    | 256   | 256 ÷ f <sub>IN</sub> <sup>[a]</sup>        |

|                              | 1.017ns at f <sub>IN</sub> = 983.04MHz |       | 0 to 259.3ns at f <sub>IN</sub> = 983.04MHz |

| SYSREF $\Phi_{REF_r}$        | T <sub>DCB</sub> <sup>[b]</sup>        | 8     | 07 * T <sub>DCB</sub> <sup>[c]</sup>        |

|                              | DLC = 0: 131ps                         |       | DLC = 0: 0 to 0.917ns                       |

|                              | DLC = 1: 262ps                         |       | DLC = 1: 0 to 1.834ns                       |

|                              | DLC = 2: 393ps                         |       | DLC = 2: 0 to 2.751ns                       |

|                              | DLC = 3: 524ps                         |       | DLC = 3: 0 to 3.668ns                       |

[a] At f<sub>IN</sub> = 983.04MHz, the clock channel delay range is equal to 260.416ns and encompasses 32 periods of a 122.88MHz clock signal.

[b]  $T_{DCB} \sim DLC \div (8 \cdot f_{DCO})$ .  $f_{DCO} = 983.04 \text{MHz}$ . DLC = 1, 2, 3 or 4.

[c] SYSREF phase delay supports  $\ge$ 8 delay stops within one input reference period for f<sub>IN</sub> = 254.76MHz to f<sub>IN</sub> = 983.04MHz.

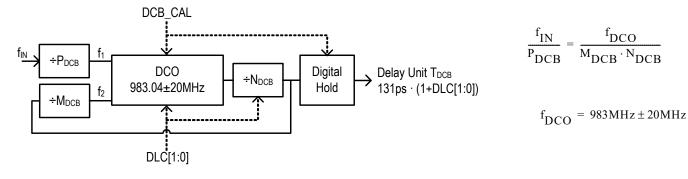

### **Delay Calibration Block (DCB)**

The DCB sets the *SYSREF* delay unit by providing a reference signal to the QREF\_*r* delay circuits. Figure 3 shows the functional diagram. The DCB requires configuration and calibration. Verification of the calibration is optional.

Description. The DCB consists of an internal DCO running at  $f_{DCO} = 983.04 \pm 20$ MHz, three frequency dividers P<sub>DCB</sub>, M<sub>DCB</sub> and N<sub>DCB</sub> and a digital hold circuit. The DCB input frequency is the device input frequency  $f_{IN}$  at the differential CLK, nCLK input. The input frequency acts as a reference to lock the oscillator to a stable and known frequency.

The output of the DCB is the effective delay unit  $T_{DCB}$  which is approx. one eighth of the oscillator period multiplied by the DLC multiplier. The DLC multiplier extends the delay unit by a factor of 1, 2, 3 or 4. For instance, at a DCO frequency of 983.04MHz, DLC = 1 sets the SYSREF delay unit to 131ps; DLC = 2 sets the delay unit to 262ps, etc.

Configuration. Select a desired delay unit and corresponding DLC multiplier from Table 4. DLC[1:0] also sets the N<sub>DCB</sub> divider. Then, find a P<sub>DCB</sub> and M<sub>DCB</sub> divider configuration to locate the oscillator frequency into the range of  $f_{DCO}$  = 983.04MHz according to the formula in Figure 3. The DCO lock condition is  $f_1 = f_2$  while both  $f_1$  and  $f_2$  must be lower than 200MHz. For instance, if  $f_{IN}$  = 245.76MHz and the smallest possible SYSREF delay unit is desired, set DLC = 1 (DLC[1:0] = 00; also sets N<sub>DCB</sub> = ÷1). Then, set P<sub>DCB</sub> = ÷24 and M<sub>DCB</sub> = ÷96. As a result,  $f_1 = f_2 = 10.24$ MHz,  $f_{DCO} = 983.04$ MHz. This example configuration results in a delay unit of measured: 131ps. Figure 5 shows more configuration examples.

Calibration. Calibration requires a valid DCB configuration with the DCO locking to an input frequency. Setting DCB\_CAL = 1 starts an automatic calibration. At the end, the DCB\_CAL bit will clear, the delay unit value is stored digitally and the DCO,  $P_{DCB}$ ,  $M_{DCB}$  and  $N_{DCB}$  frequency dividers turn off. The QREF\_r delay circuits now use the stored constant delay unit. The delay unit remains digitally stored until the next power cycle. The DCB calibration must run once as part of the device startup procedure and must be re-run after each input frequency or DCB configuration change.

Verification. Verify a successful calibration by reading the DAC\_CODE value.  $0 < DAC_CODE < 32767$  indicates a successful calibration. If DAC\_CODE = 0 or DAC\_CODE = 32767, the DCB calibration should be re-run with an alternative  $P_{DCB}$ ,  $M_{DCB}$  setting while maintaining the desired  $M_{DCB} \cdot N_{DCB}/P_{DCB}$  ratio for locking the DCO to the input frequency.

#### Figure 3. DCB Functional Diagram

#### Table 4. DCB Delay Unit at f<sub>DCO</sub> = 983.04MHz

| T                                   | DLC              |               |                  |  |  |  |  |

|-------------------------------------|------------------|---------------|------------------|--|--|--|--|

| T <sub>DCB</sub><br>Delay Unit (ps) | DLC[1:0] Setting | Numeric Value | N <sub>DCB</sub> |  |  |  |  |

| 131                                 | 00               | 1             | 1                |  |  |  |  |

| 262                                 | 01               | 2             | 2                |  |  |  |  |

| 393                                 | 10               | 3             | 3                |  |  |  |  |

| 524                                 | 11               | 4             | 4                |  |  |  |  |

#### Table 5. DCB Divider Configuration Examples<sup>[a]</sup>

| f <sub>IN</sub> (MHz) | T <sub>DCB</sub><br>Delay Unit in ps | DLC | P <sub>DCB</sub> | M <sub>DCB</sub> |

|-----------------------|--------------------------------------|-----|------------------|------------------|

|                       | 131                                  | 1   | 24               | 96               |

| 245.76                | 262                                  | 2   | 24               | 48               |

| 245.76                | 393                                  | 3   | 24               | 32               |

|                       | 524                                  | 4   | 24               | 24               |

|                       | 131                                  | 1   | 48               | 96               |

| 401.52                | 262                                  | 2   | 48               | 48               |

| 491.52                | 393                                  | 3   | 48               | 32               |

|                       | 524                                  | 4   | 48               | 24               |

|                       | 131                                  | 1   | 96               | 96               |

| 092.04                | 262                                  | 2   | 96               | 48               |

| 983.04                | 393                                  | 3   | 96               | 32               |

|                       | 524                                  | 4   | 96               | 24               |

[a] f<sub>DCO</sub> = 983.04MHz.

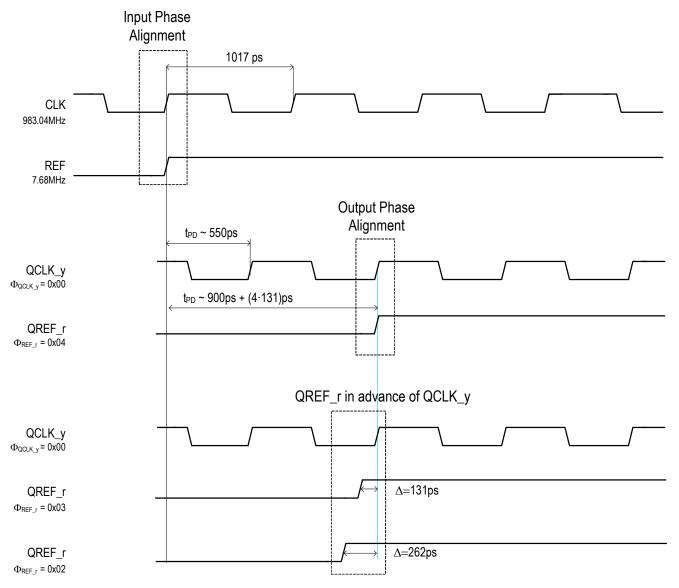

### **QCLK to SYSREF Phase Alignment**

To achieve an output phase alignment between the QCLK\_y clock and the QREF\_rSYSREF outputs, the CLK and REF input signals must be phase aligned or have a known, deterministic phase relationship. Figure 4 shows an example output phase alignment for aligned clock and SYREF inputs. The closest (smallest phase error) output alignment is achieved by setting the clock phase delay register  $\Phi_{QCLK_Y}$  to 0x00 (clock) and the SYSREF phase delay register  $\Phi_{QCLK_Y}$  to 0x04. With a SYSREF phase delay setting of 0x03 or less, the QREF\_r output phase is in advance of the QCLK\_y phase, which is applicable in JESD204B application. Phase delay settings and propagation delays are independent on the clock and SYSREF frequencies. Table 6 shows recommended phase delay setting several device configurations.

#### Table 6. Recommended Delay Settings for Closest Clock-SYSREF Output Phase Alignment<sup>[a]</sup>

| Divider Configuration | ФCLK_у | ΦREF_r |  |

|-----------------------|--------|--------|--|

| N = ÷1                | 0x00   | 0x04   |  |

[a] QCLK and QREF outputs are aligned on the incident edge.

## **Differential Outputs**

#### Table 7. Output Features

| Output                                           | Style  | Ampl. <sup>[a]</sup> | Disable | Power Down | DC Bias            | Termination                                  |

|--------------------------------------------------|--------|----------------------|---------|------------|--------------------|----------------------------------------------|

| QCLK_y <sup>[b]</sup> ,<br>QREF_r <sup>[c]</sup> | LVPECL | 250-1000mV           |         |            |                    | 50 $\Omega$ to V <sub>T</sub> <sup>[d]</sup> |

| (Clock)                                          |        |                      | Yes     | Yes        | _                  | 100 $\Omega$ differential <sup>[e][f]</sup>  |

| QREF_r                                           | LVPECL | 250-1000mV           | Yes     | Yes        | -                  | 50 $\Omega$ to V <sub>T</sub> <sup>[d]</sup> |

| (SYSREF)                                         | LVDS   | 4 steps              | 165     | 165        | Yes <sup>[g]</sup> | 100 $\Omega$ differential <sup>[e] [f]</sup> |

[a] Amplitudes are measured single-ended. Differential amplitudes supported are 500mV, 1000mV, 1500mV and 2000mV.

[b] y = A0, A1, A2, B0, B1, C0, C1 and D.

[c] r = A0, A1, A2, B0, B1, C0, C1 and D.

[d]  $V_T = V_{DD_V} - 1.5V$  (250mV amplitude setting),  $V_{DD_V} - 1.75V$  (500mV amplitude setting),  $V_{DD_V} - 2.0V$  (750mV amplitude setting),  $V_{DD_V} - 2.25V$  (1000mV amplitude setting).

[e] AC coupling and DC coupling supported.

[f] See Application Information for output termination information.

[g] In JESD204B applications, it is recommended to use QREF\_r (SYSREF) outputs configured to LVDS and 500mV amplitude. AC-coupling and DC-coupling is supported.

#### Table 8. Individual Clock Output (QCLK\_y) Settings<sup>[a]</sup>

| PD | STYLE | EN | A[1:0] | Output Power | Termination <sup>[b]</sup>                         | State                  | Amplitude (mV) |

|----|-------|----|--------|--------------|----------------------------------------------------|------------------------|----------------|

| 1  | Х     | Х  | Х      | Off          | 100 $\Omega$ differential (LVDS) or no termination | Off                    | Х              |

|    |       | 0  | XX     |              |                                                    | Disable <sup>[c]</sup> | Х              |

|    |       |    | 00     |              |                                                    |                        | 250            |

|    | 0     | 1  | 01     |              | 100 $\Omega$ differential (LVDS)                   | Enable                 | 500            |

|    |       |    | 10     |              |                                                    |                        | 750            |

| 0  |       |    | 11     | On           |                                                    |                        | 1000           |

| 0  |       | 0  | XX     | Oli          |                                                    | Disable                | Х              |

|    |       | 1  | 00     |              |                                                    | Enable                 | 250            |

|    | 1     |    | 01     |              | 50 $\Omega$ to V_T (LVPECL)                        |                        | 500            |

|    |       |    | 10     |              |                                                    |                        | 750            |

|    |       |    | 11     |              |                                                    |                        | 1000           |

[a] Applicable to clock outputs: QCLK\_y and QREF\_r outputs in clock mode (MUX\_r = 0).

[b] See Application Information for output termination information.

[c] Differential output is disabled in static low state:  $QCLK_y = L$ ,  $nQCLK_y = H$ .

| PD | STYLE | Enable    | A[1:0] | nBIAS | Output<br>Power | Termination <sup>[b]</sup>                 | State                  | Amplitude (mV) |   |  |                                  |              |     |  |

|----|-------|-----------|--------|-------|-----------------|--------------------------------------------|------------------------|----------------|---|--|----------------------------------|--------------|-----|--|

| 1  | х     | х         | Х      | Х     | Off             | $100\Omega$ differential or no termination | Off                    | Х              |   |  |                                  |              |     |  |

|    |       | 0         | XX     | 0     |                 |                                            | Disable <sup>[c]</sup> | Х              |   |  |                                  |              |     |  |

|    | 0     |           | 00     | 0     |                 |                                            | Enabled                | 250            |   |  |                                  |              |     |  |

|    |       | 1         |        |       |                 |                                            |                        | 01             | 0 |  | 100 $\Omega$ differential (LVDS) | See Table 10 | 500 |  |

|    |       |           | 01     | 1     |                 | 10022 dillerential (LVD3)                  | 0                      | 500            |   |  |                                  |              |     |  |

|    |       |           |        |       | 10 0            | Enabled                                    | 750                    |                |   |  |                                  |              |     |  |

| 0  |       |           |        |       |                 |                                            |                        |                |   |  |                                  |              |     |  |

|    |       |           |        | 0 XX  |                 |                                            | Disable                | Х              |   |  |                                  |              |     |  |

|    |       | 1 01 0 50 |        |       | 250             |                                            |                        |                |   |  |                                  |              |     |  |

|    | 1     |           | 01     | 0     |                 | 50 $\Omega$ to V <sub>T</sub> (LVPECL)     | Enable                 | 500            |   |  |                                  |              |     |  |

|    |       | I         | 10     |       |                 |                                            | Ellable                | 750            |   |  |                                  |              |     |  |

|    |       |           | 11     |       |                 |                                            |                        | 1000           |   |  |                                  |              |     |  |

### Table 9. Individual SYSREF Output (QREF\_r) Settings<sup>[a]</sup>

[a] Applicable QREF\_r outputs when configured as SYSREF output (MUX\_r = 1).

[b] See Section "Application Information" on page 41 for output termination information.

[c] Differential output is disabled in static low state:  $QCLK_y = L$ ,  $nQCLK_y = H$ .

|           |                 | QREF_r                                                 |                                                                |                                                                         |                   |  |  |  |

|-----------|-----------------|--------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------|-------------------|--|--|--|

| BIAS_TYPE | nBIAS_ <i>r</i> | Initial                                                | Active Rising Edge on the<br>REF Input                         | SYSREF Completed                                                        | Application       |  |  |  |

|           | 1               | Static                                                 | Static Low (QREF = L, nQREF_r = H)                             |                                                                         |                   |  |  |  |

| 0         | 0               | Static Low<br>(QREF = L, nQREF_ <i>r</i> = H)          | Start switching for the<br>number of received<br>SYSREF pulses | Released to static low<br>(QREF = L, nQREF_ <i>r</i> = H)               | QREF_r DC coupled |  |  |  |

| 1         | 0               | Static LVDS crosspoint level<br>(QREF = nQREF_r = VOS) | Start switching for the<br>number of received<br>SYSREF pulses | Released to static LVDS<br>crosspoint level<br>(QREF = n, QREF_r = VOS) | QREF_rAC coupled  |  |  |  |

|           | 1               | Static LVDS cro                                        | osspoint level (QREF = n, QRI                                  | EF_r = VOS)                                                             |                   |  |  |  |

### Device Startup, Reset, and Synchronization

At startup, an internal POR (power-on reset) resets the device and sets all register bits to its default value. In the default configuration the QCLK\_y and QREF\_r outputs are disabled at startup.

Recommended configuration sequence (in order):

- 1. (Optional) set the value of the CPOL register bit to define the SPI read mode, so that SPI settings can be validated by subsequent SPI read accesses.

- 2. Configure the channel circuits and the outputs to the desired values and configure the DCB:

- Output source MUX\_r, output divider N<sub>A-D</sub>, clock delay Φ<sub>A-D</sub>, MUX-output style, amplitude and power down mode for QCLK\_y and QREF\_r outputs

- For synchronization between multiple devices: Set N<sub>A-D</sub> = ÷1 and set BYP\_INIT = 1)

- (Optional) the global BIAS\_TYPE bit and nBIAS\_r for each QREF\_r in preparation for JESD204B/SYSREF operation

- Setup the DCB settings DLC, P<sub>DCB</sub> and M<sub>DCB</sub> as described in the paragraph *Configuration*, see Delay Calibration Block (DCB)

- If not already applied: apply a valid input frequency to CLK. Set the PB\_CAL bit and the DCB\_CAL bit to start the calibration of the precision bias current circuit and the DCB calibration. Both bits will auto-clear. See paragraph Configuration in section Delay Calibration Block (DCB).

- (Optional): verify the success of the DCB calibration by reading the DAC\_CODE value. See paragraph Verification in section Delay Calibration Block (DCB)

- 4. Set the initialization bit INIT\_CLK. This will initiate the N\_x divider and ΦCLK\_x delay circuits and synchronize them to each other. The INIT\_CLK bit will self-clear.

- 5. At this point, the configuration of the registers 0x00 to 0x73 should be completed and the SPI transfer ended. Set nCS to high level.

- 6. In a separate SPI write access, enable the outputs as desired by accessing the output-enable registers 0x74 and 0x76.

Registers in the address range 0x78 to 0xFF should not be used. Do not write into any registers in the 0x78 to 0xFF range.

#### **Changing Frequency Dividers and Phase Delay Values**

#### Clock Frequency Divider and Delay

Following procedure has to be applied for a change of a clock divider and phase delay value N<sub>A-D</sub>, and  $\Phi_{CLKA-D}$ :

- 1. (Optional) set the value of the CPOL register to define the SPI read mode, so that SPI settings can be validated by subsequent SPI read accesses.

- 2. (Optional) disable the outputs whose frequency divider or delay value is changed.

- 3. Configure the N<sub>A-D</sub> dividers and the delay circuits  $\Phi_{CLKA-D}$  to the desired new values.

- For synchronization between multiple devices: Set N<sub>A-D</sub> = ÷1 and set BYP\_INIT = 1)

- 4. Set the initialization bit INIT\_CLK. This will initiate all divider and delay circuits and synchronize them to each other. The INIT\_CLK bit will self-clear. During this initialization step, all QCLK\_y and QREF\_r outputs are reset to the logic low state.

- 5. (Optional) Enable the outputs whose frequency divider was changed.

#### SYSREF Delay

Following procedure has to be applied for a change of any SYSREF phase delay value  $\Phi_{\mathsf{REF}_r:}$

- 1. (Optional) set the value of the CPOL register to define the SPI read mode, so that SPI settings can be validated by subsequent SPI read accesses.

- 2. Configure any delay circuits  $\Phi_{\mathsf{REF}_f}$  to their desired new values. During configuration of  $\Phi_{\mathsf{REF}_f}$  outputs are not stopped or interrupted.

## SPI Interface

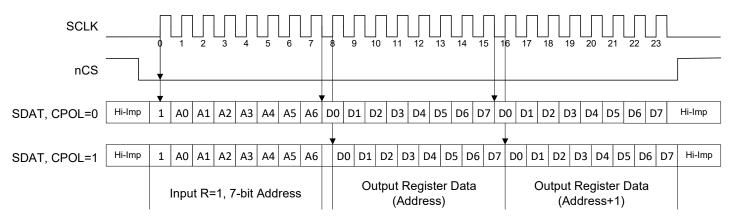

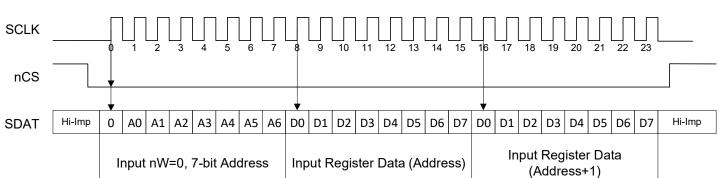

The 8V79S680 has a 3-wire serial control port capable of responding as a slave in an SPI configuration to allow read and write access to any of the internal registers for device programming or read back. The SPI interface consists of the SCLK (clock), SDAT (serial data input and output), and nCS (chip select) pins. A data transfer consists of any integer multiple of 8 bits and is always initiated by the SPI master on the bus. Internal register data is organized in SPI bytes of 8 bits each. If nCS is at logic high, the SDAT data I/O is in high-impedance state and the SPI interface of the 8V79S680 is disabled. In a write operation, data on SDAT will be clocked in on the rising edge of SCLK. In a read operation, data on SDAT will be clocked out on the falling or rising edge of SCLK depending on the CPOL setting (CPOL = 0: output data changes on the falling edge, CPOL = 1: output data changes on the rising edge).

Starting a data transfer requires nCS to set and hold at logic low level during the entire transfer. Setting nCS = 0 will enable the SPI interface with SDAT in data input mode. The master must initiate the first 8-bit transfer. The first bit presented to the slave is the direction bit R/nW (1 = Read,

0 = Write) and the following seven bits are the address bits A[0:6] pointing to an internal register in the address space 0 to 127. Data is presented with the LSB (least significant bit) first.

Read operation from an internal register: a read operation starts with an 8 bit transfer from the master to the slave: SDAT is clocked on the rising edge of SCLK. The first bit is the direction bit R/nW which must be to 1 to indicate a read transfer, followed by 7 address bits A[0:6]. After the first 8 bits are clocked into SDAT, the SDAT I/O changes to output: the register content addressed by A[0:6] is loaded into the shift register and the next 8 SCLK falling clock cycles (if CPOL = 0) will then present the loaded register data on the SDAT output and transfer these to the master. Transfers must be completed by de-asserting nCS after any multiple 8 SCLK cycles. If nCS is de-asserted at any other number of SCLKs, the SPI behavior is undefined. SPI byte (8 bit) and back-to-back read transfers of multiple registers are supported with an address auto-increment. During multiple transfers, nCS must stay at logic low level and SDAT will present multiple registers (A), (A+1), (A+2), etc. with each 8 SCLK cycles. During SPI Read operations, the user may continue to hold nCS low and provide further bytes in a single block read.

Write operation to a 8V79S680 register: During a write transfer, a SPI master transfers one or more bytes of data into the internal registers of the 8V79S680. A write transfer starts by asserting nCS to low logic level. The first bit presented by the master must set the direction bit R/nW to 0 (Write) and the 7 address bits A[0:6] must contain the 7-bit register address. Bits D0 to D7 contain 8 bit of payload data, which is written into the register addressed by A[0:6] at the end of a 8-bit write transfer. Multiple, subsequent register transfers from the master to the slave are supported by holding nCS asserted at logic low level during write transfers. The 7 bit register address will auto-increment. Transfers must be completed by de-asserting nCS after any multiple 8 SCLK cycles. If nCS is de-asserted at any other number of SCLKs, the SPI behavior is undefined.

End of transfer: After de-asserting nCS, the SPI bus is available to transfers to other slaves on the SPI bus. See also the READ diagram (Figure 5) and WRITE diagram (Figure 6) displaying the transfer of two bytes of data from and into registers.

Registers 0x78 to 0xFF: Registers in the address range 0x78 to 0xFF should not be used. Do not write into any registers in the 0x78 to 0xFF range.

#### Figure 5. Logic Diagram: READ Data from 8V79S680 Registers for CPOL = 0 and CPOL = 1

#### Figure 6. Logic Diagram WRITE Data into 8V79S680 Registers

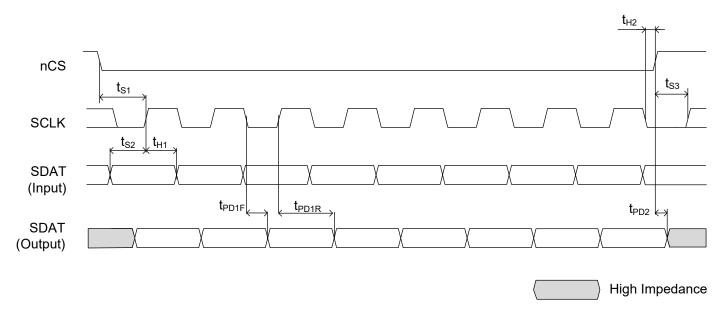

#### Table 11. SPI Read / Write Cycle Timing Parameters

| Symbol            | Parameter                                  | Test Condition | Minimum | Maximum | Unit |

|-------------------|--------------------------------------------|----------------|---------|---------|------|

| f <sub>SCLK</sub> | SCLK frequency                             |                |         | 20      | MHz  |

| t <sub>S1</sub>   | Setup time, nCS (falling) to SCLK (rising) |                | 5       |         | ns   |

| t <sub>S2</sub>   | Setup time, SDAT (input) to SCLK (rising)  |                | 5       |         | ns   |

| t <sub>S3</sub>   | Setup time, nCS (rising) to SCLK (rising)  |                | 5       |         | ns   |

| t <sub>H1</sub>   | Hold time, SCLK (rising) to SDAT (input)   |                | 5       |         | ns   |

| t <sub>H2</sub>   | Hold time, SCLK (falling) to nCS (rising)  |                | 5       |         | ns   |

| t <sub>PD1F</sub> | Propagation delay, SCLK (falling) to SDAT  | CPOL = 0       |         | 12      | ns   |

| t <sub>PD1R</sub> | Propagation delay, SCLK (rising) to SDAT   | CPOL = 1       |         | 12      | ns   |

| t <sub>PD2</sub>  | Propagation delay, nCS to SDAT disable     |                |         | 12      | ns   |

#### Figure 7. SPI Timing Diagram

## **Register Descriptions**

This section contains a list of all addressable registers and a register description, sorted by function, followed for a detailed description of each bit field for each register. Several functional blocks with multiple instances in this device have individual registers controlling their settings, but since the registers have an identical format and bit meaning, they are described only once, but with an additional table to indicate their addresses and default values. All writable register fields will come up with a default values as indicated in the Factory Defaults column unless altered by values loaded from non-volatile storage during the initialization sequence.

Fixed read-only bits will have defaults as indicated in their specific register descriptions. Read-only status bits will reflect valid status of the conditions they are designed to monitor once the internal power-up reset has been released. Unused registers and bit positions are Reserved. Reserved bit fields will be unaffected by writes and are undefined on reads.

| Register Address | Register Description         |  |  |

|------------------|------------------------------|--|--|

| 0x00 - 0x17      | Reserved                     |  |  |

| 0x18 - 0x1B      | SYSREF Control               |  |  |

| 0x1C - 0x1F      | Reserved                     |  |  |

| 0x20             | Channel A, Output Divider    |  |  |

| 0x21             | Channel A Delay $\Phi CLK_A$ |  |  |

| 0x22             | Channel A PD                 |  |  |

| 0x23             | Reserved                     |  |  |

| 0x24             | Output State QCLK_A0         |  |  |

| 0x25             | Output State QCLK_A1         |  |  |

| 0x26             | Output State QCLK_A2         |  |  |

| 0x27             | Reserved                     |  |  |

| 0x28             | $\Phi REF_A0$ Delay, MUX, PD |  |  |

| 0x29             | $\Phi REF_A1$ Delay, MUX, PD |  |  |

| 0x2A             | $\Phi REF_A2$ Delay, MUX, PD |  |  |

| 0x2B             | Reserved                     |  |  |

| 0x2C             | Output State QREF_A0         |  |  |

| 0x2D             | Output State QREF_A1         |  |  |

| 0x2E             | Output State QREF_A2         |  |  |

| 0x2F             | Reserved                     |  |  |

| 0x30             | Channel B, Output Divider    |  |  |

| 0x31             | Channel B Delay $\Phi CLK_B$ |  |  |

| 0x32             | Channel B PD                 |  |  |

| 0x33             | Reserved                     |  |  |

| 0x34             | Output State QCLK_B0         |  |  |

| 0x35             | Output State QCLK_B1         |  |  |

| 0x36 - 0x37      | Reserved                     |  |  |

| 0x38             | $\Phi REF_B0$ Delay, MUX, PD |  |  |

| 0x39             | $\Phi REF_B1$ Delay, MUX, PD |  |  |

#### Table 12. Configuration Registers

| Table 12. | Configuration | Registers | (Cont.) |

|-----------|---------------|-----------|---------|

|-----------|---------------|-----------|---------|

| Register Address | Register Description         |  |  |

|------------------|------------------------------|--|--|

| 0x3A-0x3B        | Reserved                     |  |  |

| 0x3C             | Output State QREF_B0         |  |  |

| 0x3D             | Output State QREF_B1         |  |  |

| 0x3E-0x3F        | Reserved                     |  |  |

| 0x40             | Channel C, Output Divider    |  |  |

| 0x41             | Channel C Delay $\Phi CLK_C$ |  |  |

| 0x42             | Channel C PD                 |  |  |

| 0x43             | Reserved                     |  |  |

| 0x44             | Output State QCLK_C0         |  |  |

| 0x45             | Output State QCLK_C1         |  |  |

| 0x46-0x47        | Reserved                     |  |  |

| 0x48             | $\Phi REF_C0$ Delay, MUX, PD |  |  |

| 0x49             | $\Phi REF_C1$ Delay, MUX, PD |  |  |

| 0x4A-0x4B        | Reserved                     |  |  |

| 0x4C             | Output State QREF_C0         |  |  |

| 0x4D             | Output State QREF_C1         |  |  |

| 0x4E-0x4F        | Reserved                     |  |  |

| 0x50             | Channel D, Output Divider    |  |  |

| 0x51             | Channel D Delay $\Phi CLK_D$ |  |  |

| 0x52             | Channel D PD                 |  |  |

| 0x53             | Reserved                     |  |  |

| 0x54             | Output State QCLK_D          |  |  |

| 0x55-0x57        | Reserved                     |  |  |

| 0x58             | ΦREF_D Delay, MUX, PD        |  |  |

| 0x59-0x5B        | Reserved                     |  |  |

| 0x5C             | Output State QREF_D          |  |  |

| 0x5D-0x6B        | Reserved                     |  |  |

| 0x6C-0x6D        | DAC_CODE                     |  |  |

| 0x6E-0x6F        | General Control              |  |  |

| 0x70             | Reserved                     |  |  |

| 0x71-0x73        | General Control              |  |  |

| 0x74             | Output State QCLK            |  |  |

| 0x75             | Reserved                     |  |  |

| 0x76             | Output State QREF            |  |  |

#### Table 12. Configuration Registers (Cont.)

| Register Address | Register Description |

|------------------|----------------------|

| 0x77             | Reserved             |

| 0x78             | Do not use           |

| 0x79             | Do not use           |

| 0x7A             | Do not use           |

| 0x7B             | Do not use           |

| 0x7C-0x7D        | Do not use           |

| 0x7E             | Do not use           |

| 0x7F             | Do not use           |

| 0x80-0xFF        | Do not use           |

## **Channel and Clock Output Registers**

The content of the channel register and clock output registers set the clock divider, output style, amplitude, power down state, enable state and the clock phase delay.

#### Table 13. Channel and Clock Output Register Bit Field Locations

| Bit Field Location                              |                                                              |                                                                                              |                |                                                          |                                          |                                                                                  |                |               |

|-------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------|----------------------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------|----------------|---------------|

| Register Address                                | D7                                                           | D6                                                                                           | D5             | D4                                                       | D3                                       | D2                                                                               | D1             | D0            |

| 0x20<br>0x30<br>0x40<br>0x50                    | Reserved                                                     | Reserved                                                                                     | Reserved       | Reserved                                                 | Reserved                                 | N_ <i>A</i> [2:0]<br>N_ <i>B</i> [2:0]<br>N_ <i>C</i> [2:0]<br>N_ <i>D</i> [2:0] |                |               |

| 0x21<br>0x31<br>0x41<br>0x51                    |                                                              | ΦCLK_ <i>A</i> [7:0]<br>ΦCLK_ <i>B</i> [7:0]<br>ΦCLK_ <i>C</i> [7:0]<br>ΦCLK_ <i>D</i> [7:0] |                |                                                          |                                          |                                                                                  |                |               |

| 0x22<br>0x32<br>0x42<br>0x52                    | PD_ <i>A</i><br>PD_ <i>B</i><br>PD_ <i>C</i><br>PD_ <i>D</i> | Reserved                                                                                     | Reserved       | Reserved                                                 | Reserved                                 | Reserved                                                                         | Reserved       | Reserved      |

| 0x24: QCLK_A0<br>0x25: QCLK_A1<br>0x26: QCLK_A2 | PD_ <i>A0</i><br>PD_ <i>A1</i><br>PD_ <i>A2</i>              | Reserved                                                                                     | Reserved       | STYLE_ <i>A0</i><br>STYLE_ <i>A1</i><br>STYLE_ <i>A2</i> | A_A                                      | A_ <i>A0</i> [1:0]<br>A_ <i>A1</i> [1:0]<br>A_ <i>A2</i> [1:0]                   |                | erved         |

| 0x34: QCLK_B0<br>0x35: QCLK_B1                  | PD_ <i>B0</i><br>PD_ <i>B1</i>                               | Reserved                                                                                     | Reserved       | STYLE_ <i>B0</i><br>STYLE_ <i>B1</i>                     | A_ <i>B0</i> [1:0]<br>A_ <i>B1</i> [1:0] |                                                                                  | Rese           | erved         |

| 0x44: QCLK_C0<br>0x45: QCLK_C1                  | PD_ <i>C0</i><br>PD_ <i>C1</i>                               | Reserved                                                                                     | Reserved       | STYLE_C0<br>STYLE_C1                                     | A_ <i>C0</i> [1:0]<br>A_ <i>C1</i> [1:0] |                                                                                  | Rese           | erved         |

| 0x54: QCLK_D                                    | PD_D                                                         | Reserved                                                                                     | Reserved       | STYLE_D                                                  | A_ <i>D</i> [1:0]                        |                                                                                  | Rese           | erved         |

| 0x74                                            | EN_QCLK_<br>A0                                               | EN_QCLK_<br>A1                                                                               | EN_QCLK_<br>A2 | EN_QCLK_<br>B0                                           | EN_QCLK_<br>B1                           | EN_QCLK_<br>C0                                                                   | EN_QCLK_<br>C1 | EN_QCLK_<br>D |

## Table 14. Channel and Clock Output Register Descriptions<sup>[a]</sup>

| Register Description |            |                     |                                                                                                                                                                             |                                                                                                              |                                         |  |  |  |

|----------------------|------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------|--|--|--|

| Bit Field Name       | Field Type | Default<br>(Binary) | Description                                                                                                                                                                 |                                                                                                              |                                         |  |  |  |

|                      |            |                     | Output Frequ                                                                                                                                                                | Output Frequency Divider N                                                                                   |                                         |  |  |  |

|                      |            |                     | N_ <i>x</i> [2:0]                                                                                                                                                           | N_x[2:0] Frequency Divider                                                                                   |                                         |  |  |  |

|                      |            |                     | 000                                                                                                                                                                         | ÷1 (Divider bypassed and po                                                                                  | owered-down)                            |  |  |  |

|                      |            |                     | 001                                                                                                                                                                         | ÷2                                                                                                           |                                         |  |  |  |

|                      |            |                     | 010                                                                                                                                                                         | ÷4                                                                                                           |                                         |  |  |  |

|                      |            | 000                 | 011                                                                                                                                                                         | ÷6                                                                                                           |                                         |  |  |  |

| N_ <i>x</i> [2:0]    | R/W        |                     | 100                                                                                                                                                                         | ÷8                                                                                                           |                                         |  |  |  |

|                      |            | Value: +1           | 101                                                                                                                                                                         | ÷12                                                                                                          |                                         |  |  |  |

|                      |            |                     | 110                                                                                                                                                                         | ÷16                                                                                                          |                                         |  |  |  |

|                      |            |                     | 111                                                                                                                                                                         | Not defined                                                                                                  |                                         |  |  |  |

|                      |            |                     |                                                                                                                                                                             | If N_x[2:0] = 000 (÷1), set By initialization.                                                               | YP_INIT = 1 to exclude the divider from |  |  |  |

|                      | D/M        | 0                   | 0 = Channel x is powered up                                                                                                                                                 |                                                                                                              |                                         |  |  |  |

| PD_x                 | R/W        | U                   | 1 = Channel <i>x</i> is powered down                                                                                                                                        |                                                                                                              |                                         |  |  |  |

| PD_y                 | R/W        | 0                   | 0 = Output QCLK_y is powered up                                                                                                                                             |                                                                                                              |                                         |  |  |  |

| FD_ <i>y</i>         | r/w        | U                   | 1 = Output Q                                                                                                                                                                | CLK_y is powered down                                                                                        |                                         |  |  |  |

|                      |            |                     | CLK_x Phase Delay                                                                                                                                                           |                                                                                                              |                                         |  |  |  |

|                      |            | 0000 0000           | ΦCLK_x[7:0]                                                                                                                                                                 | $\Phi$ CLK_x[7:0] Phase Delay in units of the input period: $\Phi$ CLK_x[7:0] ÷ f <sub>IN</sub> (256 steps). |                                         |  |  |  |

| ФСLK_ <i>x</i> [7:0] | R/W        |                     | 0000 0000                                                                                                                                                                   | 000 0000 0ps                                                                                                 |                                         |  |  |  |

| \$0EI(_/[/.0]        | 10,00      | Value: Ons          | 0000 0001                                                                                                                                                                   | 1 ÷ f <sub>IN</sub>                                                                                          |                                         |  |  |  |

|                      |            |                     |                                                                                                                                                                             |                                                                                                              |                                         |  |  |  |

|                      |            |                     | 1111 1111                                                                                                                                                                   | 1111 1111 255 ÷ f <sub>IN</sub>                                                                              |                                         |  |  |  |

|                      |            |                     | QCLK_y Outp                                                                                                                                                                 | out Amplitude                                                                                                |                                         |  |  |  |

|                      |            | 00                  | Setting for ST                                                                                                                                                              | YLE = 0 (LVDS)                                                                                               | Setting for STYLE = 1 (LVPECL)          |  |  |  |

|                      |            | 00                  | Termination:                                                                                                                                                                | 100 $\Omega$ across                                                                                          | Termination: 50 $\Omega$ to VT          |  |  |  |

| A_ <i>y</i> [1:0]    | R/W        | Value:              | A[1:0] = 00: 2                                                                                                                                                              | 50mV                                                                                                         |                                         |  |  |  |

|                      |            | 250mV               | A[1:0] = 01: 5                                                                                                                                                              | 00mV                                                                                                         |                                         |  |  |  |

|                      |            |                     | A[1:0] = 10: 7                                                                                                                                                              | 50mV                                                                                                         |                                         |  |  |  |

|                      |            |                     | A[1:0] = 11:10                                                                                                                                                              | 000mV                                                                                                        |                                         |  |  |  |

|                      |            | 0                   | QCLK_y Outp                                                                                                                                                                 | out Format:                                                                                                  |                                         |  |  |  |

| STYLE_y              |            |                     |                                                                                                                                                                             | LVDS (requires LVDS 100 $\Omega$ o                                                                           | , ,                                     |  |  |  |

|                      |            | Value: LVDS         | $\begin{array}{l} 1 = \text{Output is LVPECL (requires LVPECL 50}\Omega \text{ output termination to the specified} \\ \text{recommended termination voltage)} \end{array}$ |                                                                                                              |                                         |  |  |  |

|                      |            | 0                   | QCLK_y Outp                                                                                                                                                                 | out Enable:                                                                                                  |                                         |  |  |  |

| EN_y                 |            |                     | 0 = QCLK_y                                                                                                                                                                  | Output is disabled at the logic I                                                                            | low state                               |  |  |  |

| L: *_y               |            | Value:<br>disabled  | 1 = QCLK_y                                                                                                                                                                  | Dutput is enabled                                                                                            |                                         |  |  |  |

[a] *x* = A, B, C, D; *y* = A0, A1, A2, B0, B1, C0, C1, D.

## **QREF Output State Registers**

The content of the QREF output registers selects the source signal of the QREF outputs, set the phase delay, the style, the amplitude, the power state, the enable state and the output bias.

#### Table 15. QREF Output State Register Bit Field Locations<sup>[a]</sup>

| Bit Field Location                              |                                                 |                |                                                          |                                                    |                                                                         |                                                |                |               |

|-------------------------------------------------|-------------------------------------------------|----------------|----------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------|----------------|---------------|