# **Description**

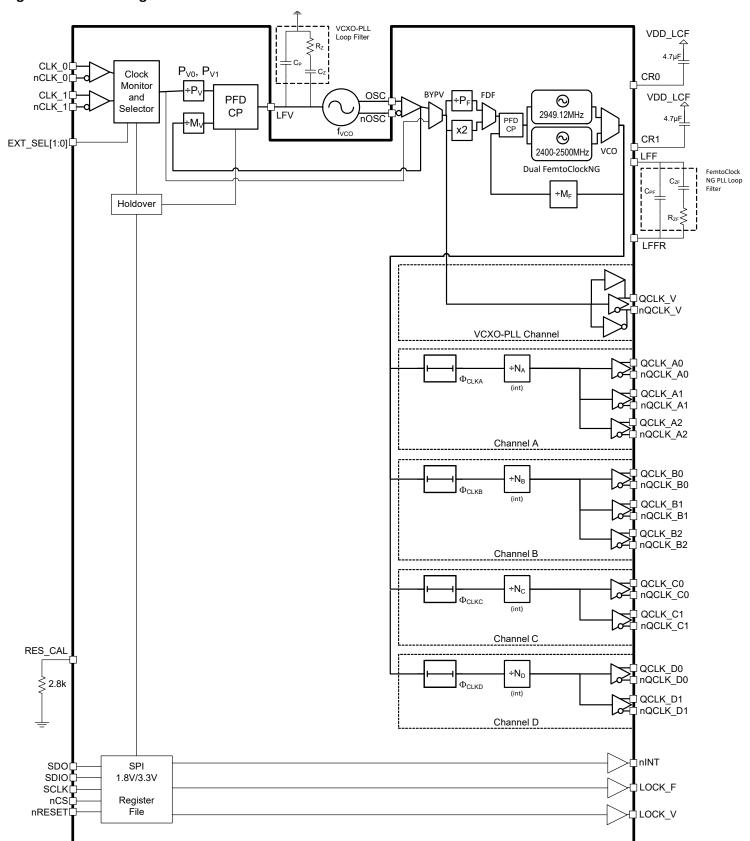

The 8V19N470 is a fully integrated FemtoClock<sup>®</sup> NG jitter attenuator and clock synthesizer designed as a high-performance clock solution for conditioning and frequency/phase management of wireless base station radio equipment boards.

The device is optimized to deliver excellent phase noise performance as required in GSM, WCDMA, LTE, LTE-A radio board implementations. A two-stage PLL architecture supports both jitter attenuation and frequency multiplication. The first stage PLL is the jitter attenuator and uses an external VCXO for best possible phase noise characteristics. The second stage PLL locks on the VCXO-PLL output signal and synthesizes the target frequency. This PLL has two VCO circuits at 2949.12MHz and 2400MHz–2500MHz, respectively, for enhanced frequency flexibility.

The device generates the output clock signals from the selected VCO by frequency division. Four independent integer frequency dividers are available. Delay circuits can be used for achieving alignment and controlled phase delay between clock signals. The two redundant inputs are monitored for activity. Four selectable clock switching modes are provided to handle clock input failure scenarios. Auto-lock, individually programmable output frequency dividers and phase adjustment capabilities are added for flexibility.

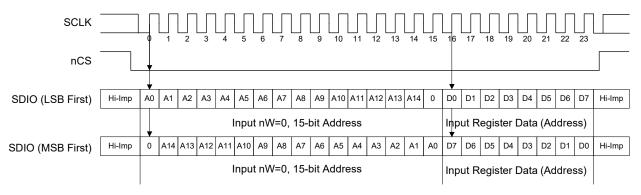

The device is configured through an SPI interface and reports PLL lock and signal loss status in internal registers, PLL lock status is also reported via two lock detect outputs. Internal status bit changes can also be reported via the nINT output. The device is ideal for driving converter circuits in wireless infrastructure, radar/imaging and instrumentation/medical applications. The device is a member of the high-performance clock family from IDT.

# **Typical Applications**

- Low phase noise clock generation, specifically for jitter-sensitive ADC and DAC circuits

- Wireless infrastructure applications: GSM, WCDMA, LTE, LTE-A

- Ethernet

## **Features**

- High-performance clock RF-PLL

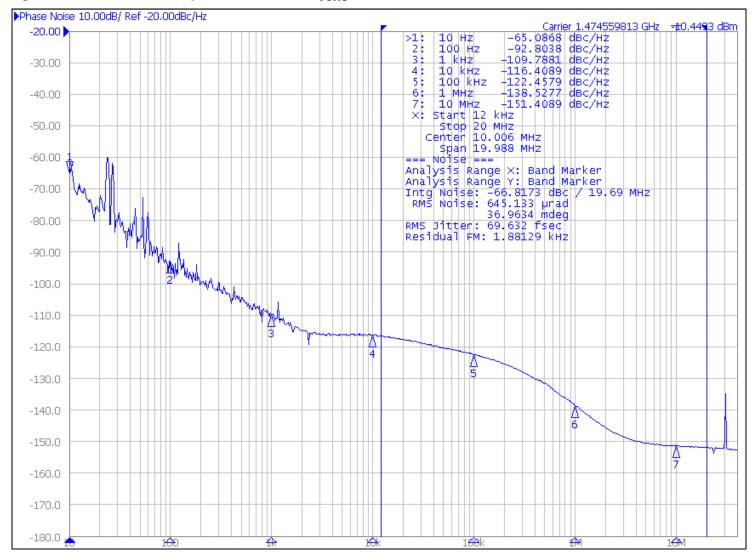

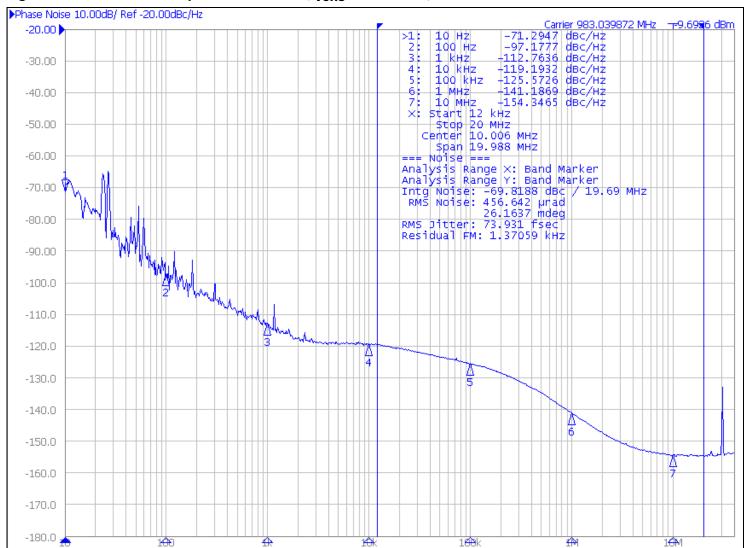

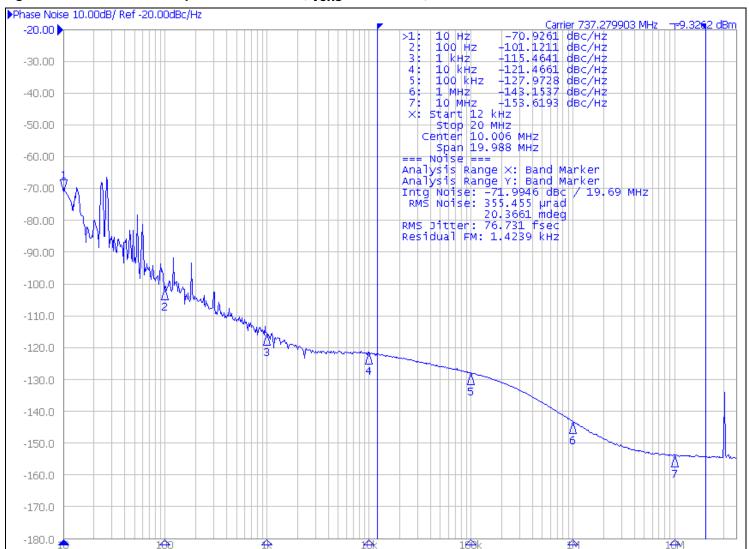

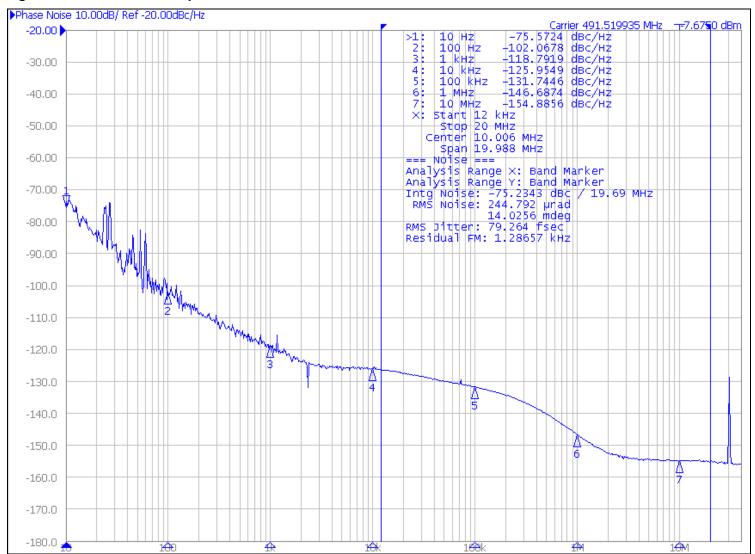

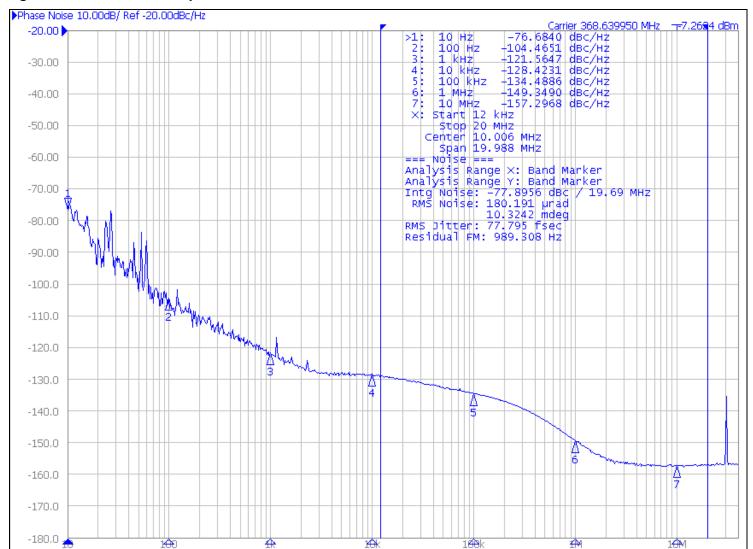

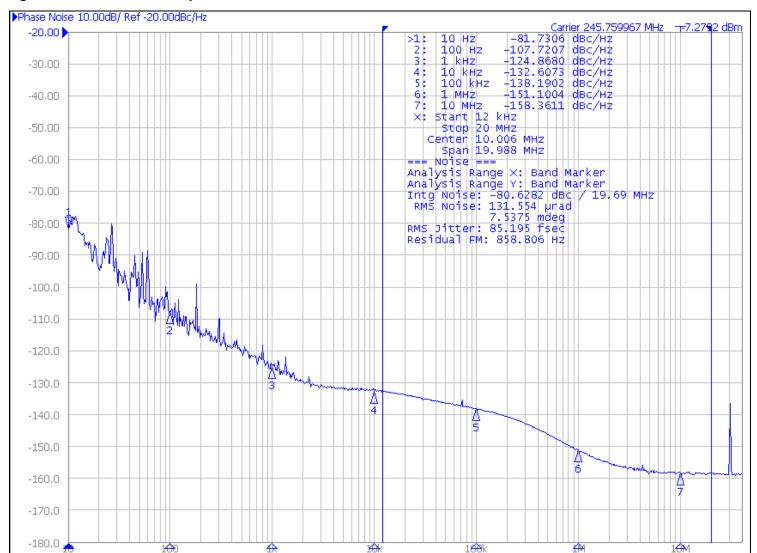

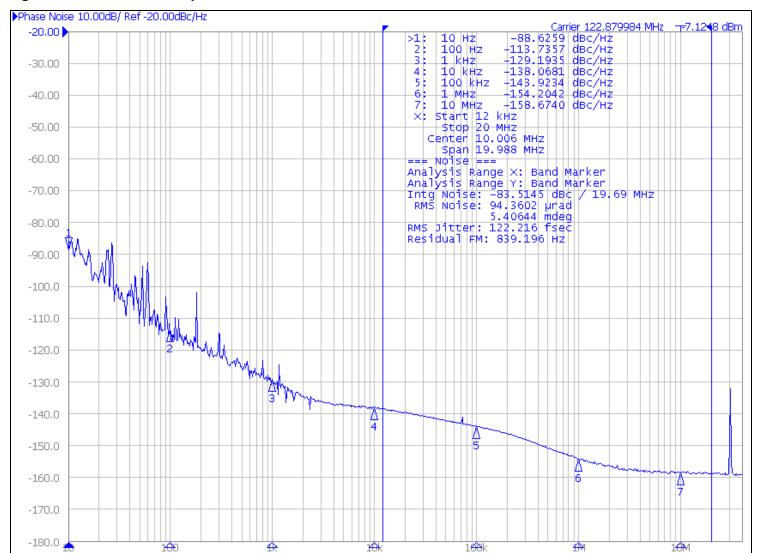

- Optimized for low phase noise: ≤150dBc/Hz (1MHz offset; 245.76MHz clock)

- Dual-PLL architecture

- 1st-PLL stage with external VCXO for clock jitter attenuation

- 2nd-PLL stage with internal FemtoClock NG PLL at selectable 2949.12MHz and 2400MHz – 2500MHz VCO

- Five output channels with a total of 11 outputs, organized in:

- Two clock channels with two differential outputs

- Two clock channels with three differential outputs

- One VCXO-PLL channel with one selectable LVDS/ two LVCMOS outputs

- Each clock channel contains an integer output divider and a phase delay circuit with 512 steps of half of the VCO period

- Supported clock output frequencies include:

- From VCO-0: 2949.12MHz, 1474.56MHz, 983.04MHz, 491.52MHz, 368.64MHz, 122.88MHz

- From VCO-1: 2457.6MHz, 1228.8MHz, 614.4MHz, 307.2MHz, 153.6, 76.8MHz or 625MHz, 500MHz, 312.5MHz, 250MHz, 156.25MHz, and 125MHz

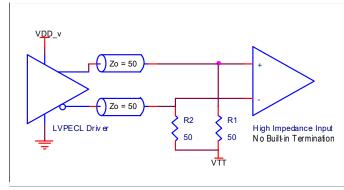

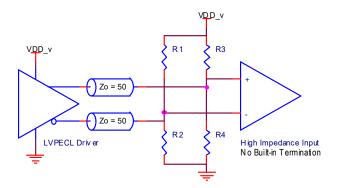

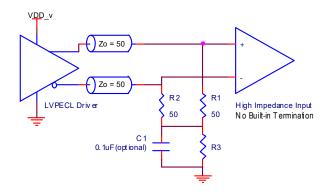

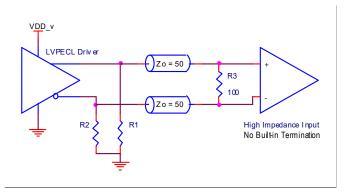

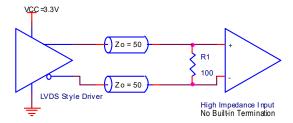

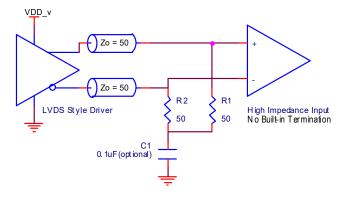

- Low-power LVPECL/LVDS outputs support configurable signal amplitude, DC and AC coupling and LVPECL, LVDS line terminations techniques

- Redundant input clock architecture

- Two inputs

- Individual input signal monitor

- Digital holdover

- Manual and automatic clock selection

- Hitless switching

- Status monitoring and fault reporting

- Input signal status

- Lock status of each individual PLL (two status pins)

- Hold-over and reference loss status

- Mask-able status interrupt pin

- Voltage supply:

- Device core supply voltage: 3.3V

- Output supply voltage: 3.3V, 2.5V or 1.8V

- Digital control I/O voltage: 1.8V (3.3V tolerant)

- SPI control I/O voltage: 1.8V or 3.3V (selectable), 3.3V tolerant inputs when set to 1.8V

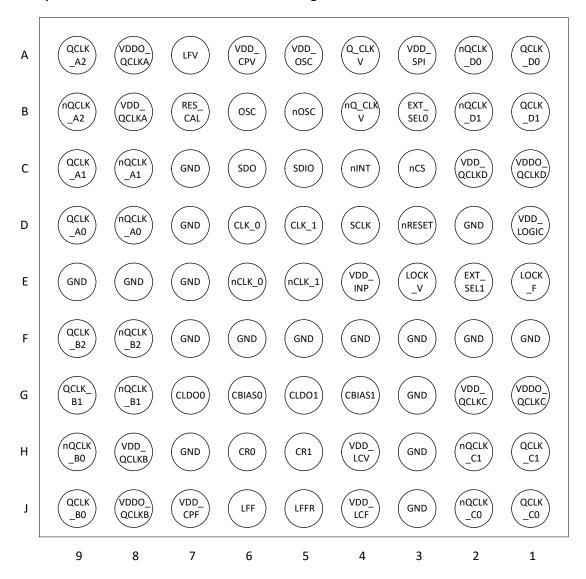

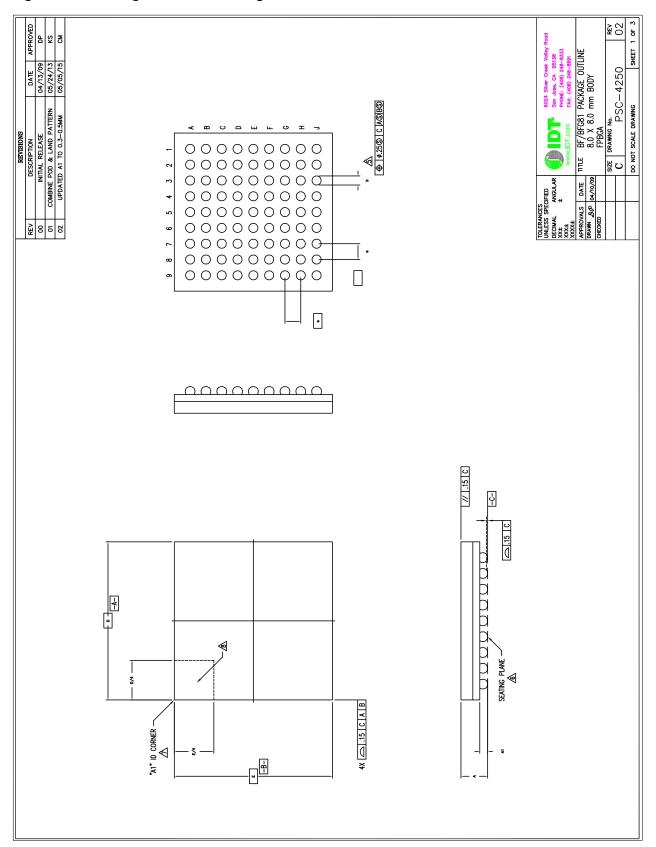

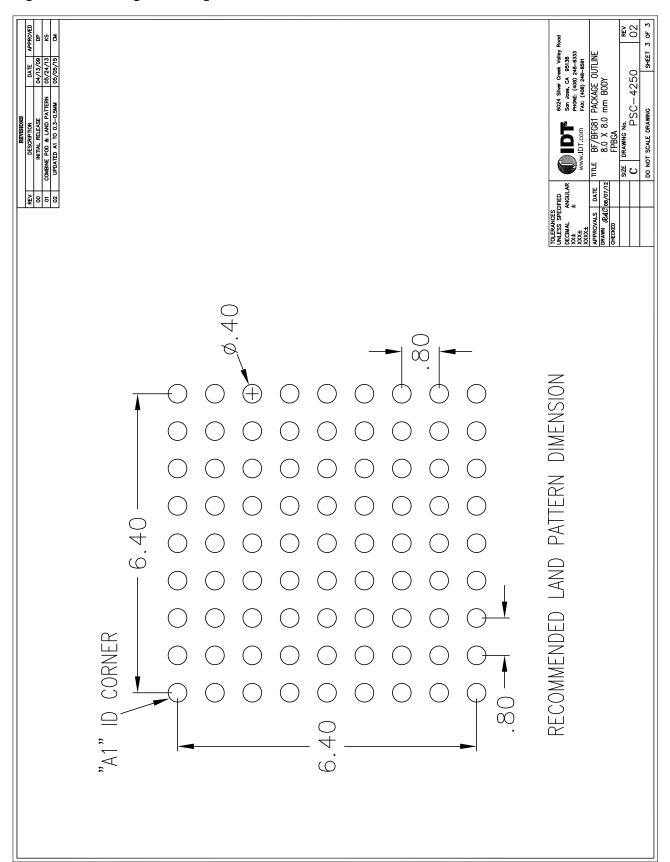

- Package: 81-FPBGA (8 × 8 × 1.35 mm, 0.8mm ball pitch)

- Temperature range: -40°C to +85°C

# **Block Diagram**

Figure 1. Block Diagram

# **Pin Assignments**

Figure 2. Ball Map for  $8 \times 8 \times 1.35$ mm, 81-CABGA Package with 0.8mm Ball Pitch – Bottom View

# **Pin Descriptions**

Table 1. Pin Descriptions<sup>[a]</sup>

| Number    | Name                 | Type <sup>[b]</sup> |       | Description                                                                                                                                            |

|-----------|----------------------|---------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| D6        | CLK_0                |                     | PD    | Device clock 0 inverting and non-inverting differential clock input.                                                                                   |

| E6        | nCLK_0               | Input               | PD/PU | Inverting input is biased to $V_{DD\_V}$ / 2 by default when left floating. Compatible with LVPECL, LVDS and LVCMOS signals.                           |

| D5        | CLK_1                |                     | PD    | Device clock 1 inverting and non-inverting differential clock input.                                                                                   |

| E5        | nCLK_1               | Input               | PD/PU | Inverting input is biased to $V_{DD\_V}$ / 2 by default when left floating. Compatible with LVPECL, LVDS and LVCMOS signals.                           |

| В3        | EXT_SEL0             | Input               | PD    | Clock reference select 0. 1.8V LVCMOS interface levels. 3.3V tolerant.                                                                                 |

| E2        | EXT_SEL1             | Input               | PD    | Clock reference select 1. 1.8V LVCMOS interface levels. 3.3V tolerant.                                                                                 |

| D9,<br>D8 | QCLK_A0,<br>nQCLK_A0 | Output              |       | Differential clock output A0 (Channel A). Configurable LVPECL/LVDS style and amplitude. Output levels are determined by the VDDO_QCLKA supply voltage. |

| C9,<br>C8 | QCLK_A1,<br>nQCLK_A1 | Output              |       | Differential clock output A1 (Channel A). Configurable LVPECL/LVDS style and amplitude. Output levels are determined by the VDDO_QCLKA supply voltage. |

| A9,<br>B9 | QCLK_A2,<br>nQCLK_A2 | Output              |       | Differential clock output A2 (Channel A). Configurable LVPECL/LVDS style and amplitude. Output levels are determined by the VDDO_QCLKA supply voltage. |

| J9,<br>H9 | QCLK_B0,<br>nQCLK_B0 | Output              |       | Differential clock output B0 (Channel B). Configurable LVPECL/LVDS style and amplitude. Output levels are determined by the VDDO_QCLKB supply voltage. |

| G9,<br>G8 | QCLK_B1,<br>nQCLK_B1 | Output              |       | Differential clock output B1 (Channel B). Configurable LVPECL/LVDS style and amplitude. Output levels are determined by the VDDO_QCLKB supply voltage. |

| F9,<br>F8 | QCLK_B2,<br>nQCLK_B2 | Output              |       | Differential clock output B2 (Channel B). Configurable LVPECL/LVDS style and amplitude. Output levels are determined by the VDDO_QCLKB supply voltage. |

| J1,<br>J2 | QCLK_C0,<br>nQCLK_C0 | Output              |       | Differential clock output C0 (Channel C). Configurable LVPECL/LVDS style and amplitude. Output levels are determined by the VDDO_QCLKC supply voltage. |

| H1,<br>H2 | QCLK_C1,<br>nQCLK_C1 | Output              |       | Differential clock output C1 (Channel C). Configurable LVPECL/LVDS style and amplitude. Output levels are determined by the VDDO_QCLKC supply voltage. |

| A1,<br>A2 | QCLK_D0,<br>nQCLK_D0 | Output              |       | Differential clock output D0 (Channel D). Configurable LVPECL/LVDS style and amplitude. Output levels are determined by the VDDO_QCLKD supply voltage. |

| B1,<br>B2 | QCLK_D1,<br>nQCLK_D1 | Output              |       | Differential clock output D1 (Channel D). Configurable LVPECL/LVDS style and amplitude. Output levels are determined by the VDDO_QCLKD supply voltage. |

| A4,<br>B4 | QCLK_V,<br>nQCLK_V   | Output              |       | Differential VCXO-PLL clock outputs. Selectable LVPECL/LVDS/ (2x LVCMOS 1.8V) style.                                                                   |

Table 1. Pin Descriptions<sup>[a]</sup> (Cont.)

| Number                                                                            | Name         | Тур          | e[p] | Description                                                                                                                                                   |

|-----------------------------------------------------------------------------------|--------------|--------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C4                                                                                | nINT         | Output       |      | Status output pin for signaling internal changed conditions. Selectable 1.8V/3.3V LVCMOS interface levels.                                                    |

| E3                                                                                | LOCK_V       | Output       |      | PLL lock detect status output for the VCXO-PLL. Selectable 1.8V/3.3V LVCMOS interface levels.                                                                 |

| E1                                                                                | LOCK_F       | Output       |      | PLL lock detect status output for the FemtoClock NG PLL. Selectable 1.8V/3.3V LVCMOS interface levels.                                                        |

| C5                                                                                | SDIO         | Input/Output |      | Serial Control Port SPI Mode Clock Input/Output. Selectable 1.8V/3.3V LVCMOS interface levels for output. 1.8V interface levels (with hysteresis) when input. |

| C6                                                                                | SDO          | Output       |      | Serial Control Port SPI Mode Output. Selectable 1.8V/3.3V LVCMOS interface levels.                                                                            |

| D4                                                                                | SCLK         | Input        | PD   | Serial Control Port SPI Clock. electable 1.8V interface levels (with hysteresis). 3.3V tolerant.                                                              |

| C3                                                                                | nCS          | Input        | PU   | Serial Control Port SPI Chip Select Input.  1.8V interface levels (with hysteresis). 3.3V tolerant.                                                           |

| D3                                                                                | nRESET       | Input        | PU   | SPI interface reset. 1.8V interface levels. 3.3V tolerant.                                                                                                    |

| H6                                                                                | CR0          | Analog       |      | Internal VCO (0) regulator bypass capacitor. Use a 4.7 µF capacitor between the CR0 and the VDD_LCF terminals.                                                |

| H5                                                                                | CR1          | Analog       |      | Internal VCO (1) regulator bypass capacitor. Use a 4.7 µF capacitor between the CR1 and the VDD_LCF terminals.                                                |

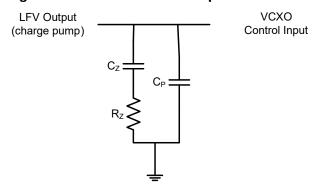

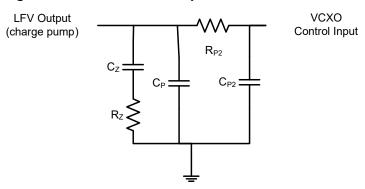

| A7                                                                                | LFV          | Output       |      | VCXO-PLL charge pump output. Connect to the loop filter for the external VCXO.                                                                                |

| B6,<br>B5                                                                         | OSC,<br>nOSC | Input        |      | VCXO non-inverting and inverting differential clock input. Compatible with LVPECL, LVDS and LVCMOS signals.                                                   |

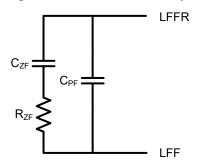

| J6                                                                                | LFF          | Output       |      | Loop filter/charge pump output for the FemtoClock NG PLL. Connect to the external loop filter.                                                                |

| J5                                                                                | LFFR         | Analog       |      | Ground return path pin for the VCO loop filter.                                                                                                               |

| B7                                                                                | RES_CAL      | Analog       |      | Connect a 2.8 kΩ (1%) resistor to GND for output current calibration.                                                                                         |

| C7, D2, D7,<br>E7, E8, E9,<br>F1, F2, F3,<br>F4, F5, F6,<br>F7, G3, H3,<br>H7, J3 | GND          | Power        |      | Ground supply voltage (GND) and ground return path. Connect to board GND (0V).                                                                                |

| G4                                                                                | CBIAS1       | Analog       |      | Internal bias circuit for VCO-1. Connect a 4.7µF capacitor to GND.                                                                                            |

| G5                                                                                | CLDO1        | Analog       |      | Internal LDO bypass for VCO-1. Connect a 10µF capacitor to GND.                                                                                               |

| G6                                                                                | CBIAS0       | Analog       |      | Internal bias circuit for VCO-0. Connect a 4.7µF capacitor to GND.                                                                                            |

| G7                                                                                | CLDO0        | Analog       |      | Internal LDO bypass for VCO-0. Connect a 10µF capacitor to GND.                                                                                               |

| A8                                                                                | VDDO_QCLKA   | Power        |      | Positive supply voltage (3.3V, 2.5V or 1.8V) for the QCLK_A[2:0] outputs.                                                                                     |

Table 1. Pin Descriptions<sup>[a]</sup> (Cont.)

| Number | Name       | Type <sup>[b]</sup> | Description                                                                                                                                                           |

|--------|------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B8     | VDD_QCLKA  | Power               | Positive supply voltage (3.3V) for channel A.                                                                                                                         |

| J8     | VDDO_QCLKB | Power               | Positive supply voltage (3.3V, 2.5V or 1.8V) for the QCLK_B[2:0] outputs.                                                                                             |

| H8     | VDD_QCLKB  | Power               | Positive supply voltage (3.3V) for channel B.                                                                                                                         |

| G1     | VDDO_QCLKC | Power               | Positive supply voltage (3.3V, 2.5V or 1.8V) for the QCLK_C[1:0] outputs.                                                                                             |

| G2     | VDD_QCLKC  | Power               | Positive supply voltage (3.3V) for channel C.                                                                                                                         |

| C1     | VDDO_QCLKD | Power               | Positive supply voltage (3.3V, 2.5V or 1.8V) for the QCLK_D[1:0] outputs.                                                                                             |

| C2     | VDD_QCLKD  | Power               | Positive supply voltage (3.3V) for channel D.                                                                                                                         |

| D1     | VDD_LOGIC  | Power               | Positive supply voltage (3.3V).                                                                                                                                       |

| A3     | VDD_SPI    | Power               | Positive supply voltage (3.3V) for the SPI interface.                                                                                                                 |

| E4     | VDD_INP    | Power               | Positive supply voltage (3.3V) for the differential inputs (CLK[1:0]).                                                                                                |

| H4     | VDD_LCV    | Power               | Positive supply voltage (3.3V) for the VCXO-PLL.                                                                                                                      |

| J4     | VDD_LCF    | Power               | Positive supply voltage (3.3V) for the internal oscillator of the FemtoClock NG PLL. For essential information on power supply filtering, see Power Supply Filtering. |

| A6     | VDD_CPV    | Power               | Positive supply voltage (3.3V) for internal VCXO_PLL circuits.                                                                                                        |

| J7     | VDD_CPF    | Power               | Positive supply voltage (3.3V) for internal FemtoClock NG circuits.                                                                                                   |

| A5     | VDD_OSC    | Power               | Positive supply voltage (3.3V) for the VCXO input.                                                                                                                    |

<sup>[</sup>a] For essential information on power supply filtering. See Power Supply Filtering.

<sup>[</sup>b] PU (pull-up) and PD (pull-down) indicate internal input resistors. For values (see Table 46).

# **Principles of Operation**

### Overview

The device generates low-phase noise, synchronized clock output signals locked to an input reference frequency. The device contains two PLLs with configurable frequency dividers. The first PLL (VCXO-PLL, suffix V) uses an external VCXO as the oscillator and provides jitter attenuation. The external loop filter is used to set the VCXO-PLL bandwidth frequency in conjunction with internal parameters. The second, low-phase noise PLL (FemtoClock NG, suffix F) multiplies the VCXO-PLL frequency to one of its two selectable VCO frequencies of 2949.12MHz or 2457.6MHz. The FemtoClock NG PLL is completely internal and provides a central reference timing reference point for all output signals. From this point, fully synchronous dividers generate the output frequencies. The device has four output channels A – D, each with one integer output divider A – D. The clock outputs are configurable with support for LVPECL, LVDS formats and a variable output amplitude. In channels A – D, the clock phase can be adjusted in phase. For reduced power consumption, individual outputs, channels and unused circuit blocks support a power-down state. The register map, accessible through a selectable 3/4-wire SPI interface with read-back capability controls the main device settings and delivers device status information. For redundancy purpose, there are two selectable reference frequency inputs and a configurable switch logic with manual, auto-selection and holdover support.

## **Phase-Locked Loop Operation**

## **Frequency Generation**

Table 2 displays the available frequency dividers for clock generation. The dividers must be set by the user to match input, VCXO and VCO frequency and to achieve frequency and phase lock on both PLLs. The frequency of the external VCXO is chosen by the user, the internal VCO frequency can be selected at frequencies of 2949.12MHz or 2457.6MHz. Table 3 – Table 7 shows example divider configurations for typical wireless infrastructure applications.

**Table 2. PLL Divider Values**

|                                                       |                    | Operation                                                                                         |                                                                                                   |  |

|-------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--|

| Divider                                               | Range              | Jitter Attenuation<br>(Dual PLL, BYPV = 0)                                                        | Frequency Synthesis<br>(VCXO-PLL bypassed, BYPV = 1)                                              |  |

| VCXO-PLL<br>Pre-Divider P <sub>V</sub> <sup>[a]</sup> | ÷1÷32767: (15-bit) | Input clock frequency:                                                                            | No external VCXO required                                                                         |  |

| VCXO-PLL Feedback<br>Divider M <sub>V</sub>           | ÷1÷32767: (15-bit) | $f_{CLK} = P_V \times \frac{f_{VCXO}}{M_V}$                                                       |                                                                                                   |  |

|                                                       |                    | VCXO frequency:                                                                                   | Input clock frequency:                                                                            |  |

| FemtoClock NG<br>Pre-Divider P <sub>F</sub>           | ÷1÷63: (6-bit)     | $f_{VCXO} = \frac{P_F}{M_F} \times f_{VCO}$                                                       | $f_{CLK} = \frac{P_F}{M_F} \times f_{VCO}$                                                        |  |

| FemtoClock NG<br>Feedback Dividers M <sub>F</sub>     | ÷8÷511 (9-bit)     | f <sub>VCO</sub> = 2949.12MHz or 2457.6MHz                                                        | f <sub>VCO</sub> = 2949.12MHz or 2457.6MHz                                                        |  |

|                                                       |                    | $P_F$ : Set $P_F$ to 0.5 in above equation if the frequency doubler is engaged by setting FDF = 1 | $P_F$ : Set $P_F$ to 0.5 in above equation if the frequency doubler is engaged by setting $FDF=1$ |  |

| Output Divider Nx,                                    | ÷1÷160             | Output frequency                                                                                  |                                                                                                   |  |

| x = A - D                                             |                    | $f_{OUT} = \frac{f_{VCO}}{N_X}$                                                                   |                                                                                                   |  |

<sup>[</sup>a] P<sub>V</sub> divider settings are in the *PV0 register* (for CLK\_0) and in the *PV1 register* (for CLK\_1). The device loads the PV *divider* from PV0 or PV1 according to the input selection. For details (see Table 13).

#### **VCXO-PLL**

The prescaler  $P_V$  and the VCXO-PLLs feedback divider  $M_V$  require configuration to match the input frequency to the VCXO-frequency. With a  $M_V$  and  $P_V$  divider value range of 15 bits, the device supports a wide range of input and VCXO-frequencies. Two different input frequencies may be applied to the clock inputs CLK\_0 and CLK\_1. The single  $P_V$  divider has two correspond divider registers, PV0 and PV1. PV0 is loaded into the PV divider when the CLK\_0 input is selected and PV1 is loaded into the PV divider with the selection of the CLK\_1 input. For clock selection information, see Table 13. Both CLK\_0 and CLK\_1 inputs may be monitored for input activity. For information, see Monitoring.

In addition, the range of available input and feedback dividers allows to adjust the phase detector frequency independent of the used input and VCXO frequencies as shown in Table 3 and Table 4. The VCXO-PLL charge pump current is controllable via internal registers and can be set in 50µA steps from 50µA to 1.6mA. The VCXO-PLL may be bypassed (BYPV): when in bypass, the FemtoClock NG PLL locks to the pre-divided input frequency for frequency synthesis.

Table 3. Example Configurations for  $f_{VCXO} = 30.72MHz$

|                       | VCXO-PLL Di |      |                        |

|-----------------------|-------------|------|------------------------|

| Input Frequency (MHz) | PV          | MV   | f <sub>PFD</sub> (MHz) |

|                       | 4           | 1    | 30.72                  |

| 122.88                | 16          | 4    | 7.68                   |

| 122.00                | 64          | 16   | 1.92                   |

|                       | 256         | 64   | 0.48                   |

| 156.25                | 15625       | 3072 | 0.01                   |

Table 4. Example Configurations for  $f_{VCXO} = 122.88MHz$

|                       | VCXO-PLL Di |     |                        |

|-----------------------|-------------|-----|------------------------|

| Input Frequency (MHz) | PV          | MV  | f <sub>PFD</sub> (MHz) |

|                       | 4           | 4   | 30.72                  |

| 122.88                | 16          | 16  | 7.68                   |

| 122.00                | 64          | 64  | 1.92                   |

|                       | 256         | 256 | 0.48                   |

Table 5. Example Configurations for  $f_{VCXO} = 153.6MHz$

|                       | VCXO-PLL Di |      |                        |

|-----------------------|-------------|------|------------------------|

| Input Frequency (MHz) | PV MV       |      | f <sub>PFD</sub> (MHz) |

| 122.88                | 4           | 5    | 30.72                  |

|                       | 16          | 20   | 7.68                   |

|                       | 64          | 80   | 1.92                   |

|                       | 256         | 320  | 0.48                   |

| 156.25                | 3125        | 3072 | 0.05                   |

Table 6. Example Configurations for  $f_{\text{VCXO}}\!=$  125MHz

|                       | VCXO-PLL Di |      |                        |

|-----------------------|-------------|------|------------------------|

| Input Frequency (MHz) | PV          | MV   | f <sub>PFD</sub> (MHz) |

|                       | 1           | 5    | 25                     |

| 25                    | 4           | 20   | 6.25                   |

| 25                    | 16          | 80   | 1.5625                 |

|                       | 64          | 320  | 0.390625               |

| 19.44                 | 486         | 3125 | 0.04                   |

|                       | 1           | 1    | 125                    |

| 125                   | 5           | 5    | 25                     |

| 125                   | 25          | 25   | 5                      |

|                       | 125         | 125  | 1                      |

|                       | 5           | 4    | 31.25                  |

| 156.25                | 50          | 40   | 3.125                  |

|                       | 500         | 400  | 0.3125                 |

Table 7. Example Configurations for  $f_{\text{VCXO}}\!=\!$  156.25MHz

|                       | VCXO- PLL Di |       |                        |

|-----------------------|--------------|-------|------------------------|

| Input Frequency (MHz) | PV           | MV    | f <sub>PFD</sub> (MHz) |

| 19.44                 | 1944         | 15625 | 0.01                   |

|                       | 4            | 25    | 6.25                   |

| 25                    | 40           | 250   | 0.625                  |

|                       | 400          | 2500  | 0.0625                 |

|                       | 4            | 5     | 31.25                  |

| 125                   | 40           | 50    | 3.125                  |

|                       | 400          | 500   | 0.3125                 |

|                       | 1            | 1     | 156.25                 |

| 156.25                | 10           | 10    | 15.625                 |

|                       | 100          | 100   | 1.5625                 |

Table 8. VCXO-PLL Bypass Settings

| BYPV | Operation                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | VCXO-PLL operation.                                                                                                                                                                                                                                                                                                                                                                                         |

| 1    | VCXO-PLL bypassed and disabled. The reference clock for the FemtoClock NG PLL is the selected input clock. Use EXT_SEL[1:0] for reference selection (00 or 01) or holdover (11). Device synthesizes an output frequency but will not attenuate input jitter. No external VCXO component and VCXO-PLL loop filter required. EXT_SEL[1:0] = 10 operation modes are not defined for VCXO-PLL bypass operation. |

#### FemtoClock NG PLL

The FemtoClock NG PLL is the second stage PLL and locks to the output signal of the VCXO-PLL (BYPV = 0). It requires configuration of the frequency doubler FDF or the pre-divider PF and the feedback divider MF to match the VCXO-PLL frequency to the selected VCO frequency of 2949.12MHz or 2457.6MHz. Best phase noise is typically achieved by engaging the internal frequency doubler (FDF = 1,  $\times$ 2). If engaged, the signal from the first PLL stage is doubled in frequency, increasing the phase detector frequency of the FemtoClock NG PLL. Enabling the frequency doubler disables the frequency pre-divider PF. If the frequency doubler is not used (FDF = 0), the PF pre-divider has to be configured. Typically PF is set to  $\div$ 1 to keep the phase detector frequency as high as possible. Set PF to other divider values to achieve specific frequency ratios between first and second PLL stage. This PLL is internally configured to high-bandwidth.

**Table 9. Frequency Doubler**

| FDF | Operation                                                                                                               |

|-----|-------------------------------------------------------------------------------------------------------------------------|

| 0   | Frequency doubler off. PF divides clock signal from VCXO-PLL or input (in bypass).                                      |

| 1   | Frequency doubler on (×2). Signal from VCXO-PLL or input (in bypass) is doubled in frequency. PF divider has no effect. |

**Table 10. Example PLL Configurations**

|                      | FemtoClock NG Divider Settings for VCO |    |    |           |    |    |

|----------------------|----------------------------------------|----|----|-----------|----|----|

|                      | 2949.12MHz                             |    |    | 2457.6MHz |    |    |

| VCXO-Frequency (MHz) | FDF                                    | PF | MF | FDF       | PF | MF |

| 153.6                | -                                      | 5  | 96 | _         | 1  | 16 |

| 155.0                |                                        |    |    | x2        | -  | 8  |

| 122.88               | -                                      | 1  | 24 | _         | 1  | 20 |

|                      | x2                                     | -  | 12 | x2        | -  | 10 |

| 30.72                | -                                      | 1  | 96 | _         | 1  | 80 |

|                      | x2                                     | _  | 48 | x2        | -  | 40 |

## **Channel Frequency Divider**

The device supports four independent output channels A - D. The channels A - D have one configurable integer frequency divider Nx, x = A - D that divides the VCO frequency to the desired output frequency with very low phase noise. The integer divider values can be selected from the range of  $\div 1$  to  $\div 160$  as shown in Table 11.

**Table 11. Integer Frequency Divider Settings**

|                                           | Output Clock Frequency (MHz) for VCO (MHz) |         |  |  |

|-------------------------------------------|--------------------------------------------|---------|--|--|

| Channel Divider N <i>x</i> <sup>[a]</sup> | 2949.12                                    | 2457.6  |  |  |

| ÷1                                        | 2949.12                                    | 2457.6  |  |  |

| ÷2                                        | 1474.56                                    | 1228.8  |  |  |

| ÷3                                        | 983.04                                     | 819.2   |  |  |

| ÷4                                        | 737.28                                     | 614.4   |  |  |

| ÷5                                        | 589.82                                     | 491.52  |  |  |

| ÷6                                        | 491.52                                     | 409.6   |  |  |

| ÷8                                        | 368.64                                     | 307.2   |  |  |

| ÷10                                       | 294.912                                    | 245.76  |  |  |

| ÷12                                       | 245.76                                     | 204.8   |  |  |

| ÷16                                       | 184.32                                     | 153.6   |  |  |

| ÷18                                       | 163.84                                     | 136.533 |  |  |

| ÷20                                       | 147.456                                    | 122.88  |  |  |

| ÷24                                       | 122.88                                     | 102.4   |  |  |

| ÷30                                       | 98.304                                     | 81.92   |  |  |

| ÷32                                       | 92.16                                      | 76.8    |  |  |

| ÷36                                       | 81.92                                      | 68.266  |  |  |

| ÷40                                       | 73.728                                     | 61.44   |  |  |

| ÷48                                       | 61.44                                      | 51.2    |  |  |

| ÷50                                       | 58.9824                                    | 49.152  |  |  |

| ÷60                                       | 49.152                                     | 40.96   |  |  |

| ÷64                                       | 46.08                                      | 38.4    |  |  |

| ÷72                                       | 40.96                                      | 34.133  |  |  |

| ÷80                                       | 36.864                                     | 30.72   |  |  |

| ÷96                                       | 30.72                                      | 25.6    |  |  |

| ÷100                                      | 29.4912                                    | 24.576  |  |  |

| ÷120                                      | 24.576                                     | 20.48   |  |  |

| ÷128                                      | 23.04                                      | 19.2    |  |  |

| ÷160                                      | 18.432                                     | 15.36   |  |  |

<sup>[</sup>a] x = A - D.

## **Redundant Inputs**

The two inputs are compatible with LVDS, LVPECL signal formats and also support single-ended signals (LVCMOS, see Applications Information for applicable input interface circuits).

## Monitoring

The two clock inputs of the device are individually and permanently monitored for activity. Inactivity is defined by a static input signal. Input frequency changes are not monitored.

### Loss of Input Signal (LOS)

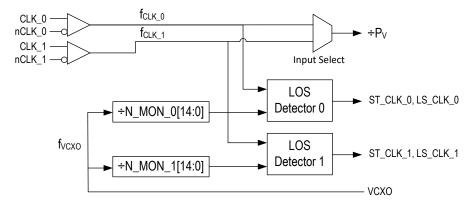

In operation, a clock input is declared invalid (LOS) with the corresponding ST\_CLK\_n and LS\_CLK\_n indicator bits set after a specified number of consecutive clock edges. If differential input signals are applied, the input will also detect an LOS condition in case of a zero differential input voltage. The device supports LOS detect circuits, one for each input. The signal detect circuits compare the signals at the CLK\_0 and CLK\_1 inputs to internally frequency-divided signals from the VCXO-PLL (see Figure 3 for details). For each loss detect circuit, the loss-of-signal fault condition is declared upon three or more missing clock input edges. Both loss detect circuits operate independent of each other, allowing correct LOS signaling for two different input frequencies. LOS requires configuration of the N\_MON\_n[14:0] frequency dividers to individually match the input frequencies CLK\_n to the VCXO frequency:  $f_{VCXO} \div N_MON_n = f_{CLK_n}$ . For instance, if one of the input frequencies is 15.36MHz and a 30.72MHz VCXO is used, set N\_MON\_ $n = \div 2$  (see Table 31 for configuration details). Then, LOS is declared after three consecutive missing clock edges. LOS is signaled through the ST\_CLK\_n (momentary) and LS\_CLK\_n (sticky, resettable) status bits and can reported as an interrupt signal on the nINT output. The LOS circuit requires the jitter attenuation mode of device (BYPV = 0). LOS does not detect frequency errors.

Figure 3. LOS Detect Circuit

#### Input Re-Validation

A clock input is declared valid and the corresponding ST\_CLK\_n bit is reset after the clock input signal returns for an user-configurable number of consecutive input periods. This re-validation of the selected input clock is controlled by the CNTV setting (verification pulse counter).

# **Input Clock Selection**

The device supports external, pin-controlled clock selection and internal, register controlled clock selection. The EXT\_SEL[1:0] pins control the input selection mode. In internal mode, automatic clock selection and manual register-controlled clock selection is available.

## Definitions for Input Clock Selection

Manual input selection The CLK\_n input is selected by the user by pin (external) or register control (internal).

Automatic input selection The CLK\_n input is selected by an internal state machine, based on internal priorities, as response to the clock input status.

## **External Input Selection Controls**

The EXT\_SEL[1:0] pins select CLK\_0 or CLK\_1 as the reference clock, enable switch control bits nMA[1:0], or set the device to holdover mode.

**Table 12. Input Selection Mode**

|                             |        |          | Reference Selection                                                          |                  |  |

|-----------------------------|--------|----------|------------------------------------------------------------------------------|------------------|--|

| EXT_SEL[1:0] <sup>[a]</sup> | EN_nMA | nMA[1:0] | Mode                                                                         | Selected Input   |  |

| 00 (default)                | Х      | Х        | External, Manual                                                             | CLK_0            |  |

| 01                          | Х      | Х        |                                                                              | CLK_1            |  |

|                             | 0      | х        | External-Controlled Holdover – No<br>Expiration Counter                      | _                |  |

|                             | 1      | 00       | Internal-Controlled, Manual Holdover                                         | by INT_SEL       |  |

| 10                          | 1      | 01       | Automatic                                                                    | by state machine |  |

|                             | 1      | 10       | Short-term Holdover                                                          | by INT_SEL       |  |

|                             | 1      | 11       | Automatic with Holdover                                                      | by state machine |  |

| 11                          | Х      | Х        | External-Controlled Holdover – No Expiration Counter (no expiration counter) | _                |  |

<sup>[</sup>a] Pin controlled input selection if EXT\_SEL[1] = 0; register controlled selection if EXT\_SEL[1] = 1.

## **Internal Input Selection Controls**

## Definitions for Automatic Input Selection

Primary clock: The CLK\_n input selected by the selection logic.

Secondary clock: The CLK\_n input not selected by the selection logic.

PLL reference clock: The CLK\_n input selected as the PLL reference signal by the selection logic. In automatic switching mode, the selection can be overwritten by a state machine.

Table 13. Internal Clock Selection Settings: Valid when EXT\_SEL[1:0] = 10 and EN\_nMA = 1

| Mc   | ode  |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Flags         |                |                                                        |                                                                                   |                                                          |

|------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|--------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------|

| nMA1 | nMA0 | Name                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ST_CLKn       | nST_HOLD       | ST_SEL                                                 | ST_REF                                                                            | Application                                              |

|      |      |                       | Input selection follows user-configuration of the INT_internal state machine.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SEL reg       | ister bit. Inp | ut selection is                                        | <i>never</i> changed                                                              | I by the                                                 |

|      |      | Manual                | LOS on the primary reference clock: Active reference stays selected and the PLLs may stall. Device will not go into holdover.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               | 1              | selected<br>input                                      | O[a]                                                                              |                                                          |

| 0    | 0    | Holdover<br>(default) | Manual change of the reference clock: The device will go into holdover and the hold-off down-counter (CNTH) starts. The device initiates a clock switch after expiration of the hold-off counter. Duration of holdover is set by CNTH × CNTR / f <sub>VCXO</sub> . Holdover is terminated even if the secondary clock input is bad (LOS). See Internal-Controlled, Manual Holdover                                                                                                                                                                                                                                                          | LOS<br>status | O[p]           | selected<br>input <sup>[c]</sup>                       | LOS status<br>of <i>selected</i><br>input                                         | selection<br>control with<br>holdover                    |

|      |      |                       | Input selection follows LOS status. A failing input clock has an LOS event, the device will immediately                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |                |                                                        |                                                                                   |                                                          |

| 0    | 1    | Automatic             | LOS on the primary reference clock: The device will switch to the secondary clock without holdover. Input selection is determined by a state machine and may differ from the user's clock selection.  No valid clock scenario: If no valid input clocks exist, the device will not attempt to switch and will not enter the holdover state. The PLL is not locked. Re-validation of an input clock will result in the PLL to attempt to lock on that input clock. See Revertive Switching.  Both primary and secondary clock must have the same frequency for the PLL to resume lock upon transition to the secondary clock: set PV0 = PV1. | LOS<br>status | 1              | selected<br>input<br>determined<br>by state<br>machine | actual LOS<br>status of<br>selected<br>input<br>determined<br>by state<br>machine | multiple<br>inputs with<br>qualified<br>clock<br>signals |

|      |      |                       | Manual change of the reference clock: The device will switch to the newly selected clock without holdover. If the newly selected clock is not valid, the PLL may stall.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               | 1              | selected<br>input                                      | actual LOS<br>status of<br>selected<br>input                                      |                                                          |

Table 13. Internal Clock Selection Settings: Valid when EXT\_SEL[1:0] = 10 and EN\_nMA = 1 (Cont.)

| Mo   | ode  |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |                                  | Flags                                                  |                                              |                                                    |

|------|------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------------------------|--------------------------------------------------------|----------------------------------------------|----------------------------------------------------|

| nMA1 | nMA0 | Name                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ST_CLKn       | nST_HOLD                         | ST_SEL                                                 | ST_REF                                       | Application                                        |

|      |      |                               | Input selection follows user-configuration of INT_SE machine.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | L register    | bit. Selecti                     | on is never cha                                        | anged by the ir                              | nternal state                                      |

| 1    | 0    | Short-term<br>Holdover        | LOS on the primary reference clock: A failing reference clock will cause an LOS event. If the selected reference fails, the device will enter holdover immediately. Re-validation of the selected input clock is controlled by the CNTV setting. A successful re-validation will result in the PLL to re-lock on that input clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | LOS<br>status | 0                                | selected<br>input                                      | 0                                            | use if a<br>single<br>reference is<br>occasionally |

|      |      |                               | Manual change of the reference clock: The device will switch to the newly selected clock without holdover. If the newly selected clock is not valid, the PLL may stall.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |               | 1                                |                                                        | LOS status<br>of selected<br>input           | interrupted                                        |

|      |      |                               | Input selection follows LOS status. A failing input clock has an LOS event, the device will go into holds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |                                  |                                                        |                                              |                                                    |

| 1    | 1    | Automatic<br>with<br>Holdover | LOS on the primary reference clock or manual change of the reference clock: the device will go into holdover and the hold-off down-counter (CNTH) starts. The device initiates a clock fail-over switch to a valid secondary clock input after expiration of the hold-off counter.  Duration of holdover is set by CNTH × CNTR / f <sub>VCXO</sub> . The holdover is terminated prior hold-off count-down if the primary clock revalidates or is terminated by a manual change of the reference clock. See Automatic with Holdover and Revertive Switching.  Both primary and secondary clock must have the same frequency for the PLL to resume lock upon transition to the secondary clock: set PV0 = PV1.  No valid clock scenario: The device remains in holdover if the secondary input clock is invalid. | LOS<br>status | 0<br>for<br>holdover<br>duration | selected<br>input<br>determined<br>by state<br>machine | actual LOS<br>status of<br>selected<br>input | multiple<br>inputs                                 |

<sup>[</sup>a] For the duration of an invalid input signal (LOS).

<sup>[</sup>b] For the duration of holdover.

<sup>[</sup>c] Delayed by holdover period.

#### Holdover

In holdover state, the output frequency and phase is derived from an internal, digital value based on previous frequency and phase information. Holdover characteristics are defined in Table 54.

## External-Controlled Holdover - No Expiration Counter

Applying the configuration EXT\_SEL[1:0] = 11 or (EXT\_SEL[1:0] = 10 and EN\_nMA = 0) sets the device in holdover. No clock input is selected. Leaving holdover requires a change from either of the two configurations above.

#### Internal-Controlled, Manual Holdover

Input switch control is manual by setting the configuration to EXT\_SEL[1:0] = 10, EN\_nMA = 1, and nM/A[1:0] = 00. The INT\_SEL bit determines the selected reference clock input. If the selection is changed by the user, the device will enter holdover until the CNTH[7:0] counter expires. Then, the new reference is selected (input switch). Application for this mode is external selection control.

- ST\_REF: status of selected reference clock

- ST\_CLK\_n will both reflect the status of the corresponding input

- ST\_SEL: the new selection after holdover

- nST\_HOLD = 0 for the duration of holdover

#### Automatic with Holdover

Configuration: EXT SEL[1:0] = 10, EN nMA = 1, and nM/A[1:0] = 11.

If an LOS event is detected on the active reference clock:

- Holdover begins immediately

- Corresponding ST\_REF and LS\_REF go low immediately

- Hold-off countdown begins immediately

During this time, both input clocks continue to be monitored and their respective ST\_CLK, LS\_CLK flags are active. LOS events will be indicated on ST\_CLK, LS\_CLK when they occur.

If the active reference clock resumes and is validated during the hold-off countdown:

- its ST\_CLK status flag will return high and the LS\_CLK is available to be cleared by an SPI write of 1 to that register bit.

- No transitions will occur of the active REF clock; ST SEL does not change

- Revertive bit has no effect during this time (whether 0 or 1)

When the hold-off countdown reaches zero:

- If the active reference has resumed and has been validated during the countdown, it will maintain being the active reference clock

- ST SEL does not change

- ST\_REF returns to 1

- LS\_REF can be cleared by an SPI write of 1 to that register

- Holdover turns off and the VCXO-PLL attempts to lock to the active reference clock

- If the active reference has not resumed, but the other clock input CLK\_n is validated, then

- ST\_SEL changes to the new active reference

- ST\_REF returns to 1

- LS REF can be cleared by an SPI write of 1 to that register

- Holdover turns off

If there is no validated CLK:

- ST\_SEL does not change

- ST\_REF remains low

- LS\_REF cannot be cleared by an SPI write of 1 to that register

- Holdover remains active

Revertive capability returns if REVS = 1.

#### **Hold-off Counter**

A configurable down-counter applicable to the *Automatic with Holdover* and *Manual with Holdover* selection modes. The purpose of this counter is a deferred, user-configurable input switch. The counter expires when a zero-transition occurs; this triggers a new reference clock selection. The counter is clocked by the frequency-divided VCXO-PLL signal. The CNTR setting determines the hold-off counter frequency divider and the CNTH setting the start value of the hold-off counter. For instance, set CNTR to a value of  $\div 131072$  to achieve 937.5Hz (or a period of 1.066ms at  $f_{VCXO} = 122.88 MHz$ ): the 8-bit CNTH counter is clocked by 937.5Hz and the user-configurable hold-off period range is 0 ms

(CNTR = 0x00) to 272ms (CNTR = 0xFF). After the counter expires, it reloads automatically from the CNTH SPI register. After the LOS status bit (LS\_CLK\_n) for the corresponding input CLK\_n has been cleared by the user, the input is enabled for generating a new LOS event.

The CNTR counter is only clocked if the device is configured in the clock selection modes *Automatic with Holdover* and the selected reference clock experiences an LOS event or in the *Manual with Holdover* mode with manual switching. Otherwise, the counter is automatically disabled (not clocked).

## **Revertive Switching**

Revertive switching: is only applicable to the two automatic switch modes shown in Table 13. Revertive switching enabled: Re-validation of the primary clock will cause a new input selection to that clock (revertive switch). An input switch is only done if the re-validated input is the primary clock.

Revertive switching disabled: Re-validation of a primary clock has no impact on the clock selection. Default setting is revertive switching disabled.

### **VCXO-PLL Lock Detect (LOLV)**

The VCXO-PLL lock detect circuit uses the signal phase difference at the phase detector as loss-of-lock criteria. Loss-of-lock is reported if the actual phase difference is larger than a configurable phase detector window set by the LOCK\_TH[14:0] configuration bits. A Loss-of-lock state is reported through the nST\_LOLV and nLS\_LOLV status bits as shown in Table 17. The VCXO-PLL lock detect function requires to set FVCV = 0.

### FemtoClock NG Loss-of-Lock (LOLF)

FemtoClock NG-PLL Loss-of-lock is signaled through the nST\_LOLF (momentary) and nLS\_LOLF (sticky, resettable) status bits and can reported as hardware signal on the LOCK\_V output as well as an interrupt signal on the nINT output.

# **Differential Outputs**

**Table 14. Output Features**

| Output | Style                 | Amplitude <sup>[a]</sup> | Disable       | Power Down | Termination            |  |                                              |

|--------|-----------------------|--------------------------|---------------|------------|------------------------|--|----------------------------------------------|

| QCLK_y | LVPECL                | 350mV – 850mV            | 350mV – 850mV |            | 350mV – 850mV          |  | $50\Omega$ to V <sub>TT</sub> <sup>[b]</sup> |

| QCLN_y | LVDS                  | 4 steps Yes              |               | Yes        | 100Ω diff.             |  |                                              |

|        | LVPECL                | 350mV - 850mV            | Yes           | Yes        | 50Ω to V <sub>TT</sub> |  |                                              |

| QCLK_V | LVDS                  | 4 steps                  | 165           | 165        | 100Ω diff.             |  |                                              |

|        | LVCMOS <sup>[c]</sup> | 1.8V                     | Yes           | Yes        | _                      |  |                                              |

<sup>[</sup>a] Amplitudes are measured single-endedly.

**Table 15. Individual Clock Output Settings**

| PD <sup>[a]</sup> | Output Power | STYLE | Termination                                | Enable | State                  | A[1:0] | Amplitude (mV) <sup>[b]</sup> |     |

|-------------------|--------------|-------|--------------------------------------------|--------|------------------------|--------|-------------------------------|-----|

| 1                 | Off          | Х     | $100\Omega$ differential or no termination | Х      | Off                    | Χ      | Х                             |     |

| 0                 | On           | 0     | 100Ω differential                          | 0      | Disable <sup>[c]</sup> | XX     | X                             |     |

|                   |              |       | (LVDS)                                     | 1      | Enable                 | 00     | 350                           |     |

|                   |              |       |                                            |        |                        |        | 01                            | 500 |

|                   |              |       |                                            |        |                        |        | 10                            | 700 |

|                   |              |       |                                            |        |                        |        | 11                            | 850 |

|                   |              | 1     | $50\Omega$ to $V_{TT}^{[d]}$               | 0      | Disable                | XX     | X                             |     |

|                   |              |       | (LVPECL)                                   | 1      | Enable                 | 00     | 350                           |     |

|                   |              |       |                                            |        | 01                     | 500    |                               |     |

|                   |              |       |                                            |        |                        | 10     | 700                           |     |

|                   |              |       |                                            |        |                        | 11     | 850                           |     |

<sup>[</sup>a] Power-down modes are available for the individual channels A – D and the outputs QCLK\_y (A0 to D1).

<sup>[</sup>b] For V<sub>TT</sub> (termination voltage) values (see Table 60).

<sup>[</sup>c] LVCMOS style: nQCLK\_V and QCLK\_V are complementary.

<sup>[</sup>b] Output amplitudes of 700mV and 850mV require a 3.3V output supply (V<sub>DDO\_V</sub>). 350mV and 500mV output amplitudes support V<sub>DDO\_V</sub> = 2.5V and 1.8V.

<sup>[</sup>c] Differential output is disabled in static low/high state.

<sup>[</sup>d] For V<sub>TT</sub> (termination voltage) values (see Table 60).

## **Output Phase-Delay**

Output phase delay is supported in each channel. The selected VCO frequency sets the delay unit to  $1/2 \times f_{VCO}$ .

**Table 16. Delay Circuit Settings**

| Delay Circuit                     | Unit                                                         | Steps | Range                         |

|-----------------------------------|--------------------------------------------------------------|-------|-------------------------------|

| Clock Phase $\Phi_{CLK_{\!-\!X}}$ |                                                              | 512   |                               |

|                                   | $\frac{1}{2 \times f_{VCO}}$                                 |       |                               |

|                                   | $f_{VCO} = 2949.12MHz$ : 169ps $f_{VCO} = 2457.6MHz$ : 203ps |       | 0 – 86.664ns<br>0 – 103.963ns |

## **Status Conditions and Interrupts**

The device has an interrupt output to signal changes in status conditions. Settings for status conditions may be accessed in the Status registers. The device has several conditions that can indicate faults and status changes in the operation of the device. These are shown in Table 17 and can be monitored directly in the status registers. Status bits (named: ST\_status\_condition) are read-only and reflect the momentary device status at the time of read-access. Several status bits are also copied into latched bit positions (named: LS\_status\_condition). The latched version is controlled by the corresponding fault and status conditions and remains set ("sticky") until reset by the user by writing "1" to the status register bit. The reset of the status condition only has an effect if the corresponding fault condition is removed, otherwise, the status bit will set again. Setting a status bit on several latched registers can be programmed to generate an interrupt signal (nINT) via settings in the Interrupt Enable bits (named: IE\_condition). A setting of "0" in any of these bits will mask the corresponding latched status bits from affecting the interrupt status pin. Setting all IE bits to 0 has the effect of disabling interrupts from the device.

Table 17. Status Bit Functions

| Statu     | ıs Bit   | Function                       |                                |                    |                         |

|-----------|----------|--------------------------------|--------------------------------|--------------------|-------------------------|

|           |          |                                | Status                         | if Bit is:         | Interrunt Enable        |

| Momentary | Latched  | Description                    | 1                              | 0                  | Interrupt Enable<br>Bit |

| ST_CLK_0  | LS_CLK_0 | CLK 0 input status             | Active                         | LOS                | IE_CLK_0                |

| ST_CLK_1  | LS_CLK_1 | CLK 1 input status             | Active                         | LOS                | IE_CLK_1                |

| nST_LOLV  | nLS_LOLV | VCXO-PLL Loss-of-lock          | Locked                         | Loss-of-lock       | IE_LOLV                 |

| nST_LOLF  | nLS_LOLF | FemtoClock NG PLL Loss-of-lock | Locked                         | Loss-of-lock       | IE_LOLF                 |

| nST_HOLD  | nLS_HOLD | Holdover                       | Not in holdover                | Device in holdover | IE_HOLD                 |

| ST_VCOF   | _        | FemtoClock NG VCO calibration  | Not completed                  | Completed          | _                       |

| ST_SEL    | _        | Clock input selection          | 0 = CLK_0<br>1 = CLK_1         |                    | _                       |

| ST_REF    | LS_REF   | PLL reference status           | Valid reference <sup>[a]</sup> | Reference lost     | IE_REF                  |

<sup>[</sup>a] Manual and short-term holdover mode: 0 indicates if the selected reference is lost, 1 if not lost.

Automatic mode: will transition to 0 while the input clock is lost and during input selection.

Will transition to 1 once a new reference is selected.

Automatic with holdover mode: 0 indicates the reference is lost and still in holdover.

Interrupts are cleared by resetting the appropriate bit(s) in the latched register after the underlying fault condition has been resolved. When all valid interrupt sources have been cleared in this manner, this will release the nINT output until the next unmasked fault.

**Table 18. Fault Indicator Outputs**

| Status E               | Bit (PLL)                   |                                                                |                                                                |

|------------------------|-----------------------------|----------------------------------------------------------------|----------------------------------------------------------------|

| nLS_LOLV<br>(VCXO-PLL) | nLS_LOLF<br>(FemtoClock NG) | Status Reported on LOCK_V <sup>[a]</sup> Output <sup>[b]</sup> | Status Reported on LOCK_F <sup>[a]</sup> Output <sup>[b]</sup> |

| Locked                 | Locked                      | 1                                                              | 1                                                              |

| Locked                 | Not locked                  | 1                                                              | 0                                                              |

| Not locked             | Locked                      | 0                                                              | 1                                                              |

| Not locked             | Not locked                  | 0                                                              | 0                                                              |

<sup>[</sup>a] Hardware interrupts on nINT require IE\_LOLV = 1, IE\_LOLF = 1 (interrupt enable).

# Device Startup, Reset and Synchronization

At startup, an internal POR (power-on reset) resets the device and sets all register bits to their default value. The device forces the VCXO control voltage at the LFV pin to half of the power supply voltage to center the VCXO-frequency. In the default configuration the QCLK\_y outputs are disabled at startup.

Recommended configuration sequence (in order):

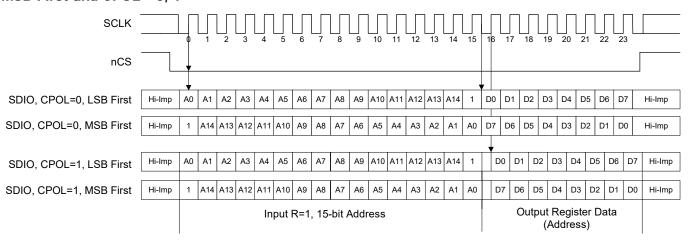

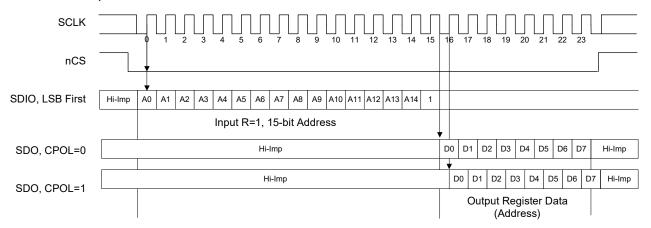

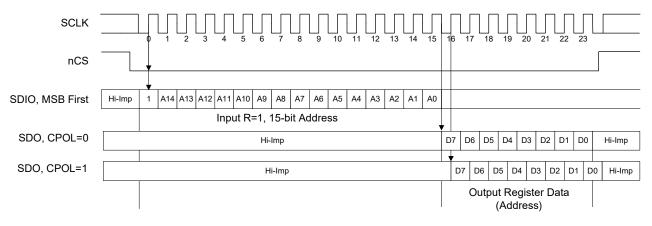

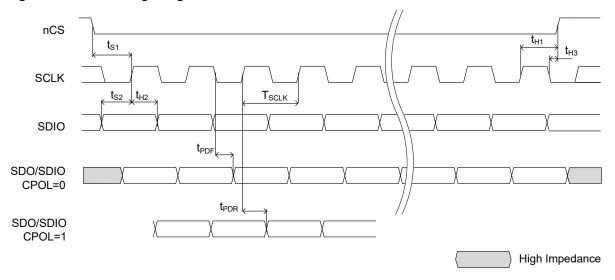

- (Optional) set the value of the CPOL register bit to define the SPI read mode supported by the SPI controller. Set the LSBIT\_1ST, SDO\_ACT, ACS\_ON and the corresponding mirrored bits in register 0x00 as appropriate for SPI read access to the device.

- Configure all PLL and output divider and delay circuits as well as other device configurations, such as the charge pump currents. Set the TRANSFER bit (register 0x0F, bit D0) for PLL registers wider than then 8 bit (see double buffered registers).

- Set the initialization bit INIT\_CLK. This will initiate all divider and delay circuits and synchronize them to each other. The INIT\_CLK bit will self-clear.

- Set both the RELOCK bit and PB\_CAL bit. This step should not be combined with the previous step (setting INIT\_CLK) in a multi SPI-byte register access. Both bits will self-clear.

- Clear the FVCV bit to release the VCXO control voltage and VCXO-PLL will attempt to lock to the input clock signal starting from its center frequency.

- Clear the status flags.

- (Optional and recommended) Optimize the internal precision bias current calibration process:

- Read the contents of the STAT\_PB[5:1] register (precision bias current in register 0x4E, ignore STAT\_PB[0])

- With a single-byte write access to register 0x63, apply the following bit pattern to OVERRIDE\_CURR[5:0] and OVERRIDE\_CAL:

- OVERRIDE\_CURR[5:1] (bit field location D[6:2] of register 0x63 = STAT\_PB[5:1] as read from above step OVERRIDE\_CURR[0] (bit field location D[1] of register 0x63) = 0

OVERRIDE CAL (bit field location D[0] of register 0x63) = 1

- Enable the outputs by accessing the output-enable registers in a separate SPI write access.

<sup>[</sup>b] SELSV[2:1] bits control the logic level (1.8V/ 3.3V) of LOCK V, LOCK F and nINT outputs.

## **Changing Frequency Dividers and Phase Delay Values**

Following procedure has to be applied for a change of a clock divider and phase delay value  $N_{A-D}$ , and  $\Phi_{CLKA-D}$ :

- (Optional) set the value of the CPOL register to define the SPI read mode, so that SPI settings can be validated by subsequent SPI read accesses.

- (Optional) disable the outputs whose frequency divider or delay value is changed.

- Configure the  $N_{A-D}$  dividers and the delay circuits  $\Phi_{CLKA-D}$  to the desired new values.