Sample &

Buv

## LDC1000-Q1

SLOS886B-SEPTEMBER 2014-REVISED OCTOBER 2014

# LDC1000-Q1 Inductance to Digital Converter

Technical

Documents

#### Features 1

- Qualified for Automotive Applications

- AEC-Q100 Qualified With the Following Results:

- Device Temperature Grade 0: -40°C to 150°C Ambient Operating Temperature Range E

- Device Temperature Grade 1: –40°C to 125°C Ambient Operating Temperature Range Q

- Device HBM ESD Classification Level 2

- Device CDM ESD Classification Level C6

- Magnet-Free Operation

- Sub-Micron Precision

- Adjustable Sensing Range (through Coil Design)

- Lower System Cost

- Remote Sensor Placement (Decoupling the LDC from Harsh Environments)

- High Durability (by Virtue of Contact-Less Operation)

- Insensitivity to Environmental Interference (such as Dirt, Dust, Water, Oil)

- Supply Voltage, Analog: 4.75 to 5.25 V

- Supply Voltage, IO: 1.8 to 5.25 V

- Supply Current (Without LC Tank): 1.7 mA

- R<sub>P</sub> Resolution: 16-bit

- L Resolution: 24-bit

- LC Frequency Range: 5 kHz to 5 MHz

#### Applications 2

- Drive-by-Wire Systems

- Gear-Tooth Counting

- Flow Meters

- **Push-Button Switches**

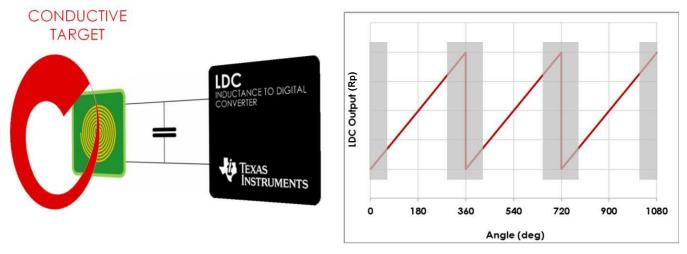

- **Rotational Position Sensor**

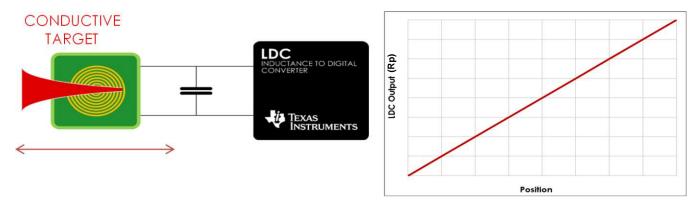

- Linear Position Sensor

- Pedal Position Sensor

- **Throttle Position Sensor**

# 3 Description

Tools &

Software

Inductive sensing is a contactless, short-range sensing technology that enables low-cost, highresolution sensing of conductive targets in the presence of dust, dirt, oil, and moisture, making this technology extremely reliable in harsh environments. Using a coil that can be created for example on a PCB as a sensing element, the LDC1000-Q1 device enables ultra-low cost system solutions.

Support &

Community

**.**...

Inductive sensing technology enables precise measurement of linear or angular position. displacement, motion, compression, vibration, metal composition, and many other applications in markets including automotive, consumer, computer, industrial, medical, and communications. Inductive sensing offers better performance and reliability at lower cost than other competitive solutions.

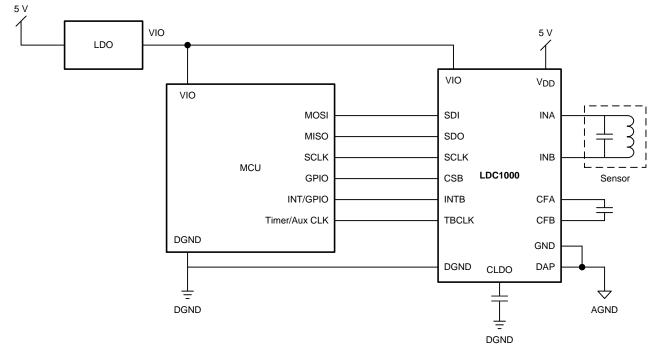

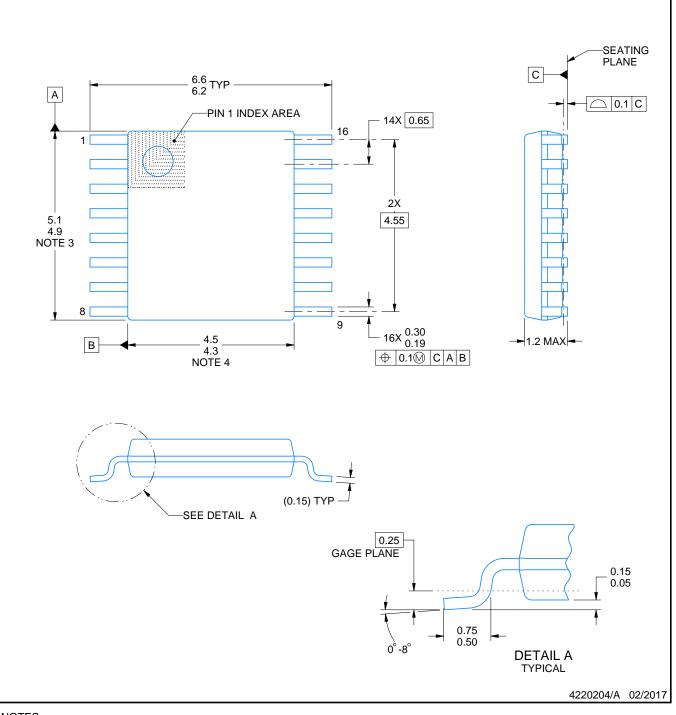

The LDC1000-Q1 device is the first automotivequalified LDC, offering the benefits of inductive sensing in a low-power, small-footprint solution. The product is available in a 16-pin TSSOP package and offers several modes of operation. An SPI interface simplifies connection to an MCU.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |

|-------------|------------|-------------------|

| LDC1000-Q1  | TSSOP (16) | 5.00 mm × 4.40 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

### Typical Application — Axial Distance Sensing

# **Table of Contents**

| 1 | Feat | tures 1                            |

|---|------|------------------------------------|

| 2 | Арр  | lications 1                        |

| 3 | Des  | cription 1                         |

| 4 | Rev  | ision History 2                    |

| 5 | Pin  | Configuration and Functions        |

| 6 |      | cifications 4                      |

|   | 6.1  | Absolute Maximum Ratings 4         |

|   | 6.2  | Handling Ratings 4                 |

|   | 6.3  | Recommended Operating Conditions 4 |

|   | 6.4  | Thermal Information 4              |

|   | 6.5  | Electrical Characteristics 5       |

|   | 6.6  | Timing Requirements 6              |

|   | 6.7  | Typical Characteristics 7          |

| 7 | Deta | ailed Description8                 |

|   | 7.1  | Overview                           |

|   | 7.2  | Functional Block Diagram 8         |

|   |      |                                    |

|    | 7.3  | Feature Description               | 8  |

|----|------|-----------------------------------|----|

|    | 7.4  | Device Functional Modes           | 12 |

|    | 7.5  | Programming                       | 14 |

|    | 7.6  | Register Map                      | 16 |

| 8  | Арр  | lication and Implementation       | 26 |

|    | 8.1  | Application Information           | 26 |

|    | 8.2  | Typical Application               | 28 |

| 9  | Pow  | er Supply Recommendations         | 32 |

| 10 | Lay  | out                               | 32 |

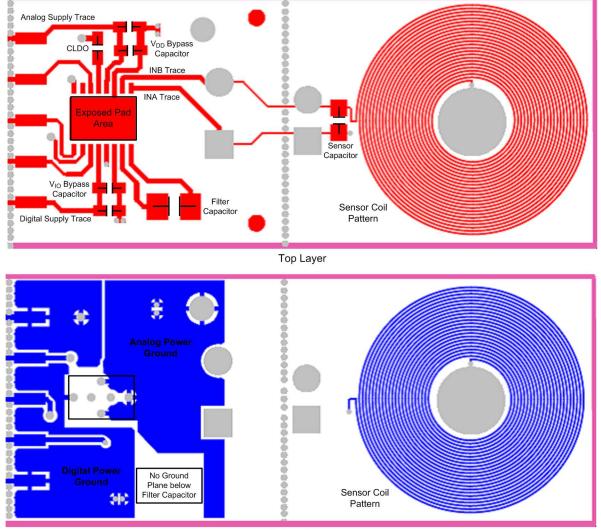

|    | 10.1 | Layout Guidelines                 | 32 |

|    | 10.2 | Layout Example                    | 33 |

| 11 |      | ice and Documentation Support     |    |

|    | 11.1 | Trademarks                        | 34 |

|    | 11.2 | Electrostatic Discharge Caution   | 34 |

|    | 11.3 | Glossary                          | 34 |

| 12 | Mec  | hanical, Packaging, and Orderable |    |

|    |      | rmation                           | 34 |

|    |      |                                   |    |

# 4 Revision History

| Changes from Revision A (September 2014) to Revision B                          | Page |

|---------------------------------------------------------------------------------|------|

| Changed pin configuration image and removed DAP from <i>Pin Functions</i> table |      |

| Changes from Original (September 2014) to Revision A                            | Page |

| Changed the device status from Product Preview to Production Data               |      |

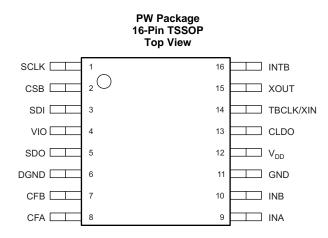

# 5 Pin Configuration and Functions

## **Pin Functions**

| PIN |                 | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                        |  |  |

|-----|-----------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO. | NAME            | ITPE                | DESCRIPTION                                                                                                                                                                                                        |  |  |

| 1   | SCLK            | DI                  | SPI clock input. The SCLK pin is used to clock-out and clock-in the data from or into the chip                                                                                                                     |  |  |

| 2   | CSB             | DI                  | SPI CSB. Multiple devices can be connected on the same SPI bus and the CSB pin can be used to select which device is communicated with.                                                                            |  |  |

| 3   | SDI             | DI                  | SPI Slave Data In (Master Out Slave In). This pin should be connected to the Master Out Slave In of the master device.                                                                                             |  |  |

| 4   | VIO             | Р                   | Digital IO Supply                                                                                                                                                                                                  |  |  |

| 5   | SDO             | DO                  | SPI Slave Data Out (Master In Slave Out). This pin is high-Z when the CSB pin is high.                                                                                                                             |  |  |

| 6   | DGND            | Р                   | Digital ground                                                                                                                                                                                                     |  |  |

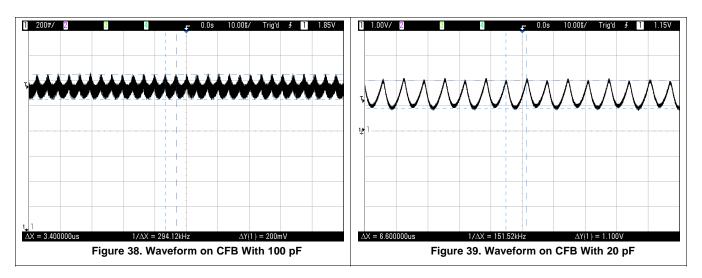

| 7   | CFB             | А                   | LDC filter capacitor                                                                                                                                                                                               |  |  |

| 8   | CFA             | А                   | LDC filter capacitor                                                                                                                                                                                               |  |  |

| 9   | INA             | А                   | External LC Tank. Connect this pin to an external LC tank.                                                                                                                                                         |  |  |

| 10  | INB             | А                   | External LC Tank. Connect this pin to an external LC tank.                                                                                                                                                         |  |  |

| 11  | GND             | Р                   | Analog ground                                                                                                                                                                                                      |  |  |

| 12  | V <sub>DD</sub> | Р                   | Analog supply                                                                                                                                                                                                      |  |  |

| 13  | CLDO            | А                   | LDO bypass capacitor. Connect a 56-nF capacitor from this pin to GND.                                                                                                                                              |  |  |

| 14  | TBCLK/XIN       | DI/A                | External time-base clock and XTAL. This pin is either an external clock or is connected to a crystal.                                                                                                              |  |  |

| 15  | XOUT            | A                   | XTAL. Crystal out. Connecting an 8-Mhz crystal between the TBCLK/XIN pin and the XOUT pin with 20-pF capacitor from each pin to ground is recommended. This pin should be floating when an external clock is used. |  |  |

| 16  | INTB            | DO                  | Configurable interrupt. This pin can be configured to function in three different ways (threshold detect, wakeup, or DRDYB) by programing the INT pin mode register.                                               |  |  |

(1) DO: Digital Output, DI: Digital Input, P: Power, A: Analog

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                      |                       | MIN  | MAX                   | UNIT |

|--------------------------------------|-----------------------|------|-----------------------|------|

| Analog supply voltage                | V <sub>DD</sub> – GND |      | 5.5                   | V    |

| IO supply voltage                    | VIO – GND             |      | 5.5                   | V    |

| Voltage                              | On any pin            | -0.3 | V <sub>DD</sub> + 0.3 | V    |

|                                      | On any digital pin    | -0.3 | V <sub>IO</sub> + 0.3 | V    |

| Input Current                        | INA and INB           |      | 8                     | mA   |

| Junction Temperature, T <sub>J</sub> |                       |      | 150                   | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 Handling Ratings

|                  |                                |                                                         | MIN   | MAX  | UNIT |

|------------------|--------------------------------|---------------------------------------------------------|-------|------|------|

| T <sub>stg</sub> | Storage temperature range      |                                                         | -65   | 150  | °C   |

| V                | V(ESD) Electrostatic discharge | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup> | -2000 | 2000 | V    |

| V(ESD)           |                                | Charged device model (CDM), per AEC Q100-011, all pins  | -1000 | 1000 | V    |

(1) AEC Q100-002 indicates HBM stressing is done in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                 |                                                                   |                               | MIN  | MAX  | UNIT |

|-----------------|-------------------------------------------------------------------|-------------------------------|------|------|------|

| V <sub>DD</sub> | Analog supply voltage (V <sub>DD</sub> – GND)                     |                               | 4.75 | 5.25 | V    |

| V <sub>IO</sub> | IO supply voltage (VIO – GND)                                     |                               | 1.8  | 5.25 | V    |

|                 | V <sub>DD</sub> – VIO                                             |                               | ≥0   |      | V    |

|                 | Operating temperature (see the Mechanical,                        | Grade 0 (temperature range E) | -40  | 150  |      |

| T <sub>A</sub>  | Packaging, and Orderable Information section for package options) | Grade 1 (temperature range Q) | -40  | 125  | °C   |

# 6.4 Thermal Information

|                       | THERMAL METRIC <sup>(1)</sup>                | PW<br>16 PINS | UNIT  |

|-----------------------|----------------------------------------------|---------------|-------|

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 106.3         |       |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 40.8          |       |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 51.3          | 80 AM |

| ΨJT                   | Junction-to-top characterization parameter   | 3.6           | °C/W  |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 50.8          |       |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | _             |       |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

# 6.5 Electrical Characteristics

Unless otherwise specified, all limits ensured for  $T_A = 25^{\circ}C$ ,  $V_{DD} = 5 \text{ V}$ ,  $V_{IO} = 3.3 \text{ V}$

|                         | PARAMETER                         | TEST CONDITIONS                                                             | MIN                      | ТҮР                            | MAX                 | UNIT                    |

|-------------------------|-----------------------------------|-----------------------------------------------------------------------------|--------------------------|--------------------------------|---------------------|-------------------------|

| POWER                   |                                   |                                                                             |                          |                                |                     |                         |

| V <sub>DD</sub>         | Analog supply voltage             |                                                                             | 4.75                     | 5                              | 5.25                | V                       |

| V <sub>IO</sub>         | IO supply voltage                 | $V_{IO} \le V_{DD}$                                                         | 1.8                      | 3.3                            | 5.25                | V                       |

| I <sub>DD</sub>         | Supply current                    | Does not include the LC tank current                                        |                          | 1.7                            | 2.3                 | mA                      |

| I <sub>IO</sub>         | IO supply current                 | Static current                                                              |                          |                                | 14                  | μA                      |

| I <sub>DD(LP)</sub>     | Low-power mode supply current     | Without LC tank                                                             |                          | 250                            |                     | μA                      |

| t <sub>(start)</sub>    | Start-up time                     | From POR to ready-to-<br>convert. Crystal not used<br>for frequency counter |                          | 2                              |                     | ms                      |

| LDC                     |                                   |                                                                             |                          |                                |                     |                         |

| f <sub>sensor_min</sub> | Minimum sensor frequency          |                                                                             |                          | 5                              |                     | kHz                     |

| f <sub>sensor_max</sub> | Maximum sensor frequency          |                                                                             |                          | 5                              |                     | MHz                     |

| A <sub>sensor_min</sub> | Minimum sensor amplitude          |                                                                             |                          | 1                              |                     | V <sub>PP</sub>         |

| A <sub>sensor_max</sub> | Maximum sensor amplitude          |                                                                             |                          | 4                              |                     | V <sub>PP</sub>         |

| t <sub>rec</sub>        | Recovery time                     | Oscillation start-up time<br>after RP under-range<br>condition              |                          | 10                             |                     | 1 / f <sub>sensor</sub> |

| Z <sub>RP_min</sub>     | Minimum sensor RP range           |                                                                             |                          | 798                            |                     | Ω                       |

| R <sub>RP_max</sub>     | Maximum sensor RP range           |                                                                             |                          | 3.93                           |                     | MΩ                      |

| R <sub>RP_res</sub>     | RP measurement resolution         |                                                                             |                          | 16                             |                     | Bits                    |

| t <sub>res(min)</sub>   | Minimum response time             | Minimum programmable settling time of digital filter                        |                          | 192 × 1 / f <sub>sensor</sub>  |                     | S                       |

| t <sub>res(max)</sub>   | Maximum response time             | Maximum programmable settling time of digital filter                        |                          | 6144 × 1 / f <sub>sensor</sub> |                     | S                       |

| EXTERNAL                | CLOCK AND CRYSTAL FOR FREQU       | ENCY COUNTER                                                                |                          |                                |                     |                         |

| f <sub>ref</sub>        | Crystal frequency                 |                                                                             |                          | 8                              |                     | MHz                     |

| t <sub>xtalst</sub>     | Crystal startup time              |                                                                             |                          | 30                             |                     | ms                      |

|                         | External clock frequency          |                                                                             |                          |                                | 8                   | MHz                     |

|                         | External clock input high voltage |                                                                             |                          |                                | V <sub>IO</sub>     | V                       |

| DIGITAL I/O             | CHARACTERISTICS                   | · · · ·                                                                     |                          |                                |                     |                         |

| V <sub>IH</sub>         | Logic 1 input voltage             |                                                                             | 0.8 ×<br>V <sub>IO</sub> |                                |                     | V                       |

| V <sub>IL</sub>         | Logic 0 input voltage             |                                                                             |                          |                                | $0.2 \times V_{IO}$ | V                       |

| V <sub>OH</sub>         | Logic 1 output voltage            | $I_{(SOURCE)} = 400 \ \mu A$                                                |                          | V <sub>IO</sub> - 0.3          |                     | V                       |

| V <sub>OL</sub>         | Logic 0 output voltage            | I <sub>(SINK)</sub> = 400 μA                                                |                          |                                | 0.3                 | V                       |

| I <sub>lkgIO</sub>      | Digital IO leakage current        |                                                                             | -500                     |                                | 500                 | nA                      |

**ISTRUMENTS**

EXAS

## LDC1000-Q1

SLOS886B-SEPTEMBER 2014-REVISED OCTOBER 2014

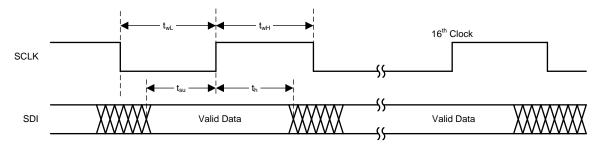

# 6.6 Timing Requirements

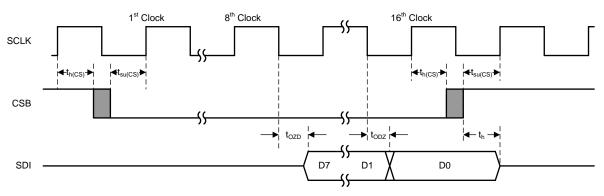

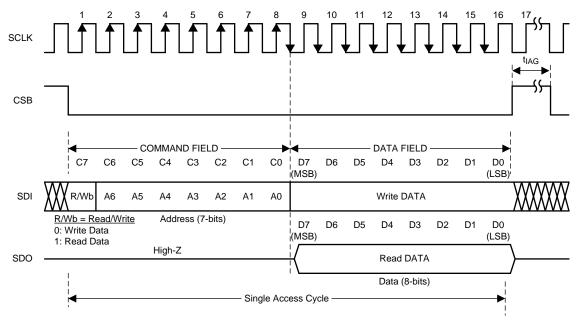

Unless otherwise noted, all limits specified at  $T_A = 25^{\circ}$ C,  $V_{DD} = 5$  V,  $V_{IO} = 3.3$  V, 10-pF capacitive load in parallel with a 10-k $\Omega$  load on the SDO. Specified by design; not production tested. See Figure 1

|                        |                             |                                                      | MIN                     | NOM                     | MAX | UNIT |

|------------------------|-----------------------------|------------------------------------------------------|-------------------------|-------------------------|-----|------|

| f <sub>SCLK</sub>      | Serial clock frequency      | See Figure 1                                         |                         |                         | 4   | MHz  |

| t <sub>wH</sub>        | SCLK pulse-width high       | f <sub>SCLK</sub> = 4 Mhz, See Figure 1              | 0.4 / f <sub>SCLK</sub> |                         |     | s    |

| t <sub>wL</sub>        | SCLK pulse-width low        | f <sub>SCLK</sub> = 4 Mhz, See Figure 1              | 0.4 / f <sub>SCLK</sub> |                         |     | s    |

| t <sub>su</sub>        | SDI setup time              | See Figure 1                                         | 10                      |                         |     | ns   |

| t <sub>h</sub>         | SDI hold time               | - See Figure 1                                       | 10                      |                         |     | ns   |

| t <sub>ODZ</sub>       | SDO driven-to-tristate time | Measured at 10% / 90% point, See<br>Figure 2         |                         |                         | 20  | ns   |

| t <sub>OZD</sub>       | SDO tristate-to-driven time | Measured at 10% / 90% point, See<br>Figure 2         |                         |                         | 20  | ns   |

| t <sub>d(OUTPUT)</sub> | SDO output delay time       |                                                      |                         |                         | 20  | ns   |

| t <sub>su(CS)</sub>    | CSB setup time              | See Figure 2                                         | 20                      |                         |     | ns   |

| t <sub>h(CS)</sub>     | CSB hold time               |                                                      | 20                      |                         |     | ns   |

| t <sub>IAG</sub>       | inter-access gap            | See Figure 16                                        | 100                     |                         |     | ns   |

| t <sub>w(DRDY)</sub>   | Data ready pulse width      | Data ready pulse at every 1 / ODR if no data is read |                         | 1 / f <sub>sensor</sub> |     | S    |

# Figure 1. Write Timing Diagram

Figure 2. Read Timing Diagram

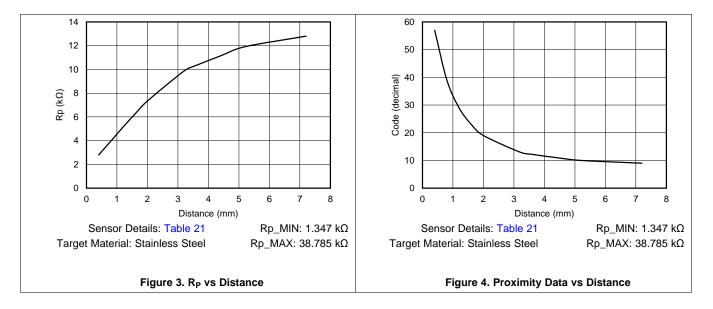

# 6.7 Typical Characteristics

# 7 Detailed Description

# 7.1 Overview

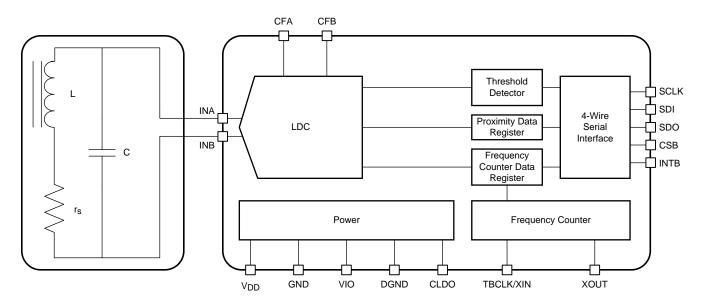

The LDC1000-Q1 device is an inductance-to-digital converter that simultaneously measures the impedance and resonant frequency of an LC resonator. The device accomplishes this task by regulating the oscillation amplitude in a closed-loop configuration to a constant level, while monitoring the energy dissipated by the resonator. By monitoring the amount of power injected into the resonator, the LDC1000-Q1 device can determine the value of  $R_p$ . When the value is determined, the device returns this as a digital value which is inversely proportional to  $R_p$ . In addition, the LDC1000-Q1 device also measure the oscillation frequency of the LC circuit. This frequency is used to determine the inductance of the LC circuit. The device outputs a digital value that is inversely proportional to frequency.

The threshold detector block provides a comparator with hysteresis. With the threshold registers programed and comparator enabled, the proximity data register is compared with threshold registers and INTB pin indicates the output.

The device has a simple 4-wire SPI interface. The INTB pin provides multiple functions which are programmable with SPI.

The device has separate analog and I/O supplies. The analog supply operates at 5 V and the I/O operates at 1.8 to 5 V. The integrated LDO requires a 56-nF capacitor connected from the CLDO pin to GND.

# 7.2 Functional Block Diagram

# 7.3 Feature Description

### 7.3.1 Inductive Sensing

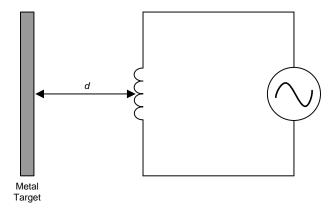

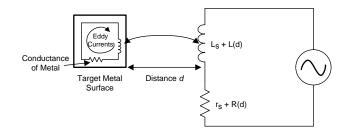

An alternating current (AC) flowing through a coil generates an AC magnetic field. If a conductive material, such as a metal target, is brought into the vicinity of the coil, this magnetic field induces circulating currents (eddy currents) on the surface of the target. These eddy currents are a function of the distance, size, and composition of the target. These eddy currents then generate a magnetic field that opposes the original field generated by the coil. This mechanism is best compared to a transformer, where the coil is the primary core and the eddy current is the secondary core. The inductive coupling between both cores depends on distance and shape. Hence the resistance and inductance of the secondary core (eddy current), shows up as a distant dependent resistive and inductive component on the primary side (coil). Figure 5 through Figure 8 show a simplified circuit model.

# Feature Description (continued)

Figure 5. Inductor with a Metal Target

Eddy currents generated on the surface of the target can be modeled as a transformer as shown in Figure 6. The coupling between the primary and secondary coils is a function of the distance and characteristics of the conductor. In Figure 6, the inductance  $L_s$  is the inductance of the coil, and  $r_s$  is the parasitic series resistance of the coil. The inductance L(d), which is a function of distance, *d*, is the coupled inductance of the metal target. Likewise, R(d) is the parasitic resistance of the eddy currents.

Figure 6. Metal Target Modeled as L and R With Circulating Eddy Currents

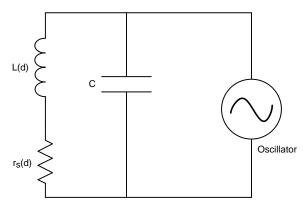

Generating an alternating magnetic field with just an inductor consumes a large amount of power. This power consumption can be reduced by adding a parallel capacitor, turning the right part of Figure 6 into a resonator as shown in Figure 7. In this manner the power consumption is reduced to the eddy and inductor losses  $r_s + R(d)$  only.

Figure 7. LC Tank Connected to Oscillator

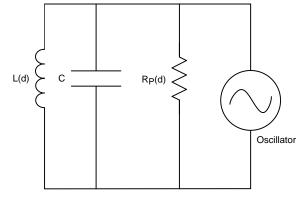

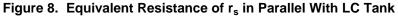

The LDC1000-Q1 device does not directly measure the series resistance. Instead, the device measures the equivalent parallel resonance impedance  $R_P$  (see Figure 8). This representation is equivalent to the representation shown in Figure 8, where the parallel resonance impedance  $R_P(d)$  is given by Equation 1.

Copyright © 2014, Texas Instruments Incorporated

# Feature Description (continued)

$R_{P}(d) = (1/([r_{s} + R(d)]) \times ([L_{s} + L(d)]) / C$  $R_{P} = (1 / r_{s}) \times (L / C)$  (1) (2)

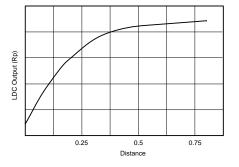

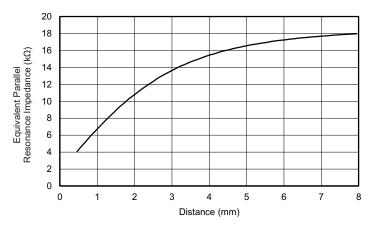

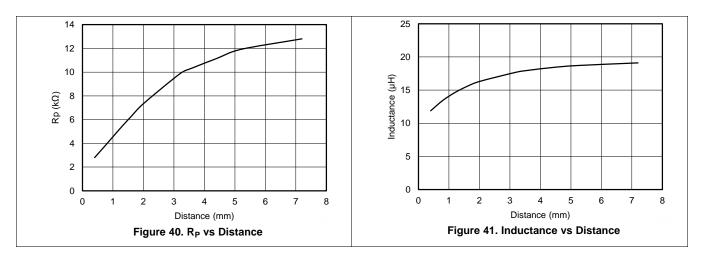

Figure 9 shows the variation in R<sub>P</sub> as a function of distance for a 14-mm diameter PCB coil (23 turns, 4-mil trace width, 4-mil spacing between trace,1-oz copper thickness, FR4). The target metal used is a stainless steel 2-mm thick.

Figure 9. Typical R<sub>P</sub> versus Distance With a 14-mm PCB Coil

### 7.3.2 Measuring Parallel Resonance Impedance and Inductance with LDC1000-Q1

The LDC1000-Q1 device is an inductance-to-digital converter that simultaneously measures the impedance and resonant frequency of an LC resonator. The device accomplishes this task by regulating the oscillation amplitude in a closed-loop configuration to a constant level, while monitoring the energy dissipated by the resonator. By monitoring the amount of power injected into the resonator, the LDC1000-Q1 device can determine the value of  $R_p$ . The device returns this value as a digital value which is inversely proportional to  $R_p$ . In addition, the LDC1000-Q1 device can also measure the oscillation frequency of the LC circuit. This frequency is used to determine the inductance of the LC circuit. The oscillation frequency is returned as a digital value.

The LDC1000-Q1 device supports a wide range of LC combinations with oscillation frequencies ranging from 5 kHz to 5 MHz and  $R_P$  ranging from 798  $\Omega$  to 3.93 M $\Omega$ . This range of  $R_P$  can be viewed as the maximum input range of an ADC. As shown in Figure 9, the range of  $R_P$  is typically much smaller than maximum input range supported by the LDC1000-Q1 device. To achieve better resolution in the desired sensing range, the LDC1000-Q1 device offers a programmable input range through the Rp\_MIN and Rp\_MAX registers. See the *Calculation of Rp\_Min and Rp\_Max* section for how to set these registers.

When the resonance impedance of the sensor,  $R_P$ , drops below the programed  $Rp_MIN$ , the  $R_P$  output of the LDC will clip at the full scale output. An example occurrence of this situation is when a target comes too close to the coil.

## **Feature Description (continued)**

Use Equation 3 to calculate the resonance impedance from the digital output code.

$R_p = (Rp_MAX \times Rp_MIN) / (Rp_MIN \times (1 - Y) + Rp_MAX \times Y)$ , in  $\Omega$ .

Where:

- $Y = Proximity Data / 2^{15}$

- Proximity data is the LDC output, register address 0x21 and 0x22.

(3)

**Example:** If Proximity data (address 0x22 to 0x21) is 5000, Rp\_MIN is 2.394 k $\Omega$ , and Rp\_MAX is 38.785 k $\Omega$ , the resonance impedance is given by:

| $Y = 5000 / 2^{15} = 0.1526$                                                                                                | (4) |

|-----------------------------------------------------------------------------------------------------------------------------|-----|

| $R_P = (38785 \times 2394) \ / \ (2394 \times (1 - 0.1526) + 38785 \times 0.1526) = (92851290) \ / \ (2028.675 + 5918.591)$ | (5) |

| R <sub>P</sub> = 11.683 kΩ                                                                                                  | (6) |

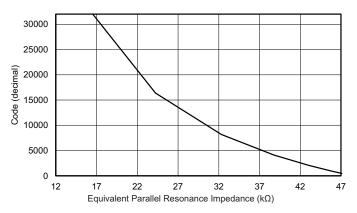

Figure 11 and Figure 12 show the change in RMS noise versus distance and a histogram of noise, with the target at an 0.8-mm distance from the sensor coil. Data was collected with a 14-mm PCB coil (23 turns, 4-mil trace width, 4-mil spacing between trace,1-oz copper thickness, FR4) with a sensing range of 0.125 mm to 1.125 mm. At a distance of 0.8 mm, the RMS noise is approximately 250 nm.

# NOTE

Although the LDC1000-Q1 device has high resolution, the absolute accuracy depends on offset and gain correction which can be achieved by two-point calibration.

# Feature Description (continued)

# 7.3.2.1 Measuring Inductance

www.ti.com

The LDC1000-Q1 device measures the frequency of the oscillation of the sensor by a frequency counter. The frequency counter timing is set by an external clock or crystal. Either the external clock (8 MHz typical) from a microcontroller can be provided on the TBCLK/XIN pin or a crystal can be connected on the TBCLK/XIN and XOUT pins. The clock mode is controlled through clock configuration register (address 0x05). The sensor resonance frequency is derived from the frequency-counter register value (see the *Frequency Counter LSB* (offset = 0x23) [reset = NA] section through the *Frequency Counter MSB* (offset = 0x25) [reset = NA] section) as shown in Equation 7.

$f_{sensor} = (1/3) \times (f_{ext} / f_{count}) \times t_{res}$

where

- f<sub>sensor</sub> is the sensor frequency

- f<sub>ext</sub> is the frequency of the external clock or crystal

- f<sub>count</sub> is the value obtained from the Frequency Counter Data register (see the Frequency Counter LSB (offset = 0x23) [reset = NA] section through the Frequency Counter MSB (offset = 0x25) [reset = NA] section)

- $t_{res}$  is the programmed response time (see the LDC Configuration (offset = 0x04) [reset = 0x1B] section) (7)

The inductance in H can be calculated with Equation 8.

L=1 / [C ×  $(2 \times \pi \times f_{sensor})^2$ ]

where

• C is the parallel capacitance of the resonator

#### 7.3.2.1.1 Example

If the following values are selected,  $f_{ext} = 6$  Mhz,  $t_{res} = 6144$ , C = 10 0pF, and measured  $f_{count} = 3000$  (decimal) (see the *Frequency Counter LSB (offset = 0x23) [reset = NA]* section through the *Frequency Counter MSB (offset = 0x25) [reset = NA]* section) then:

$f_{sensor} = 1/3 \times (6000000 / 3000) \times (6144) = 4.096 \text{ MHz}$

Now use Equation 10.

```

L = 1 / [C \times (2 \times \pi \times f_{sensor})^2]

```

where

•  $L = 15.098 \,\mu H$  (10)

The accuracy of measurement largely depends upon the choice of the external time-base clock (TBCLK) or the crystal oscillator (XIN and XOUT).

# 7.4 Device Functional Modes

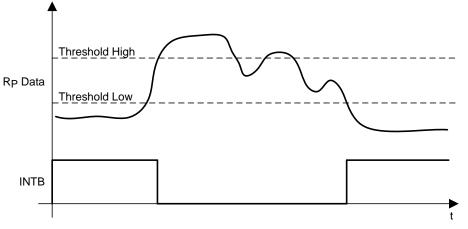

### 7.4.1 INTB Pin Modes

The INTB pin is a configurable output pin which can be used to drive an interrupt on an MCU. The LDC1000-Q1 device provides three different modes on the INTB pin which include:

- 1. Comparator mode

- 2. Wake-up mode

- 3. DRDY mode

The LDC1000-Q1 device has a built-in high trigger and low trigger threshold registers that can be a comparator with programmable hysteresis or a special mode that is used to wake-up an MCU. The following sections describe these modes in detail.

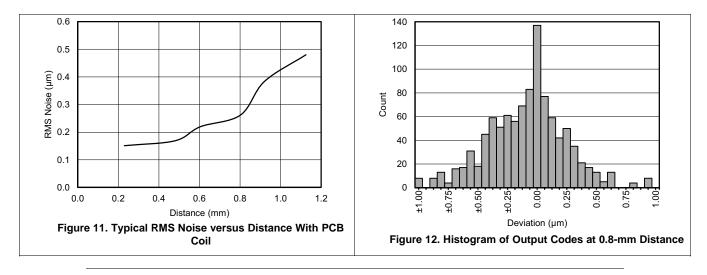

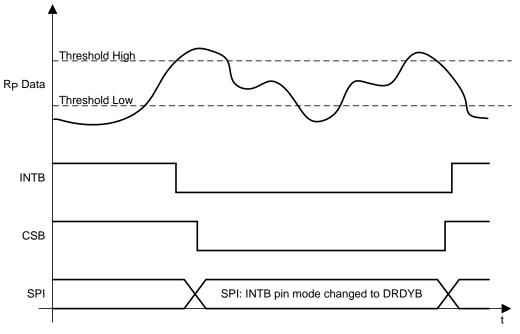

### 7.4.1.1 Comparator Mode

In the comparator mode, the INTB pin is asserted or de-asserted when the proximity register value increases above the threshold high registers or decreases below the threshold low registers respectively. In this mode, the function of the LDC1000-Q1 device is a proximity switch with programmable hysteresis.

(8)

(9)

# **Device Functional Modes (continued)**

Figure 13. Behavior of the INTB Pin in Comparator Mode

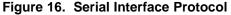

## 7.4.1.2 Wake-Up Mode

In wake-up mode, the INTB pin is asserted when proximity register value increases above the threshold high registers and is deasserted when wake-up mode is disabled in the INTB pin mode register.

This mode can wake-up an MCU that is in sleep mode to conserve power.

Figure 14. Behavior of the INTB Pin in Wake-Up Mode

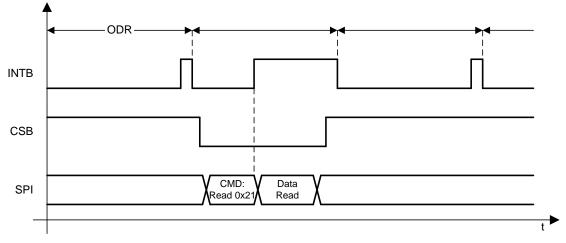

# 7.4.1.3 DRDYB Mode

In DRDY mode (default), the INTB pin is asserted every time the conversion data is available and is deasserted when the read command on register 0x21 is registered internally. If the read command is in progress, the pin is pulsed instead.

# **Device Functional Modes (continued)**

Figure 15. Behavior of the INTB Pin in DRDYB Mode

# 7.5 Programming

## 7.5.1 Digital Interface

The LDC1000-Q1 device uses a 4-wire SPI interface to access control and data registers. The LDC1000-Q1 device is an SPI slave device and does not initiate any transactions.

## 7.5.1.1 SPI Description

A typical serial interface transaction begins with an 8-bit instruction that is comprised of a read-write (R/W) bit (MSB, R = 1) and a 7-bit address of the register followed by a data field that is typically 8 bits. However, the data field can be extended to a multiple of 8 bits by providing sufficient SPI clocks. See the *Extended SPI Transactions* section.

### **Programming (continued)**

Each assertion of the chip select bar (CSB) begins a new register access. The R/W bit in the command field configures the direction of the access. A value of 0 indicates a write operation and a value of 1 indicates a read operation. All output data is driven on the falling edge of the serial clock SCLK, and all input data is sampled on the rising edge of the serial clock SCLK. Data is written into the register on the rising edge of the 16th clock. Deasserting the CSB pin after the 16th clock is required. No data write occurs if the CSB pin is deasserted before the 16th clock.

## 7.5.1.2 Extended SPI Transactions

A transaction can be extended to multiple registers by keeping the CSB pin asserted beyond the stated 16 clocks. In this mode, the register addresses increment automatically. The CSB pin must be asserted during 8  $\times$  (1+ *N*) clock cycles of SCLK, where *N* is the amount of bytes to write or read during the transaction.

During an extended read access, the SDO pin outputs register contents every 8 clock cycles after the initial 8 clocks of the command field. During an extended write access, the data is written to the registers every 8 clock cycles after the initial 8 clocks of the command field.

Extended transactions can be used to read 16-bits of proximity data and 24-bits of frequency data all in one SPI transaction by initiating a read from register 0x21.

# 7.6 Register Map

|                                     | Table 1. Register Map ( / / |                     |         |          |                                       |                |                |              |       |           |          |  |

|-------------------------------------|-----------------------------|---------------------|---------|----------|---------------------------------------|----------------|----------------|--------------|-------|-----------|----------|--|

| REGISTER NAME                       | ADDRESS                     | TYPE <sup>(3)</sup> | DEFAULT | BIT 7    | BIT 6                                 | BIT 5          | BIT 4          | BIT 3        | BIT 2 | BIT 1     | BIT 0    |  |

| Device ID                           | 0x00                        | R                   | 0x80    |          | •                                     | -              | Devid          | ce ID        |       | ·         |          |  |

| Rp_MAX                              | 0x01                        | R/W                 | 0x0E    |          |                                       |                | Rp Ma          | ximum        |       |           |          |  |

| Rp_MIN                              | 0x02                        | R/W                 | 0x14    |          |                                       |                | Rp Mir         | nimum        |       |           |          |  |

| Sensor Frequency                    | 0x03                        | R/W                 | 0x45    |          |                                       |                | Min Resonati   | ng Frequency |       |           |          |  |

| LDC Configuration                   | 0x04                        | R/W                 | 0x1B    |          | Reserved(000) Amplitude Response Time |                |                |              |       |           |          |  |

| Clock Configuration                 | 0x05                        | R/W                 | 0x01    |          | Reserved(000000) CLK_SEL C            |                |                |              |       |           |          |  |

| Comparator<br>Threshold High<br>LSB | 0x06                        | R/W                 | 0xFF    |          | Threshold High LSB                    |                |                |              |       |           |          |  |

| Comparator<br>Threshold High<br>MSB | 0x07                        | R/W                 | 0xFF    |          | Threshold High MSB                    |                |                |              |       |           |          |  |

| Comparator<br>Threshold Low<br>LSB  | 0x08                        | R/W                 | 0x00    |          | Threshold Low LSB                     |                |                |              |       |           |          |  |

| Comparator<br>Threshold Low<br>MSB  | 0x09                        | R/W                 | 0x00    |          |                                       |                | Threshold      | Low MSB      |       |           |          |  |

| INTB Pin<br>Configuration           | 0x0A                        | R/W                 | 0x00    |          | I                                     | Reserved(00000 | ))             |              |       | INTB_MODE |          |  |

| Power<br>Configuration              | 0x0B                        | R/W                 | 0x00    |          |                                       | R              | eserved(000000 | 0)           |       |           | PWR_MODE |  |

| Status                              | 0x20                        | R                   |         | OSC Dead | DRDYB                                 | Wake-up        | Comparator     |              | Dor   | n't Care  |          |  |

| Proximity Data LSB                  | 0x21                        | R                   |         |          |                                       |                | Proximity      | Data[7-0]    |       |           |          |  |

| Proximity Data<br>MSB               | 0x22                        | R                   |         |          | Proximity Data[15-8]                  |                |                |              |       |           |          |  |

| Frequency Counter<br>Data LSB       | 0x23                        | R                   |         |          | ODR LSB                               |                |                |              |       |           |          |  |

| Frequency Counter<br>Data Mid-Byte  | 0x24                        | R                   |         |          | ODR Mid Byte                          |                |                |              |       |           |          |  |

| Frequency Counter<br>Data MSB       | 0x25                        | R                   |         |          |                                       |                | ODR            | MSB          |       |           |          |  |

Table 1, Register Map<sup>(1)(2)</sup>

Values of bits which are unused should be set to default values only.

LEGEND R/W = read/write. R = read only. W = write only

When the device is in active mode (the PWR\_MODE bit is SET), registers 0x01 through 0x05 are read only (R).

# 7.6.1 Register Description

# 7.6.1.1 Revision ID (offset = 0x00) [reset = 0x80]

## Figure 17. Revision ID Register

| 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------------|---|---|---|---|---|---|---|--|

| Revision ID |   |   |   |   |   |   |   |  |

|             | R |   |   |   |   |   |   |  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 2. Revision ID Field Descriptions

| Bit | Field       | Туре | Reset | Description             |

|-----|-------------|------|-------|-------------------------|

| 7-0 | Revision ID | R    | 0x080 | Revision ID of silicon. |

LDC1000-Q1

Figure 18. Rp\_MAX Register

| 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|------------|---|---|---|---|---|---|---|--|--|

| Rp Maximum |   |   |   |   |   |   |   |  |  |

| R/W        |   |   |   |   |   |   |   |  |  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

| Table 3. | Rp    | MAX | Field  | Descri | otions |

|----------|-------|-----|--------|--------|--------|

|          | · `P_ |     | 1 1010 | 200011 |        |

| Bit               | Field               | Туре        | Reset                    | Description                                                                                                           |

|-------------------|---------------------|-------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------|

| <b>Bit</b><br>7-0 | Field<br>Rp Maximum | Type<br>R/W | P_MAX F<br>Reset<br>0x0E | -                                                                                                                     |

|                   |                     |             |                          | 0x09 = 349.066<br>0x0A = 249.333<br>0x0B = 193.926<br>0x0C = 145.444<br>0x0D = 109.083                                |

|                   |                     |             |                          | 0x0E = 83.111<br>0x0F = 64.642<br>0x10 = 48.481<br>0x11 = 38.785<br>0x12 = 27.704<br>0x13 = 21.547                    |

|                   |                     |             |                          | 0x13 = 21.547 $0x14 = 16.16$ $0x15 = 12.12$ $0x16 = 9.235$ $0x17 = 7.182$ $0x18 = 5.387$                              |

|                   |                     |             |                          | 0x18 = 3.387 $0x19 = 4.309$ $0x1A = 3.078$ $0x1B = 2.394$ $0x1C = 1.796$ $0x1D = 1.347$ $0x1E = 1.026$ $0x1F = 0.798$ |

ISTRUMENTS

EXAS

# 7.6.1.3 Rp\_MIN (offset = 0x02) [reset = 0x14]

# Figure 19. Rp\_MIN Register

| 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|------------|---|---|---|---|---|---|---|--|--|

| Rp Minimum |   |   |   |   |   |   |   |  |  |

| R/W        |   |   |   |   |   |   |   |  |  |

#### LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 4. Rp\_MIN Field Descriptions

| Bit | Field      | Туре | Reset | Description                                                                                                            |

|-----|------------|------|-------|------------------------------------------------------------------------------------------------------------------------|

| 7-0 | Rp Minimum | R/W  | 0x014 | Minimum $R_P$ that the LDC1000-Q1 device must measure.<br>Configures the input dynamic range of the LDC1000-Q1 device. |

|     |            |      |       | Register setting for Rp_MIN ( $k\Omega$ ):                                                                             |

|     |            |      |       | 0x20 = 3926.991                                                                                                        |

|     |            |      |       | 0x21 = 3141.593                                                                                                        |

|     |            |      |       | 0x22 = 2243.995                                                                                                        |

|     |            |      |       | 0x23 = 1745.329                                                                                                        |

|     |            |      |       | 0x24 = 1308.997                                                                                                        |

|     |            |      |       | 0x25 = 981.748                                                                                                         |

|     |            |      |       | 0x26 = 747.998                                                                                                         |

|     |            |      |       | 0x27 = 581.776                                                                                                         |

|     |            |      |       | 0x28 = 436.332                                                                                                         |

|     |            |      |       | 0x29 = 349.066                                                                                                         |

|     |            |      |       | 0x2A = 249.333                                                                                                         |

|     |            |      |       | 0x2B = 193.926                                                                                                         |

|     |            |      |       | 0x2C = 145.444                                                                                                         |

|     |            |      |       | 0x2D = 109.083                                                                                                         |

|     |            |      |       | 0x2E = 83.111                                                                                                          |

|     |            |      |       | 0x2F = 64.642                                                                                                          |

|     |            |      |       | 0x30 = 48.481                                                                                                          |

|     |            |      |       | 0x31 = 38.785                                                                                                          |

|     |            |      |       | 0x32 = 27.704                                                                                                          |

|     |            |      |       | 0x33 = 21.547                                                                                                          |

|     |            |      |       | 0x34 = 16.16                                                                                                           |

|     |            |      |       | 0x35 = 12.12                                                                                                           |

|     |            |      |       | 0x36 = 9.235                                                                                                           |

|     |            |      |       | 0x37 = 7.182                                                                                                           |

|     |            |      |       | 0x38 = 5.387                                                                                                           |

|     |            |      |       | 0x39 = 4.309                                                                                                           |

|     |            |      |       | 0x3A = 3.078                                                                                                           |

|     |            |      |       | 0x3B = 2.394                                                                                                           |

|     |            |      |       | 0x3C = 1.796                                                                                                           |

|     |            |      |       | 0x3D = 1.347                                                                                                           |

|     |            |      |       | 0x3E = 1.026                                                                                                           |

|     |            |      |       | 0x3F = 0.798                                                                                                           |

**Table 5. Sensor Frequency Field Descriptions**

| Bit | Field                    | Туре | Reset | Description                                                                                                                                                                                       |  |  |

|-----|--------------------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7-0 | Min Resonating Frequency | R/W  | 0x45  | Sets the minimum resonating frequency to approximately 20% below the lowest resonating frequency of the sensor with ne target in front. Use the formula below to determine the value or register. |  |  |

|     |                          |      |       | $N = 68.94 \times \log_{10}(f / 2000)$                                                                                                                                                            |  |  |

|     |                          |      |       | where                                                                                                                                                                                             |  |  |

|     |                          |      |       | <ul> <li>N = Register Value. Round to nearest value.</li> </ul>                                                                                                                                   |  |  |

|     |                          |      |       | • f = 20% below resonating frequency,<br>Hz (11)                                                                                                                                                  |  |  |

|     |                          |      |       | <b>Example:</b> Sensor frequency (f <sub>sensor</sub> ) = 1 MHz                                                                                                                                   |  |  |

|     |                          |      |       | $f = 0.8 \times 1 \text{ MHz} = 800 \text{ KHz}$ (12)                                                                                                                                             |  |  |

|     |                          |      |       | $N = 68.94 \times \log_{10}(800 \text{ KHz} / 2000) = \text{Round to nearest}$<br>whole number (179.38) = 179 (Value to be programmed                                                             |  |  |

|     |                          |      |       | in the sensor frequency register) (13)                                                                                                                                                            |  |  |

# 7.6.1.5 LDC Configuration (offset = 0x04) [reset = 0x1B]

# Figure 21. LDC Configuration Register

| 7 | 6        | 5 | 4   | 3      | 2             | 1 | 0 |  |

|---|----------|---|-----|--------|---------------|---|---|--|

|   | Reserved |   | Amp | litude | Response Time |   |   |  |

|   | _        |   |     | W      | R/W           |   |   |  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

# **Table 6. LDC Configuration Field Descriptions**

| Bit | Field         | Туре                                    | Reset | Description                    |

|-----|---------------|-----------------------------------------|-------|--------------------------------|

| 7-5 | Reserved      | —                                       | —     | Reserved to 0                  |

| 4-3 | Amplitude     | R/W 0x1B Sets the oscillation amplitude |       | Sets the oscillation amplitude |

|     |               |                                         |       | 00: 1 V                        |

|     |               |                                         |       | 01: 2 V                        |

|     |               |                                         |       | 10: 4 V                        |

|     |               |                                         |       | 11: Reserved                   |

| 2-0 | Response Time | R/W                                     | 0x1B  | Sets the response time         |

|     |               |                                         |       | 000: Reserved                  |

|     |               |                                         |       | 001: Reserved                  |

|     |               |                                         |       | 010: 192                       |

|     |               |                                         |       | 011: 384                       |

|     |               |                                         |       | 100: 768                       |

|     |               |                                         |       | 101: 1536                      |

|     |               |                                         |       | 110: 3072                      |

|     |               |                                         |       | 111: 6144                      |

# 7.6.1.4 Sensor Frequency (offset = 0x03) [reset = 0x45]

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

| 7                        | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|--------------------------|-----|---|---|---|---|---|---|--|--|

| Min Resonating Frequency |     |   |   |   |   |   |   |  |  |

|                          | R/W |   |   |   |   |   |   |  |  |

| e | 20. | Sensor | Freque | ency F | Register |

|---|-----|--------|--------|--------|----------|

RUMENTS

AS

### 7.6.1.6 Clock Configuration (offset = 0x05) [reset = 0x01]

#### Figure 22. Clock Configuration Register

| 7 | 6        | 5 | 4 | 3 | 2 | 1 | 0 |

|---|----------|---|---|---|---|---|---|

|   | Reserved |   |   |   |   |   |   |

|   | R/W      |   |   |   |   |   |   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 7. Clock Configuration Field Descriptions

|     |         |      | -     | -                                                                                                                              |

|-----|---------|------|-------|--------------------------------------------------------------------------------------------------------------------------------|

| Bit | Field   | Туре | Reset | Description                                                                                                                    |

| 7-2 | Resrved | _    | _     | Reserved to 0                                                                                                                  |

| 1   | CLK_SEL | R/W  | 0x01  | 1:External crystal used for frequency counter (XIN or XOUT).<br>0:External time-base clock used for frequency counter (TBCLK). |

| 0   | CLK_PD  | R/W  | 0x01  | 1:Disable external time base clock. Crystal oscillator<br>power down.<br>0:Enable External time base clock.                    |

### 7.6.1.7 Comparator Threshold High LSB (offset = 0x06) [reset = 0xFF]

## Figure 23. Comparator Threshold High LSB Register

| 7                      | 6                    | 5                    | 4                    | 3                    | 2                    | 1                    | 0                    |

|------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| Threshold<br>High[7:0] | Threshold<br>High[6] | Threshold<br>High[5] | Threshold<br>High[4] | Threshold<br>High[3] | Threshold<br>High[2] | Threshold<br>High[1] | Threshold<br>High[0] |

| R/W                    | R/W                  | R/W                  | R/W                  | R/W                  | R/W                  | R/W                  | R/W                  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### **Table 8. Comparator Threshold High LSB Field Descriptions**

| Bit | Field                                     | Туре | Reset | Description                                                                                                                                                                                                                                                                                                   |

|-----|-------------------------------------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | Threshold High LSB<br>Threshold High[7:0] | R/W  | 0xFF  | Least Significant byte (LSB) of the threshold high register. This register is a buffer. A read reflects the current value of the threshold high[7:0] register. See the <i>Comparator Threshold High MSB</i> (offset = $0x07$ ) [reset = $0xFF$ ] section for details on updating the threshold high register. |

### 7.6.1.8 Comparator Threshold High MSB (offset = 0x07) [reset = 0xFF]

### Figure 24. Comparator Threshold High MSB Register

| 7                     | 6                     | 5                     | 4                     | 3                     | 2                     | 1                    | 0                    |

|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|----------------------|----------------------|

| Threshold<br>High[15] | Threshold<br>High[14] | Threshold<br>High[13] | Threshold<br>High[12] | Threshold<br>High[11] | Threshold<br>High[10] | Threshold<br>High[9] | Threshold<br>High[8] |

| R/W                   | R/W                   | R/W                   | R/W                   | R/W                   | R/W                   | R/W                  | R/W                  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 9. Comparator Threshold High MSB Field Descriptions

| Bit | Field                                      | Туре | Reset | Description                                                                                                                                                                                                                                                                                                      |

|-----|--------------------------------------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | Threshold High MSB<br>Threshold High[15:8] | R/W  | 0xFF  | Most significant byte (MSB) of the threshold high register. A write to this register copies the contents of the 0x06 register and writes to the threshold high register[15:0]. A read returns the threshold high [15:8] register. To update the threshold high register write register 0x06 first and then 0x07. |

RUMENTS

# 7.6.1.9 Comparator Threshold Low LSB (offset = 0x08) [reset = 0x00]

#### Figure 25. Comparator Threshold Low LSB Register

| 7                     | 6                   | 5                   | 4                   | 3                   | 2                   | 1                   | 0                   |

|-----------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| Threshold<br>Low[7:0] | Threshold<br>Low[6] | Threshold<br>Low[5] | Threshold<br>Low[4] | Threshold<br>Low[3] | Threshold<br>Low[2] | Threshold<br>Low[1] | Threshold<br>Low[0] |

| R/W                   | R/W                 | R/W                 | R/W                 | R/W                 | R/W                 | R/W                 | R/W                 |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 10. Comparator Threshold Low LSB Field Descriptions

| Bit | Field                                   | Туре | Reset | Description                                                                                                                                                                                                                                                                                       |

|-----|-----------------------------------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | Threshold Low LSB<br>Threshold Low[7:0] | R/W  |       | Least significant byte of the threshold low value. This register is a buffer. A read reflects the current value of the threshold low [7:0] register. See the <i>Comparator Threshold Low MSB (offset</i> = $0x09$ ) [reset = $0x00$ ] section for details on updating the threshold low register. |

### 7.6.1.10 Comparator Threshold Low MSB (offset = 0x09) [reset = 0x00]

#### Figure 26. Comparator Threshold Low MSB Register

| 7                    | 6                    | 5                    | 4                    | 3                    | 2                    | 1                   | 0                   |

|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|---------------------|---------------------|

| Threshold<br>Low[15] | Threshold<br>Low[14] | Threshold<br>Low[13] | Threshold<br>Low[12] | Threshold<br>Low[11] | Threshold<br>Low[10] | Threshold<br>Low[9] | Threshold<br>Low[8] |

| R/W                  | R/W                  | R/W                  | R/W                  | R/W                  | R/W                  | R/W                 | R/W                 |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

### Table 11. Comparator Threshold Low MSB Field Descriptions

| Bit | Field                                    | Туре | Reset | Description                                                                                                                                                                                                                                                                                                    |

|-----|------------------------------------------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | Threshold Low MSB<br>Threshold Low[15:8] | R/W  | 0x00  | Most significant byte of the threshold low register. A write to this register copies the contents of the 0x08 register and writes to the threshold low register[15:0]. A read returns the threshold low [15:8] register. To update the threshold low register write register address 0x08 first and then 0x09. |

# 7.6.1.11 INTB Pin Configuration (offset = 0x0A) [reset = 0x00]

## Figure 27. INTB Pin Configuration Register

| 7 | 6 | 5        | 4 | 3 | 2 | 1    | 0 |

|---|---|----------|---|---|---|------|---|

|   |   | Reserved |   |   |   | Mode |   |

|   |   | _        |   |   |   | R/W  |   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

# **Table 12. INTB Pin Configuration Field Descriptions**

| Bit | Field    | Туре | Reset | Description                                                                                                                                                                                                                                                 |

|-----|----------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:3 | Reserved | —    | —     | Reserved to 0                                                                                                                                                                                                                                               |

| 2:0 | Mode     | R/W  | 0x00  | <ul> <li>100: DRDYB enabled on the INTB pin</li> <li>010: The INTB pin indicates the status of the comparator output</li> <li>001: Wake-up enabled on the INTB pin</li> <li>000: All modes disabled</li> <li>All other combinations are reserved</li> </ul> |

#### 7.6.1.12 Power Configuration (offset = 0x0B) [reset = 0x00]

#### Figure 28. Power Configuration Register

| 7 | 6        | 5 | 4 | 3 | 2 | 1 | 0        |

|---|----------|---|---|---|---|---|----------|

|   | Reserved |   |   |   |   |   | PWR_MODE |

|   |          |   |   |   |   |   |          |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

### Table 13. Power Configuration Field Descriptions

| Bit | Field    | Туре | Reset | Description                                               |

|-----|----------|------|-------|-----------------------------------------------------------|

| 7:1 | Reserved | _    | _     | Reserved to 0                                             |

| 0   | PWR_MODE | R/W  | 0x00  | 0: Stand-by mode<br>1: Active mode. Conversion is enabled |

## 7.6.1.13 Status (offset = 0x20) [reset = NA]

#### Figure 29. Status Register

| 7          | 6          | 5       | 4          | 3 | 2     | 1    | 0 |

|------------|------------|---------|------------|---|-------|------|---|

| OSC status | Data Ready | Wake-up | Comparator |   | Don't | Care |   |

| R          | R          | R       | R          | R |       |      |   |

|            |            |         |            |   |       |      |   |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 14. Status Field Descriptions

| Bit | Field      | Туре | Reset | Description                                                               |  |  |

|-----|------------|------|-------|---------------------------------------------------------------------------|--|--|

| 7   | OSC status | R    | NA    | 1: Indicates that the oscillator is overloaded and has stopped            |  |  |

|     |            |      |       | 0: Oscillator is working                                                  |  |  |

| 6   | Data Ready | R    | NA    | 0: Data is ready to be read                                               |  |  |

|     |            |      |       | 1: No new data is available                                               |  |  |

| 5   | Wake-up    | R    | NA    | 0: Wake-up triggered. Proximity data is more than the thresho high value. |  |  |

|     |            |      |       | 1: Wake-up is disabled                                                    |  |  |

| 4   | Comparator | R    | NA    | 0: Proximity data is more than the threshold high value                   |  |  |

|     |            |      |       | 1: Proximity data is less than the threshold low value                    |  |  |

| 3:0 | Don't Care | R    | NA    |                                                                           |  |  |

### 7.6.1.14 Proximity Data LSB (offset = 0x21) [reset = NA]

### Figure 30. Proximity Data LSB Register

| 7                    | 6                    | 5                    | 4                    | 3                    | 2                    | 1                    | 0                    |

|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| Proximity<br>Data[7] | Proximity<br>Data[6] | Proximity<br>Data[5] | Proximity<br>Data[4] | Proximity<br>Data[3] | Proximity<br>Data[2] | Proximity<br>Data[1] | Proximity<br>Data[0] |

| R                    | R                    | R                    | R                    | R                    | R                    | R                    | R                    |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 15. Proximity Data LSB Field Descriptions

| Bit | Field               | Туре | Reset | Description                              |

|-----|---------------------|------|-------|------------------------------------------|

| 7:0 | Proximity Data[7:0] | R    | NA    | Least significant byte of proximity data |

## 7.6.1.15 Proximity Data MSB (offset = 0x22) [reset = NA]

Figure 31. Proximity Data MSB Register

|   | 7         | 6         | 5         | 4         | 3         | 2         | 1         | 0         |

|---|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

|   | Proximity |

| ļ | Data[15]  | Data[14]  | Data[13]  | Data[12]  | Data[11]  | Data[10]  | Data[9]   | Data[8]   |

|   | R         | R         | R         | R         | R         | R         | R         | R         |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 16. Proximity Data MSB Field Descriptions

| Bit | Field                | Туре | Reset | Description                             |

|-----|----------------------|------|-------|-----------------------------------------|

| 7:0 | Proximity data[15:8] | R    | NA    | Most significant byte of proximity data |

### 7.6.1.16 Frequency Counter LSB (offset = 0x23) [reset = NA]

#### Figure 32. Frequency Counter LSB Register

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ODR[7] | ODR[6] | ODR[5] | ODR[4] | ODR[3] | ODR[2] | ODR[1] | ODR[0] |

| R      | R      | R      | R      | R      | R      | R      | R      |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 17. Frequency Counter LSB Field Descriptions

| Bit | Field               | Туре | Reset | Description                                                                                                                          |

|-----|---------------------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | ODR LSB<br>ODR[7:0] | R    | NA    | LSB of output data rate. Sensor frequency can be calculated using the output data rate. See the <i>Measuring Inductance</i> section. |

### 7.6.1.17 Frequency Counter Mid-Byte (offset = 0x24) [reset = NA]

#### Figure 33. Frequency Counter Mid-Byte Register

| 7       | 6       | 5       | 4       | 3       | 2       | 1      | 0      |

|---------|---------|---------|---------|---------|---------|--------|--------|

| ODR[15] | ODR[14] | ODR[13] | ODR[12] | ODR[11] | ODR[10] | ODR[9] | ODR[8] |

| R       | R       | R       | R       | R       | R       | R      | R      |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

### Table 18. Frequency Counter Mid-Byte Field Descriptions

| Bit | Field                     | Туре | Reset | Description                     |

|-----|---------------------------|------|-------|---------------------------------|

| 7:0 | ODR Mid byte<br>ODR[15:8] | R    | NA    | Middle byte of output data rate |

www.ti.com

# 7.6.1.18 Frequency Counter MSB (offset = 0x25) [reset = NA]

## Figure 34. Frequency Counter MSB Register

| 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ODR[23] | ODR[22] | ODR[21] | ODR[20] | ODR[19] | ODR[18] | ODR[17] | ODR[16] |