#### LMF40 High Performance 4th-Order Switched-Capacitor Butterworth Low-Pass Filter

#### **General Description**

The LMF40 is a versatile, easy to use, precision 4th-order Butterworth low-pass filter fabricated using National's high performance LMCMOS process. Switched-capacitor techniques eliminate external component requirements and allow a clock-tunable cutoff frequency. The ratio of the clock frequency to the low-pass cutoff frequency is internally set to 50-to-1 (LMF40-50) or 100-to-1 (LMF40-100). A Schmitt trigger clock input stage allows two clocking options, either self-clocking (via an external resistor and capacitor) for stand-alone applications, or for tighter cutoff frequency control, an external TTL or CMOS logic compatible clock can be applied. The maximally flat passband frequency response together with a DC gain of 1 V/V allows cascading LMF40 sections together for higher-order filtering.

#### **Features**

- Cutoff frequency range of 0.1 Hz to 40 kHz

- Cutoff frequency accuracy of ±1.0%, maximum

- Low offset voltage, ±100 mV, maximum, ±5V supply

- Low clock feedthrough of 5 mV<sub>P-P</sub>, typical

- Dynamic range of 88 dB, typical

- No external components required

- 8-pin mini-DIP or 14-pin wide-body small-outline packages

- 4V to 14V single/dual supply operation

- Cutoff frequency set by external or internal clock

- Pin-compatible with MF4

#### **Applications**

- Communication systems

- Instrumentation

- Automated control systems

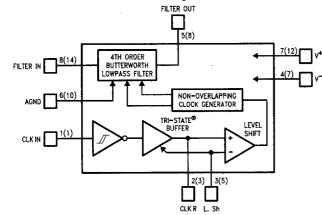

#### **Block and Connection Diagrams**

\*Pin numbers in parentheses are for the 14-pin package

#### TL/H/10557-1

#### **Ordering Information**

| Industrial ( $-40^{\circ}$ C $\leq$ T <sub>A</sub> $\leq$ $+85^{\circ}$ C)  | Package |

|-----------------------------------------------------------------------------|---------|

| LMF40CIN-50, LMF40CIN-100                                                   | N08E    |

| LMF40CIWM-50                                                                | M14B    |

| LMF40CIWM-100                                                               | M14B    |

| Military ( $-55^{\circ}$ C $\leq$ T <sub>A</sub> $\leq$ + 125 $^{\circ}$ C) |         |

| LMF40CMJ-50, LMF40CMJ-100                                                   | J08A    |

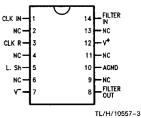

# Dual-In-Line Package SLK IN 1 8 FILTER CLK R 2 7 V' L. Sh 3 6 AGND FILTER OUT TL/H/10557-2

#### Small-Outline-Wide-Body Package

Top View

#### **Absolute Maximum Ratings**

(Notes 1 & 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage (V+-V-) Voltage at Any Pin  $V^{-} - 0.2V$  to  $V^{+} + 0.2V$

Input Current at Any Pin (Note 13) 5 mA

Package Input Current (Note 13) 20 mA Power Dissipation (Note 14) 500 mW

Storage Temperature

-65°C to +150°C

Lead Temperature

N Package, Soldering (10 sec.) +260°C J Package, Soldering (10 sec.) +300°C

WM Package, Vapor Phase (60 sec.) (Note 16) +215°C WM Package, Infrared (15 sec.) +220°C

ESD Susceptibility (Note 12) 2000V Pin 1 CLK IN 1700V

#### Operating Ratings (Notes 1 & 2)

Temperature Range  $T_{MIN} \le T_A \le T_{MAX}$ LMF40CIN-50, LMF40CIN-100 LMF40CIWM-50. LMF40CIWM-100  $-40^{\circ}\text{C} \leq \text{T}_{\text{A}} \leq +85^{\circ}\text{C}$

LMF40CMJ-50, LMF40CMJ-100  $-55^{\circ}$ C  $\leq T_{A} \leq +125^{\circ}$ C Supply Voltage Range (V+ - V-)

#### Filter Electrical Characteristics

The following specifications apply for  $f_{CLK} = 500$  kHz. Boldface limits apply for  $f_A = f_J = f_{MIN}$  to  $f_{MAX}$ : All other limits  $f_A$  $= T_{.1} = 25^{\circ}C.$

| Symbol                                | Parameter                                                                  | Conditions                 | Typical<br>(Note 10) | Limits<br>(Note 11)                                                                    | Units<br>(Limit)      |

|---------------------------------------|----------------------------------------------------------------------------|----------------------------|----------------------|----------------------------------------------------------------------------------------|-----------------------|

| V+ = +5V, V                           | = -5V                                                                      |                            |                      |                                                                                        |                       |

| fclk                                  | Clock Frequency Range (Note 17)                                            |                            | 5                    | 2                                                                                      | Hz (min)<br>MHz (max) |

| Is                                    | Supply Current                                                             | CMJ<br>CIN, CIJ, CIWM      | *.                   | 3.5 / <b>7.0</b><br>3.5 / <b>5.0</b>                                                   | mA (max)<br>mA (max)  |

| H <sub>O</sub>                        | DC Gain                                                                    | R <sub>Source</sub> ≤ 2 kΩ |                      | +0.05 / + <b>0.05</b><br>-0.15 / - <b>0.20</b>                                         | dB (max)<br>dB (min)  |

| fclk/fc                               | Clock to Cutoff<br>Frequency Ratio<br>(Note 3)<br>LMF40-50<br>LMF40-100    |                            |                      | 49.80 ± 0.8% / <b>49.80</b> ± <b>1.0%</b><br>99.00 ± 0.8% / <b>99.00</b> ± <b>1.0%</b> | (max)<br>(max)        |

| Δf <sub>CLK</sub> /f <sub>c</sub> /ΔT | Clock to Cutoff Frequency Ratio Temperature Coefficient LMF40-50 LMF40-100 |                            | 5<br>5               |                                                                                        | ppm/°C<br>ppm/°C      |

| A <sub>MIN</sub>                      | Stopband Attenuation                                                       | At 2 f <sub>c</sub>        |                      | 24.0                                                                                   | dB (min)              |

Filter Electrical Characteristics (Continued)

The following specifications apply for  $f_{CLK} = 500$  kHz. Boldface limits apply for  $T_A = T_J = T_{MIN}$  to  $T_{MAX}$ : All other limits  $T_A = T_J = 25^{\circ}C$ .

| Symbol          | Parameter                                                            | Conditions                                                          | Typical<br>(Note 10) | Limits<br>(Note 11)                                                                    | Units<br>(Limit)     |

|-----------------|----------------------------------------------------------------------|---------------------------------------------------------------------|----------------------|----------------------------------------------------------------------------------------|----------------------|

| V+ = +5         | $V, V^- = -5V$ (Continued)                                           |                                                                     |                      |                                                                                        |                      |

| Vos             | Unadjusted DC<br>Offset Voltage<br>LMF40-50<br>LMF40-100             |                                                                     |                      | ±80 / ±100<br>±80 / ±100                                                               | mV (max)<br>mV (max) |

| v <sub>o</sub>  | Output Swing                                                         | $R_L = 5 k\Omega$                                                   |                      | +3.9 / + <b>3.7</b><br>-4.2 / - <b>4.0</b>                                             | V (min)<br>V (max)   |

| I <sub>SC</sub> | Output Short Circuit<br>Current (Note 8)                             | Source<br>Sink                                                      | 90<br>2.2            |                                                                                        | mA<br>mA             |

|                 | Dynamic Range<br>(Note 4)                                            |                                                                     | 88                   |                                                                                        | dB                   |

|                 | Additional Magnitude<br>Response Test Points<br>(Note 6)<br>LMF40-50 | $f_{\text{IN}} = 12  \text{kHz}$<br>$f_{\text{IN}} = 9  \text{kHz}$ |                      | -7.50 ±0.26 / - <b>7.50</b> ± <b>0.30</b><br>-1.46 ±0.12 / - <b>1.46</b> ± <b>0.16</b> | dB (max)<br>dB (max) |

|                 | LMF40-100                                                            | $f_{IN} = 6 \text{ kHz}$<br>$f_{IN} = 4.5 \text{ kHz}$              |                      | -7.15 ±0.26 / -7.15 ±0.30<br>-1.42 ±0.12 / -1.42 ±0.16                                 | dB (max)<br>dB (max) |

|                 | Clock Feedthrough                                                    | Filter Output<br>V <sub>IN</sub> = 0V                               | 5                    |                                                                                        | mV <sub>P−</sub> p   |

# Filter Electrical Characteristics The following specifications apply for $f_{CLK}=250$ kHz. Boldface limits apply for $T_A=T_J=T_{MIN}$ to $T_{MAX}$ : All other limits $T_A=T_J=25^{\circ}C$ .

| Symbol                           | Parameter                                      | Conditions                                         | Typical<br>(Note 10) | Limits<br>(Note 11)                            | Units<br>(Limit)      |

|----------------------------------|------------------------------------------------|----------------------------------------------------|----------------------|------------------------------------------------|-----------------------|

| V + = +2                         | $2.5V, V^- = -2.5V$                            |                                                    |                      |                                                |                       |

| fCLK                             | Clock Frequency Range<br>(Note 17)             |                                                    | 5                    | 1.0                                            | Hz (min)<br>MHz (max) |

| Is                               | Supply Current                                 | CMJ<br>CIN, CIJ, CIWM                              |                      | 2.1 / <b>4.0</b><br>2.1 / <b>3.0</b>           | mA (max)<br>mA (max)  |

| H <sub>O</sub>                   | DC Gain                                        | $R_S \le 2 k\Omega$<br>$f_{CLK} = 250 \text{ kHz}$ |                      | +0.05 / + <b>0.05</b><br>-0.15 / - <b>0.20</b> | dB (max)<br>dB (min)  |

|                                  | f <sub>CLK</sub> = 500 kHz                     | -0.1                                               |                      | dB                                             |                       |

| f <sub>CLK</sub> /f <sub>c</sub> | Clock to Cutoff<br>Frequency Ratio<br>LMF40-50 | f <sub>CLK</sub> = 250 kHz                         |                      | 49.80 ± 0.8%                                   | (max)                 |

|                                  |                                                | f <sub>CLK</sub> = 500 kHz                         | 49.80<br>±0.6%       |                                                |                       |

|                                  | LMF40-100                                      | f <sub>CLK</sub> = 250 kHz                         |                      | 99.00 ±1.0% / <b>99.00</b> ± <b>1.2%</b>       | (max)                 |

| (Note 3)                         |                                                | f <sub>CLK</sub> = 500 kHz                         | 99.00<br>±1.2%       |                                                |                       |

Filter Electrical Characteristics (Continued) The following specifications apply for  $f_{CLK}=250$  kHz. Boldface limits apply for  $T_A=T_J=T_{MIN}$  to  $T_{MAX}$ : All other limits  $T_A=T_J=25^{\circ}C$ .

| Symbol                                | Parameter                                                                  | Conditions                                            | Typical<br>(Note 10) | Limits<br>(Note 11)                                                                    | Units<br>(Limit)     |

|---------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------|----------------------|----------------------------------------------------------------------------------------|----------------------|

| $V^{+} = +2.5V$                       | , <b>V</b> <sup>−</sup> = − <b>2.5V</b> (Continued)                        |                                                       | <del>1 010</del>     |                                                                                        |                      |

| Δf <sub>CLK</sub> /f <sub>c</sub> /ΔT | Clock to Cutoff Frequency Ratio Temperature Coefficient LMF40-50 LMF40-100 |                                                       | 5<br>5               |                                                                                        | ppm/°C<br>ppm/°C     |

| A <sub>MIN</sub>                      | Stopband Attenuation                                                       | At 2 f <sub>c</sub>                                   |                      | -24.0                                                                                  | dB (min)             |

| V <sub>OS</sub>                       | Unadjusted DC<br>Offset Voltage<br>LMF40-50<br>LMF40-100                   |                                                       |                      | ±80 / ±100<br>±80 / ±100                                                               | mV (max)<br>mV (max) |

| V <sub>O</sub>                        | Output Swing                                                               | $R_L = 5 k\Omega$                                     |                      | +1.4 / + <b>1.2</b><br>-2.0 / - <b>1.8</b>                                             | V (min)<br>V (max)   |

| Isc                                   | Output Short Circuit<br>Current (Note 8)                                   | Source<br>Sink                                        | 42<br>0.9            |                                                                                        | mA<br>mA             |

|                                       | Dynamic Range<br>(Note 4)                                                  |                                                       | 81                   |                                                                                        | dB                   |

|                                       | Additional Magnitude Response<br>Test Points (Note 6)<br>LMF40-50          | f <sub>IN</sub> = 6 kHz                               |                      | -7.50 ±0.26 / - <b>7.50</b> ± <b>0.30</b>                                              | dB (max)             |

|                                       | LIVIF40-30                                                                 | $f_{IN} = 4.5 \text{ kHz}$                            |                      | -7.50 ±0.267 -7.50 ±0.30<br>-1.46 ±0.12 / -1.46 ±0.16                                  | dB (max)             |

|                                       | LMF40-100                                                                  | f <sub>IN</sub> = 3 kHz<br>f <sub>IN</sub> = 2.25 kHz |                      | -7.15 ±0.26 / - <b>7.15</b> ± <b>0.30</b><br>-1.42 ±0.12 / - <b>1.42</b> ± <b>0.16</b> | dB (max)<br>dB (max) |

|                                       | Clock Feedthrough                                                          | Filter Output<br>V <sub>IN</sub> = 0V                 | 5                    |                                                                                        | mV <sub>P-P</sub>    |

## **Logic Input-Output Characteristics** The following specifications apply for $V^- = 0V$ unless otherwise specified. **Boldface limits apply for T\_A = T\_J = T\_{MIN} to T\_{MAX}: all other limits T\_A = T\_J = 25^{\circ}C.**

| Symbol           | Parameter                               | Conditions                         | Typical<br>(Note 10) | Limits<br>(Note 11) | Units<br>(Limit) |

|------------------|-----------------------------------------|------------------------------------|----------------------|---------------------|------------------|

| TL CLOCK INP     | UT, CLK R PIN (Note 9)                  |                                    |                      |                     |                  |

|                  | TTL CLK R Pin Input Voltage             | $V^{+} = +5V$<br>$V^{-} = -5V$     |                      |                     |                  |

|                  | Logic "1"                               |                                    |                      | 2.0 / <b>2.1</b>    | V (min)          |

|                  | Logic "0"                               |                                    |                      | 0.8 / <b>0.8</b>    | V (max)          |

|                  | CLK R Input Voltage                     | $V^{+} = +2.5V$<br>$V^{-} = -2.5V$ |                      |                     |                  |

|                  | Logic "1"                               |                                    |                      | 2.0 / <b>2.0</b>    | V (min)          |

|                  | Logic "0"                               |                                    |                      | 0.6 / <b>0.4</b>    | V (max)          |

|                  | Maximum Leakage Current<br>at CLK R Pin |                                    | 2.0                  |                     | μΑ               |

| CHMITT TRIGG     | ER                                      |                                    |                      |                     |                  |

| V <sub>T</sub> + | Positive Going Input                    | V+ = +10V                          |                      | 6.1 / <b>6.0</b>    | V (min)          |

|                  | Threshold Voltage                       |                                    |                      | 8.8 / <b>8.9</b>    | V (max)          |

|                  | CLK IN Pin                              | V+ = +5V                           |                      | 3.0 / <b>2.9</b>    | V (min)          |

|                  |                                         |                                    |                      | 4.3 / <b>4.4</b>    | V (max)          |

**Logic Input-Output Characteristics** (Continued) The following specifications apply for  $V^- = 0V$  unless otherwise specified. **Boldface limits apply for T\_A = T\_J = T\_{MIN} to T\_{MAX}:** all other limits  $T_A = T_J = 25^{\circ}C$ .

| Symbol                                                    | Parameter                                               | Conditions                                             | Typical<br>(Note 10) | Limits<br>(Note 11)                  | Units<br>(Limit)     |

|-----------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------|----------------------|--------------------------------------|----------------------|

| CHMITT TRIGGER                                            | (Continued)                                             |                                                        |                      |                                      | •                    |

| V <sub>T</sub> -                                          | V <sub>T</sub> - Negative Going Input Threshold Voltage | V <sup>+</sup> = +10V                                  |                      | 1.4 / <b>1.3</b><br>3.8 / <b>3.9</b> | V (min)<br>V (max)   |

|                                                           | CLK IN Pin                                              | V+ == +5V                                              |                      | 0.7 / <b>0.6</b><br>1.9 / <b>2.0</b> | V (min)<br>V (max)   |

| V <sub>T</sub> + - V <sub>T</sub> - Hysteresis CLK IN Pin | Hysteresis CLK IN Pin                                   | V+ = +10V                                              |                      | 2.3 / <b>2.1</b><br>7.4 / <b>7.6</b> | V (min)<br>V (max)   |

|                                                           |                                                         | V+ = +5V                                               |                      | 1.1 / <b>0.9</b><br>3.6 / <b>3.8</b> | V (min)<br>V (max)   |

|                                                           | Logical "1" Output<br>Voltage CLK R<br>Pin              | $I_{O} = -10 \mu\text{A}$ $V^{+} = +10V$ $V^{+} = +5V$ |                      | 9.1 / <b>9.0</b><br>4.6 / <b>4.5</b> | V (min)<br>V (min)   |

|                                                           | Logical "0" Output<br>Voltage CLK R<br>Pin              | $I_{O} = -10 \mu A$<br>$V^{+} = +10V$<br>$V^{+} = +5V$ |                      | 0.9 / <b>1.0</b><br>0.4 / <b>0.5</b> | V (max)<br>V (max)   |

|                                                           | Output Source Current<br>CLK R Pin                      | CLK R to V <sup></sup><br>V+ = +10V<br>V+ = +5V        |                      | 4.9 / <b>3.7</b><br>1.6 / <b>1.2</b> | mA (min)<br>mA (min) |

|                                                           | Output Sink Current<br>CLK R Pin                        | CLK R to V+<br>V+ = + 10V<br>V+ = +5V                  |                      | 4.9 / <b>3.7</b><br>1.6 / <b>1.2</b> | mA (min)<br>mA (min) |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating the device beyond its specified operating range.

Note 2: All voltages are specified with respect to ground.

Note 3: The filter's cutoff frequency is defined as the frequency where the magnitude response is 3.01 dB less than the DC gain of the filter.

Note 4: For  $\pm 5V$  supplies the dynamic range is referenced to 2.62  $V_{rms}$  (3.7V peak) where the wideband noise over a 20 kHz bandwidth is typically 100  $\mu V_{rms}$  for the LMF40. For  $\pm 2.5V$  supplies the dynamic range is referenced to 0.849  $V_{rms}$  (1.2V peak) where the wideband noise over a 20 kHz bandwidth is typically 75  $\mu V_{rms}$  for the LMF40.

Note 5: The specifications for the LMF40 have been given for a clock frequency ( $1_{CLK}$ ) of 500 kHz at  $\pm$ 5V and 250 kHz at  $\pm$ 2.5V. Above this clock frequency the cutoff frequency begins to deviate from the specified error band of  $\pm$ 0.8% over the temperature range, but the filter still maintains its magnitude characteristics. See Application Information, Section 1.4.

Note 6: The filter's magnitude response is tested at the cutoff frequency,  $f_c$ ,  $f_S = 2 f_c$ , and at these other two additional frequencies.

Note 7: For simplicity all logic levels have been referenced to V<sup>-</sup> = 0V (except for the TTL input logic levels). The logic levels will scale accordingly for ±5V and ±2.5V supplies.

Note 8: The short circuit source current is measured by forcing the output that is being tested to its maximum positive swing and then shorting that output to the negative supply. The short circuit sink current is measured by forcing the output that is being tested to its maximum negative voltage and then shorting that output to the positive supply. These are worst case conditions.

Note 9: The LMF40 is operated with symmetrical supplies and L. Sh. is tied to ground.

Note 10: Typicals are at  $T_{J}=25^{\circ}\text{C}$  and represent the most likely parametric norm.

Note 11: Guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 12: Human body model; 100 pF discharged through a 1.5  $k\Omega$  resistor.

Note 13: When the input voltage  $(V_{IN})$  at any pin exceeds the power supply voltages  $(V_{IN} < V^- \text{ or } V_{IN} > V^+)$  the absolute value of the current at that pin should be limited to 5 mA or less. The 20 mA package input current limits the number of pins that can exceed the power supply voltages with 5 mA current limit to four.

Note 14: The maximum power dissipation must be de-rated at elevated temperatures and is dictated by  $T_{JMAX}$ ,  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable power dissipation is PD =  $(T_{JMAX} - T_A)/\theta_{JA}$  or the number given in the Absolute Maximum Ratings, whichever is lower. For the LMF40,  $T_{JMAX} = 125^{\circ}$ C, and the typical junction-to-ambient thermal resistance, when board mounted, is 67°C/W for the LMF40CIN, 62°C/W for the LMF40CIJ and LMF40CINJ, and 78°C/W for the LMC40CIWM.

Note 15: In popular usage the term cutoff frequency defines that frequency at which a filter's gain drops 3.01 dB below its DC value. Equations (2) and (3) and design example 2.1, however, use the term cutoff frequency (f<sub>b</sub>) to define that frequency at which a filter's gain drops by a variable amount as determined from the given design specifications.

Note 16: See AN-450 "Surface Mounting Methods and Their Effect on Product Reliability" for other methods of soldering surface mount devices or see the section titled "Surface Mount" in the Linear Data Book.

Note 17: The nominal ratio of the clock frequency to the low-pass cutoff frequency is internally set to 50-to-1 (LMF40-50) or 100-to-1 (LMF40-100).

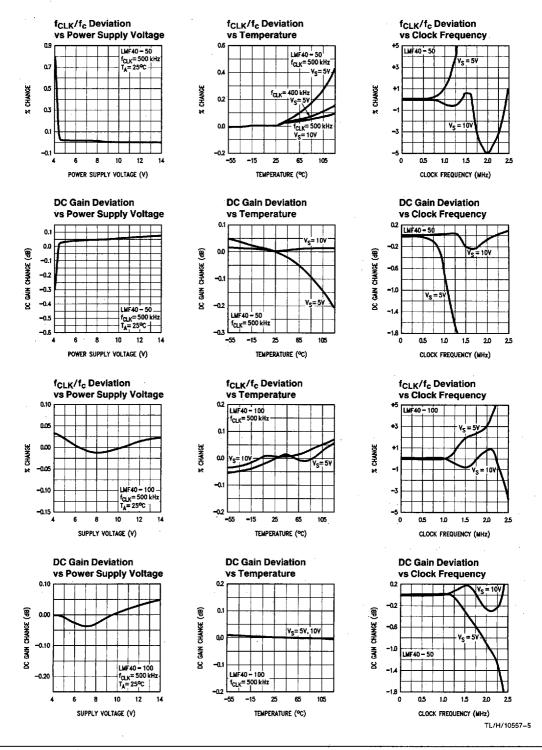

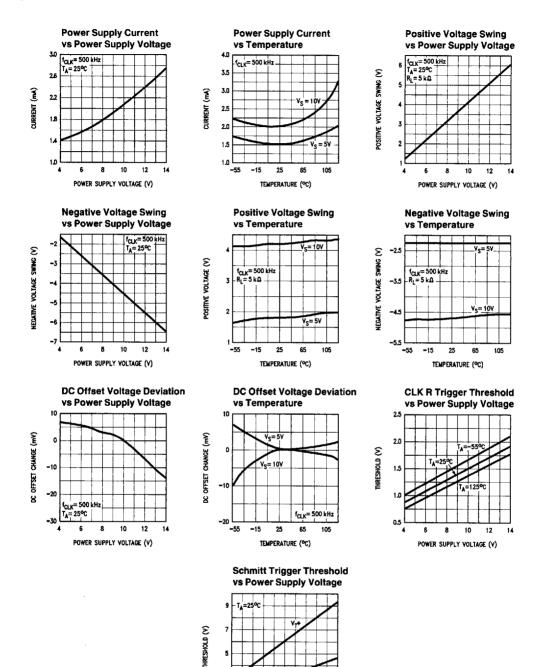

#### **Typical Performance Characteristics**

#### Typical Performance Characteristics (Continued)

TL/H/10557-6

10 12

POWER SUPPLY VOLTAGE (V)

#### **Pin Descriptions**

(Numbers in ( ) are for 14-pin package).

| Pin<br>"              | Pin                   | Function                                                                                                                                                                                                                                                                                                     |

|-----------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| # .                   | Name                  | A CMOS Sobreitt trianne in the                                                                                                                                                                                                                                                                               |

| 1 (1)                 | CLK IN                | A CMOS Schmitt-trigger input<br>to be used with an external<br>CMOS logic level clock. Also<br>used for self clocking Schmitt-<br>trigger oscillator (see Section<br>1.1).                                                                                                                                   |

| 2<br>(3)              | CLK R                 | A TTL logic level clock input when in split supply operation $(\pm 2.0 \text{V to } \pm 7 \text{V})$ with L. Sh tied to system ground. This pin becomes a low impedance output when L. Sh is tied to                                                                                                         |

|                       | \$                    | V <sup>-</sup> . Also used in conjunction with the CLK IN pin for a self clocking Schmitt-trigger oscillator (see Section 1.1). The TTL input signal must not exceed the supply voltages by more than 0.2V.                                                                                                  |

| 3<br>(5)              | L. Sh                 | Level shift pin; selects the<br>logic threshold levels for the<br>clock. When tied to V <sup>-</sup> it<br>enables an internal TRI-                                                                                                                                                                          |

|                       |                       | STATE® buffer stage between the Schmitt trigger and the internal clock level shift stage thus enabling the CLK IN Schmitt-trigger input and making the CLK R pin a low impedance output. When the                                                                                                            |

|                       |                       | voltage level at this input<br>exceeds 25% (V+ - V-) +<br>V- the internal TRI-STATE<br>buffer is disabled allowing the<br>CLK R pin to become the                                                                                                                                                            |

|                       |                       | clock input for the internal clock level-shift stage. The CLK R threshold level is now 2V above the voltage on the L. Sh pin. The CLK R pin will be compatible with TTL logic levels when the LMF40 is operated on split supplies with the L. Sh pin connected to system ground.                             |

| 5<br>(8)<br>6<br>(10) | FILTER<br>OUT<br>AGND | The output of the low-pass filter.  The analog ground pin. This pin sets the DC bias level for the filter section and must be tied to the system ground for split supply operation or to mid-supply for single supply operation (see Section 1.2). When tied to mid-supply this pin should be well bypassed. |

| Pin<br>*#       | Pin<br>Name  | Function                                                                                                                                                                                                                                                  |

|-----------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7, 4<br>(7, 12) | V+,V-        | The positive and negative supply pins. The total power supply range is 4V, to 14V. Decoupling these pins with 0.1 µF capacitors is highly recommended.                                                                                                    |

| 8 (14)          | FILTER<br>IN | The input to the low-pass filter. To minimize gain errors the source impedance that drives this input should be less than 2k (see Section 3). For single supply operation the input signal must be biased to midsupply or AC coupled through a capacitor. |

#### 1.0 LMF40 Application Information

The LMF40 is a non-inverting unity gain low-pass fourth-order Butterworth switched-capacitor filter. The switched-capacitor topology makes the cutoff frequency (where the gain drops 3.01 dB below the DC gain) a direct ratio (100:1 or 50:1) of the clock frequency supplied to the filter. Internal integrator time constants set the filter's cutoff frequency. The resistive element of these integrators is actually a capacitor which is "switched" at the clock frequency (for a detailed discussion see Input Impedance section). Varying the clock frequency changes the value of this resistive element and thus the time constant of the integrators. The clock-to-cutoff-frequency ratio (f\_CLK/f\_c) is set by the ratio of the input and feedback capacitors in the integrators. The higher the clock-to-cutoff-frequency ratio the closer this approximation is to the theoretical Butterworth response.

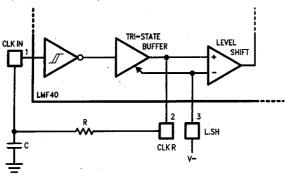

#### 1.1 CLOCK INPUTS

The LMF40 has a Schmitt-trigger inverting buffer which can be used to construct a simple R/C oscillator. Pin 3 is connected to  $V^-$ , making Pin 2 a low impedance output. The oscillator's frequency is nominally

$$f_{CLK} = \frac{1}{RC \ln \left[ \left( \frac{V_{CC} - V_{t-}}{V_{CC} - V_{t+}} \right) \left( \frac{V_{t+}}{V_{t-}} \right) \right]}$$

(1)

which is typically

$$f_{CLK} \simeq \frac{1}{1.37 \text{ RC}}$$

(1a)

for  $V_{CC} = 10V$ .

Note that  $f_{CLK}$  is dependent on the buffer's threshold levels as well as the resistor/capacitor tolerance (see *Figure 1*). Schmitt-trigger threshold voltage levels can change significantly causing the R/C oscillator's frequency to vary greatly from part to part.

Where accurate cutoff frequency is required, an external clock can be used to drive the CLK R input of the LMF40. This input is TTL logic level compatible and also presents a very light load to the external clock source ( $\sim 2~\mu A)$ . With split supplies and the level shift (L. Sh) tied to system ground, the logic level is about 2V. (See the Pin Description for L. Sh).

#### 1.0 LMF40 Application Information (Continued)

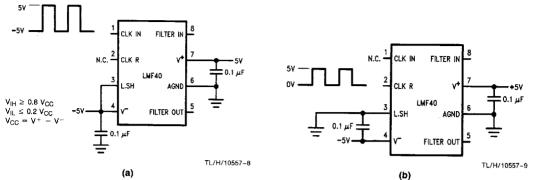

#### 1.2 POWER SUPPLY

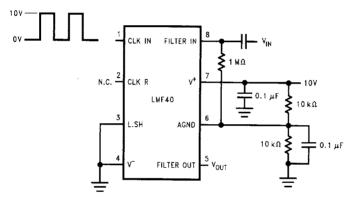

The LMF40 can be powered from a single supply or split supplies. The split supply mode shown in Figure 2 is the most flexible and easiest to implement. Supply voltages of ±5V to ±7V enable the use of TTL or CMOS clock logic levels. Figure 3 shows AGND resistor-biased to V+/2 for single supply operation. In this mode only CMOS clock logic levels can be used, and input signals should be capacitorcoupled or biased near mid-supply.

#### 1.3 INPUT IMPEDANCE

The LMF40 low-pass filter input (FILTER IN) is not a high impedance buffer input. This input is a switched-capacitor resistor equivalent, and its effective impedance is inversely proportional to the clock frequency. The equivalent circuit of the filter's input can be seen in Figure 4. The input capacitor charges to VIN during the first half of the clock period; during the second half the charge is transferred to the feedback capacitor. The total transfer of charge in one clock cycle is therefore Q = CIN VIN, and since current is defined as the flow of charge per unit time, the average input current becomes

$$I_{IN} = Q/T$$

(where T equals one clock period) or

$$i_{\text{IN AVE}} = \frac{C_{\text{IN}} \, V_{\text{IN}}}{T} = \, C_{\text{IN}} \, V_{\text{IN}} \, f_{\text{CLK}}$$

The equivalent input resistor (RIN) then can be expressed

$$R_{IN} = \frac{V_{IN}}{I_{IN}} = \frac{1}{C_{IN} \, f_{CLK}}$$

The input capacitor is 2 pF for the LMF40-50 and 1 pF for the LMF40-100, so for the LMF40-100

$$R_{IN} = \frac{1 \times 10^{12}}{f_{CLK}} = \frac{1 \times 10^{12}}{f_{c} \times 100} = \frac{1 \times 10^{10}}{f_{c}}$$

and

$$R_{IN} = \frac{5 \times 10^{11}}{f_{CLK}} = \frac{5 \times 10^{11}}{f_{c} \times 50} = \frac{1 \times 10^{10}}{f_{c}}$$

for the LMF40-50. The above equation shows that for a given cutoff frequency (fc), the input resistance of the LMF40-50 is the same as that of the LMF40-100. The higher the clock-to-cutoff-frequency ratio, the greater equivalent input resistance for a given clock frequency.

This input resistance will form a voltage divider with the source impedance (R<sub>Source</sub>). Since R<sub>IN</sub> is inversely proportional to the cutoff frequency, operation at higher cutoff frequencies will be more likely to attenuate the input signal which would appear as an overall decrease in gain to the output of the filter. Since the filter's ideal gain is unity, the overall gain is given by:

$$A_V = \frac{R_{IN}}{R_{IN} + R_{Source}}$$

If the LMF40-50 or the LMF40-100 were set up for a cutoff frequency of 10 kHz the input impedance would be:

$$R_{\text{IN}} = \frac{1 \times 10^{10}}{10 \text{ kHz}} = 1 \text{ M}\Omega$$

As an example, with a source impedance of 10 k $\Omega$  the overall gain would be:

$$A_V = \frac{1 \text{ M}\Omega}{10 \text{ k}\Omega + 1 \text{ M}\Omega} = 0.99009 \text{ or } -0.086 \text{ dB}$$

Since the maximum overall gain error for the LMF40 is +0.05, -0.15 dB @ 25°C with  $R_S \le 2 k\Omega$  the actual gain error for this case would be -0.04 dB to -0.24 dB.

#### 1.4 CUTOFF FREQUENCY RANGE

The filter's cutoff frequency (fc) has a lower limit due to leakage currents through the internal switches draining the charge stored on the capacitors. At lower clock frequencies these leakage currents can cause millivolts of error. For example:

$$f_{CLK} = 100 \text{ Hz}, I_{Leakage} = 1 \text{ pA}, C = 1 \text{ pF}$$

$$V = \frac{1 \text{ pA}}{1 \text{ pF} (100 \text{ Hz})} = 10 \text{ mV}$$

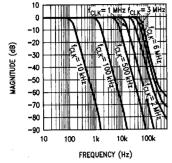

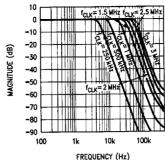

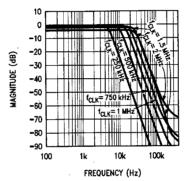

The propagation delay in the logic and the settling time required to acquire a new voltage level on the capacitors limit the filter's accuracy at high clock frequencies. The amplitude characteristic on ±5V supplies will typically stay flat until f<sub>CLK</sub> exceeds 1.5 MHz and then peak at about 0.1 dB at the corner frequency with a 2 MHz clock. As supply voltage drops to  $\pm 2.5$ V, a shift in the  $f_{CLK}/f_c$  ratio occurs which will become noticeable when the clock frequency exceeds 500 kHz. The response of the LMF40 is still a good approximation of the ideal Butterworth low-pass characteristic shown in Figure 5.

#### 2.0 Designing with the LMF40

Given any low-pass filter specification, two equations will come in handy in trying to determine whether the LMF40 will do the job. The first equation determines the order of the low-pass filter required to meet a given response specification:

$$n = \frac{\log \left[ (10^{0.1} \text{Amin} - 1) / (10^{0.1} \text{Amax} - 1) \right]}{2 \log (f_b / f_b)}$$

(2)

where n is the order of the filter, Amin is the minimum stopband attenuation (in dB) desired at frequency fs, and Amax is the passband ripple or attenuation (in dB) at cutoff frequency fb (Note 15). If the result of this equation is greater than 4, more than one LMF40 will be required.

The attenuation at any frequency can be found by the following equation:

Attn (f) =

$$10 \log [1 + (10^{0.14} \text{max} - 1)(f/f_b)^{2n}] dB$$

(3) where n = 4 for the LMF40.

#### 2.1 A LOW-PASS DESIGN EXAMPLE

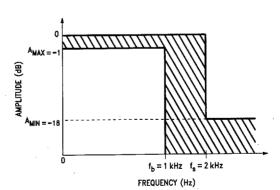

Suppose the amplitude response specification in Figure 6 is given. Can the LMF40 be used? The order of the Butterworth approximation will have to be determined using (1):

$$\begin{split} A_{min} = 18 \text{ dB, } A_{max} = 1.0 \text{ dB, } f_s = 2 \text{ kHz, and } f_b = 1 \text{ kHz} \\ n = \frac{log[(10^{1.8} - 1)/(10^{0.1} - 1)]}{2 \log(2)} = 3.95 \end{split}$$

Since n can only take on integer values, n = 4. Therefore the LMF40 can be used. In general, if n is 4 or less a single LMF40 can be utilized.

Likewise, the attenuation at  $f_s$  can be found using (3) with the above values and n = 4:

Attn (2 kHz) =

$$10 \log[1 + 10^{0.1} - 1) (2 \text{ kHz/1 kHz})^8]$$

=  $18.28 \text{ dB}$

This result also meets the design specification given in Figure 6 again verifying that a single LMF40 section will be adequate.

Since the LMF40's cutoff frequency ( $f_c$ ), which corresponds to a gain attenuation of -3.01 dB, was not specified in this example, it needs to be calculated. Solving equation (3) where  $f = f_c$  as follows:

$$f_{C} = f_{D} \left[ \frac{10^{0.1(3.01 \text{ dB})} - 1}{(10^{0.1\text{A}} \text{max} - 1)} \right] 1/(2n)$$

$$= 1 \text{ kHz} \left[ \frac{10^{0.301} - 1}{10^{0.1} - 1} \right] 1/8$$

$$= 1.184 \text{ kHz}$$

where  $f_C = f_{CLK}$  /50 or  $f_{CLK}$ /100. To implement this example for the LMF40-50 the clock frequency will have to be set to  $f_{CLK} = 50(1.184 \text{ kHz}) = 59.2 \text{ kHz}$ , or for the LMF40-100,  $f_{CLK} = 100 (1.184 \text{ kHz}) = 118.4 \text{ kHz}$ .

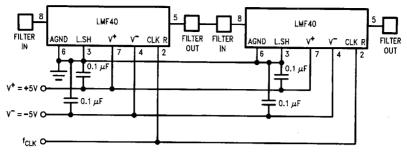

#### 2.2 CASCADING LMF40s

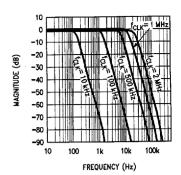

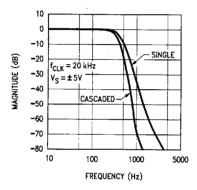

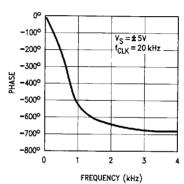

When a steeper stopband attenuation rate is required, two LMF40s can be cascaded (Figure 7) yielding an 8th order slope of 48 dB per octave. Because the LMF40 is a Butterworth filter and therefore has no ripple in its passband, when LMF40s are cascaded the resulting filter also has no ripple in its passband. Likewise the DC and passband gains will remain at 1V/V. The resulting response is shown in Figure 8a

In determining whether the cascaded LMF40s will yield a filter that will meet a particular amplitude response specification, as above, equations (4) and (5) can be used, shown below

$$n = \frac{log[(10,^{0.05Amin} - 1)/(10^{0.05Amax} - 1)]}{2 log(f_b/f_b)}$$

(4)

Attn (f) =

$$10 \log \left[1 + (10^{0.05\text{A}_{max}} - 1) (f/f_b)^2\right] dB$$

(5) where n = 4 (the order of each filter).

Equation (4) will determine whether the order of the filter is adequate (n  $\leq$  4) while equation (5) can determine the actual stopband attenuation and cutoff frequency (f<sub>c</sub>) necessary to obtain the desired frequency response. The design procedure would be identical to the one shown in Section 2.0.

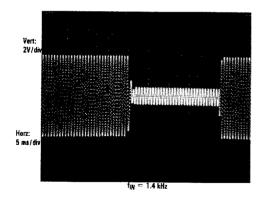

## 2.3 CHANGING CLOCK FREQUENCY INSTANTANEOUSLY

The LMF40 responds well to an instantaneous change in clock frequency. If the control signal in Figure 9 is low the LMF40-50 has a 100 kHz clock making  $f_{\rm C}=2$  kHz; when this signal goes high the clock frequency changes to 50 kHz yielding  $f_{\rm C}=1$  kHz. As Figure 9 illustrates, the output signal changes quickly and smoothly in response to a sudden change in clock frequency.

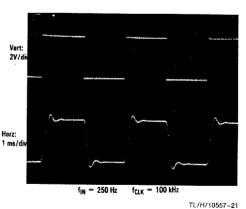

The step response of the LMF40 in *Figure 10* is dependent on f<sub>c</sub>. The LMF40 responds as a classical fourth-order Butterworth low-pass filter.

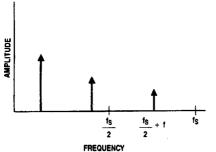

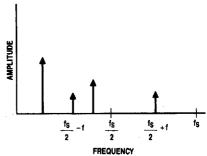

#### 2.4 ALIASING CONSIDERATIONS

Aliasing effects have to be considered when input signal frequencies exceed half the sampling rate. For the LMF40 this equals half the clock frequency ( $f_{CLK}$ ). When the input signal contains a component at a frequency higher than half the clock frequency  $f_{CLK}/2$ , as in Figure 11a, that component will be "reflected" about  $f_{CLK}/2$  into the frequency range below  $f_{CLK}/2$ , as in Figure 11b. If this component is within the passband of the filter and of large enough amplitude it can cause problems. Therefore, if frequency components in the input signal exceed  $f_{CLK}/2$  they must be attenuated before being applied to the LMF40 input. The necessary amount of attenuation will vary depending on system requirements. In critical applications the signal components above  $f_{CLK}/2$  will have to be attenuated at least to the filter's residual noise level.

$$\begin{split} f &= \frac{1}{\text{RC In} \left[ \left( \frac{V_{\text{CC}} - V_{t^-}}{V_{\text{CC}} - V_{t^+}} \right) \left( \frac{V_{t^+}}{V_{t^-}} \right) \right]} \\ &\quad f &\simeq \frac{1}{1.37 \text{ RC}} \\ &\quad (V_{\text{CC}} = 10V) \end{split}$$

TL/H/10557-7

FIGURE 1. Schmitt Trigger R/C Oscillator

FIGURE 2. Split Supply Operation with CMOS Level Clock (a), and TTL Level Clock (b)

FIGURE 3. Single Supply Operation. AGND Resistor Biased to V+/2

ILTER NPUT  $R_{IN} = \frac{1}{C_{IN}} f_{CLK}$ FILTER  $R_{IN} = \frac{1}{C_{IN}} f_{CLK}$

a) Equivalent Circuit for LMF40 Filter Input

b) Actual Circuit for LMF40 Filter Input

FIGURE 4. LMF40 Filter Input

TL/H/10557-12

AGND

TL/H/10557~10

TL/H/10557-13

FIGURE 5a. LMF40-100 Amplitude Response with ±5V Supplies

TL/H/10557-14

FIGURE 5b. LMF40-50 Amplitude Response with ±5V Supplies

TL/H/10557-15 FIGURE 5c. LMF40-100 Amplitude Response with  $\pm\,2.5$ V Supplies

FIGURE 5d. LMF40-50 Amplitude Response with ±2.5V Supplies

FIGURE 6. Design Example Magnitude Response Specification. The response of the filter design must fall within the shaded area of the specification. TL/H/10557-17

TL/H/10557-16

FIGURE 7. Cascading Two LMF40s

FIGURE 8a. One LMF40-50 vs Two LMF40-50s Cascaded

of Two Cascaded LMF40-50s

TL/H/10557-19

FIGURE 8b. Phase Response

TL/H/10557-20 FIGURE 9. LMF40-50 Abrupt Clock Frequency Change

FIGURE 10. LMF40-50 Input Step Response

(a) Input Signal Spectrum

TL/H/10557-22

TL/H/10557-23

(b)Output Signal Spectrum. Note that the input signal at  $f_8/2 + f$  causes an output signal to appear at  $f_8/2 - f$ .

FIGURE 11. The phenomenon of aliasing in sampled-data systems. An input signal whose frequency is greater than one-half the sampling frequency will cause an output to appear at a frequency lower than one-half the sampling frequency. In the LMF40,  $f_8 = f_{CLK}$ .