## January 2015

# FSA9285A — MCPC-Compliant, USB-Port, Multimedia Switch with Auto-Detection, 12 V $V_{BUS}$

## Features

| Switch Type          | Audio, FS/HS-USB, Charging         |  |  |  |  |  |

|----------------------|------------------------------------|--|--|--|--|--|

| Switch Mechanism     | Programmable Switching with        |  |  |  |  |  |

|                      | Available Interrupt                |  |  |  |  |  |

|                      | Headsets with MIC and Send/End     |  |  |  |  |  |

|                      | USB Data Cable                     |  |  |  |  |  |

| Accessory Detection  | USB Chargers (Car, CDP, DCP)       |  |  |  |  |  |

| Accessory Detection  | USB On-The-Go (OTG)                |  |  |  |  |  |

|                      | MCPC Specification Compliant       |  |  |  |  |  |

|                      | Programmable Modes                 |  |  |  |  |  |

| USB                  | FS and HS 2.0 Complian             |  |  |  |  |  |

|                      | Battery Charging 1.2 Compliant     |  |  |  |  |  |

| USB Charging         | Integrated FET, Charger Detect,    |  |  |  |  |  |

|                      | OCP (1.45 A), OVP (6.5 V - 14.0 V) |  |  |  |  |  |

|                      | Left, Right, MIC (Negative Swing)  |  |  |  |  |  |

| Audio                | Built-in Termination Resistors for |  |  |  |  |  |

|                      | Audio Pop Reduction                |  |  |  |  |  |

| V <sub>BAT</sub>     | 2.7 to 4.4 V                       |  |  |  |  |  |

| Programmability      | l <sup>2</sup> C                   |  |  |  |  |  |

| ESD                  | 15 kV IEC 61000-4-2 Air Gap        |  |  |  |  |  |

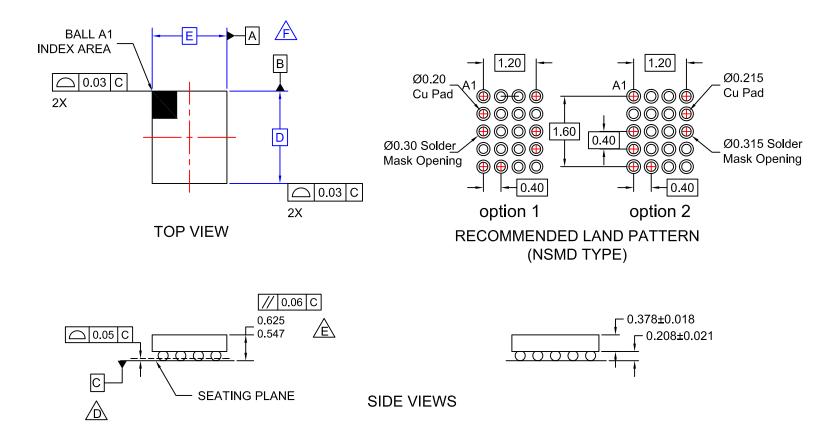

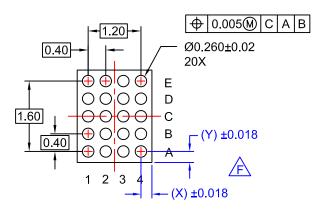

| Deekege              | 20-Lead, WLCSP (2.010 x 1.672 x    |  |  |  |  |  |

| Package              | 0.625 mm, 0.4 mm Pitch)            |  |  |  |  |  |

| Ordering Information | FSA9285AUCX                        |  |  |  |  |  |

|                      |                                    |  |  |  |  |  |

## Description

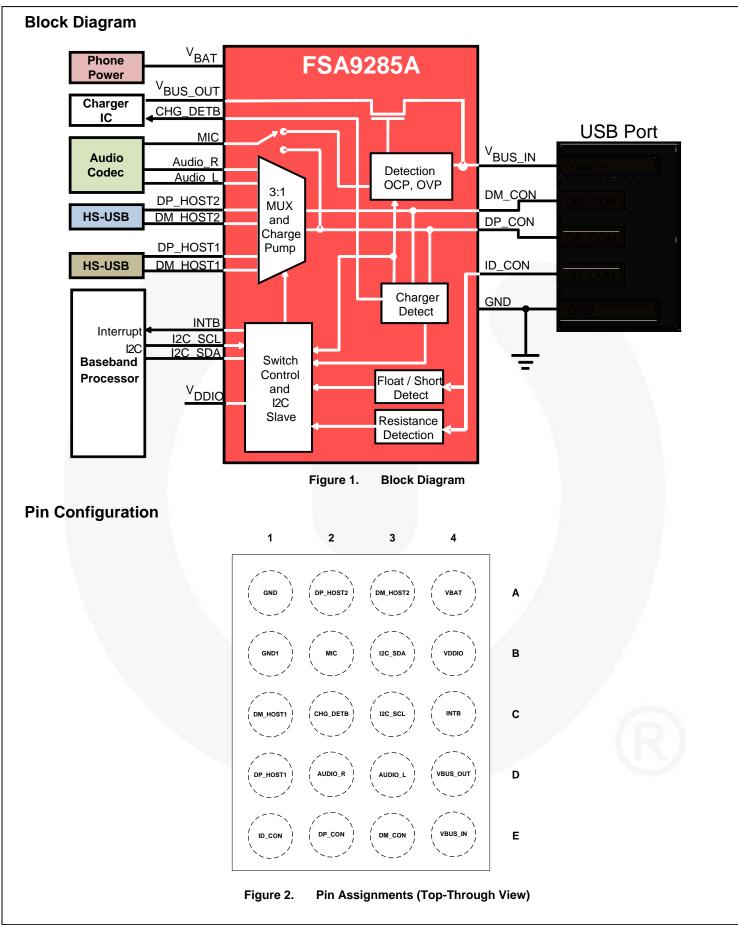

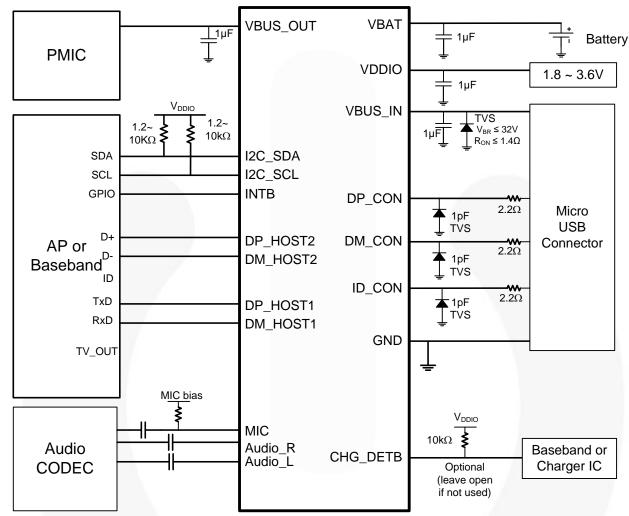

The FSA9285A is a high-performance multimedia switch featuring automatic switching and accessory detection for a USB port. The FSA9285A allows sharing of a common USB port to pass audio and USB data while simultaneously charging.

In addition, the FSA9285A integrates detection of accessories such as headphones, headsets Mobile Computing Promotion Consortium (MCPC) with MIC and Send/End, car chargers, USB chargers, USB On-The-Go (OTG), and Accessory Charging Adapters (ACA) to use a common USB connector. The FSA9285A can be programmed for manual or automatic switching of USB data paths based on the accessory detected. With an integrated 14 V over-voltage and 1.45 A over-current protected FET, the FSA9285A integrates common USB protection functions for V<sub>BUS</sub>.

## Applications

Mobile Phones, Portable Media Players

| <b>Pin Descriptions</b> | 5 |

|-------------------------|---|

|-------------------------|---|

| Name                       | Pin #  | Туре                 | Default<br>State | Description                                                                                                                                                                                             |

|----------------------------|--------|----------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB Interface              |        |                      |                  | ·                                                                                                                                                                                                       |

| DP_HOST1                   | D1     | Signal Path          | Open             | D+ signal switch path, dedicated USB port to be connected to the resident USB transceiver on the phone                                                                                                  |

| DM_HOST1                   | C1     | Signal Path          | Open             | D- signal switch path, dedicated USB port to be connected to the resident USB transceiver on the phone                                                                                                  |

| DP_HOST2                   | A2     | Signal Path          | Open             | D+ signal switch path, dedicated USB port to be connected to the resident USB transceiver on the phone                                                                                                  |

| DM_HOST2                   | A3     | Signal Path          | Open             | D- signal switch path, dedicated USB port to be connected to the resident USB transceiver on the phone                                                                                                  |

| V <sub>BUS_IN</sub>        | E4     | Power Path           | N/A              | Input voltage supply pin to be connected to the $V_{\mbox{\scriptsize BUS}}$ pin of the USB connector                                                                                                   |

| V <sub>BUS_OUT</sub>       | D4     | Power Path           | N/A              | Output voltage supply pin to be connected to the source voltage pin on the charger IC                                                                                                                   |

| CHG_DETB                   | C2     | Open-Drain<br>Output | Hi-Z             | Open-drain active LOW output, used to signal the charger IC that a charger has been attached                                                                                                            |

| Audio Interfac             | е      |                      |                  |                                                                                                                                                                                                         |

| Audio_R                    | D2     | Signal Path          | Open             | Right audio channel switch path from mobile phone audio CODEC                                                                                                                                           |

| Audio_L                    | D3     | Signal Path          | Open             | Left audio channel switch path from mobile phone audio CODEC                                                                                                                                            |

| MIC                        | B2     | Signal Path          | Open             | Connected to the mobile phone audio CODEC MIC input pin to complete the MIC switch path                                                                                                                 |

| Connector Inte             | erface |                      |                  |                                                                                                                                                                                                         |

| ID_CON                     | E1     | Signal Path          | Open             | Connected to the USB connector ID pin and used for detecting accessories or button presses                                                                                                              |

| DP_CON                     | E2     | Signal Path          | Open             | Connected to the USB connector D+ pin; depending on the signaling mode, can be switched to DP_HOST1, DP_HOST2, or Audio_R pins                                                                          |

| DM_CON                     | E3     | Signal Path          | Open             | Connected to the USB connector D- pin; depending on the signaling mode, can switched to DM_HOST1, DM_HOST2, or Audio_L pins                                                                             |

| Power Interfac             | e      |                      |                  |                                                                                                                                                                                                         |

| V <sub>BAT</sub>           | A4     | Power Path           | N/A              | Input voltage supply pin to be connected to the mobile phone battery output or to an internal regulator on the phone                                                                                    |

| V <sub>DDIO</sub>          | B4     | Power Path           | N/A              | Baseband processor interface I/O supply pin                                                                                                                                                             |

| GND1                       | B1     | Ground               | N/A              | Ground                                                                                                                                                                                                  |

| GND                        | A1     | Ground               | N/A              | Ground                                                                                                                                                                                                  |

| I <sup>2</sup> C Interface |        |                      |                  |                                                                                                                                                                                                         |

| I2C_SCL                    | C3     | Input                | Hi-Z             | I <sup>2</sup> C serial clock signal to be connected to the phone-based I <sup>2</sup> C master                                                                                                         |

| I2C_SDA                    | B3     | Open-Drain I/O       | Hi-Z             | I <sup>2</sup> C serial data signal to be connected to the phone-based I <sup>2</sup> C master                                                                                                          |

| INTB                       | C4     | CMOS Output          | HIGH             | Interrupt active LOW output used to prompt the phone baseband processor to read the $I^2C$ register bits, indicates a change in ID_CON or $V_{\text{BUS}\_IN}$ pin status or accessories' attach status |

## 1. Functional Description

The FSA9285A is a USB port accessory-detection switch with integrated 14 V over-voltage and 1.45 A over-current protected FET. Fully controlled using I<sup>2</sup>C protocols, the FSA9285A enables all of the following to use a common connector (micro / mini USB 2.0 port): high-speed USB 2.0 standard downstream data port, stereo and mono audio headphones / headsets with or without a microphone, wired remote controller with optional send / end button, USB Charging Downstream Port (CDP) battery charger, USB Dedicated Charging Port (DCP) charger, and ANSI/CEA-936-A USB Car Kit charger.

The FSA9285A enables factory-mode testing by defaulting to manual mode (EN MAN SW = 1) and defaulting the MANUAL SW register to USB switches DP\_HOST1 / DM\_HOST1 closed and the V<sub>BUS</sub> FET closed. In manual configuration, USB switches DP\_HOST1 / DM\_HOST1 only close when an accessory is attached that has an ID\_CON resistance (ID\_CON not floating) and / or valid V<sub>BUS</sub> voltage is present. The V<sub>BUS</sub> FET only closes when V<sub>BUS</sub> is valid. All switches remain open to protect the system when there is no accessory attached. This default switch condition can be overridden with I<sup>2</sup>C commands.

Detection of USB accessories utilizing a USB micro-B or micro-A/B connector is made possible by the presence of a standard resistor between the ID pin and ground of the accessory. Advanced modes manage wired remote-control sensing for audio accessories. The FSA9285A is designed to allow audio signals to swing below ground on the USB 2.0 port data lines. Internal power for the FSA9285A is automatically derived from either the battery voltage (V<sub>BAT</sub>) or the USB supply (V<sub>BUS IN</sub>) for simplicity and long battery life.

# 2. I<sup>2</sup>C and Digital Core

The FSA9285A includes a full I<sup>2</sup>C slave controller. The I<sup>2</sup>C slave fully complies with version 2.1 of the I<sup>2</sup>C specifications. This block is designed for fast-mode, 400 kHz signals. The slave addresses are shown in Table 1. This block also includes the chip master controller. The chip controller monitors commands sent to the FSA9285A via I<sup>2</sup>C from the baseband processor and takes action. The digital core takes inputs from the various functional blocks and the I<sup>2</sup>C commands received from the mobile phone baseband processor and relays relevant status updates to the phone.

#### ·2~

| Name          | Size (Bits)                                                         | Bit 7                | Bit 6                              | Bit 5                                       | Bit 4                            | Bit 3                                      | Bit 2            | Bit 1                         | Bit 0             |

|---------------|---------------------------------------------------------------------|----------------------|------------------------------------|---------------------------------------------|----------------------------------|--------------------------------------------|------------------|-------------------------------|-------------------|

| Slave Address | 8                                                                   | 0                    | 1                                  | 0                                           | 0                                | 1                                          | 0                | 1                             | Read / Wri        |

|               | rite and read seq<br>bits<br>dress WR A Regi<br>Single byte read is | 8bits<br>ster Addres | 8bit<br>s K <mark>A</mark> Write D | S<br>Data <mark>A</mark> Writ<br>P immediat | te Data K+1 🖌                    | <mark>A Write Data</mark><br>first data by |                  | ite Data K+N                  | - <u>1 A</u> P    |

|               |                                                                     | ecified              | A S Slave A<br>Single- or r        | multi byte rea<br>nitiated by m             | ad executed fro<br>aster with NA | om current reg<br>immediately fo           | ollowing first d | (single-byte re<br>lata byte) | ad is             |

|               |                                                                     |                      | Figure                             |                                             | Read Seque                       |                                            |                  |                               |                   |

|               | rom Master to Slave<br>rom Slave to Master                          |                      | Start Condition<br>Acknowledge (   |                                             | NA NOT Ac<br>WR Write=0          | knowledge (S<br>)                          | iDA High)        | RD Read<br>P Stop             | d =1<br>Condition |

## 3. Power-Up Initialization and Reset

FSA9285A operates correctly without special power sequencing. When power is first applied, the device undergoes a hardware reset and all the registers are initialized to the default values shown in Table 6. All of the combinations of valid  $V_{BUS\_IN}$  and  $V_{BAT}$  are shown in Table 2.

As shown in Table 2,  $V_{BAT}$  is used as the primary power supply.  $V_{DDIO}$  is the dedicated baseband IO voltage and is only used for  $I^2C$  interface and interrupt processing within the FSA9285A.

When  $V_{BAT}$  is not valid, but  $V_{BUS_IN}$  is; the FSA9285A powers off  $V_{BUS_IN}$ . In this condition, the FSA9285A operates in its default state and is able to detect USB accessories and all chargers. The FSA9285A always turns on the  $V_{BUS}$  FET upon any attach state with  $V_{BUS_Valid}$  (unless Manual Mode is enabled with the  $V_{BUS}$  FET switch state configured open). This allows charging of a dead battery when the rest of the system is not powered to configure the FSA9285A.

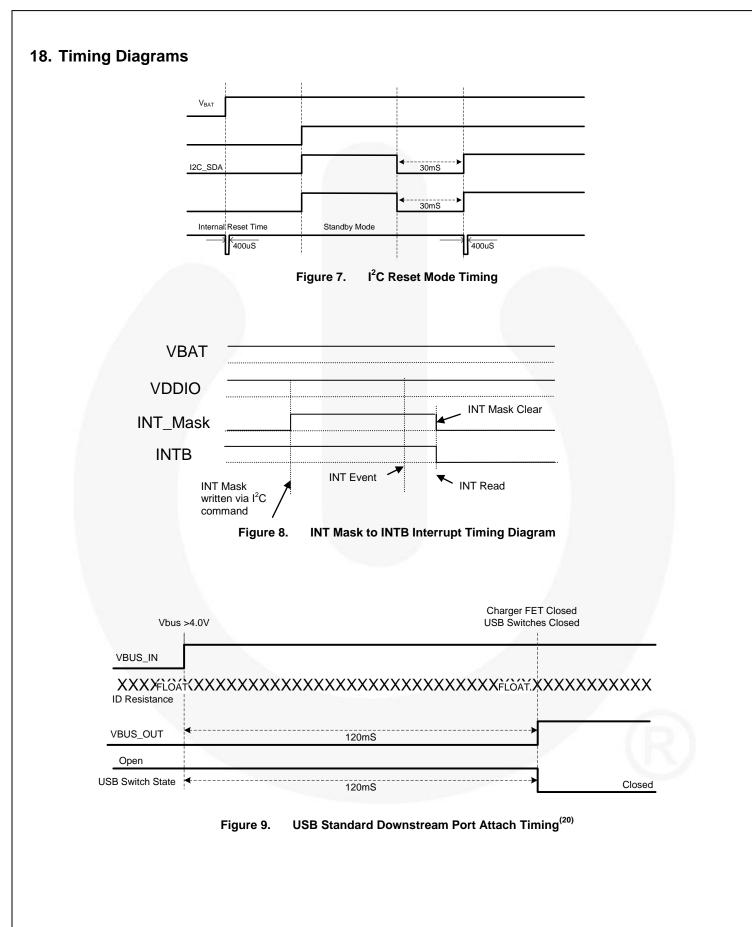

When the device is reset, all I<sup>2</sup>C registers are initialized to the default values shown in Table 6 (see Section 4 - Configuration). After reset or power up, the FSA9285A enters Standby Mode and is ready to detect accessories sensed on its V<sub>BUS\_IN</sub> or ID\_CON pins.

The device has three hardware reset mechanisms:

- Power-on reset caused by the initial rising edge of V<sub>BUS</sub> (if V<sub>BAT</sub> < 1.0 V) or rising edge of V<sub>BAT</sub> (If not V<sub>BUS\_VALID</sub>)

- The falling edge of V<sub>DDIO</sub>

- I<sup>2</sup>C reset: holding I2C\_SDA and I2C\_SCL LOW for 30 ms

The device has one software reset mechanism:

Writing the ResetB bit (bit 6) in the Control register (02h)

| Valid                        |                        | Valid              |                                    |                         | Enabled Functionality                                      |           |  |  |  |

|------------------------------|------------------------|--------------------|------------------------------------|-------------------------|------------------------------------------------------------|-----------|--|--|--|

| Valid<br>V <sub>BUS_IN</sub> | Valid V <sub>BAT</sub> |                    | Power State                        | Charging<br>through FET | Processor Communication<br>(I <sup>2</sup> C & Interrupts) | Detection |  |  |  |

| NO                           | NO                     | NO                 | Power Down                         | NO                      | NO                                                         | NO        |  |  |  |

| NO                           | NO                     | YES <sup>(2)</sup> |                                    | ILLEGAL STATE           |                                                            |           |  |  |  |

| NO                           | YES                    | NO                 | Powered Off $V_{\text{BAT}}$       | NO                      | NO                                                         | YES       |  |  |  |

| NO                           | YES                    | YES                | Powered Off $V_{BAT}$              | NO                      | YES                                                        | YES       |  |  |  |

| YES                          | NO                     | NO                 | Powered Off<br>V <sub>BUS_IN</sub> | Yes                     | NO                                                         | YES       |  |  |  |

| YES                          | YES                    | NO                 | Powered Off $V_{BAT}$              | YES                     | NO                                                         | YES       |  |  |  |

| YES                          | NO                     | YES <sup>(2)</sup> | Powered Off<br>V <sub>BUS_IN</sub> | YES                     | YES                                                        | YES       |  |  |  |

| YES                          | YES                    | YES                | Powered Off $V_{\text{BAT}}$       | YES                     | YES                                                        | YES       |  |  |  |

### Table 2. Power States Summary

#### Notes:

1.  $V_{DDIO}$  is expected to be the same supply used by the baseband I/Os.

2. This is not a typical state. Both V<sub>BAT</sub> and V<sub>DDIO</sub> are typically provided from the same regulator.

## 4. Configuration

The FSA9285A must be configured for operation upon reset. There are several options to note about reset configuration:

- 1. The Interrupt Mask bit is set and must be cleared for the FSA9285A to interrupt the host processor.

- 2. Upon hardware reset, the USB Path DP\_HOST1 / DM\_HOST1 switches are configured to close when an accessory is attached (with an ID\_CON resistance or valid  $V_{BUS}$  voltage) to support production programming. These switches may be opened using  $I^2C$  commands.

- If MIC Mode is going to be used, it is recommended that MIC\_OVP\_EN bit be set to 1 at reset.

- 4. To enable manual configuration of the USB switches, the EN\_MAN\_SW bit must be set to 1. The switch settings then override any automatic settings (this assumes that the USB discovery state machine has completed its operations and a device is attached). For the weak (or dead) battery case to work reliably, V<sub>DDIO</sub> must be removed (to reset the FSA9285A state) whenever the battery is too low for reliable I<sup>2</sup>C communication.

- Performing a software reset sets all I<sup>2</sup>C Register Map (Table 6) registers to default, with the exception of the Control register, Manual SW register, and the Manual CHG\_CTRL register. These registers are only reset to default on a hardware reset.

## 5. Interrupt Operation

The baseband processor recognizes interrupt signals by observing the INTB signal, which is active LOW. Interrupts are masked upon reset via the INT Mask register bit (bit 0 of Control register, address 02h in Table 6 of the I<sup>2</sup>C register map) and INTB pin defaults HIGH. After the INT Mask bit is cleared by the baseband processor, the INTB pin is generally driven HIGH (INTB is not an open-drain output) in preparation for a future interrupt. The INTB remains HIGH until the INTB mask is cleared. If the Interrupt Mask bit in the I<sup>2</sup>C Control register is written LOW when an interruptible event occurs, INTB transitions LOW and returns HIGH when the processor reads the Interrupt register at addresses 03h.

## 6. Analog Switch Descriptions

The FSA9285A has a three-port data switch, providing routing capability to two data ports and one audio port. The two data switches are high bandwidth to provide high-speed USB 2.0 "eye" compliance. These switches also operate full-swing for full-speed USB and UART signals up to 4.4 V.

The high-performance negative-swing-capable audio switch utilizes a termination resistor for audio pop reduction. The audio configuration also provides for routing a microphone signal from a headset. The MIC signals can be routed to either the  $V_{BUS_{-}IN}$  pin for stereo audio configurations or the DP\_CON pin for mono audio configurations that also allow simultaneous charging over the  $V_{BUS}$  line.

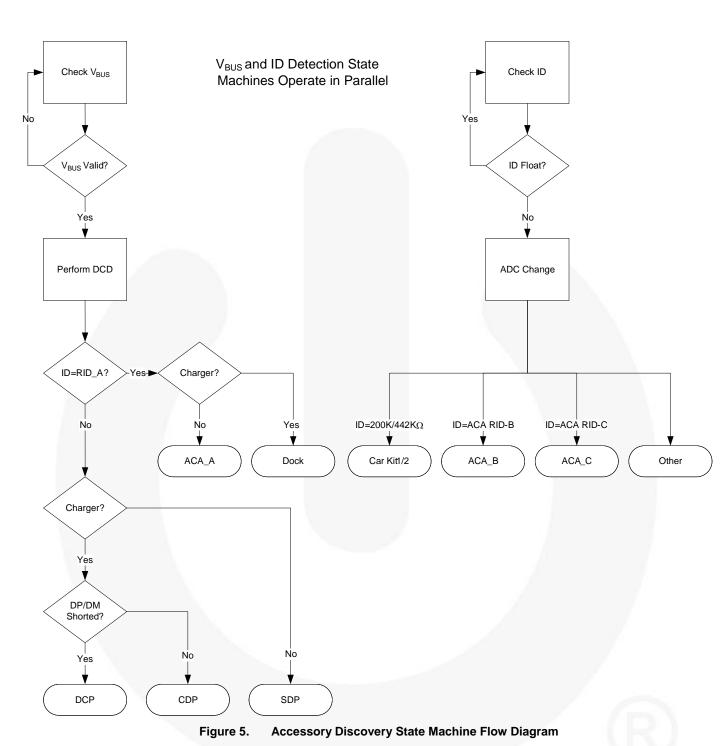

## 7. Accessory Detection

In Standby Mode, after power-up or reset, the FSA9285A monitors the V<sub>BUS\_IN</sub> and ID\_CON pins for any connectivity using very low power (see "Battery Supply Standby Mode Current" in the Switch Path DC Electrical Characteristics section). To minimize standby power, many functional blocks are powered down until an accessory attach is detected. The V<sub>BUS IN</sub> detection recognizes if the voltage on V<sub>BUS IN</sub> is within the valid range (>4.0 V). For resistance to GND on the ID\_CON pin, the FSA9285A measures voltage with an injected current to determine this resistance. All accessories attached or detached are reported to the processor via the Interrupt register. Any changes of resistance on the ID\_CON pin are reported as a Resistor\_Change interrupt. Additional information about the accessory is reported in the Device Type, Resistor Code, and Status registers. For USB accessories without an ID\_CON resistance, a V<sub>BUS\_Valid</sub> Change interrupt is reported to signal an attach or detach condition. Status of VBUS Valid and ID\_CON resistance is always available after any interrupt.

The USB detection flow is show in Figure 5. Note that the INTB Mask bit in the Control register must be cleared after a reset or power-up before interrupts can be signaled by the FSA9285A. Individual Interrupt Masks bits can be enabled by writing the Interrupt Mask register (see Table 6).

ID\_CON resistor detection is accomplished in a little more than three times the "Resistor Detection Time," where Resistor Detection Time bits are programmable in the Timing Set register. The FSA9285A is designed to allow up to 1 nF capacitance on the ID\_CON pin. ID\_CON is short-circuit protected from a faulty resistor or an accidental short where the current is limited to 5 mA sourced by the FSA9285A.

The detection of a  $V_{\text{BUS_IN}}$  goes through the USB detection flow only once.  $V_{\text{BUS_IN}}$  must be removed before the USB detection state machine reverts to its initial state.

After an initial attach, the FSA9285A continuously monitors the ID pin for changes and reports those changes to the baseband processor. To provide the fastest response for changes in button checking after initial attach, the FSA9285A indicates a change in ID\_CON resistor after two samples are taken instead of the three consecutive samples taken on initial attach. To save power, the resistor detection block can be disabled after an initial attach with the ID\_DIS bit in the Control register. The resistor detection block is normally disabled when no ID\_CON resistance is present (ID\_CON floating) to save power. The condition of ID\_FLOAT continues to be monitored regardless of the ID\_DIS setting.

Whenever a resistance is measured on ID\_CON, the USB discovery state machine halts after completion of its current state and the ID\_CON state machine continues for accessory detection. The only exception is when an ACA RID-A accessory is detected. In this case, the USB discovery state machine is used to differentiate between a docking station and a powered A-device attached to a docking station (*per USB Battery Charging Specification 1.2*).

If the EN\_MAN\_SW bit is set on attach, FSA9285A configures the switches to the state in the MANUAL SW register.

Upon the removal of any accessory, the FSA9285A detects and indicates a change in ID\_CON resistance (regardless of ID\_DIS bit setting), a removal of  $V_{\text{BUS}\_IN}$ , or both. The FSA9285A automatically opens all switches (and  $V_{\text{BUS}}$  FET) on detach (ID\_FLOAT and  $V_{\text{BUS}}$  not valid), even if the FSA9285A is set to Manual Switching Mode.

For the weak battery case, the FSA9285A needs to be in Automatic Switching Mode. Should the processor NOT be able to respond to INTB, FSA9285A must be placed in Automatic Switching Mode explicitly or  $V_{\text{DDIO}}$  must be removed, resetting the FSA9285A state to its default values.

**Note:** If the FSA9285A is to be used in automatic switching mode (EN\_MAN\_SW = 0) then the Manual SW register must be configured for all switches OPEN).

## Note:

Figure 5 illustrates operation with a valid V<sub>DDIO</sub> supply voltage. Figure 5 does not illustrate Dead Battery Provision (DBP) See Section 9 for details.

| Resistor            | ID_CON | Resistance | to GND | Auto Switch  | 11   |                                      |

|---------------------|--------|------------|--------|--------------|------|--------------------------------------|

| Code <sup>(4)</sup> | Min.   | Тур.       | Max.   | USB Switches | Unit | Accessory Detected                   |

| 10110               | 0      |            | 18     |              | Ω    | OTG                                  |

| 10100               | 19000  | 20000      | 21000  |              | Ω    | Resistor 20 kΩ                       |

| 10011               | 22800  | 24000      | 25200  |              | Ω    | Resistor 24 kΩ                       |

| 10010               | 27265  | 28700      | 30135  |              | Ω    | Resistor 28.7 kΩ                     |

| 10001               | 34675  | 36500      | 36865  | YES          | Ω    | ACA RID-C <sup>(5)</sup>             |

| 10000               | 39798  | 40200      | 40602  |              | Ω    | Resistor 40.2 kΩ                     |

| 01111               | 44650  | 47000      | 49350  |              | Ω    | MCPC Send/End                        |

| 01110               | 55638  | 56200      | 56762  |              | Ω    | Resistor 56.2 kΩ                     |

| 01101               | 64600  | 68000      | 71400  | YES          | Ω    | ACA RID-B <sup>(5)</sup>             |

| 01100               | 80275  | 84500      | 88725  |              | Ω    | Resistor 84.5 kΩ                     |

| 01011               | 96900  | 102000     | 107100 |              | Ω    | Phone Power Device                   |

| 01010               | 117800 | 124000     | 130200 | YES          | Ω    | ACA RID-A <sup>(5)</sup>             |

| 01001               | 148500 | 150000     | 151500 |              | Ω    | Resistor 150 kΩ                      |

| 01000               | 171000 | 180000     | 183600 |              | Ω    | MCPC Maintenance                     |

| 00111               | 198000 | 200000     | 202000 |              | Ω    | Car Kit Type-1 Charger <sup>(t</sup> |

| 00110               | 229680 | 232000     | 234320 |              | Ω    | Resistor 232 kΩ                      |

| 00101               | 272650 | 287000     | 301350 |              | Ω    | MCPC Mode 1                          |

| 00100               | 370500 | 390000     | 401700 |              | Ω    | MCPC Reserved                        |

| 00011               | 437580 | 442000     | 446420 |              | Ω    | Car Kit Type-2 Charger               |

| 00010               | 529150 | 557000     | 584850 |              | Ω    | MCPC Mode 3                          |

| 00001               | 757150 | 797000     | 836850 |              | Ω    | MCPC Mode 2                          |

| 00000               | 970000 |            | Open   | 0            | Ω    | Float <sup>(6)</sup>                 |

## Table 3. ID CON Resistor Identification

## Notes:

The resistor code values are reported in the Resistor Code register whenever a valid resistor code value changes. See Table 4 for details, additional requirements may be applicable for detection. 4.

5.

Resistance  $\ge$  970 k $\Omega$  status bit /ID\_FLOAT=0. 6.

## 8. USB Port and Charger Detection

The FSA9285A can detect the USB 2.0 port types summarized in Table 4.  $V_{BUS}$  must be present to detect these accessories.

For SDP, CDP, and ACA USB accessories; the following pin mapping is automatically configured:

- DP\_HOST1 = DP\_CON (If EN\_MAN\_SW = 0)

- DM\_HOST1 = DM\_CON (If EN\_MAN\_SW = 0)

- V<sub>BUS\_OUT</sub> = V<sub>BUS\_IN</sub>

The FSA9285A allows factory testing or programming through the DP\_HOST1 and DM\_HOST1 switches by closing these switches when a USB cable with an ID resistance or  $V_{\text{BUS}}$  voltage is detected.

For USB chargers that do not automatically close USB switches, the switches can be closed manually through the Manual Switch register when EN\_MAN\_SW is enabled.

Whenever V<sub>BUS\_IN</sub> becomes valid, the integrated charger FET is closed (unless EN\_MAN\_SW = 1 and Manual SW[1:0]≠11) and V<sub>BUS\_IN</sub> voltage is continuously monitored to incorporate Over-Voltage Protection (OVP). If the attached device is recognized as one of the chargers in Table 4 (excluding SDP), the CHG\_DETB pin goes LOW to send a signal to the charger IC, external to the FSA9285A, to increase the charging current to the maximum allowed level by the Over-Current Protection (OCP) trigger (see the Switch Path DC Electrical Characteristics section). V<sub>BUS\_OUT</sub> must be valid 10 ms before sourcing greater than 100 mA.

| Resistor<br>Code <sup>(7)</sup> | V <sub>BUS_IN</sub> | USB<br>Switches <sup>(8)</sup> | CHG_DETB <sup>(8)</sup> | ID_CON Resistance<br>to GND |         |           | Accessory Detected                                                                    |

|---------------------------------|---------------------|--------------------------------|-------------------------|-----------------------------|---------|-----------|---------------------------------------------------------------------------------------|

| Code                            |                     | Switches                       |                         | Min.                        | Тур.    | Max.      |                                                                                       |

| 00111                           | 5 V                 | Open                           | Asserted                | 198 kΩ                      | 200 kΩ  | 202 kΩ    | Car Kit Type-1 Charger                                                                |

| 00011                           | 5 V                 | Open                           | Asserted                | 437.58 kΩ                   | 442 kΩ  | 446.42 kΩ | Car Kit Type-2 Charger                                                                |

| 00000                           | 5 V                 | Open                           | Asserted                | 3 ΜΩ                        | Open    | Open      | USB Dedicated Charging Port, Travel Adapter or Dedicated Charger (DCP) <sup>(9)</sup> |

| 00000                           | 5 V                 | Auto_close                     | Asserted                | 3 MΩ                        | Open    | Open      | USB Charging Downstream Port (CDP) <sup>(9)</sup>                                     |

| 00000                           | 5 V                 | Auto_close                     | Not Asserted            | 3 MΩ                        | Open    | Open      | USB Standard Downstream Port (SDP) <sup>(9)</sup>                                     |

| 10001                           | 5 V                 | Auto_close                     | Asserted                | 34.675 kΩ                   | 36.5 kΩ | 36.865 kΩ | ACA RID-C                                                                             |

| 01101                           | 5 V                 | Auto_close                     | Asserted                | 64.6 kΩ                     | 68 kΩ   | 71.4 kΩ   | ACA RID-B                                                                             |

| 01010                           | 5 V                 | Auto_close                     | Asserted                | 117.8 kΩ                    | 124 kΩ  | 130.2 kΩ  | ACA RID-A                                                                             |

#### Table 4. ID CON and VRUS Detection for USB and Car Kit Devices

#### Notes:

7. The resistor code values are reported in the Resistor Code register, independent of the state of USB switches or V<sub>BUS IN</sub>.

8. In Table 4, switches auto-close and CHG\_DETB are asserted only if V<sub>BUS VALID</sub>.

9. The FSA9285A follows the Battery Charging 1.2 specification, which uses DP\_CON and DM\_CON to determine the USB accessory attached. Refer to Battery Charging 1.2 Specification for details.

## 9. Dead Battery Provision

Since V<sub>BUS</sub> charging power connects through it, the FSA9285A must automatically turn on the V<sub>BUS</sub> FET to allow the mobile device to charge after shutdown due to a dead battery. When detecting that V<sub>BUS</sub> is valid, the FSA9285A automatically turns on the V<sub>BUS</sub> FET after BC1.2 charger detection is complete. Turning on at this time allows the DP / DM switches to turn on at the same time as the V<sub>BUS</sub> FET.

If the FSA9285A detects a USB port (SDP, CDP, or DCP) when V<sub>BAT</sub> and V<sub>DDIO</sub> are not valid, it applies 0.6 V to DP\_CON in accordance with the USB BC1.2 Dead Battery Provision. The FSA9285A automatically removes the 0.6 V on DP\_CON upon detach of an accessory, when V<sub>DDIO</sub> returns to a valid voltage, or when V<sub>BAT</sub> > V<sub>BAT\_TH</sub>. If the mobile device should manually assert the 0.6 V on DP\_CON, it can do so using the ASSERT\_D+ bit (bit 2) of the Manual CHG\_CTRL register (14h); V<sub>BUS</sub> must be valid to do so.

## 10. Over-Voltage Protection (OVP) and Over-Current Protection (OCP)

When  $V_{\text{BUS_IN}}$  is less than nominally 6.5 V, the FSA9285A allows the  $V_{\text{BUS_IN}}$  supply to enter the chip-power select voltage regulator block. For  $V_{\text{BUS_IN}}$  greater than nominally 6.5 V, the input is disconnected, protecting the FSA9285A from excess voltage. Upon entering Shutdown Mode, the OVP bit in the Interrupt register is set HIGH (to reflect a change in OVP state) and an interrupt is sent to the baseband. The OVP Status register is also written HIGH to indicate that an OVP condition is present. In Shutdown Mode, the FSA9285A continually monitors  $V_{\text{BUS}}$  and exits Shutdown Mode when  $V_{\text{BUS}}$  drops to below 6.5 V or it senses an accessory detach. Upon exiting an OVP condition, another OVP interrupt is triggered (reflecting a change in OVP state) and the OVP status bit is cleared (indicating an OVP condition is not present).

The Over-Current Protection (OCP) feature limits current through the charger FET to nominally 1.45 A. OCP is only implemented when  $V_{BUS_IN}$  is provided by the attached accessory. The FSA9285A senses an over-current event, opens (turns off) the  $V_{BUS}$  FET, and reports this to the baseband by asserting the OCP bit (to reflect a change in OCP state) in the Interrupt register. When in an OCP state, the OCP status bit is written HIGH. While the OCP condition is present, the FSA9285A continually monitors the  $V_{BUS}$  current and exits Shutdown Mode when the  $V_{BUS}$  current drops below nominally 1.45 A or it senses an accessory detach. Upon exiting OCP state, the OCP Interrupt bit is again written HIGH, indicating a change in OCP state is not present.

## **11. Audio Accessory Detection**

After an audio device is attached and a change in ID\_CON resistance is detected (if ID\_DIS=0), the FSA9285A asserts an interrupt and the baseband processor can read the Resistor Code register to determine the ID\_CON resistance change to detect if a key, such as MCPC SEND / END, was pressed.

For powered audio accessories with V<sub>BUS</sub> present, the FSA9285A detects when V<sub>BUS</sub> is valid and interrupts the baseband processor. The baseband processor must manually control the FSA9285A switches for proper functionality. MIC can be switched to either V<sub>BUS</sub> or DP\_CON through the Manual SW register, allowing more flexibility.

# 12. Absolute Maximum Ratings

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol                              | Р                                                   | arameter                      |                  |          | Min. | Max. | Unit |

|-------------------------------------|-----------------------------------------------------|-------------------------------|------------------|----------|------|------|------|

| V <sub>BAT</sub> /V <sub>DDIO</sub> | Supply Voltage from Battery / Baseb                 | and                           |                  |          | -0.5 | 6.0  | V    |

| V <sub>BUS_IN</sub>                 | Supply Voltage from Micro-USB Cor                   | nnector                       |                  |          | -0.5 | 28.0 | V    |

|                                     |                                                     |                               | USB              |          | -1.0 | 6.0  |      |

| V <sub>SW</sub>                     | Switch I/O Voltage                                  | Stereo/Mono Audio Path Active |                  | -2.0     | 6.0  | V    |      |

|                                     |                                                     |                               | All Other Ch     | nannels  | -0.5 | 6.0  |      |

| I <sub>IK</sub>                     | Input Clamp Diode Current                           |                               |                  |          | -50  |      | mA   |

| I <sub>CHG</sub>                    | Charger Detect CHG_DETB Pin Current Sink Capability |                               |                  |          |      | 30   | mA   |

|                                     |                                                     |                               | USB              |          |      | 50   |      |

| I <sub>SW</sub>                     | Switch I/O Current (Continuous)                     | Audio                         |                  |          | 60   | mA   |      |

|                                     |                                                     | All Other Ch                  | nannels          |          | 50   |      |      |

|                                     |                                                     | USB                           |                  |          | 150  | mA   |      |

| lawar.u                             | Peak Switch Current (Pulsed at 1 ma                 | Audio                         |                  |          | 150  | mA   |      |

| ISWPEAK                             | <10% Duty Cycle)                                    |                               | Charger FE       | Т        |      | 2    | А    |

|                                     |                                                     |                               | All Other Ch     | nannels  |      | 150  | mA   |

| T <sub>STG</sub>                    | Storage Temperature Range                           |                               |                  |          | -65  | +150 | °C   |

| TJ                                  | Maximum Junction Temperature                        |                               |                  |          |      | +150 | °C   |

| TL                                  | Lead Temperature (Soldering, 10 Se                  | econds)                       |                  |          |      | +260 | °C   |

|                                     | IEC 61000-4-2 System Level (DP_0                    | Connector P                   |                  | All Gap  |      |      | V    |

| ESD                                 |                                                     | ON) to GND                    | US_IN, V BUS_IN, |          |      |      |      |

| 200                                 | Human Body Model, JEDEC JESD2                       | 2-A114                        |                  | All Pins | 5000 |      | v    |

|                                     | Charged Device Model, JEDEC JES                     | D22-C101                      |                  | All Pins | 1500 |      | ]    |

# 13. Recommended Operating Conditions

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol                      | Parameter                                     |                    | Min. | Тур.                 | Max. | Unit |

|-----------------------------|-----------------------------------------------|--------------------|------|----------------------|------|------|

| $V_{BAT}$                   | Battery Supply Voltage                        | 2.7                | 3.8  | 4.4                  | V    |      |

| $V_{BAT_TH}$                | Battery Supply Voltage Threshold for Weak / I | 2.7                | 3.0  | 3.3                  | V    |      |

| $V_{\text{BUS}\_\text{IN}}$ | Supply Voltage from V <sub>BUS_IN</sub> Pin   | 4.0                |      | 14.0 <sup>(10)</sup> | V    |      |

| V <sub>DDIO</sub>           | Processor Supply Voltage                      | 1.7                |      | 3.6                  | V    |      |

|                             | U                                             | SB Path Active     | 0    |                      | 4.4  |      |

| $V_{\text{SW}}$             | Switch I/O Voltage                            | udio Path Active   | -1.5 |                      | 3.0  | V    |

|                             | A                                             | ll Other Pins      | 0    |                      | 5.0  |      |

| <b>ID</b> <sub>CAP</sub>    | Capacitive Load on ID_CON Pin for Reliable A  | ccessory Detection |      |                      | 1.0  | nF   |

| T <sub>A</sub>              | Operating Temperature                         | -40                |      | +85                  | °C   |      |

Note:

10. Maximum operating condition set by design.

# 14. Switch Path DC Electrical Characteristics

All typical values are at  $T_A=25^{\circ}C$  unless otherwise specified.

| Ourself of              | Banamatan                                                                    |                     | O an alitian                                                           | T <sub>A</sub> =                | -40 to + | 85°C                    | Unit |

|-------------------------|------------------------------------------------------------------------------|---------------------|------------------------------------------------------------------------|---------------------------------|----------|-------------------------|------|

| Symbol                  | Parameter                                                                    | V <sub>BAT</sub> (V | ) Condition                                                            | Min.                            | Тур.     | Max.                    |      |

| Host Inte               | rface Pins (INTB, CHG-DETB)                                                  | 1                   |                                                                        | 11                              |          | 1                       | 1    |

| V <sub>OH</sub>         | Output High Voltage <sup>(11)</sup>                                          | 3.0 to 4.           | 4 I <sub>OH</sub> =2 mA                                                | $0.7 \ x \ V_{\text{DDIO}}$     |          |                         | V    |

| V <sub>OL</sub>         | Output Low Voltage                                                           | 3.0 to 4.           | 4 I <sub>OL</sub> =8 mA                                                |                                 |          | 0.4                     | V    |

| I <sup>2</sup> C Interf | ace Pins – Fast Mode (I2C_SDA, I2C_SC                                        | CL)                 |                                                                        |                                 |          |                         |      |

| VIL                     | Low-Level Input Voltage                                                      | 3.0 to 4.           | 4                                                                      |                                 |          | 0.3 x V <sub>DDIO</sub> | V    |

| V <sub>IH</sub>         | High-Level Input Voltage                                                     | 3.0 to 4.           | 4                                                                      | $0.7 \text{ x V}_{\text{DDIO}}$ |          |                         | V    |

| I <sub>I2C</sub>        | Input Current of I2C_SDA and I2C_SCL<br>Pins, Input Voltage 0.26 V to 2.34 V | 3.0 to 4.           | 4                                                                      | -10                             |          | 10                      | μA   |

| Switch O                | ff Characteristics                                                           |                     |                                                                        |                                 |          |                         |      |

| IOFF                    | Power-Off Leakage Current                                                    | 0                   | All Data Ports Except<br>Audio & MIC, V <sub>SW</sub> =4.4 V           |                                 |          | 10                      | μA   |

| I <sub>NO(OFF)</sub>    | Off Leakage Current                                                          | 4.4                 | All Ports Except Audio &<br>MIC, I/O Pins=0.3 V,<br>4.1 V, or Floating | -0.100                          | 0.001    | 0.100                   | μA   |

| IIDSHRT                 | Short-Circuit Current                                                        | 3.0 to 4.           | 4 Current Limit if<br>ID_CON=0                                         |                                 | 5        |                         | mA   |

| USB Swit                | tch (DP_HOSTn, DM_HOSTn) ON Paths                                            |                     |                                                                        |                                 |          |                         |      |

|                         | USB Switch Paths On Resistance <sup>(12,13)</sup>                            | 2.0.45.4            | V <sub>D+/D-</sub> =0, 0.4 V, I <sub>ON</sub> =8 mA                    |                                 | 8        | 10                      | Ω    |

| R <sub>ON</sub>         | USB Switch Paths On Resistance                                               | 3.0 to 4.           | V <sub>D+/D-</sub> =0, 3.6 V, I <sub>ON</sub> =8 mA                    |                                 | 11       | 17                      | Ω    |

| Charging                | FET ON Path                                                                  |                     |                                                                        |                                 |          |                         | -    |

| V <sub>OVP</sub>        | Over-Voltage Protection (OVP)<br>Threshold Voltage                           | 3.0 to 4.           | 4                                                                      | 6.2                             | 6.5      | 6.9                     | V    |

| R <sub>ON</sub>         | Charging FET On Resistance <sup>(12,13)</sup>                                | 3.0 to 4.           | 4 V <sub>BUS_IN</sub> =4.2 V-5.0 V,<br>I <sub>ON</sub> =1 A            |                                 | 200      |                         | mΩ   |

| I <sub>OCP</sub>        | Over-Current Protection (OCP)<br>Threshold Current                           | 3.0 to 4.           | 4 V <sub>BUS_IN</sub> =5.2 V                                           | 1.20                            |          | 1.65                    | A    |

Continued on the following page...

## Switch Path DC Electrical Characteristics (Continued)

All typical values are at  $T_A=25^{\circ}C$  unless otherwise specified.

|                 | Bananatan                                                                              | N 00                 |                      |                                                                                                                                                                | T <sub>A</sub> = | -40 to +8           | 5°C                 |      |

|-----------------|----------------------------------------------------------------------------------------|----------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------|---------------------|------|

| Symbol          | Parameter                                                                              | V <sub>BAT</sub> (V) | V <sub>BUS</sub> (V) | Condition                                                                                                                                                      | Min.             | Тур.                | Max.                | Unit |

| Audio_R         | / Audio_L Switch ON Paths                                                              |                      |                      | • • • •                                                                                                                                                        |                  |                     |                     | •    |

| P               | Audio Switch On Resistance <sup>(12,13)</sup>                                          |                      |                      | V <sub>L/R</sub> =-0.8 V,<br>0.8 V;<br>I <sub>ON</sub> =30 mA;<br>f=0-470 kHz                                                                                  |                  |                     | 3.5                 |      |

| R <sub>on</sub> |                                                                                        | 3.0 to 4.4 -         |                      | V <sub>L/R</sub> =-1.5 V,<br>1.5 V;<br>I <sub>ON</sub> =30 mA,<br>f=0-470 kHz                                                                                  |                  |                     |                     | Ω    |

|                 | Audio R <sub>on</sub> Flatness <sup>(12,14)</sup>                                      |                      |                      | V <sub>L/R</sub> =-0.8 V,<br>0.8 V;<br>I <sub>ON</sub> =30 mA,<br>f=0-470 kHz                                                                                  |                  |                     | 0.1                 | Ω    |

|                 |                                                                                        | 3.0 to 4.4 -         |                      | V <sub>L/R</sub> =-1.5 V,<br>1.5 V;<br>I <sub>ON</sub> =30 mA,<br>f=0-470 kHz                                                                                  |                  |                     | 0.2                 |      |

| RTERM           | Internal Termination Resistors                                                         |                      |                      |                                                                                                                                                                |                  | 1.5                 |                     | kΩ   |

| <b>MIC Swit</b> | ch ON Paths                                                                            |                      |                      |                                                                                                                                                                |                  |                     |                     |      |

|                 | (12.13)                                                                                |                      |                      | $\label{eq:states} \begin{array}{l} \mbox{MIC Connected} \\ \mbox{to } V_{BUS\_IN}, \\ V_{SW} = 0, \ 2.8 \ V; \\ I_{ON} = 30 \ mA \end{array}$                 |                  | 40                  |                     |      |

| R <sub>on</sub> | MIC Path ON Resistance <sup>(12,13)</sup>                                              | 3.0 to 4.4           |                      | $\begin{array}{l} \mbox{MIC Connected} \\ \mbox{to DP_CON}, \\ \mbox{V}_{SW} \mbox{=} 0, 2.8 \ \mbox{V}; \\ \mbox{I}_{ON} \mbox{=} 30 \ \mbox{mA} \end{array}$ |                  | 40                  |                     | Ω    |

| MICOVP          | Over-Voltage Protection (OVP) Threshold Voltage with MIC on $V_{\text{BUS_IN}}^{(15)}$ |                      |                      | MIC Connected<br>to V <sub>BUS_IN</sub><br>Entering OVP                                                                                                        | 2.80             |                     | 3.35                | V    |

| Total Cu        | rrent Consumption <sup>(17)</sup>                                                      |                      |                      |                                                                                                                                                                | 1                |                     |                     |      |

|                 | Battery Supply Standby Mode Current No<br>Accessory Attached (ID_CON Floating)         |                      | Floating             | VBUS Floating                                                                                                                                                  |                  | 10                  | 15                  |      |

| IBAT            | Average Battery Supply Standby Mode<br>Current with Accessory Attached                 | 3.0 to 4.4           | 0.0                  | ID_DIS=1                                                                                                                                                       |                  | 35                  | 50                  | μA   |

|                 | (ID_CON Not Floating)                                                                  |                      | 5.0                  | ID_DIS=1                                                                                                                                                       |                  | 100 <sup>(16)</sup> | 150 <sup>(16)</sup> |      |

Notes:

11. Does not apply to the CHG\_DETB pin because it is open drain.

12. Limits based on Electrical Characterization data.

13. On resistance is the voltage drop between the two terminals at the indicated current through the switch.

14. Flatness is the difference between the maximum and minimum values of on resistance over the specified range of conditions.

15. The MIC bias applied should not exceed 2.8 V.

- 16.  $V_{DDIO}$  of either 0 V or in the valid range of 1.7 V to 3.6 V.

- 17. Typically the battery charges from  $V_{\text{BUS}}$ .

# 15. Capacitance

| Symbol             | Devenetor                                                         |                      | Condition                         | T <sub>A</sub> = | Unit |      |      |

|--------------------|-------------------------------------------------------------------|----------------------|-----------------------------------|------------------|------|------|------|

|                    | Parameter                                                         | V <sub>ВАТ</sub> (V) | Condition                         | Min.             | Тур. | Max. | Unit |

| C <sub>ONUSB</sub> | DP_CON, DM_CON On Capacitance<br>(USB Mode, Both HOST1 and HOST2) | 3.8                  | V <sub>BIAS</sub> =0.2 V, f=1 MHz |                  | 8    |      | pF   |

| Cı                 | Capacitance for Each I/O Pin                                      | 3.8                  |                                   |                  | 2    |      | pF   |

| $C_{OFF}$          | Off Capacitance (HOST1 and HOST2)                                 | 3.8                  |                                   |                  | 2    |      | pF   |

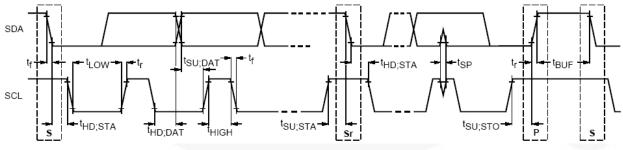

# 16. I<sup>2</sup>C AC Electrical Characteristics

| Cumb al             | Deremeter                                                         |                                      | Fast Mode |      |  |  |  |

|---------------------|-------------------------------------------------------------------|--------------------------------------|-----------|------|--|--|--|

| Symbol              | Parameter                                                         | Min.                                 | Max.      | Unit |  |  |  |

| f <sub>SCL</sub>    | SCL Clock Frequency                                               | 0                                    | 400       | kHz  |  |  |  |

| t <sub>HD;STA</sub> | Hold Time (Repeated) START Condition                              | 0.6                                  |           | μs   |  |  |  |

| t <sub>LOW</sub>    | LOW Period of SCL Clock                                           | 1.3                                  |           | μs   |  |  |  |

| t <sub>HIGH</sub>   | HIGH Period of SCL Clock                                          | 0.6                                  |           | μs   |  |  |  |

| t <sub>su;sta</sub> | Set-up Time for Repeated START Condition                          | 0.6                                  |           | μs   |  |  |  |

| t <sub>HD;DAT</sub> | Data Hold Time                                                    | 0                                    | 0.9       | μs   |  |  |  |

| t <sub>SU;DAT</sub> | Data Set-up Time <sup>(18)</sup>                                  | 100                                  |           | ns   |  |  |  |

| tr                  | Rise Time of SDA and SCL Signals <sup>(19)</sup>                  | 20+0.1C <sub>b</sub> <sup>(18)</sup> | 300       | ns   |  |  |  |

| t <sub>f</sub>      | Fall Time of SDA and SCL Signals <sup>(19)</sup>                  | 20+0.1C <sub>b</sub> <sup>(18)</sup> | 300       | ns   |  |  |  |

| t <sub>su;sто</sub> | Set-up Time for STOP Condition                                    | 0.6                                  |           | μs   |  |  |  |

| t <sub>BUF</sub>    | BUS-Free Time between STOP and START Conditions                   | 1.3                                  |           | μs   |  |  |  |

| t <sub>SP</sub>     | Pulse Width of Spikes that Must Be Suppressed by the Input Filter | 0                                    | 50        | ns   |  |  |  |

Notes:

- C<sub>b</sub> equals the total capacitance of one BUS line in pf. If mixed with high-speed devices; faster fall times are allowed, according to the I<sup>2</sup>C Bus specification.

- 19. A fast-mode I<sup>2</sup>C Bus<sup>®</sup> device can be used in a Standard-Mode I<sup>2</sup>C-Bus system, but the requirement that t<sub>SU;DAT</sub> ≥ 250 ns must be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line t<sub>r\_max</sub> + t<sub>SU;DAT</sub> = 1000 + 250 = 1250 ns before the SCL line is released (according to the Standard-Mode I<sup>2</sup>C Bus specification).

Figure 6. Definition of Timing for Full-Speed Mode Devices on the I<sup>2</sup>C Bus<sup>®</sup>

## Table 5. I<sup>2</sup>C Slave Address

| Name          | Size (Bits) | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------------|-------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Slave Address | 8           | 0     | 1     | 0     | 0     | 1     | 0     | 1     | R/W   |

# **17. Switch Path AC Electrical Characteristics**

All typical values are for V<sub>BAT</sub>=3.8 V at T<sub>A</sub>=25°C unless otherwise specified.

| Ourseland           | Demonster                                                                                                                                                                             |               | O an dition a                                                                  | T <sub>A</sub> = | -40 to + | 85°C | 110:4 |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------------|------------------|----------|------|-------|

| Symbol              | Parameter                                                                                                                                                                             |               | Conditions                                                                     | Min.             | Тур.     | Max. | Unit  |

| Vtalle              | Active Channel Crosstalk                                                                                                                                                              | Audio Mode    | f=20 kHz, $R_T$ =32 $\Omega$ , $C_L$ =0 pF                                     |                  | -90      |      | dB    |

| Xtalk               | DP_CON to DM_CON                                                                                                                                                                      | USB Mode      | f=1 MHz, $R_T$ =50 $\Omega$ , $C_L$ =0 pF                                      |                  | -60      |      | aв    |

| O <sub>IRR</sub>    | Off Isolation                                                                                                                                                                         | Audio Mode    | f=20 kHz, $R_T$ =32 $\Omega$ , $C_L$ =0 pF                                     |                  | -100     |      | dB    |

| OIRR                |                                                                                                                                                                                       | USB Mode      | f=1 MHz, $R_T$ =50 $\Omega$ , $C_L$ =0 pF                                      |                  | -60      |      | ųБ    |

| PSRR                | Power Supply Rejection Ratio                                                                                                                                                          | , MIC on      | Power Supply Noise 300 Mv <sub>PP</sub> ,<br>f=217 Hz Sine Wave                |                  | -100     |      | dB    |

| THD                 | Total Harmonic Distortion (Au                                                                                                                                                         | dio Path)     | 20 Hz to 20 kHz, R <sub>L</sub> =32/16 Ω,<br>Input Signal Range -1.5 V, +1.5 V |                  | 0.07     |      | %     |

| t <sub>SK(P)</sub>  | Skew of Opposite Transitions<br>Output (USB Mode)                                                                                                                                     | of the Same   | $t_r{=}t_f{=}750$ ps (10-90%) at 240 MHz, $C_L{=}0$ pF, $R_L{=}50$ $\Omega$    |                  | 35       |      | ps    |

| t <sub>I2CRST</sub> | Time When I2C_SDA and I2C<br>LOW to Cause Reset                                                                                                                                       | SCL Both      | See Figure 7                                                                   | 30               |          |      | ms    |

| <b>t</b> SDPDET     | Time from V <sub>BUS_IN</sub> Valid to V <sub>BU</sub><br>Charger FET Closed and USE<br>Closed for USB Standard Dov                                                                   | 3 Switches    | See Figure 9                                                                   |                  | 120      |      | ms    |

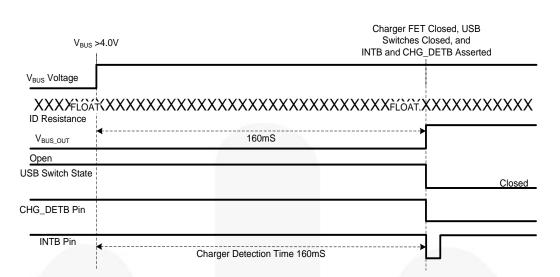

| tсндоит             | Time from V <sub>BUS_IN</sub> Valid to V <sub>BU</sub><br>Charger FET Closed for Both<br>Ports (CDP and DCP)                                                                          |               | See Figure 10                                                                  |                  | 160      |      | ms    |

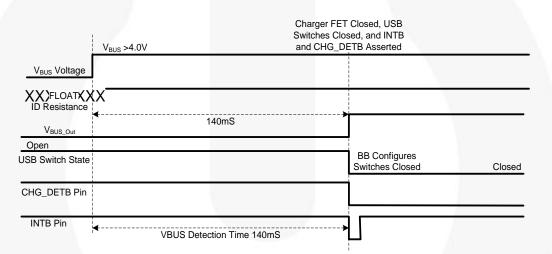

| <b>t</b> CARKIT     | Time from V <sub>BUS_IN</sub> Valid to Car<br>Type-2 Charger Detected                                                                                                                 | Kit Type-1 or | See Figure 11                                                                  |                  | 140      |      | ms    |

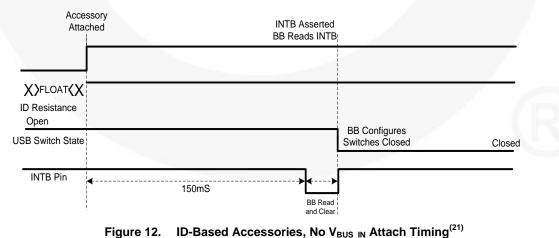

| tiddet              | Time from ID_CON Not Floating to INTB<br>LOW to Signal Accessory Attached that is<br>ID_CON Resistance-Based Only<br>(V <sub>BUS_IN</sub> Not Valid, Default timing<br>configuration) |               | See Figure 12                                                                  |                  | 150      |      | ms    |

| t <sub>BC11</sub>   | Timeout for Data Contact Dur                                                                                                                                                          | ng DCD Check  |                                                                                | 300              | 600      | 900  | ms    |

FSA9285A— MCPC Compliant USB Port Multimedia Switch with Auto-Detection, 12 V V<sub>BUS</sub>

Figure 10. USB Dedicated Charging Port (DCP) or Charging Downstream Port (CDP) Attach Timing<sup>(20)</sup>

- Figure 12. ID-Dased Accessories, No V<sub>BUS\_N</sub> Attach Thining

- USB Switch State timing is based on Automatic Switching mode (EN\_MAN\_SW = 0). Automatic switching excludes DCP.

ID\_CON resistance detection based on default Timing Set and Applications register values and on initial ID\_CON accessory attach only (50 ms Resistor Detection Time with three ID checks on initial attach = 150 ms typical detection time).

FSA9285A---

MCPC Compliant USB Port Multimedia Switch with Auto-Detection, 12 V V<sub>BUS</sub>

# **19. Bit Definitions**

## Table 6. I<sup>2</sup>C Register Map

|         |                    |      | •              |                   |                                    |                         |                   |                         |                                            |                                          |                                          |

|---------|--------------------|------|----------------|-------------------|------------------------------------|-------------------------|-------------------|-------------------------|--------------------------------------------|------------------------------------------|------------------------------------------|

| Address | Register           | Туре | Reset<br>Value | Bit 7             | Bit 6                              | Bit 5                   | Bit 4             | Bit 3                   | Bit 2                                      | Bit 1                                    | Bit 0                                    |

| 01H     | Device ID          | R    | 00010000       |                   |                                    | Version I               | D                 |                         |                                            | Do Not Use                               |                                          |

| 02H     | Control            | R/W  | 11010001       | DCD Timeout<br>EN | RESETB                             | ID_DIS                  | EN_MAN_SW         | Do Not Use              | Do Not Use                                 | Do Not Use                               | INT Mask                                 |

| 03H     | Interrupt          | R/C  | 00000000       | Do Not Use        | OCP<br>Change                      | OVP<br>Change           | MIC_OVP<br>Change | Resistor Code<br>Change | V <sub>BUS</sub> _Valid<br>Change          | BC1.2_Complete                           | Do Not Use                               |

| 05H     | Interrupt<br>Mask  | R/W  | 00000000       | Do Not Use        | OCP                                | OVP                     | MIC_OVP           | Resistor Code<br>Change | $V_{\text{BUS}}$ Valid                     | BC1.2_Complete                           | Do Not Use                               |

| 07H     | Resistor<br>Code   | R    | 00000000       | Do Not Use        | Do Not Use Do Not Use Resistor Cod |                         |                   | le                      |                                            |                                          |                                          |

| 08H     | Timing Set         | R/W  | 00000000       |                   | Do Not Use                         |                         |                   | Resistor Detection Time |                                            |                                          |                                          |

| 09H     | Status             | R    | 00000000       | ID_SHORT          | OCP                                | OVP                     | MIC_OVP           | /ID_FLOAT               | $V_{\text{BUS}}$ Valid                     | BC1.2_Active                             | DCD                                      |

| 0AH     | Device Type        | R    | 00000000       | Do Not Use        | Do Not<br>Use                      | Dock                    | Do Not Use        | Do Not Use              | USB<br>Dedicated<br>Charging<br>Port (DCP) | USB Charging<br>Downstream Port<br>(CDP) | USB Standard<br>Downstream<br>Port (SDP) |

| 0BH     | DAC SAR            | R    | 00000000       |                   |                                    |                         | DA                | C SAR Value             |                                            |                                          |                                          |

| 13H     | Manual SW          | R/W  | 00100111       | D- 8              | Switching                          |                         |                   | D+ Switching            |                                            | V <sub>BUS</sub> Sw                      | itching                                  |

| 14H     | Manual<br>CHG_CTRL | R/W  | 00000000       | Do Not Use        | Do Not<br>Use                      | MIC OVPENI Assert D+ Do |                   | Do Not                  | Use                                        |                                          |                                          |

| 1BH     | Applications1      | R/W  | X0001000       | Do Not Use        | Do Not<br>Use                      | Do Not<br>Use           | # of Consec       | utive ID Matches        | s for Attach                               | Do Not Use                               | Do Not Use                               |

| 1CH     | Applications2      | R/W  | XXXX0101       | Do Not Use        | Do Not<br>Use                      | Do Not<br>Use           | Do Not Use        | # ID Checks<br>Code C   |                                            | Max. Capacit                             | ance on ID                               |

## Table 7. Device ID

- Address: 01H

- Reset Value: 00010000

- Type: Read

| Bit # | Name       | Size (Bits) | Description   |

|-------|------------|-------------|---------------|

| 7:3   | Version ID | 5           | Rev 0.0=00010 |

| 2:0   | Do Not Use | 3           | Do not use    |

## Table 8. Control

- Address: 02H

- Reset Value: 11010001

- Type: Read/Write

| Bit # | Name          | Size<br>(Bits) | Description                                                                                                                                                                                                                                                                   |

|-------|---------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | DCDTimeout_EN | 1              | 1: DCD timeout is enabled.<br>0: DCD timeout is disabled.                                                                                                                                                                                                                     |

| 6     | RESETB        | 1              | 1: Do nothing.<br>0: Reset FSA9285A – resets all of FSA9285A except the Control register (02H),<br>Manual SW (13H), and Manual CHG_CTRL(14H).<br><b>Note</b> : This bit is momentarily set to 0 on a write. It immediately reverts to 1.                                      |

| 5     | ID_DIS        | 1              | <ol> <li>1: ID_CON resistor detection is disabled after a resistance is detected on ID_CON.</li> <li>0: ID_CON resistor detection is enabled after a resistance is detected on ID_CON.</li> <li>Note: The FSA9285A continues to monitor for an ID_FLOAT condition.</li> </ol> |

| 4     | EN_MAN_SW     | 1              | 1: Configure switches based on Manual SW register settings.                                                                                                                                                                                                                   |

FSA9285A---

| Bit # | Name       | Size<br>(Bits) | Description                                                                                                                                                                                                                         |

|-------|------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |            |                | 0: Use only defined automatic switch settings.                                                                                                                                                                                      |