# **Atmel ATPL100A**

# FSK Power Line Communications SoC

# DATASHEET

### **Features**

- Core

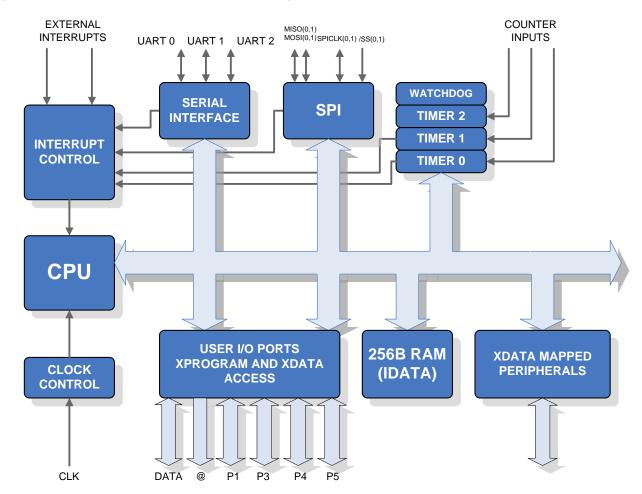

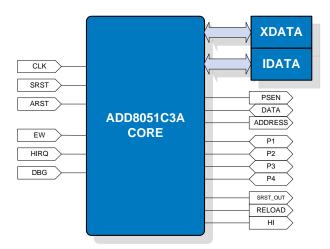

- ADD8051C3A enhanced 8051 core

- Speedups up to x5 vs. standard 8051 microcontroller

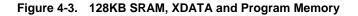

- 128Kbytes internal SRAM

- In-circuit serial flash programming

- Auto boot-loading program from serial flash

- Media Access Control

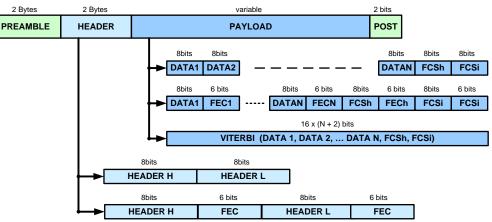

- Convolutional and block (FEC) channel coding, Viterbi decoding

- Hardware CRC error detection and FEC error correction

- By-pass mode to support earlier no-MAC FSK modem software

- Modem

- Power Line Carrier Modem for 50 and 60 Hz mains

- 8 Programmable Carrier Frequencies from 60 to 132.5KHz

- Baud rate Selectable: 600 to 4800 bps

- Half Duplex communication

- Receiver Sensitivity: Up to 44dBµVrms

- Peripherals

- Three 2-wire UARTs

- Two SPI. SPI to serial flash and External RTC. Buffered SPI to external metering IC

- Programmable Watchdog

- Quad dimmer in/out

- 24x8/28x4 segments LCD driver

- Up to 20 I/O lines

- Package

- 144-lead LQFP, 16 x 16 mm, pitch 0.4 mm

- Pb-free and RoHS compliant

- Typical Applications

- Automated Meter Reading (AMR) & Advanced Meter Management (AMM)

- Street lighting

- Home Automation

### Description

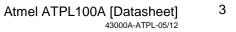

The ATPL100A is a Power Line Communications System on Chip that implements a full PLC node using FSK modulations and includes a hardwired Medium Access Controller (ADD1210). It has been developed to reduce the CPU computational load in PLC systems. Thus, the microcontroller is free to be used in the applications tasks.

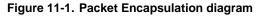

MAC functional capabilities of ATPL100A (performed in ADD1210 Medium Access Controller) involve the construction of message packets, adding convolutional or FEC (Forward Error Correction) codes to bytes and FCS (Frame Check Sequence) to packets. In reception, the MAC provides frame detection and Viterbi decoding or FCS and FEC correction.

ATPL100A MAC design is versatile and allows users to create a wide range of datagram structures. The MAC shall be set in a bypass mode allowing direct connection between the microcontroller and the modem to support old FSK software that doesn't include the MAC.

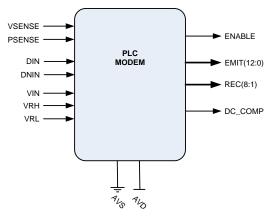

ATPL100A PLC modem (ADD1310) is based on a Frequency-shift keying (FSK) Modulation Scheme supporting Minimum Shift Frequency (MSK) with selectable carrier frequencies from 60 KHz to 132,5KHz. It shall work using a single power supply of 3.3V and a few external components, supporting several Analog Front End (AFE) configurations suitable for Home Automation purposes. It can replace the traditional analog PLC modem and can use the same software libraries or a simplified version if the hardwired MAC is used. The PLC modem fits CENELEC C-band and EN50065-1 access rules, and has receiver sensitivity up to 44dBµVrms (158 µVrms).

ATPL100A core (ADD8051C3A) includes all features of the standard 8051, with an average speed up x5 and some additional features.

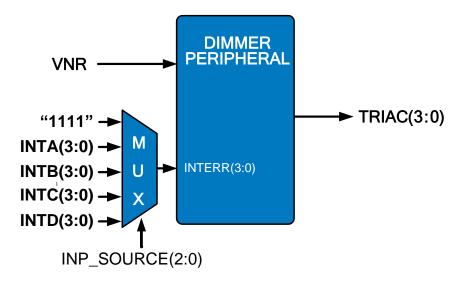

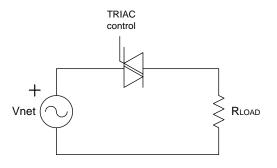

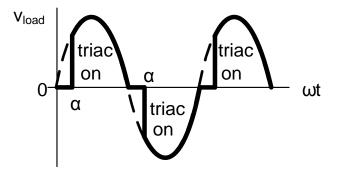

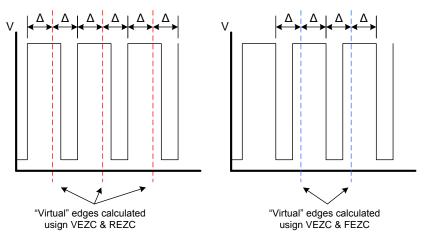

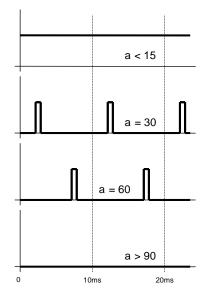

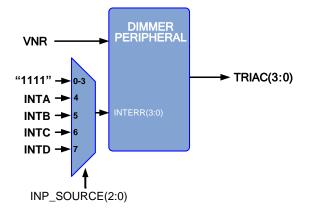

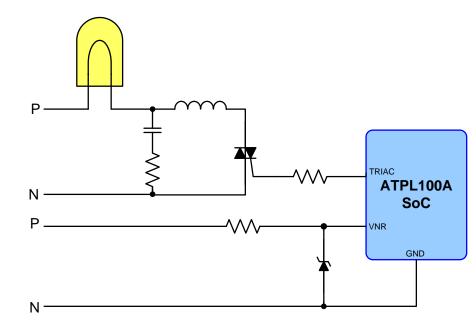

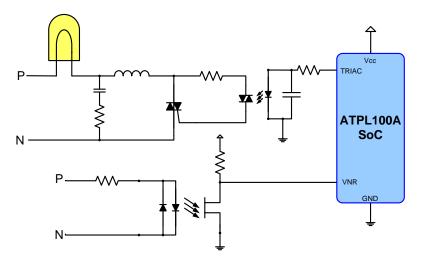

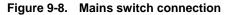

The microcontroller includes some specific peripherals as 4 input / 4 output dimmers for power regulation (phase angle control), and also capable of generating PWM (Pulse-Width Modulation) control.

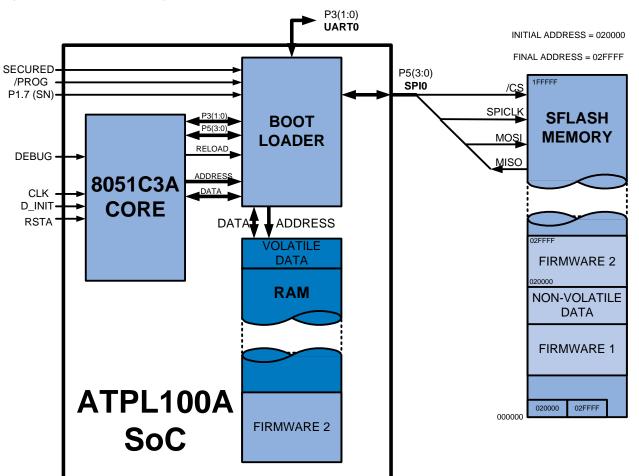

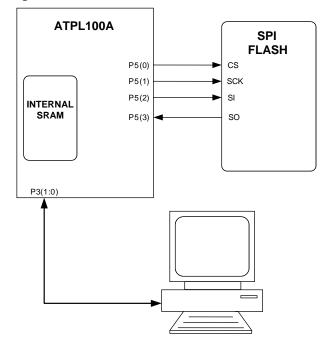

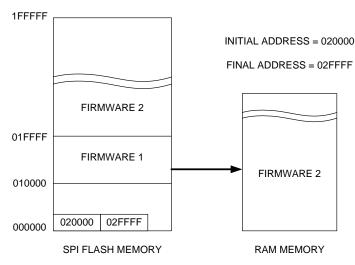

A flash program loader allows downloading the microcontroller program in a standard SPI serial flash memory and executing it from internal SRAM. In the start-up process, the program is uploaded from serial flash to the internal 128Kbytes of SRAM before starting the execution. After start-up, the free space in the serial flash shall be used to store application data. ATPL100A includes an encryption engine for code protection. Using a larger flash, several programs should be stored at the same time and the microcontroller shall switch from one program to another. This feature could be used to reprogram the SoC using PLC downloading.

# **Table of Contents**

| 1. | Block Diagram7 |                                                                               |      |  |  |  |  |  |

|----|----------------|-------------------------------------------------------------------------------|------|--|--|--|--|--|

| 2. | Pacl           | kage and Pinout                                                               | 8    |  |  |  |  |  |

|    | 2.1            | 144-Lead LQFP Package Outline                                                 | 8    |  |  |  |  |  |

|    | 2.2            | 144-Lead LQFP Pinout                                                          |      |  |  |  |  |  |

|    |                |                                                                               |      |  |  |  |  |  |

| 3. | Pin I          | Description                                                                   | 11   |  |  |  |  |  |

| 4. |                | cessor and Architecture                                                       |      |  |  |  |  |  |

|    | 4.1            | ADD8051C3A Microcontroller Description                                        |      |  |  |  |  |  |

|    | 4.2            | Core Pinout Description                                                       |      |  |  |  |  |  |

|    | 4.3            | Memory Organization                                                           |      |  |  |  |  |  |

|    |                | 4.3.1 Program Memory                                                          |      |  |  |  |  |  |

|    |                | 4.3.2 Extended Addressing                                                     |      |  |  |  |  |  |

|    |                | 4.3.3 Data Memory                                                             |      |  |  |  |  |  |

|    | 4.4            | 4.3.4 SFR Registers<br>Instruction Set                                        |      |  |  |  |  |  |

|    | 4.4            |                                                                               |      |  |  |  |  |  |

|    |                | <ul><li>4.4.1 Program Status Word</li><li>4.4.2 Addressing Modes</li></ul>    |      |  |  |  |  |  |

|    |                | 4.4.3 Arithmetic Instructions                                                 |      |  |  |  |  |  |

|    |                | 4.4.4 Logical Instructions                                                    |      |  |  |  |  |  |

|    |                | 4.4.5 Data Transfer Instructions                                              |      |  |  |  |  |  |

|    |                | 4.4.6 Boolean Instructions                                                    |      |  |  |  |  |  |

|    |                | 4.4.7 Jump Instructions                                                       | . 37 |  |  |  |  |  |

|    | 4.5            | CPU Timing                                                                    | . 39 |  |  |  |  |  |

|    |                | 4.5.1 Reset                                                                   |      |  |  |  |  |  |

|    |                | 4.5.2 Power Saving Modes                                                      |      |  |  |  |  |  |

|    |                | 4.5.3 Idle Mode                                                               |      |  |  |  |  |  |

|    | 4.0            | 4.5.4 Power-Down Mode                                                         |      |  |  |  |  |  |

|    | 4.6            | Interrupts                                                                    |      |  |  |  |  |  |

|    |                | 4.6.1 Interrupt Enabling                                                      |      |  |  |  |  |  |

|    |                | <ul><li>4.6.2 Interrupt Priorities</li><li>4.6.3 Interrupt Handling</li></ul> |      |  |  |  |  |  |

|    | 4.7            | I/O Ports                                                                     |      |  |  |  |  |  |

|    | 4.7            | 4.7.1 I/O Configurations                                                      |      |  |  |  |  |  |

|    |                | 4.7.2 Read-Modify-Write Feature                                               |      |  |  |  |  |  |

|    |                | 4.7.3 Accessing External Memories                                             |      |  |  |  |  |  |

|    | 4.8            | Debug Mode                                                                    |      |  |  |  |  |  |

| ~  | <b>T</b> :     |                                                                               |      |  |  |  |  |  |

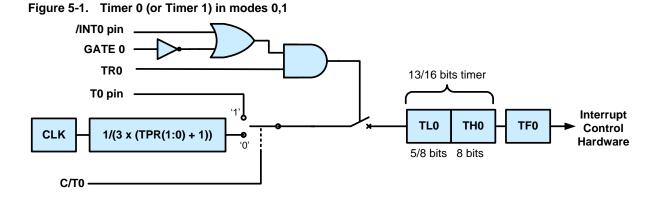

| 5. | 1 Ime          | ers                                                                           | 50   |  |  |  |  |  |

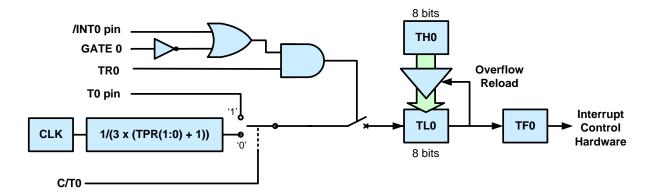

|    | 5.1            | Timer 0 and Timer 1                                                           |      |  |  |  |  |  |

|    |                | 5.1.1 Timer Mode 0                                                            |      |  |  |  |  |  |

|    |                | 5.1.2 Timer Mode 1                                                            |      |  |  |  |  |  |

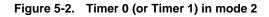

|    |                | 5.1.3 Timer Mode 2                                                            |      |  |  |  |  |  |

|    | FO             | 5.1.4 Timer Mode 3                                                            |      |  |  |  |  |  |

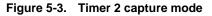

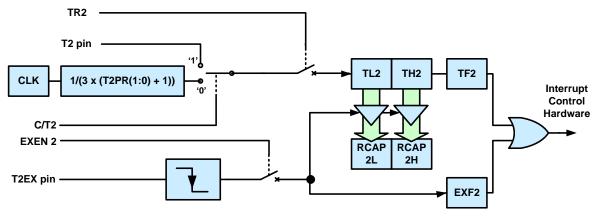

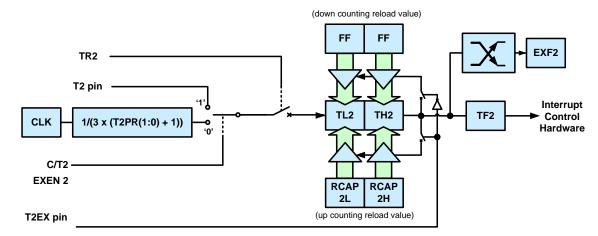

|    | 5.2            | Timer 2                                                                       |      |  |  |  |  |  |

|    |                | 5.2.2 Capture mode<br>5.2.3 Auto-Reload mode                                  |      |  |  |  |  |  |

|    |                | 5.2.3 Auto-Reload mode<br>5.2.4 Clock-Out mode                                |      |  |  |  |  |  |

|    |                | 5.2.4 Clock-Out mode<br>5.2.5 Baud rate Generator mode                        |      |  |  |  |  |  |

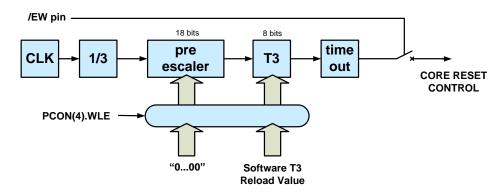

|    | 5.3            | Watchdog (timer 3)                                                            |      |  |  |  |  |  |

| 6. | Stan           | ndard Serial Interfaces                                                       | 58   |  |  |  |  |  |

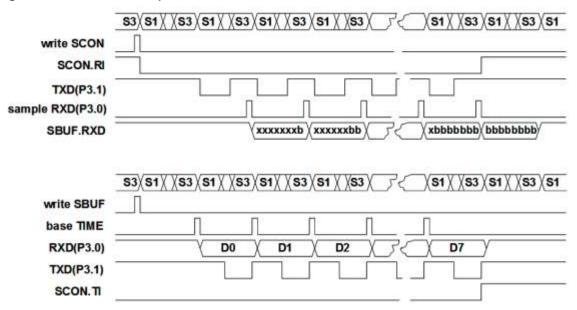

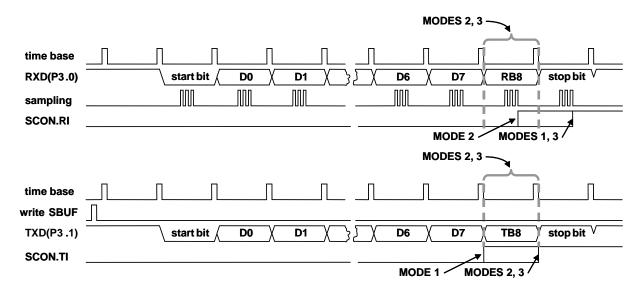

|    | 6.1            | Serial Port modes                                                             |      |  |  |  |  |  |

|    | 0.1            | 6.1.1 Mode 0 (shift register mode)                                            |      |  |  |  |  |  |

|    |                | 6.1.2 Mode 1 (8-bit UART)                                                     |      |  |  |  |  |  |

|    |                | 6.1.3 Modes 2 and 3 (9-bit UART)                                              | . 59 |  |  |  |  |  |

|    | 6.2            | Serial Port Timers (Timers 11, 12 and 14)                                     | . 60 |  |  |  |  |  |

|     | Seria                                | al Peripheral Interfaces SPI0 and SPI1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 64                                                                                                                                                                                  |

|-----|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

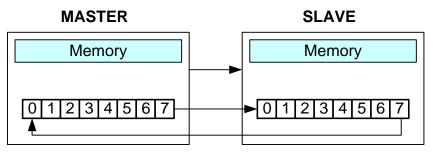

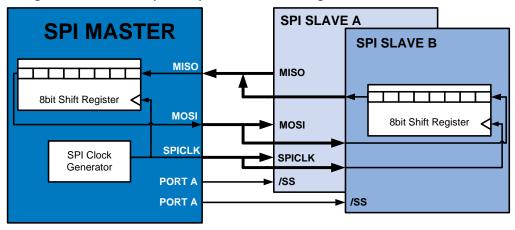

|     | 7.1                                  | SPI description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                     |

|     |                                      | 7.1.2 SPI clock phase, polarity and operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66                                                                                                                                                                                  |

|     | 7.0                                  | 7.1.3 SPI0 write collision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                     |

|     | 7.2                                  | SPI Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                     |

|     | 7.3                                  | SPI1 buffer operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                     |

| 8.  |                                      | t Loader                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                     |

|     | 8.1                                  | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                     |

|     | 8.2                                  | Flash Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                     |

|     |                                      | <ul><li>8.2.1 In-System programming</li><li>8.2.2 SPI Flash programming</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                     |

|     | 8.3                                  | System startup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                     |

|     | 0.0                                  | 8.3.2 Encrypted firmware requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                     |

|     |                                      | 8.3.3 Supported Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                     |

|     |                                      | 8.3.3.1 Serial Number Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                     |

| 9.  | Dimr                                 | mer Peripheral                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                     |

|     | 9.1                                  | Configuration Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 79                                                                                                                                                                                  |

|     |                                      | 9.1.1 DIM_CTRL register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                     |

|     |                                      | 9.1.2 INP_ST register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                     |

|     |                                      | 9.1.3 OUT_ST register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                     |

|     |                                      | 9.1.4 OUT_REF registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                     |

|     |                                      | 9.1.5 POLARITY register<br>9.1.6 D CONF register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                     |

|     |                                      | 9.1.6 D_CONF register<br>9.1.7 V_SWC register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                     |

|     |                                      | 9.1.8 PWM_PER register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                     |

|     |                                      | 9.1.9 INP_SOURCE register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                     |

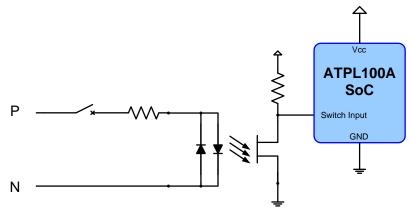

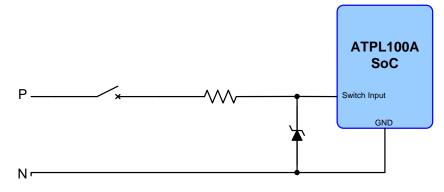

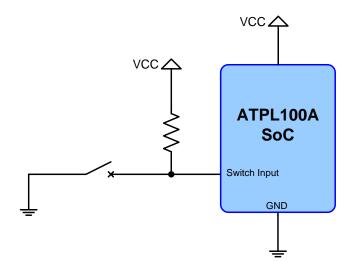

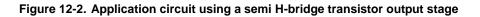

|     | 9.2                                  | External Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 89                                                                                                                                                                                  |

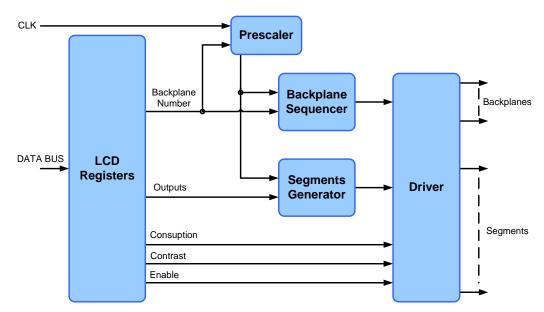

| 10  | . LCD                                | Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                     |

|     | 10.1                                 | External Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                     |

|     | 10.2                                 | Register Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 92                                                                                                                                                                                  |

|     |                                      | 10.2.1 CONFIC register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                     |

|     |                                      | 10.2.1 CONFIG register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                     |

|     |                                      | 10.2.2 CONTRAST register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 93<br>94                                                                                                                                                                            |

|     | 10.3                                 | 10.2.2       CONTRAST register         10.2.3       Output Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                     |

|     | 10.3                                 | 10.2.2       CONTRAST register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                     |

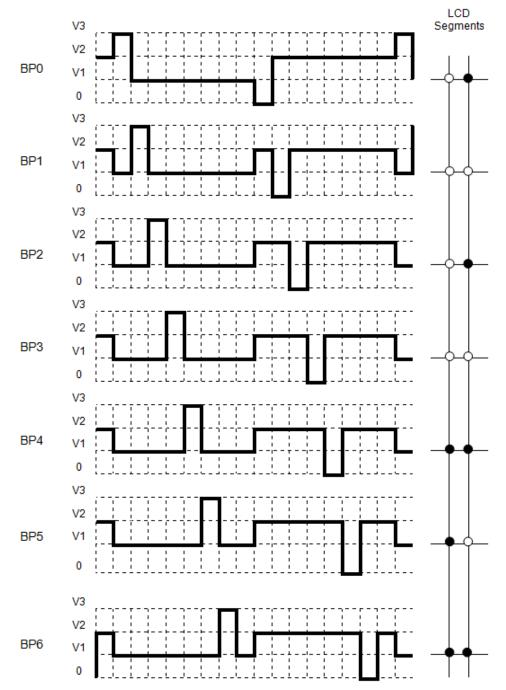

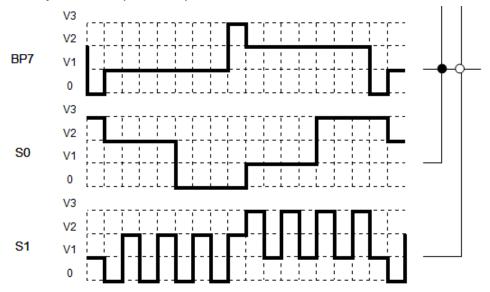

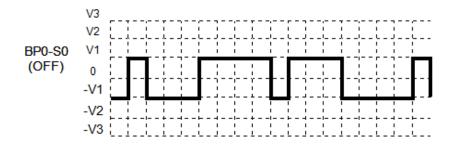

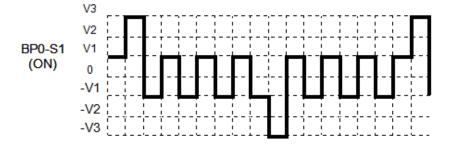

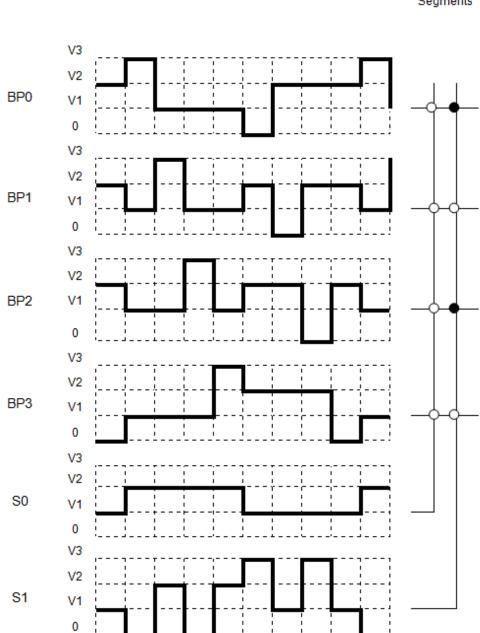

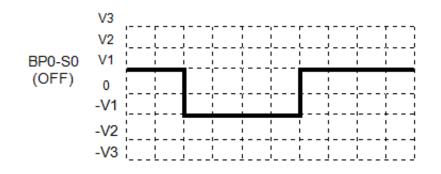

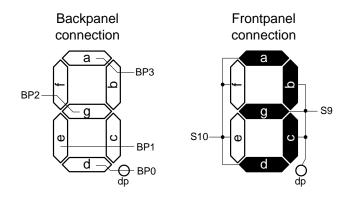

|     | 10.3                                 | <ul> <li>10.2.2 CONTRAST register</li> <li>10.2.3 Output Registers</li> <li>LCD Waveform examples</li> <li>10.3.1 Operation mode 1: 1/8 duty multiplexed</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 93<br>94<br>95<br>97<br>97                                                                                                                                                          |

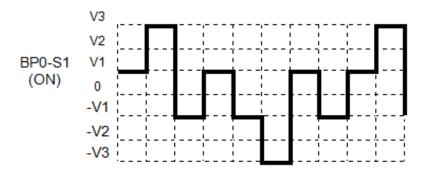

|     | 10.3<br>10.4                         | <ul> <li>10.2.2 CONTRAST register</li> <li>10.2.3 Output Registers</li> <li>LCD Waveform examples</li> <li>10.3.1 Operation mode 1: 1/8 duty multiplexed</li> <li>10.3.2 Operation mode 2: ¼ duty multiplexed</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                              | 93<br>94<br>95<br>97<br>97<br>99<br>99                                                                                                                                              |

| 11. | 10.4                                 | <ul> <li>10.2.2 CONTRAST register</li> <li>10.2.3 Output Registers</li> <li>LCD Waveform examples</li> <li>10.3.1 Operation mode 1: 1/8 duty multiplexed</li> <li>10.3.2 Operation mode 2: ¼ duty multiplexed</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                              | 93<br>94<br>95<br>97<br>97<br>97<br>99<br>                                                                                                                                          |

| 11. | 10.4                                 | 10.2.2       CONTRAST register         10.2.3       Output Registers         LCD Waveform examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 93<br>94<br>95<br>97<br>97<br>99<br>99<br>100<br>102<br>102                                                                                                                         |

| 11. | 10.4<br>. <b>Med</b>                 | 10.2.2       CONTRAST register         10.2.3       Output Registers         LCD Waveform examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 93<br>94<br>95<br>97<br>97<br>99<br>99<br>100<br>102<br>102<br>104                                                                                                                  |

| 11. | 10.4<br>. <b>Med</b><br>11.1         | 10.2.2       CONTRAST register         10.2.3       Output Registers         LCD Waveform examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 93<br>94<br>95<br>97<br>97<br>99<br>97<br>97<br>99<br>100<br>102<br>102<br>104<br>104                                                                                               |

| 11. | 10.4<br>. <b>Med</b><br>11.1<br>11.2 | 10.2.2       CONTRAST register         10.2.3       Output Registers         LCD Waveform examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 93<br>94<br>95<br>97<br>97<br>99<br>100<br>102<br>102<br>102<br>104<br>104<br>104<br>105                                                                                            |

| 11. | 10.4<br>. <b>Med</b><br>11.1<br>11.2 | 10.2.2       CONTRAST register         10.2.3       Output Registers         LCD Waveform examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 93<br>94<br>95<br>97<br>97<br>99<br>                                                                                                                                                |

| 11. | 10.4<br>. <b>Med</b><br>11.1<br>11.2 | 10.2.2       CONTRAST register         10.2.3       Output Registers         LCD Waveform examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 93<br>94<br>95<br>97<br>97<br>99<br>100<br>102<br>102<br>102<br>104<br>104<br>105<br>107<br>109                                                                                     |

| 11. | 10.4<br>. <b>Med</b><br>11.1<br>11.2 | <ul> <li>10.2.2 CONTRAST register</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 93<br>94<br>95<br>97<br>97<br>99<br>100<br>100<br>102<br>104<br>104<br>104<br>105<br>107<br>109<br>111                                                                              |

| 11. | 10.4<br>. <b>Med</b><br>11.1<br>11.2 | <ul> <li>10.2.2 CONTRAST register</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 93<br>94<br>95<br>97<br>97<br>99<br>100<br>100<br>102<br>104<br>104<br>104<br>105<br>107<br>109<br>111<br>112                                                                       |

| 11. | 10.4<br>. <b>Med</b><br>11.1<br>11.2 | <ul> <li>10.2.2 CONTRAST register</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 93<br>94<br>95<br>97<br>97<br>99<br>100<br>100<br>102<br>104<br>104<br>104<br>105<br>107<br>109<br>111<br>112<br>113                                                                |

| 11. | 10.4<br>. <b>Med</b><br>11.1<br>11.2 | <ul> <li>10.2.2 CONTRAST register</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 93<br>94<br>95<br>97<br>97<br>99<br>100<br>100<br>102<br>104<br>104<br>104<br>105<br>107<br>109<br>111<br>112<br>113<br>114                                                         |

| 11. | 10.4<br>. <b>Med</b><br>11.1<br>11.2 | <ul> <li>10.2.2 CONTRAST register</li> <li>10.2.3 Output Registers</li> <li>LCD Waveform examples</li> <li>10.3.1 Operation mode 1: 1/8 duty multiplexed</li> <li>10.3.2 Operation mode 2: ¼ duty multiplexed</li> <li>LCD seven segment example description</li> </ul> <b>Jia Access Layer</b> Packet Encapsulation MAC Architecture MAC Configuration Registers 11.3.1 CTRL register 11.3.2 FLAGS1 register 11.3.3 FLAGS2 register 11.3.4 DATA register 11.3.5 TH_PREAM register 11.3.6 TH_HEADER register 11.3.7 BAUDRATE register                                                                                                 | 93<br>94<br>95<br>97<br>97<br>99<br>97<br>99<br>100<br>102<br>102<br>102<br>102<br>102<br>104<br>104<br>104<br>105<br>107<br>109<br>111<br>112<br>113<br>114<br>115                 |

| 11. | 10.4<br>. <b>Med</b><br>11.1<br>11.2 | <ul> <li>10.2.2 CONTRAST register</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 93<br>94<br>95<br>97<br>97<br>99<br>100<br>100<br>102<br>102<br>104<br>104<br>104<br>105<br>107<br>109<br>111<br>112<br>113<br>114<br>115<br>116                                    |

| 11. | 10.4<br>. <b>Med</b><br>11.1<br>11.2 | <ul> <li>10.2.2 CONTRAST register</li> <li>10.2.3 Output Registers</li> <li>LCD Waveform examples</li> <li>10.3.1 Operation mode 1: 1/8 duty multiplexed</li> <li>10.3.2 Operation mode 2: ¼ duty multiplexed</li> <li>LCD seven segment example description</li> </ul> <b>Jia Access Layer</b> Packet Encapsulation MAC Configuration Registers 11.3.1 CTRL register 11.3.2 FLAGS1 register 11.3.3 FLAGS2 register 11.3.4 DATA register 11.3.5 TH_PREAM register 11.3.6 TH_HEADER register 11.3.7 BAUDRATE register 11.3.8 TRACK register 11.3.9 PREAM register 11.3.10 CTRL2 register 11.3.10 CTRL2 register 11.3.10 CTRL2 register | 93<br>94<br>95<br>97<br>97<br>99<br>100<br>100<br>102<br>102<br>104<br>104<br>104<br>105<br>107<br>109<br>111<br>112<br>113<br>114<br>115<br>116<br>117<br>118                      |

| 11. | 10.4<br>. <b>Med</b><br>11.1<br>11.2 | 10.2.2       CONTRAST register         10.2.3       Output Registers         LCD Waveform examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 93<br>94<br>95<br>97<br>97<br>99<br>100<br>100<br>102<br>102<br>104<br>104<br>104<br>105<br>107<br>109<br>111<br>112<br>113<br>114<br>115<br>116<br>117<br>118<br>119               |

| 11. | 10.4<br>. <b>Med</b><br>11.1<br>11.2 | <ul> <li>10.2.2 CONTRAST register</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 93<br>94<br>95<br>97<br>97<br>99<br>100<br>102<br>102<br>104<br>104<br>104<br>105<br>107<br>109<br>111<br>112<br>113<br>114<br>115<br>116<br>117<br>118<br>119<br>120               |

| 11  | 10.4<br>. <b>Med</b><br>11.1<br>11.2 | 10.2.2       CONTRAST register         10.2.3       Output Registers         LCD Waveform examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 93<br>94<br>95<br>97<br>97<br>99<br>100<br>102<br>102<br>104<br>104<br>104<br>104<br>105<br>107<br>109<br>111<br>112<br>113<br>114<br>115<br>116<br>117<br>118<br>119<br>120<br>121 |

|     | 11.4  | Operatio         | ation modes                             |     |  |  |  |

|-----|-------|------------------|-----------------------------------------|-----|--|--|--|

|     |       | 11.4.2           | BYPASS mode                             |     |  |  |  |

|     |       | 11.4.3           | WHD mode                                |     |  |  |  |

|     |       | 11.4.4           | BYTE mode                               |     |  |  |  |

|     |       | 11.4.5           | FEC mode                                |     |  |  |  |

|     |       | 11.4.6           | VTB mode                                |     |  |  |  |

|     |       | 11.4.7           | FCS mode                                |     |  |  |  |

|     |       | 11.4.8           | NULL mode                               |     |  |  |  |

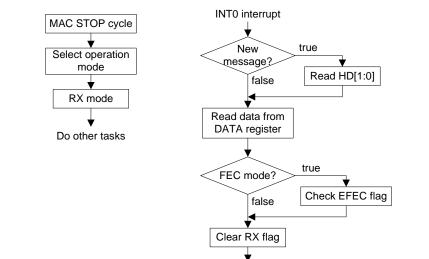

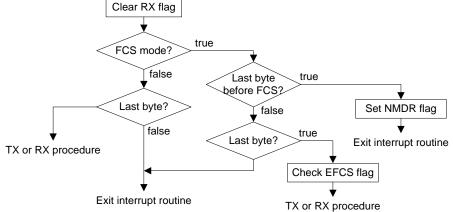

|     | 11.5  |                  | on Procedures                           |     |  |  |  |

|     |       | 11.5.1           | STOP cycle                              |     |  |  |  |

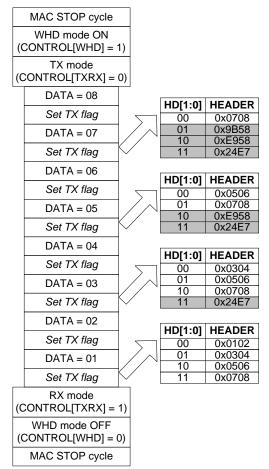

|     |       | 11.5.2           | WHD mode operation procedure            |     |  |  |  |

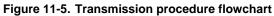

|     |       | 11.5.3           | Transmission procedure                  | 125 |  |  |  |

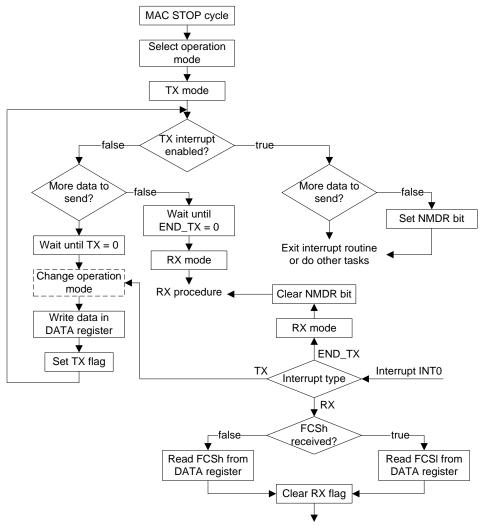

|     |       | 11.5.4           | Reception procedure                     | 127 |  |  |  |

| 12  | PLC   | Modem            | ۱ 1                                     | 129 |  |  |  |

| 12. |       |                  |                                         |     |  |  |  |

|     | 12.1  |                  | Frequencies and frequency coding        |     |  |  |  |

|     | 12.2  |                  | Transmission and Reception              |     |  |  |  |

|     |       | 12.2.1           | Transmission characteristics            |     |  |  |  |

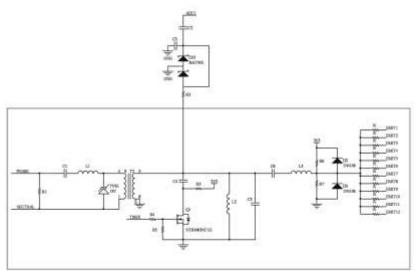

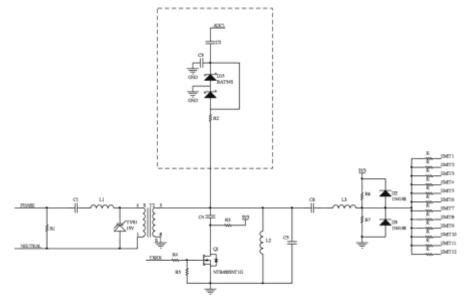

|     |       |                  | 12.2.1.1 High Performance configuration |     |  |  |  |

|     |       | 10.0.0           | 12.2.1.2 Direct configuration           |     |  |  |  |

|     |       | 12.2.2           | Reception characteristics               |     |  |  |  |

|     | 40.0  | 12.2.3           | Carrier Detection                       |     |  |  |  |

|     | 12.3  |                  | dem Configuration registers             |     |  |  |  |

|     |       | 12.3.1           | CD_CONTROL register                     |     |  |  |  |

|     |       | 12.3.2           | THRESHOLD registers                     |     |  |  |  |

|     |       | 12.3.3           | GAIN register                           |     |  |  |  |

|     |       | 12.3.4           | CONTROL2 register                       |     |  |  |  |

|     |       | 12.3.5           | FREQ register                           |     |  |  |  |

|     |       | 12.3.6           | CONFIG register                         |     |  |  |  |

|     |       | 12.3.7<br>12.3.8 | GFSK_ADDR register                      |     |  |  |  |

|     |       | 12.3.0           | GFSK_DX registers                       |     |  |  |  |

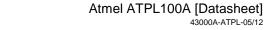

|     |       |                  | COMP register<br>VSENSE_CONFIG register |     |  |  |  |

|     |       |                  | VINIT register                          |     |  |  |  |

|     |       |                  | VMAX register                           |     |  |  |  |

|     |       |                  | TTRANS register                         |     |  |  |  |

|     |       |                  | STEP register                           |     |  |  |  |

|     |       |                  | TRISE register                          |     |  |  |  |

|     |       |                  | TFALL register                          |     |  |  |  |

|     |       |                  | SECRATE register                        |     |  |  |  |

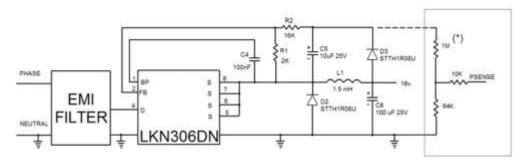

|     |       |                  | VFAIL register                          |     |  |  |  |

|     |       |                  | SECLEVEL register                       |     |  |  |  |

|     |       |                  | MAXAMP register                         |     |  |  |  |

|     |       |                  | POT_BF registers                        |     |  |  |  |

|     |       |                  | MAXPOT registers                        |     |  |  |  |

|     |       | 12.3.23          | NUMCYCLES register                      | 162 |  |  |  |

|     |       | 12.3.24          | ALFA_NUMMILIS register                  | 163 |  |  |  |

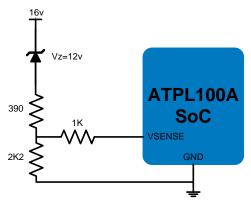

|     |       |                  | PSENSECYCLES registers                  |     |  |  |  |

|     |       |                  | MEAN registers                          |     |  |  |  |

|     |       | 12.3.27          | PMAX registers                          | 166 |  |  |  |

|     |       |                  | KNX_EN register                         |     |  |  |  |

|     |       |                  | CD_ENABLE register                      |     |  |  |  |

|     |       | 12.3.30          | CD_DECISION_TIME register               | 169 |  |  |  |

|     |       |                  | CD_DECISION_ERROR register              |     |  |  |  |

|     |       |                  | TXRX_CTL register                       |     |  |  |  |

|     |       | 12.3.33          | Ri registers                            | 172 |  |  |  |

| 13. | Elect | rical Ch         | naracteristics1                         | 73  |  |  |  |

|     | 13.1  |                  | e Maximum Ratings                       |     |  |  |  |

|     | 13.1  |                  | nended Operating Conditions             |     |  |  |  |

|     |       |                  | racteristics                            |     |  |  |  |

|     | 13.3  |                  |                                         |     |  |  |  |

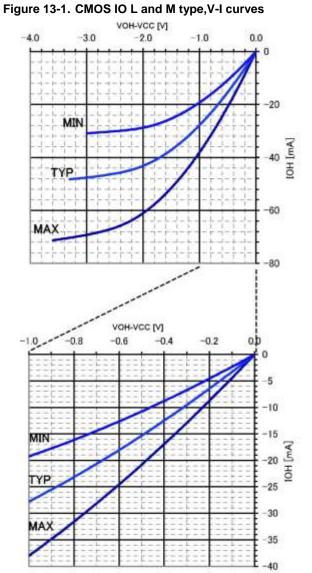

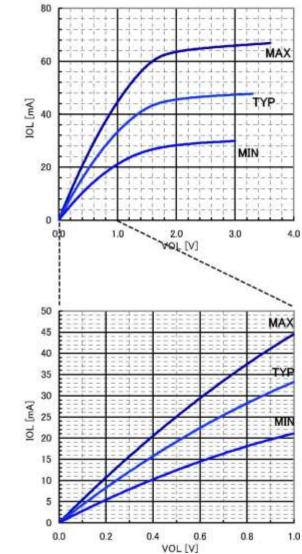

|     |       | 13.3.2           | V-I curves                              | 1/6 |  |  |  |

|     | 13.5<br>13.6                       | Power Consumption<br>Thermal Data<br>Oscillator<br>Power on |     |  |  |  |

|-----|------------------------------------|-------------------------------------------------------------|-----|--|--|--|

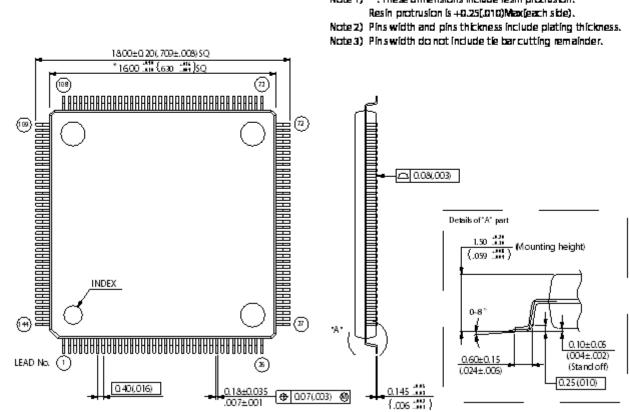

| 14. | Mech                               | nanical Characteristics                                     | 183 |  |  |  |

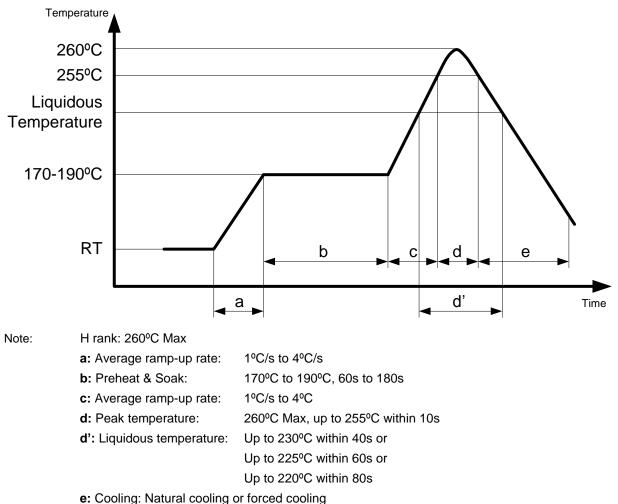

| 15. | 5. Recommended mounting conditions |                                                             |     |  |  |  |

|     | 15.1                               | Conditions of Standard Reflow                               |     |  |  |  |

|     |                                    | Manual Soldering                                            |     |  |  |  |

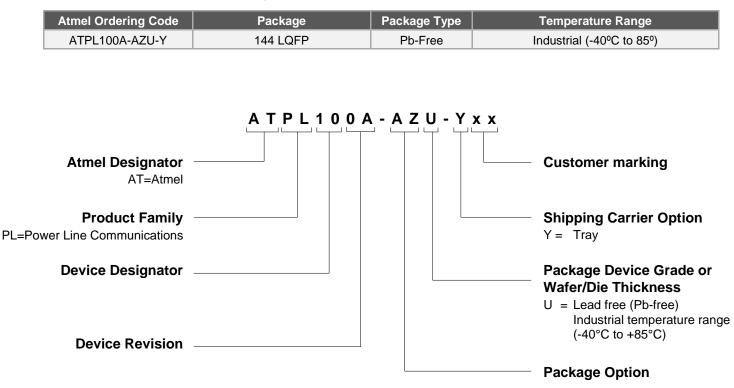

| 16. | 6. Ordering Information            |                                                             |     |  |  |  |

| 17. | 7. Revision History 187            |                                                             |     |  |  |  |

|     |                                    |                                                             |     |  |  |  |

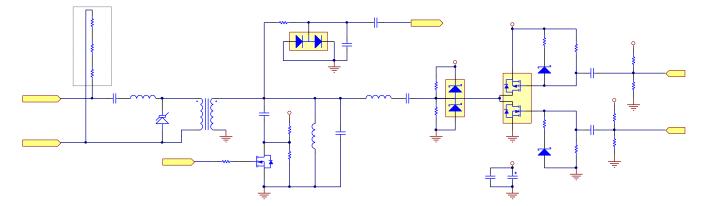

# 1. Block Diagram

# 2. Package and Pinout

# 2.1 144-Lead LQFP Package Outline

Figure 2-1. Orientation of the 144-Lead Package

# 2.2 144-Lead LQFP Pinout

Table 2-1. ATPL100A 144-Lead LQFP pinout

| PinNo  | Pin Name        | I/O | l(mA) | Res | HY |

|--------|-----------------|-----|-------|-----|----|

| 1      | P3_3/INT1       | I/O | ±5    | PU  | -  |

| 2      | VCC             | Р   | -     | -   | -  |

| 3      | GND             | Р   | -     | -   | -  |

| 4      | GND             | Р   | -     | -   | -  |

| 5      | GND             | Р   | -     | -   | -  |

| 6      | TDI             | I   | ±5    | PU  | -  |

| 7      | TDO             | 0   | ±5    | -   | -  |

| 8      | 8 TCK           |     | ±5    | -   | -  |

| 9      | TMS             | Ι   | ±5    | PU  | -  |

| 10     | TRST            | Ι   | ±5    | PU  | -  |

| 11     | D_INIT          | Ι   | ±5    | PD  | Y  |

| 12     | RSTA            | Ι   | ±5    | PD  | Y  |

| 13     | /PROG           | I   | ±5    | PU  | Y  |

| 14     | SECURED         | I   | ±5    | PD  | Y  |

| 15     | /EWDG           | I   | ±5    | PD  | Y  |

| 16     | DEBUG           | Ι   | ±5    | PD  | Y  |

| 17     | 17 VCC          |     | -     | -   | -  |

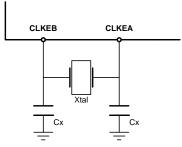

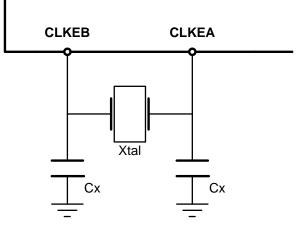

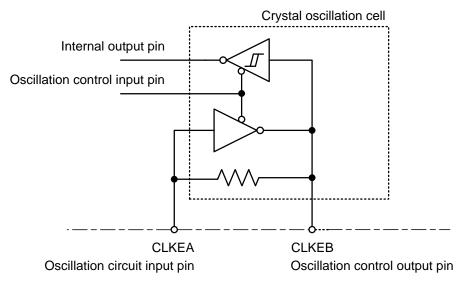

| 18     | CLKEB           | I/O | -     | -   | -  |

| 19     | GND             | Р   | -     | -   | -  |

| 20     | CLKEA           | Ι   | -     | -   | -  |

| 21     | VCC             | Р   | -     | -   | -  |

| 22 GND |                 | Р   | -     | -   | -  |

| 23 GND |                 | Р   | -     | -   | -  |

| 24     | 24 VDE0 P       |     | -     | -   | -  |

| 25     | VDE0            | Р   | -     | -   | -  |

| 26     | VSS0            | Р   | -     | -   | -  |

| 27     | LDO_PD          | I   |       |     |    |

| 28     | VDD             | Р   | -     | -   | -  |

| 29     | GND             | Р   | -     | -   | -  |

| 30     | VCC             | Р   | -     | -   | -  |

| 31     | VSENSE          | I   | ±5    | -   | Y  |

| 32     | PSENSE          | I   | ±5    | -   | Y  |

| 33     | VNR             | I   | ±5    | -   | Y  |

| 34     | TRIAC_3         | 0   | ±5    | -   | -  |

| 35     | TRIAC_2         | 0   | ±5    | -   | -  |

| 36     | TRIAC_1         | 0   | ±5    | -   | -  |

| 37     | TRIAC_0         | 0   | ±5    | -   | -  |

| 38     | P5_5/TXD1/INTA1 | I/O | ±5    | PU  | -  |

| PinNo | Pin Name           | I/O | l(mA) | Res | HY |

|-------|--------------------|-----|-------|-----|----|

| 39    | P5_4/RXD1/INTA0    | I/O | ±5    | PU  | -  |

| 40    | P4_7/T2EX/INTA3    | I/O | ±5    | PU  | -  |

| 41    | P4_6/T2/INTA2      | I/O | ±5    | PU  | -  |

| 42    | P1_7/SSN           | I/O | ±5    | PU  | -  |

| 43    | 43 VCC             |     | -     | -   | -  |

| 44    | GND                | Р   | -     | -   | -  |

| 45    | EMIT_0             | 0   | ±Χ    | -   | -  |

| 46    | EMIT_1             | 0   | ±Χ    | -   | -  |

| 47    | EMIT_2             | 0   | ±Χ    | -   | -  |

| 48    | VCC                | Р   | -     | -   | -  |

| 49    | GND                | Р   | -     | -   | -  |

| 50    | EMIT_3             | 0   | ±Χ    | -   | -  |

| 51    | EMIT_4             | 0   | ±Χ    | -   | -  |

| 52    | EMIT_5             | 0   | ±Χ    | -   | -  |

| 53    | EMIT_6             | 0   | ±Χ    | -   | -  |

| 54    | VCC                | Р   | -     | -   | -  |

| 55    | 55 GND             |     | -     | -   | -  |

| 56    | 56 EMIT_7          |     | ±Χ    | -   | -  |

| 57    | 57 EMIT_8          |     | ±Χ    | -   | -  |

| 58    | EMIT_9             | 0   | ±Χ    | -   | -  |

| 59    | EMIT_10            | 0   | ±Χ    | -   | -  |

| 60    | 60 VCC             |     | -     | -   | -  |

| 61    | GND                | Р   | -     | -   | -  |

| 62    | EMIT_11            | 0   | ±Χ    | -   | -  |

| 63    | EMIT_12            | 0   | ±Χ    | -   | -  |

| 64    | VCC                | Р   | -     | -   | -  |

| 65    | GND                | Р   | -     | -   | -  |

| 66    | P3_1/TXD0          | I/O | ±5    | PU  | -  |

| 67    | P3_0/RXD0          | I/O | ±5    | PU  | -  |

| 68    | P4_5/MISO1/INTB3   | I/O | ±5    | PU  | -  |

| 69    | P4_4/MOSI1/INTB2   | I/O | ±5    | PU  | -  |

| 70    | P4_3/SPICLK1/INTB1 | I/O | ±5    | PU  | -  |

| 71    | P4_2/SS1/INTB0     | I/O | ±5    | PU  | -  |

| 72    | P4_1/TXD2          | I/O | ±5    | PU  | -  |

| 73    | P4_0/RXD2          | I/O | ±5    | PU  | -  |

| 74    | VCC                | Р   | -     | -   | -  |

| 75    | GND                | Р   | -     | -   | -  |

| 76    | SEGM_23/INTC3      | I/O | ±5    | -   | -  |

| PinNo | Pin Name                 | I/O | l(mA) | Res | HY  |

|-------|--------------------------|-----|-------|-----|-----|

| 77    | SEGM_22/INTC2            | I/O | ±5    | -   | -   |

| 78    | SEGM_21/INTC1            | I/O | ±5    | -   | -   |

| 79    | SEGM_20/INTC0            | I/O | ±5    | -   | -   |

| 80    | SEGM_19                  | 0   | ±5    | -   | -   |

| 81    | SEGM_18                  | 0   | ±5    | -   | -   |

| 82    | 82 SEGM_17               |     | ±5    | -   | -   |

| 83    | 83 SEGM_16               |     | ±5    | -   | -   |

| 84    | SEGM_15                  | 0   | ±5    | -   | -   |

| 85    | SEGM_14                  | 0   | ±5    | -   | -   |

| 86    | SEGM_13                  | 0   | ±5    | -   | -   |

| 87    | SEGM_12                  | 0   | ±5    | -   | -   |

| 88    | SEGM_11                  | 0   | ±5    | -   | -   |

| 89    | VDD                      | Р   | -     | -   | -   |

| 90    | VCC                      | Р   | -     | -   | -   |

| 91    | 91 GND                   |     | -     | -   | -   |

| 92    | 92 SEGM_10               |     | ±5    | -   | -   |

| 93    | SEGM_9                   | 0   | ±5    | -   | -   |

| 94    | 94 SEGM_8                |     | ±5    | -   | -   |

| 95    | 95 SEGM_7                |     | ±5    | -   | -   |

| 96    | SEGM_6                   | 0   | ±5    | -   | -   |

| 97    | SEGM_5                   | 0   | ±5    | -   | -   |

| 98    | SEGM_4                   | 0   | ±5    | -   | -   |

| 99    | SEGM_3                   | 0   | ±5    | -   | -   |

| 100   | SEGM_2                   | 0   | ±5    | -   | -   |

| 101   | SEGM_1                   | 0   | ±5    | -   | -   |

| 102   | SEGM_0                   | 0   | ±5    | -   | -   |

| 103   | VCC                      | Р   | -     | -   | -   |

| 104   | GND                      | Р   | -     | -   | - ] |

| 105   | BCKP_7/SEGM_27<br>/INTD3 | I/O | ±5    | -   | -   |

| 106   | BCKP_6/SEGM_26<br>/INTD2 | I/O | ±5    | -   | -   |

| 107   | BCKP_5/SEGM_25<br>/INTD1 | I/O | ±5    | -   | -   |

| 108   | BCKP_4/SEGM_24<br>/INTD0 | I/O | ±5    | -   | -   |

| 109   | BCKP_3                   | 0   | ±5    | -   | -   |

| 110   | BCKP_2                   | 0   | ±5    | -   | -   |

| 111   | BCKP_1                   | 0   | ±5    | -   | -   |

| Table 2-1. | ATPL100A 144-Lead LQFP pinout (Continued) |

|------------|-------------------------------------------|

|------------|-------------------------------------------|

| PinNo | Pin Name       | I/O | l(mA) | Res | HY |

|-------|----------------|-----|-------|-----|----|

| 112   | BCKP_0         | 0   | ±5    | -   | -  |

| 113   | GND            | Р   | -     | -   | -  |

| 114   | DC_COMP        | 0   | ±10   | -   | -  |

| 115   | VCC            | Р   | -     | -   | -  |

| 116   | 116 ENABLE     |     | ±10   | -   | -  |

| 117   | GND            | Р   | -     | -   | -  |

| 118   | DNIN           | I   | ±5    | -   | -  |

| 119   | DIN            | I   | ±5    | -   | -  |

| 120   | REC_1          | 0   | ±5    | -   | -  |

| 121   | REC_2          | 0   | ±5    | -   | -  |

| 122   | REC_3          | 0   | ±5    | -   | -  |

| 123   | REC_4          | 0   | ±5    | -   | -  |

| 124   | REC_5          | 0   | ±5    | -   | -  |

| 125   | REC_6          | 0   | ±5    | -   | -  |

| 126   | 126 REC_7      |     | ±5    | -   | -  |

| 127   | REC_8          | 0   | ±5    | -   | -  |

| 128   | 128 VCC        |     | -     | -   | -  |

| 129   | <b>129</b> GND |     | -     | -   | -  |

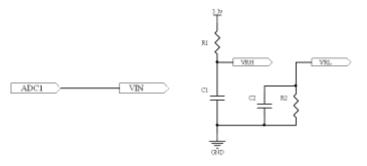

| 130   | 130 VRL        |     | (**)  | -   | -  |

| 131   | 131 VIN        |     | (**)  | -   | -  |

| 132   | 132 VRH        |     | (**)  | -   | -  |

| 133   | AVD1           | Р   | -     | -   | -  |

| 134   | AVS1           | Р   | -     | -   | -  |

| 135   | AVD2           | Р   | -     | -   | -  |

| 136   | AVS2           | Р   | -     | -   | -  |

| 137   | VCC            | Р   | -     | -   | -  |

| 138   | GND            | Р   | -     | -   | -  |

| 139   | P5_3/MISO0     | I/O | ±5    | PU  | -  |

| 140   | P5_2/MOSI0     | I/O | ±5    | PU  | -  |

| 141   | P5_1/SPICLK0   | I/O | ±5    | PU  | -  |

| 142   | P5_0/SS0       | I/O | ±5    | PU  | -  |

| 143   | P3_5/T1        | I/O | ±5    | PU  | -  |

| 144   | P3_4/T0        | I/O | ±5    | PU  | -  |

Notes: 1. Mandatory to be tied down

**I/O**=pin direction:

I=input, O=Output, P=Power

I(mA)=nominal current: +=source, -=sink, X=fixed by external resistor

RES=pin pullup/pulldown resistor: PU=pullup, PD=pulldown;

Atmel ATPL100A [Datasheet] 10 43000A-ATPL-05/12

HY=Input Hysteresis

# 3. Pin Description

### Table 3-1.Pin Description List

| Pin Number                                                                               | Pin Name            | Туре         | Comments                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------|---------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                          |                     |              | Microcontroller port 3.3 / External Interrupt 1                                                                                                                                                                          |

| 1                                                                                        | P3.3/INT1           | I/O          | <ul> <li>When configured as P3.3, this pin is a pseudo-<br/>bidirectional microcontroller I/O port</li> </ul>                                                                                                            |

| ı                                                                                        | 1 3.3/1011          | 1/0          | <ul> <li>When configured as INT1, this pin is the 8051C3A<br/>microcontroller external interrupt 1</li> </ul>                                                                                                            |

|                                                                                          |                     |              | <ul> <li>Internal configuration: 33kΩ typ. pull-up resistor</li> </ul>                                                                                                                                                   |

| 2, 17, 21, 30, 43,<br>48, 54, 60, 64,<br>74, 90, 103, 115,<br>128, 137                   | VCC                 | Power        | 3.3v digital supply. Digital power supply must be decoupled by external capacitors                                                                                                                                       |

| 3, 4, 5, 19, 22,<br>23, 29, 44, 49,<br>55, 61, 65, 75,<br>91, 104, 113,<br>117, 129, 138 | GND                 | Power        | Digital ground                                                                                                                                                                                                           |

| 6                                                                                        | TDI <sup>(1)</sup>  | Input        | <ul> <li>Test Data In</li> <li>Internal configuration: 33kΩ typ. pull-up resistor</li> </ul>                                                                                                                             |

| 7                                                                                        | TDO <sup>(1)</sup>  | Output       | Test Data out                                                                                                                                                                                                            |

| 8                                                                                        | TCK <sup>(1)</sup>  | Input        | Test Clock                                                                                                                                                                                                               |

| 9                                                                                        | TMS <sup>(1)</sup>  | Input        | <ul> <li>Test Mode Select</li> <li>Internal configuration: 33kΩ typ. pull-up resistor</li> </ul>                                                                                                                         |

| 10                                                                                       | TRST <sup>(1)</sup> | Input        | Test Reset<br>Internal configuration: 33kΩ typ. pull-up resistor                                                                                                                                                         |

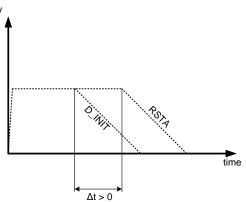

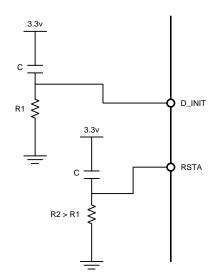

|                                                                                          |                     |              | Initialization Signal                                                                                                                                                                                                    |

| 11                                                                                       | D_INIT              | D_INIT Input | <ul> <li>During power-on, D_INIT should be released before<br/>asynchronous reset signal RSTA, in order to ensure<br/>proper system start up. Not minimum time is required<br/>between both releases, ∆t&gt;0</li> </ul> |

|                                                                                          |                     |              | <ul> <li>D_INIT is active high</li> </ul>                                                                                                                                                                                |

|                                                                                          |                     |              | <ul> <li>Internal configuration: 33kΩ typ. pull-down resistor</li> </ul>                                                                                                                                                 |

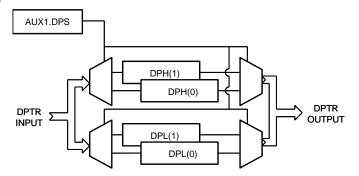

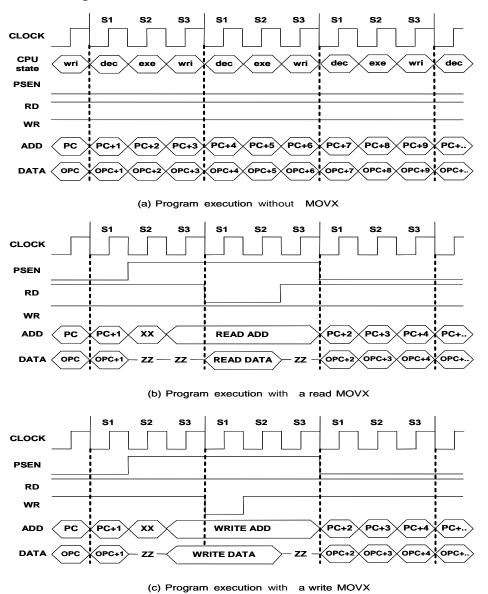

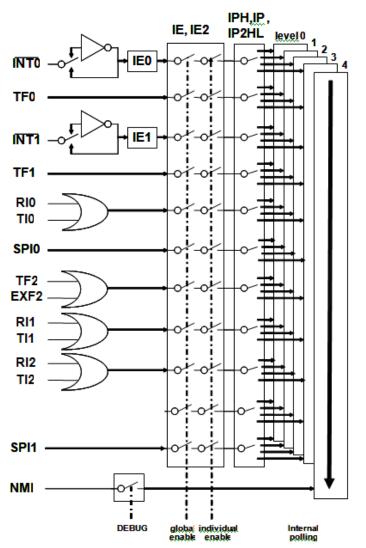

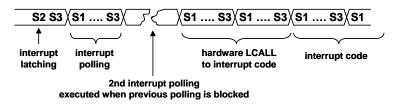

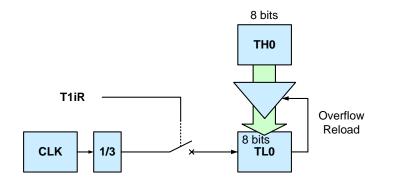

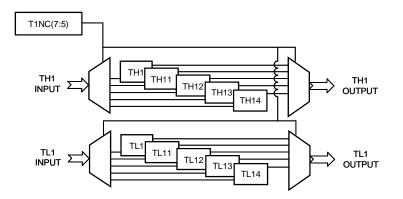

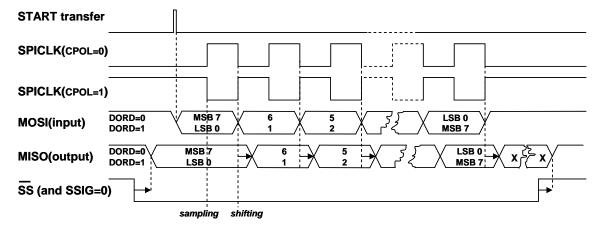

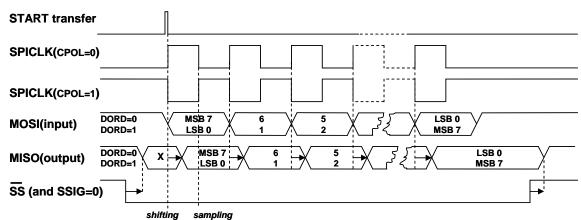

|                                                                                          |                     |              | Asynchronous reset                                                                                                                                                                                                       |