# Please note that Cypress is an Infineon Technologies Company.

The document following this cover page is marked as "Cypress" document as this is the company that originally developed the product. Please note that Infineon will continue to offer the product to new and existing customers as part of the Infineon product portfolio.

# **Continuity of document content**

The fact that Infineon offers the following product as part of the Infineon product portfolio does not lead to any changes to this document. Future revisions will occur when appropriate, and any changes will be set out on the document history page.

# **Continuity of ordering part numbers**

Infineon continues to support existing part numbers. Please continue to use the ordering part numbers listed in the datasheet for ordering.

www.infineon.com

# EZ-USB® FX3S SuperSpeed USB Controller

### **Features**

- Universal serial bus (USB) integration

- □ USB 3.0 and USB 2.0 peripherals compliant with USB 3.0 specification 1.0

- □ 5-Gbps USB 3.0 PHY compliant with PIPE 3.0

- □ High-speed On-The-Go (HS-OTG) host and peripheral compliant with OTG Supplement Version 2.0

- ☐ Thirty-two physical endpoints

- General Programmable Interface (GPIF™ II)

- □ Programmable 100-MHz GPIF II enables connectivity to a wide range of external devices

- □ 8- and 16-bit data bus

- □ As many as 16 configurable control signals

- Mass storage support

- □ SD 3.0 (SDXC) UHS-1

- □ eMMC 4.41

- Two ports that can support memory card sizes up to 2TB

- Built-in RAID with support for RAID0 and RAID1

- System I/O expansion with two secure digital I/O (SDIO 3.0) ports

- Support for USB-attached storage (UAS), mass-storage class (MSC), human interface device (HID), full, and Turbo-MTP™

- Fully accessible 32-bit CPU

- □ ARM926EJ core with 200-MHz operation

- □ 512-KB or 256-KB embedded SRAM

- Additional connectivity to the following peripherals

- □ I<sup>2</sup>C master controller at 1 MHz

- □ I2S master (transmitter only) at sampling frequencies of 8 kHz, 16 kHz, 32 kHz, 44.1 kHz, 96 kHz and 192 kHz

- UART support of up to 4 Mbps

- □ SPI master at 33 MHz

- Selectable clock input frequencies

- □ 19.2, 26, 38.4, and 52 MHz

- □ 19.2-MHz crystal input support

- Ultra low-power in core power-down mode

- □ Less than 60 µA with VBATT on

- □ 20 µA with VBATT off

- Independent power domains for core and I/O

- □ Core operation at 1.2 V

- □ I2S, UART, and SPI operation at 1.8 to 3.3 V

- □ I<sup>2</sup>C operation at 1.2 V

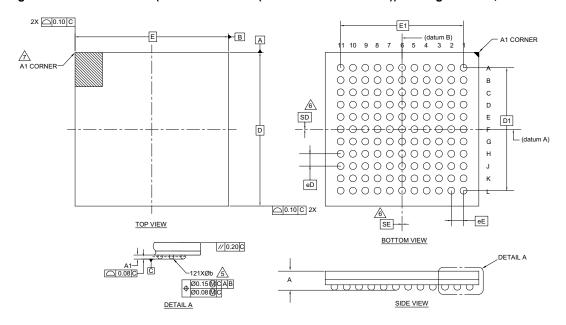

- 10-mm × 10-mm, 0.8-mm pitch Pb-free ball grid array (BGA) package

- EZ-USB<sup>®</sup> software and development kit (DVK) for easy code development

## **Applications**

- Digital video camcorders

- Digital still cameras

- Printers

- Scanners

- Video capture cards

- Test and measurement equipment

- Surveillance cameras

- Personal navigation devices

- Medical imaging devices

- Video IP phones

- Portable media players

- Industrial cameras

- RAID controller

- USB Disk on Module

# **Functional Description**

For a complete list of related resources, click here.

# **Logic Block Diagram**

### More Information

Cypress provides a wealth of data at www.cypress.com to help you to select the right product> device for your design, and to help you to quickly and effectively integrate the device into your design.

- Overview: USB Portfolio, USB Roadmap

- USB 3.0 Product Selectors: FX3, FX3S, CX3, HX3

- Application notes: Cypress offers a large number of USB application notes covering a broad range of topics, from basic to advanced level. Recommended application notes for getting started with FX3 are:

- □ AN75705 Getting Started with EZ-USB FX3

- □ AN76405 EZ-USB FX3 Boot Options

- □ AN70707 EZ-USB FX3/FX3S Hardware Design Guidelines and Schematic Checklist

- □ AN65974 Designing with the EZ-USB FX3 Slave FIFO Interface

- □ AN75779 How to Implement an Image Sensor Interface with EZ-USB FX3 in a USB Video Class (UVC) Framework

- □ AN86947 Optimizing USB 3.0 Throughput with EZ-USB FX3

- □ AN84868 Configuring an FPGA over USB Using Cypress EZ-USB FX3

- □ AN68829 Slave FIFO Interface for EZ-USB FX3: 5-Bit Address Mode

- □ AN73609 EZ-USB FX2LP/ FX3 Developing Bulk-Loop Example on Linux

- □ AN77960 Introduction to EZ-USB FX3 High-Speed USB Host Controller

- AN76348 Differences in Implementation of EZ-USB FX2LP and EZ-USB FX3 Applications

- □ AN89661 USB RAID 1 Disk Design Using EZ-USB FX3S

- Code Examples:

- □ USB Hi-Speed

- USB Full-Speed

- □ USB SuperSpeed

- Technical Reference Manual (TRM):

- □ EZ-USB FX3 Technical Reference Manual

- Development Kits:

- □ CYUSB3KIT-003, EZ-USB FX3 SuperSpeed Explorer Kit

- Models: IBIS

### **EZ-USB FX3 Software Development Kit**

Cypress delivers the complete software and firmware stack for FX3, in order to easily integrate SuperSpeed USB into any embedded application. The Software Development Kit (SDK) comes with tools, drivers and application examples, which help accelerate application development.

### GPIF™ II Designer

The GPIF II Designer is a graphical software that allows designers to configure the GPIF II interface of the EZ-USB FX3 USB 3.0 Device Controller.

The tool allows users the ability to select from one of five Cypress supplied interfaces, or choose to create their own GPIF II interface from scratch. Cypress has supplied industry standard interfaces such as asynchronous and Synchronous Slave FIFO, Asynchronous and Synchronous SRAM, and Asynchronous SRAM. Designers who already have one of these pre-defined interfaces in their system can simply select the interface of choice, choose from a set of standard parameters such as bus width (x8, 16, x32) endianess, clock settings, and compile the interface. The tool has a streamlined three step GPIF interface development process for users who need a customized interface. Users are able to first select their pin configuration and standard parameters. Secondly, they can design a virtual state machine using configurable actions. Finally, users can view output timing to verify that it matches the expected timing. Once the three step process is complete, the interface can be compiled and integrated with FX3.

### **Contents**

| Functional Overview                   | 4        |

|---------------------------------------|----------|

| Application Examples                  |          |

| USB Interface                         | 5        |

| OTG                                   |          |

| ReNumeration                          | 6        |

| VBUS Overvoltage Protection           | 6        |

| Carkit UART Mode                      |          |

| Host Processor Interface (P-Port)     | 7        |

| GPIF II                               |          |

| Slave FIFO Interface                  |          |

| Asynchronous SRAM                     |          |

| Asynchronous Address/Data Multiplexed |          |

| Synchronous ADMux Interface           |          |

| Processor MMC (PMMC) Slave Interface  |          |

| CPU                                   |          |

| Storage Port (S-Port)                 |          |

| SD/MMC Clock Stop                     |          |

| SD_CLK Output Clock Stop              |          |

| Card Insertion and Removal Detection  |          |

| Write Protection (WP)                 |          |

| SDIO InterruptSDIO Read-Wait Feature  |          |

|                                       |          |

| JTAG Interface                        |          |

| Other Interfaces                      |          |

| UART Interface                        |          |

| I2S Interface                         |          |

| SPI Interface                         |          |

| Boot Options                          |          |

| Reset                                 |          |

| Hard Reset                            |          |

| Soft Reset                            |          |

| Clocking                              |          |

| 32-kHz Watchdog Timer Clock Input     | 12<br>12 |

| Power                                 |          |

| Power Modes                           |          |

| Configuration Options                 |          |

| Digital I/Os                          |          |

| <del>-</del>                          |          |

| GPIOs                                 |          |

| System-level ESD                      | 15       |

| Pinouts                                     | 16  |

|---------------------------------------------|-----|

| Pin Description                             | 17  |

| Electrical Specifications                   |     |

| Absolute Maximum Ratings                    |     |

| Operating Conditions                        |     |

| DC Specifications                           |     |

| Thermal Characteristics                     |     |

| AC Timing Parameters                        | 23  |

| GPIF II lines AC characteristics at 100 MHz |     |

| GPIF II PCLK Jitter characteristics         |     |

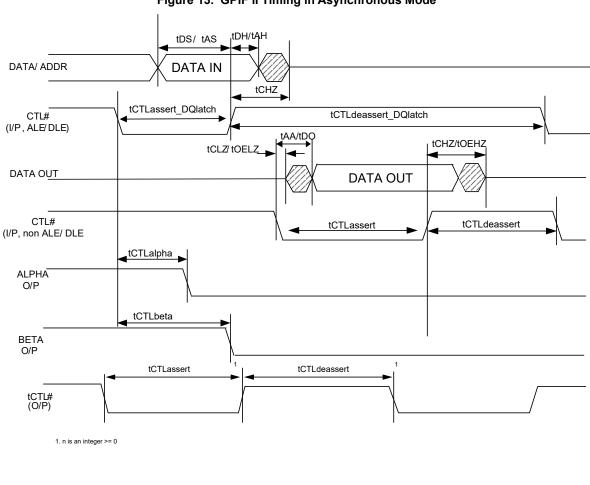

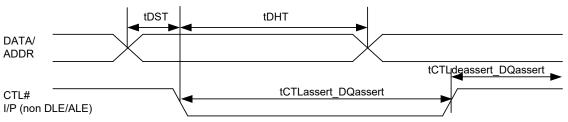

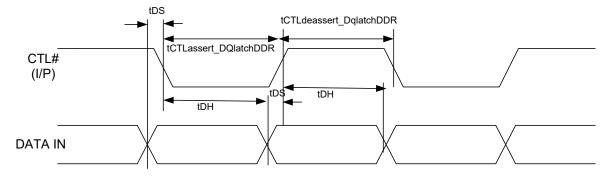

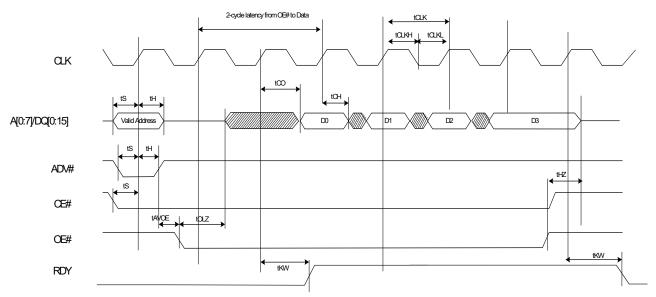

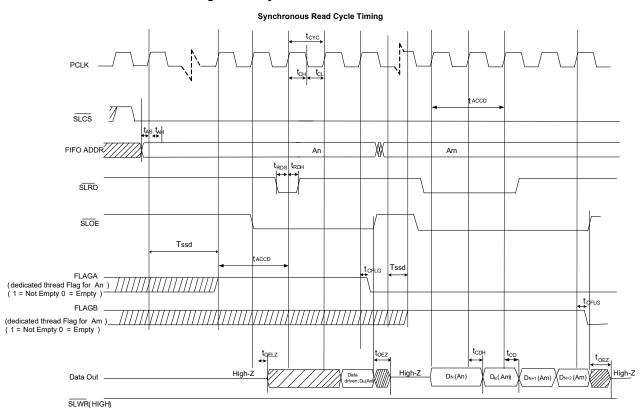

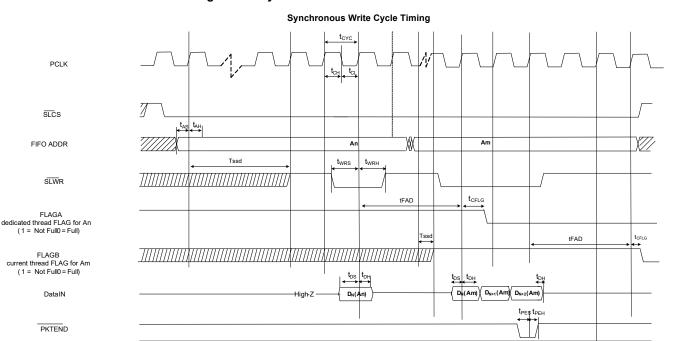

| GPIF II Timing                              | 24  |

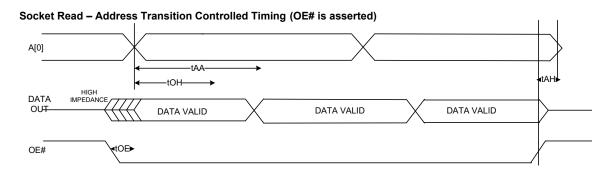

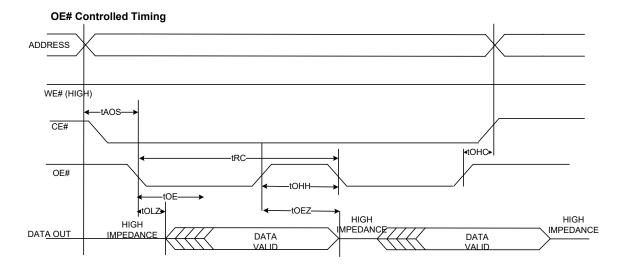

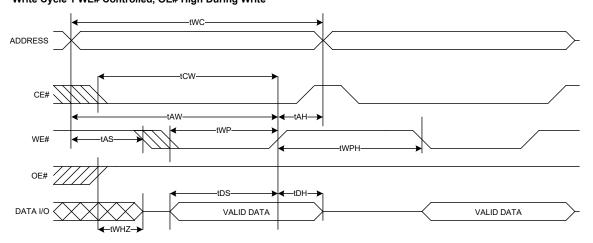

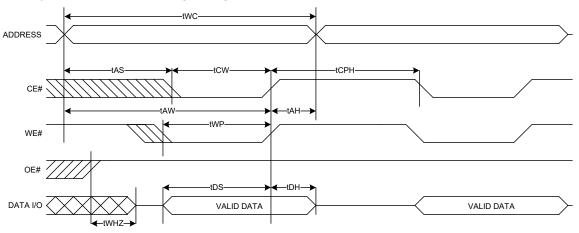

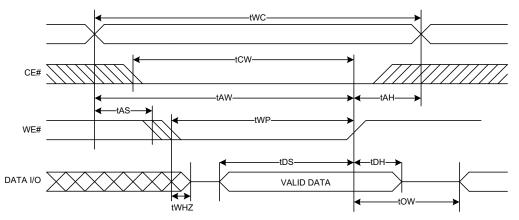

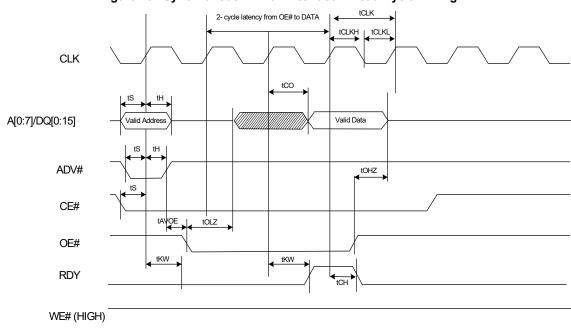

| Asynchronous SRAM Timing                    |     |

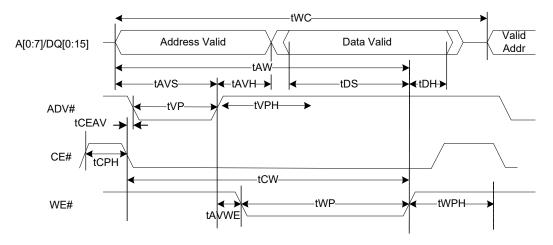

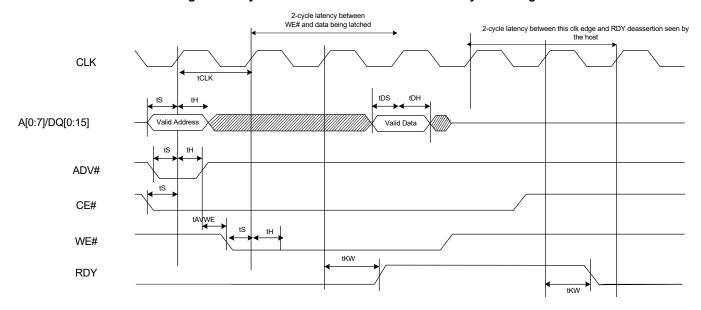

| ADMux Timing for Asynchronous Access        |     |

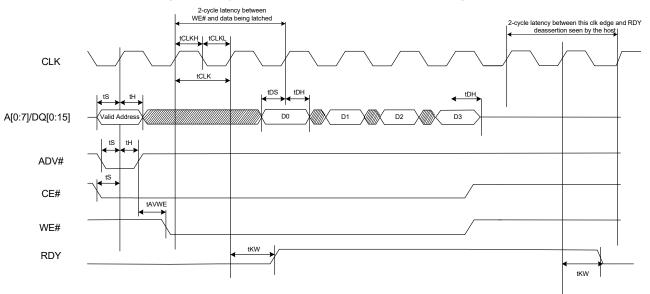

| Synchronous ADMux Timing                    |     |

| Slave FIFO Interface                        | 35  |

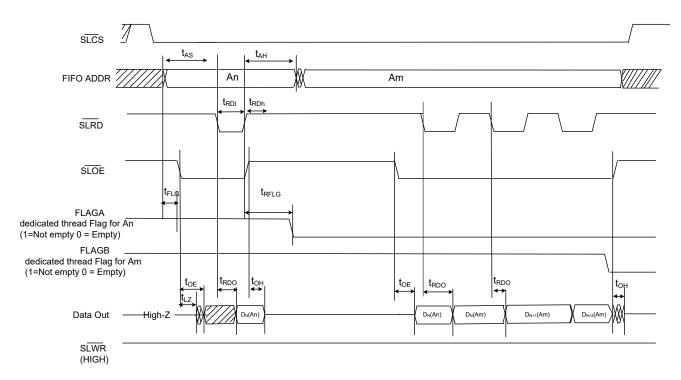

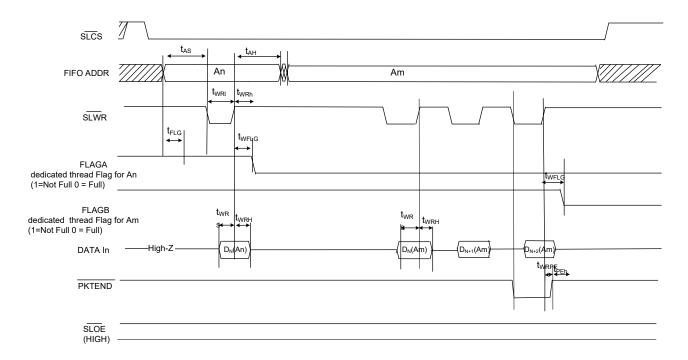

| Asynchronous Slave FIFO                     |     |

| Read Sequence Description                   | 37  |

| Asynchronous Slave FIFO                     |     |

| Write Sequence Description                  |     |

| Storage Port Timing                         |     |

| Serial Peripherals Timing                   |     |

| Reset Sequence                              |     |

| Package Diagram                             | 50  |

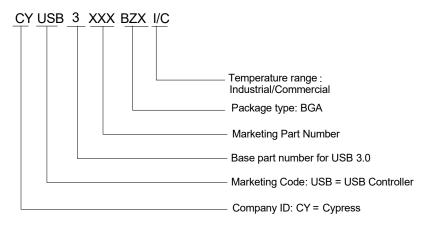

| Ordering Information                        | 51  |

| Ordering Code Definitions                   | 51  |

| Acronyms                                    | 52  |

| Document Conventions                        | 52  |

| Units of Measure                            |     |

| Errata                                      |     |

| Qualification Status                        |     |

| Errata Summary                              |     |

| Document History Page                       |     |

| Sales, Solutions, and Legal Information     |     |

| Worldwide Sales and Design Support          |     |

| Products                                    |     |

| PSoC® Solutions                             |     |

| Cypress Developer Community                 |     |

| Technical Support                           |     |

| 1 001111001 00ppoit                         | 🔾 1 |

### **Functional Overview**

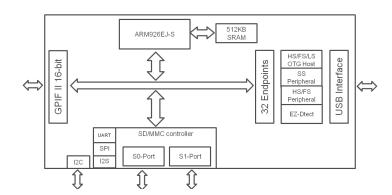

Cypress's EZ-USB FX3S is the next-generation USB 3.0 peripheral controller, providing integrated and flexible features. FX3S has a fully configurable, parallel, general programmable interface called GPIF II, which can connect to any processor, ASIC, or FPGA. GPIF II is an enhanced version of the GPIF in FX2LP, Cypress's flagship USB 2.0 product. It provides easy and glueless connectivity to popular interfaces, such as asynchronous SRAM, asynchronous and synchronous address data multiplexed interfaces, and parallel ATA. FX3S has integrated the USB 3.0 and USB 2.0 physical layers (PHYs) along with a 32-bit ARM926EJ-S microprocessor for powerful data processing and for building custom applications. It implements an architecture that enables 185-MBps data transfer from GPIF II to the USB interface.

FX3S features an integrated storage controller and can support up to two independent mass storage devices on its storage ports. It can support SD 3.0 and eMMC 4.41 memory cards. It can also support SDIO 3.0 on these ports. FX3 has built in RAID with support for RAID 0 and RAID 1 using either SD or eMMC.

An integrated USB 2.0 OTG controller enables applications in which FX3S may serve dual roles; for example, EZ-USB FX3S may function as an OTG Host to MSC as well as HID-class devices. FX3S contains 512 KB or 256 KB of on-chip SRAM for code and data. EZ-USB FX3S also provides interfaces to connect to serial peripherals such as UART, SPI, I<sup>2</sup>C, and I2S. FX3S comes with application development tools. The software development kit comes with application examples for accelerating time to market.

FX3S complies with the USB 3.0 v1.0 specification and is also backward compatible with USB 2.0. It also complies with USB 2.0 OTG Specification v2.0.

### **Application Examples**

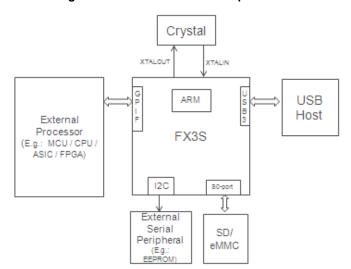

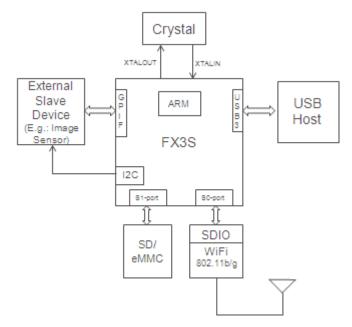

In a typical application (see Figure 1), FX3S functions as a coprocessor and connects to an external processor, which manages system-level functions. Figure 2 shows a typical application diagram when FX3S functions as the main processor.

Figure 1. EZ-USB FX3S as a Coprocessor

#### Note

Document Number: 001-84160 Rev. \*J

<sup>1.</sup> Assuming that GPIF II is configured for a 16-bit data bus (available with certain part numbers; see Ordering Information on page 51), synchronous interface operating at 100 MHz. This number also includes protocol overheads.

Figure 2. EZ-USB FX3S as Main Processor

### **USB** Interface

FX3S complies with the following specifications and supports the following features:

- Supports USB peripheral functionality compliant with the USB 3.0 Specification Revision 1.0 and is also backward compatible with the USB 2.0 Specification.

- Complies with OTG Supplement Revision 2.0. It supports High-Speed, Full-Speed, and Low-Speed OTG dual-role device capability. As a peripheral, FX3S is capable of SuperSpeed, High-Speed, and Full-Speed. As a host, it is capable of High-Speed, Full-Speed, and Low-Speed.

- Supports Carkit Pass-Through UART functionality on USB D+/D- lines based on the CEA-936A specification.

- Supports up to 16 IN and 16 OUT endpoints.

- Supports the USB 3.0 Streams feature. It also supports USB Attached SCSI (UAS) device-class to optimize mass-storage access performance.

- As a USB peripheral, FX3S supports UAS, USB Video Class (UVC), Mass Storage Class (MSC), and Media Transfer Protocol (MTP) USB peripheral classes. As a USB peripheral, all other device classes are supported only in the pass-through mode when handled entirely by a host processor external to the device.

- As an OTG host, FX3S supports MSC and HID device classes. **Note** When the USB port is not in use, disable the PHY and transceiver to save power.

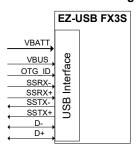

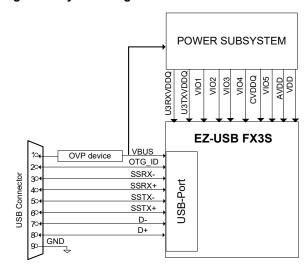

Figure 3. USB Interface Signals

### **OTG**

FX3S is compliant with the OTG Specification Revision 2.0. In the OTG mode, FX3S supports both A and B device modes and supports Control, Interrupt, Bulk, and Isochronous data transfers.

FX3S requires an external charge pump (either standalone or integrated into a PMIC) to power VBUS in the OTG A-device mode.

The Target Peripheral List for OTG host implementation consists of MSC- and HID-class devices.

FX3S does not support Attach Detection Protocol (ADP).

### **OTG Connectivity**

In OTG mode, FX3S can be configured to be an A, B, or dual-role device. It can connect to the following:

- ACA device

- Targeted USB peripheral

- SRP-capable USB peripheral

- HNP-capable USB peripheral

- OTG host

- HNP-capable host

- OTG device

### ReNumeration

Because of FX3S's soft configuration, one chip can take on the identities of multiple distinct USB devices.

When first plugged into USB, FX3S enumerates automatically with the Cypress Vendor ID (0x04B4) and downloads firmware and USB descriptors over the USB interface. The downloaded firmware executes an electrical disconnect and connect. FX3S enumerates again, this time as a device defined by the downloaded information. This patented two-step process, called ReNumeration, happens instantly when the device is plugged in.

### **VBUS Overvoltage Protection**

The maximum input voltage on FX3S's VBUS pin is 6 V. A charger can supply up to 9 V on VBUS. In this case, an external overvoltage protection (OVP) device is required to protect FX3S from damage on VBUS. Figure 4 shows the system application diagram with an OVP device connected on VBUS. Refer to the DC Specifications table for the operating range of VBUS and VBATT.

Figure 4. System Diagram with OVP Device For VBUS

### **Carkit UART Mode**

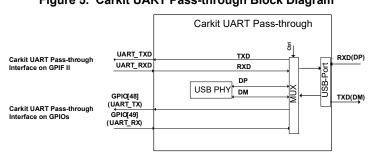

The USB interface supports the Carkit UART mode (UART over D+/D-) for non-USB serial data transfer. This mode is based on the CEA-936A specification.

In the Carkit UART mode, the output signaling voltage is 3.3 V. When configured for the Carkit UART mode, TXD of UART (output) is mapped to the D- line, and RXD of UART (input) is mapped to the D+ line.

In the Carkit UART mode, FX3S disables the USB transceiver and D+ and D- pins serve as pass-through pins to connect to the UART of the host processor. The Carkit UART signals may be routed to the GPIF II interface or to GPIO[48] and GPIO[49], as shown in Figure 5.

In this mode, FX3S supports a rate of up to 9600 bps.

Figure 5. Carkit UART Pass-through Block Diagram

## **Host Processor Interface (P-Port)**

A configurable interface enables FX3S to communicate with various devices such as Sensor, FPGA, Host Processor, or a Bridge chip. FX3S supports the following P-Port interfaces.

- GPIF II (16-bit)

- Slave FIFO Interface

- 16-bit Asynchronous SRAM Interface

- 16-bit Asynchronous address/data multiplexed (ADMux) Interface

- 16-bit Synchronous address/data multiplexed (ADMux) Interface

- Processor MMC slave Interface compatible with MMC System specification, MMCA Technical Committee, Version 4.2 with eMMC 4.3 and 4.4 Pass-Through boot

The following sections describe these P-Port interfaces.

#### GPIF II

The high-performance GPIF II interface enables functionality similar to, but more advanced than, FX2LP's GPIF and Slave FIFO interfaces.

The GPIF II is a programmable state machine that enables a flexible interface that may function either as a master or slave in industry-standard or proprietary interfaces. Both parallel and serial interfaces may be implemented with GPIF II.

Here are a list of GPIF II features:

- Functions as master or slave

- Provides 256 firmware programmable states

- Supports 8-bit and 16-bit parallel data bus

- Enables interface frequencies up to 100 MHz

- Supports 16 configurable control pins when a 16/8 data bus is used. All control pins can be either input/output or bi-directional.

GPIF II state transitions are based on control input signals. The control output signals are driven as a result of the GPIF II state transitions. The INT# output signal can be controlled by GPIF II. Refer to the GPIFII Designer tool. The GPIF II state machine's behavior is defined by a GPIF II descriptor. The GPIF II descriptor is designed such that the required interface specifications are met. 8 kB of memory (separate from the 512 kB of embedded SRAM) is dedicated to the GPIF II waveform where the GPIF II descriptor is stored in a specific format

Cypress's GPIF II Designer Tool enables fast development of GPIF II descriptors and includes examples for common interfaces.

Example implementations of GPIF II are the asynchronous slave FIFO and synchronous slave FIFO interfaces.

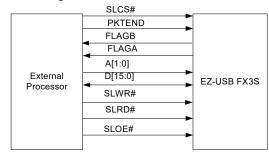

### Slave FIFO Interface

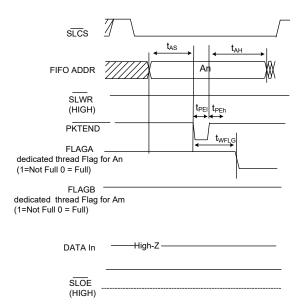

The Slave FIFO interface signals are shown in Figure 6. This interface allows an external processor to directly access up to

four buffers internal to FX3S. Further details of the Slave FIFO interface are described on page 35.

**Note** Access to all 32 buffers is also supported over the slave FIFO interface. For details, contact Cypress Applications Support.

Figure 6. Slave FIFO Interface

Note: Multiple Flags may be configured.

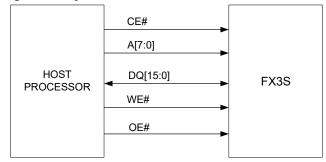

### **Asynchronous SRAM**

This interface consists of standard asynchronous SRAM interface signals as shown in Figure 7. This interface is used to access both the configuration registers and buffer memory of FX3S. Both single-cycle and burst accesses are supported by asynchronous interface signals.

The most significant address bit, A[7], determines whether the configuration registers or buffer memory are accessed. When the configuration registers are selected by asserting the address bit A[7], the address bus bits A[6:0] point to a configuration register. When A[7] is deasserted, the buffer memory is accessed as indicated by the P-Port DMA transfer register and the transfer size is determined by the P-Port DMA transfer size register.

Application processors with a DMA controller that use address auto-increment during DMA transfers, can override this by connecting any higher-order address line (such as A[15]/A[23]/A[31]) of the application processor to FX3S's A[7].

In the asynchronous SRAM mode, when reading from a buffer memory, FX3S supports two methods of reading out next data from the buffer. The next data may be read out on the rising edge of OE# or by toggling the least significant address bit A[0].

In this mode, the P-Port interface works with a 32.5-ns minimum access cycle providing an interface data rate of up to  $61.5\,\mathrm{MB}$  per second.

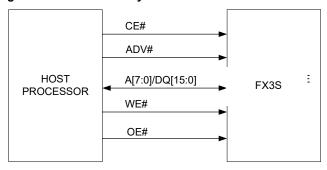

Figure 7. Asynchronous SRAM Interface

### Asynchronous Address/Data Multiplexed

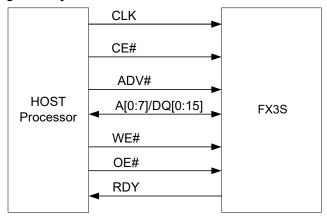

The physical ADMux memory interface consists of signals shown in Figure 8. This interface supports processors that implement a multiplexed address/data bus.

Figure 8. ADMux Memory Interface

FX3S's ADMux interface supports a 16-bit time-multiplexed address/data SRAM bus.

For read operations, assert both CE# and OE#.

For write operations, assert both CE# and WE#. OE# is "Don't Care" during a write operation (during both address and data phase of the write cycle). The input data is latched on the rising edge of WE# or CE#, whichever occurs first. Latch the addresses prior to the write operation by toggling Address Valid (ADV#). Assert Address Valid (ADV#) during the address phase of the write operation, as shown in Figure 19 on page 30.

ADV# must be LOW during the address phase of a read/write operation. ADV# must be HIGH during the data phase of a read/write operation, as shown in Figure 18 on page 30 and Figure 19 on page 30.

### Synchronous ADMux Interface

FX3S's P-Port supports a synchronous address/data multiplexed interface. This operates at an interface frequency of up to 100 MHz and supports a 16-bit data bus.

The RDY output signal from the FX3S device indicates a data valid for read transfers and is acknowledged for write transfers.

Figure 9. Synchronous ADMux Interface

See the Synchronous ADMux Interface timing diagrams for details.

### **Processor MMC (PMMC) Slave Interface**

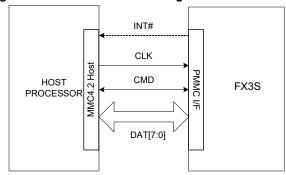

FX3S supports an MMC slave interface on the P-Port. This interface is named "PMMC" to distinguish it from the S-Port MMC interface.

Figure 10 illustrates the signals used to connect to the host processor.

The PMMC interface's GO\_IRQ\_STATE command allows FX3S to communicate asynchronous events without requiring the INT# signal. The use of the INT# signal is optional.

Figure 10. PMMC Interface Configuration

The MMC slave interface features are as follows:

- Interface operations are compatible with the MMC-System Specification, MMCA Technical Committee, Version 4.2.

- Supports booting from an eMMC device connected to the S-Port. This feature is supported for eMMC devices operating up to 52-MHz SDR.

- Supports PMMC interface voltage ranges of 1.7 V to 1.95 V and 2.7 V to 3.6 V.

- Supports open drain (both drive and receive open drain signals) on CMD pin to allow GO\_IRQ\_STATE (CMD40) for PMMC.

- Interface clock-frequency range: 0 to 52 MHz.

- Supports 1-bit, 4-bit, or 8-bit mode of operation. This configuration is determined by the MMC initialization procedure.

- FX3S responds to standard initialization phase commands as specified for the MMC 4.2 slave device.

- PMMC mode MMC 4.2 command classes: Class 0 (Basic), Class 2 (Block read), and Class 4 (Block write), Class 9 (I/O).

FX3S supports the following PMMC commands:

- Class 0: Basic

- CMD0, CMD1, CMD2, CMD3, CMD4, CMD6, CMD7, CMD8, CMD9, CMD10, CMD12, CMD13, CMD15, CMD19, CMD5 (wakeup support)

- Class 2: Block Read

CMD16, CMD17, CMD18, CMD23

■ Class 4: Block Write

CMD16, CMD23, CMD24, CMD25

■ Class 9: I-O

CMD39, CMD40

### CPU

FX3S has an on-chip 32-bit, 200-MHz ARM926EJ-S core CPU. The core has direct access to 16 kB of Instruction Tightly Coupled Memory (TCM) and 8 kB of Data TCM. The ARM926EJ-S core provides a JTAG interface for firmware debugging.

FX3S offers the following advantages:

- Integrates 512 KB of embedded SRAM for code and data and 8 KB of Instruction cache and Data cache.

- Implements efficient and flexible DMA connectivity between the various peripherals (such as, USB, GPIF II, I<sup>2</sup>S, SPI, UART), requiring firmware only to configure data accesses between peripherals, which are then managed by the DMA fabric.

- Allows easy application development on industry-standard development tools for ARM926EJ-S.

Examples of the FX3S firmware are available with the Cypress EZ-USB FX3S Development Kit. Software APIs that can be ported to an external processor are available with the Cypress EZ-USB FX3S Software Development Kit.

### Storage Port (S-Port)

FX3S has two independent storage ports (S0-Port and S1-Port). Both storage ports support the following specifications:

- MMC-system specification, MMCA Technical Committee, Version 4.41

- SD specification, Version 3.0

- SDIO host controller compliant with SDIO Specification Version 3.00

Both storage ports support the following features:

#### SD/MMC Clock Stop

FX3S supports the stop clock feature, which can save power if the internal buffer is full when receiving data from the SD/MMC/SDIO.

### **SD CLK Output Clock Stop**

During the data transfer, the SD\_CLK clock can be enabled (on) or disabled (stopped) at any time by the internal flow control mechanism.

SD\_CLK output frequency is dynamically configurable using a clock divisor from a system clock. The clock choice for the divisor is user-configurable through a register. For example, the following frequencies may be configured:

- 400 kHz For the SD/MMC card initialization

- 20 MHz For a card with 0- to 20-MHz frequency

- 24 MHz For a card with 0- to 26-MHz frequency

- 48 MHz For a card with 0- to 52-MHz frequency (48-MHz frequency on SD\_CLK is supported when the clock input to FX3S is 19.2 MHz or 38.4 MHz)

- 52 MHz For a card with 0- to 52-MHz frequency (52-MHz frequency on SD\_CLK is supported when the clock input to FX3S is 26 MHz or 52 MHz)

■ 100 MHz – For a card with 0- to 100-MHz frequency

If the DDR mode is selected, data is clocked on both the rising and falling edge of the SD clock. DDR clocks run up to 52 MHz.

### **Card Insertion and Removal Detection**

FX3S supports the two-card insertion and removal detection mechanisms.

- Use of SD\_D[3] data: During system design, this signal must have an external 470-kΩ pull-down resistor connected to SD\_D[3]. SD cards have an internal 10-kΩ pull-up resistor. When the card is inserted or removed from the SD/MMC connector, the voltage level at the SD\_D[3] pin changes and triggers an interrupt to the CPU. The older generations of MMC cards do not support this card detection mechanism.

- Use of the S0/S1\_INS pin: Some SD/MMC connectors facilitate a micro switch for card insertion/removal detection. This micro switch can be connected to S0/S1\_INS. When the card is inserted or removed from the SD/MMC connector, it turns the micro switch on and off. This changes the voltage level at the pin that triggers the interrupt to the CPU. The card-detect micro switch polarity is assumed to be the same as the write-protect micro switch polarity. A low indicates that the card is inserted. This S0/S1\_INS pin is shared between the two S-Ports. Register configuration determines which port gets to use this pin. This pin is mapped to the S1VDDQ power domain; if S0VDDQ and S1VDDQ are at different voltage levels, this pin cannot be used as S1\_INS.

### Write Protection (WP)

The S0\_WP/S1\_WP (SD Write Protection) on S-Port is used to connect to the WP micro switch of SD/MMC card connector. This pin internally connects to a CPU-accessible GPIO for firmware to detect the SD card write protection.

#### **SDIO Interrupt**

The SDIO interrupt functionality is supported as specified in the SDIO specification Version 2.00 (January 30, 2007).

#### **SDIO Read-Wait Feature**

FX3S supports the optional read-wait and suspend-resume features as defined in the SDIO specification Version 2.00 (January 30, 2007).

### JTAG Interface

FX3S's JTAG interface has a standard five-pin interface to connect to a JTAG debugger in order to debug firmware through the CPU-core's on-chip-debug circuitry.

Industry-standard debugging tools for the ARM926EJ-S core can be used for the FX3S application development.

### Other Interfaces

FX3S supports the following serial peripherals:

- **■** UART

- I<sup>2</sup>C

- I<sup>2</sup>S

- SPI

The SPI, UART, and I<sup>2</sup>S interfaces are multiplexed on the serial peripheral port.

#### **UART Interface**

The UART interface of FX3S supports full-duplex communication. It includes the signals noted in Table 1.

**Table 1. UART Interface Signals**

| Signal | Description   |

|--------|---------------|

| TX     | Output signal |

| RX     | Input signal  |

| CTS    | Flow control  |

| RTS    | Flow control  |

The UART is capable of generating a range of baud rates, from 300 bps to 4608 Kbps, selectable by the firmware. If flow control is enabled, then FX3S's UART only transmits data when the CTS input is asserted. In addition to this, FX3S's UART asserts the RTS output signal, when it is ready to receive data.

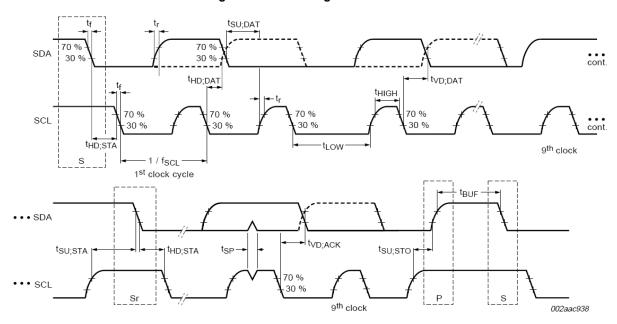

### I<sup>2</sup>C Interface

FX3S's I<sup>2</sup>C interface is compatible with the I<sup>2</sup>C Bus Specification Revision 3. This I<sup>2</sup>C interface is capable of operating only as I<sup>2</sup>C master; therefore, it may be used to communicate with other I<sup>2</sup>C slave devices. For example, FX3S may boot from an EEPROM connected to the I<sup>2</sup>C interface, as a selectable boot option.

FX3S's I<sup>2</sup>C Master Controller also supports multi-master mode functionality.

The power supply for the  $I^2C$  interface is VIO5, which is a separate power domain from the other serial peripherals. This gives the  $I^2C$  interface the flexibility to operate at a different voltage than the other serial interfaces.

The  $I^2C$  controller supports bus frequencies of 100 kHz, 400 kHz, and 1 MHz. When VIO5 is 1.2 V, the maximum operating frequency supported is 100 kHz. When VIO5 is 1.8 V, 2.5 V, or 3.3 V, the operating frequencies supported are 400 kHz and 1 MHz. The  $I^2C$  controller supports the clock-stretching feature to enable slower devices to exercise flow control.

The I<sup>2</sup>C interface's SCL and SDA signals require external pull-up resistors. The pull-up resistors must be connected to VIO5.

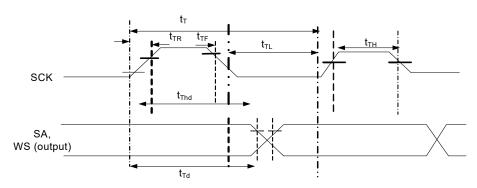

### I<sup>2</sup>S Interface

FX3S has an I<sup>2</sup>S port to support external audio codec devices. FX3S functions as I<sup>2</sup>S Master as transmitter only. The I<sup>2</sup>S interface consists of four signals: clock line (I2S\_CLK), serial data line (I2S\_SD), word select line (I2S\_WS), and master system clock (I2S\_MCLK). FX3S can generate the system clock as an output on I2S\_MCLK or accept an external system clock input on I2S MCLK.

The sampling frequencies supported by the I<sup>2</sup>S interface are 8 kHz, 16 kHz, 32 kHz, 44.1 kHz, 96 kHz and 192 kHz.

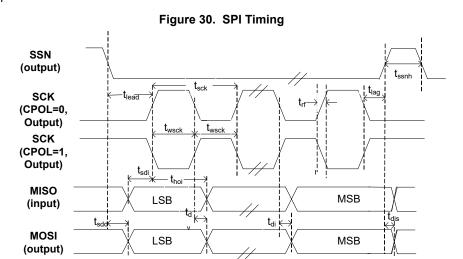

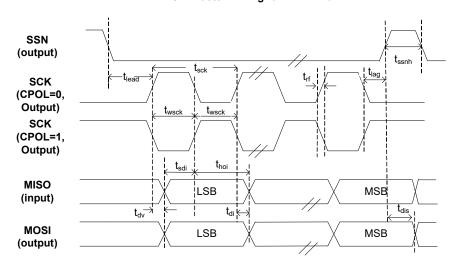

### **SPI Interface**

FX3S supports an SPI Master interface on the Serial Peripherals port. The maximum operation frequency is 33 MHz.

The SPI controller supports four modes of SPI communication (see SPI Timing Specification on page 47 for details on the modes) with the Start-Stop clock. This controller is a single-master controller with a single automated SSN control. It supports transaction sizes ranging from 4 bits to 32 bits.

## **Boot Options**

FX3S can load boot images from various sources, selected by the configuration of the PMODE pins. Following are the FX3S boot options:

- Boot from USB

- Boot from I<sup>2</sup>C

- Boot from SPI

- □ Cypress SPI flash parts supported are S25FS064S (64-Mbit), S25FS128S (128-Mbit) and S25LFL064L (64-Mbit).

- □ W25Q32FW (32-Mbit) is also supported.

- Boot from eMMC (S0-port)

- Boot from GPIF II ASync ADMux mode

- Boot from GPIF II Sync ADMux mode

- Boot from GPIF II ASync SRAM mode

- Boot from PMMC (P-Port)

Table 2. FX3S Booting Options

| PMODE[2:0] [2] | Boot From                                         |

|----------------|---------------------------------------------------|

| F00            | Sync ADMux (16-bit)                               |

| F01            | Async ADMux (16-bit)                              |

| F10            | PMMC Legacy                                       |

| F11            | USB boot                                          |

| F0F            | Async SRAM (16-bit)                               |

| F1F            | I <sup>2</sup> C, On Failure, USB Boot is Enabled |

Table 2. FX3S Booting Options (continued)

| PMODE[2:0] [2] | Boot From                                      |

|----------------|------------------------------------------------|

| 1FF            | I <sup>2</sup> C only                          |

| 0F1            | SPI, On Failure, USB Boot is Enabled           |

| 000            | S0-Port (eMMC) On failure, USB boot is enabled |

| 100            | S0-port (eMMC)                                 |

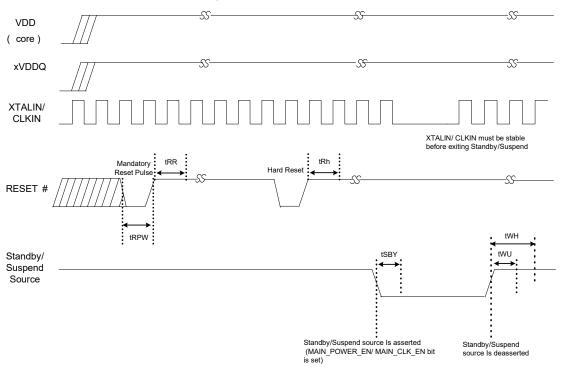

### Reset

### **Hard Reset**

A hard reset is initiated by asserting the Reset# pin on FX3S. The specific reset sequence and timing requirements are detailed in Figure 31 on page 49 and Table 27 on page 49. All I/Os are tristated during a hard reset.

#### Soft Reset

In a soft reset, the processor sets the appropriate bits in the PP\_INIT control register. There are two types of Soft Reset:

- CPU Reset The CPU Program Counter is reset. Firmware does not need to be reloaded following a CPU Reset.

- Whole Device Reset This reset is identical to Hard Reset.

- The firmware must be reloaded following a Whole Device Reset.

2. F indicates Floating.

## Clocking

FX3S allows either a crystal to be connected between the XTALIN and XTALOUT pins or an external clock to be connected at the CLKIN pin. The XTALIN, XTALOUT, CLKIN, and CLKIN 32 pins can be left unconnected if they are not used.

Crystal frequency supported is 19.2 MHz, while the external clock frequencies supported are 19.2, 26, 38.4, and 52 MHz.

FX3S has an on-chip oscillator circuit that uses an external 19.2-MHz (±100 ppm) crystal (when the crystal option is used). An appropriate load capacitance is required with a crystal. Refer to the specification of the crystal used to determine the appropriate load capacitance. The FSLC[2:0] pins must be configured appropriately to select the crystal- or clock-frequency option. The configuration options are shown in Table 3.

Clock inputs to FX3S must meet the phase noise and jitter requirements specified in Table 4.

The input clock frequency is independent of the clock and data rate of the FX3S core or any of the device interfaces (including P-Port and S-Port). The internal PLL applies the appropriate clock multiply option depending on the input frequency.

Table 3. Crystal/Clock Frequency Selection

| FSLC[2] | FSLC[1] | FSLC[0] | Crystal/Clock<br>Frequency |

|---------|---------|---------|----------------------------|

| 0       | 0       | 0       | 19.2-MHz crystal           |

| 1       | 0       | 0       | 19.2-MHz input CLK         |

| 1       | 0       | 1       | 26-MHz input CLK           |

| 1       | 1       | 0       | 38.4-MHz input CLK         |

| 1       | 1       | 1       | 52-MHz input CLK           |

Table 4. FX3S Input Clock Specifications

| Parameter                   | December 2     | Specif | Specification |       |

|-----------------------------|----------------|--------|---------------|-------|

| Parameter                   | Description    | Min    | Max           | Units |

| Phase noise                 | 100-Hz offset  | _      | -75           | dB    |

|                             | 1- kHz offset  | _      | -104          | dB    |

|                             | 10-kHz offset  | _      | -120          | dB    |

|                             | 100-kHz offset | _      | -128          | dB    |

|                             | 1-MHz offset   | _      | -130          | dB    |

| Maximum frequency deviation |                | _      | 150           | ppm   |

| Duty cycle                  |                | 30     | 70            | %     |

| Overshoot                   |                | _      | 3             | %     |

| Undershoot                  |                | _      | -3            | %     |

| Rise time/fall time         |                | _      | 3             | ns    |

### 32-kHz Watchdog Timer Clock Input

FX3S includes a watchdog timer. The watchdog timer can be used to interrupt the ARM926EJ-S core, automatically wake up the FX3S in Standby mode, and reset the ARM926EJ-S core. The watchdog timer runs a 32-kHz clock, which may be optionally supplied from an external source on a dedicated FX3S pin.

The firmware can disable the watchdog timer.

Requirements for the optional 32-kHz clock input are listed in Table 5.

Table 5. 32-kHz Clock Input Requirements

| Parameter           | Min | Max  | Units |

|---------------------|-----|------|-------|

| Duty cycle          | 40  | 60   | %     |

| Frequency deviation | _   | ±200 | ppm   |

| Rise time/fall time | -   | 200  | ns    |

#### **Power**

FX3S has the following power supply domains:

- IO\_VDDQ: This is a group of independent supply domains for digital I/Os. The voltage level on these supplies is 1.8 V to 3.3 V. FX3S provides six independent supply domains for digital I/Os listed as follows (see Pin Description on page 17 for details on each of the power domain signals):

- □ VIO1: GPIF II I/O

- □ VIO2: S0-Port Supply

- □ VIO3: S1-Port Supply

- □ VIO4: S1-Port and Low Speed Peripherals (UART/SPI/I2S) Supply

- □ VIO5: I<sup>2</sup>C and JTAG (supports 1.2 V to 3.3 V)

- □ CVDDQ: Clock

- V<sub>DD</sub>: This is the supply voltage for the logic core. The nominal supply-voltage level is 1.2 V. This supplies the core logic circuits. The same supply must also be used for the following:

- AVDD: This is the 1.2-V supply for the PLL, crystal oscillator, and other core analog circuits

- U3TXVDDQ/U3RXVDDQ: These are the 1.2-V supply voltages for the USB 3.0 interface.

- VBATT/VBUS: This is the 3.2-V to 6-V battery power supply for the USB I/O and analog circuits. This supply powers the USB

transceiver through FX3S's internal voltage regulator. VBATT is internally regulated to 3.3 V.

**Note:** No specific power-up sequence for FX3S power domains. Minimum power on reset time of 1 ms should be met and the power domains must be stable for FX3S operation.

### **Power Modes**

FX3S supports the following power modes:

- Normal mode: This is the full-functional operating mode. The internal CPU clock and the internal PLLs are enabled in this mode.

- Normal operating power consumption does not exceed the sum of I<sub>CC</sub> Core max and I<sub>CC</sub> USB max (see the DC Specifications table for current consumption specifications).

- □ The I/O power supplies VIO2, VIO3, VIO4, and VIO5 can be turned off when the corresponding interface is not in use. VIO1 cannot be turned off at any time if the GPIF II interface is used in the application.

- Low-power modes (see Table 6):

- □ Suspend mode with USB 3.0 PHY enabled (L1)

- □ Suspend mode with USB 3.0 PHY disabled (L2)

- □ Standby mode (L3)

- □ Core power-down mode (L4)

Table 6. Entry and Exit Methods for Low-Power Modes

| <b>Low-Power Mode</b>         | Characteristics                                                                                                                                                                                              | Methods of Entry                                                                                                                                                                                                                                                                     | Methods of Exit                                                                              |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

|                               | ■ The power consumption in this mode does not exceed ISB <sub>1</sub>                                                                                                                                        |                                                                                                                                                                                                                                                                                      |                                                                                              |

|                               | ■ USB 3.0 PHY is enabled and is in U3 mode (one of the suspend modes defined by the USB 3.0 specification). This one block alone is operational with its internal clock while all other clocks are shut down |                                                                                                                                                                                                                                                                                      | <ul> <li>D+ transitioning to low or high</li> <li>D- transitioning to low or high</li> </ul> |

|                               | ■ All I/Os maintain their previous state                                                                                                                                                                     |                                                                                                                                                                                                                                                                                      | ■ Impedance change on                                                                        |

|                               | core power must be retained. All other power domains can be turned on/off individually  The states of the configuration registers.                                                                           | <ul> <li>Firmware executing on ARM926EJ-S core can put FX3S into suspend mode. For example, on USB suspend condition, firmware may decide to put FX3S into suspend mode</li> <li>External Processor, through the use of mailbox registers, can put FX3S into suspend mode</li> </ul> | OTG_ID pin                                                                                   |

| Suspend Mode with USB 3.0 PHY |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                      | ■ Resume condition on SSRX±                                                                  |

| Enabled (L1)                  |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                      | ■ Detection of VBUS                                                                          |

|                               |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                      | ■ Level detect on UART_CTS                                                                   |

|                               |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                      | (programmable polarity)                                                                      |

|                               |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                      | ■ GPIF II interface assertion of CTL[0]                                                      |

|                               | ■ The firmware resumes operation from where it was suspended (except when woken up by RESET# assertion) because the program counter does not reset                                                           |                                                                                                                                                                                                                                                                                      | ■ Assertion of RESET#                                                                        |

Table 6. Entry and Exit Methods for Low-Power Modes (continued)

| Low-Power Mode    | Characteristics                                                                                                                                                                                                                                                                                        | Methods of Entry                                                                          | Methods of Exit                                             |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------|

|                   | ■ The power consumption in this mode does not exceed ISB <sub>2</sub>                                                                                                                                                                                                                                  |                                                                                           |                                                             |

|                   | ■ USB 3.0 PHY is disabled and the USB interface is in suspend mode                                                                                                                                                                                                                                     |                                                                                           |                                                             |

|                   | ■ The clocks are shut off. The PLLs are disabled                                                                                                                                                                                                                                                       |                                                                                           | ■ D+ transitioning to low or high                           |

|                   | ■ All I/Os maintain their previous state                                                                                                                                                                                                                                                               |                                                                                           | ■ D- transitioning to low or                                |

|                   | ■ USB interface maintains the previous state                                                                                                                                                                                                                                                           | ■ Firmware executing on ARM926EJ-S                                                        | high                                                        |

| Suspend Mode      | ■ Power supply for the wakeup source and core power must be retained. All other                                                                                                                                                                                                                        | core can put FX3S into suspend mode.<br>For example, on USB suspend                       | ■ Impedance change on<br>OTG_ID pin                         |

| with USB 3.0 PHY  | power domains can be turned on/off                                                                                                                                                                                                                                                                     | condition, firmware may decide to put FX3S into suspend mode                              | ■ Detection of VBUS                                         |

| Disabled (L2)     | <ul> <li>■ The states of the configuration registers,<br/>buffer memory and all internal RAM are<br/>maintained</li> </ul>                                                                                                                                                                             | ■ External Processor, through the use of mailbox registers can put FX3S into suspend mode | ■ Level detect on<br>UART_CTS<br>(programmable<br>polarity) |

|                   | ■ All transactions must be completed before FX3S enters Suspend mode                                                                                                                                                                                                                                   |                                                                                           | ■ GPIF II interface assertion of CTL[0]                     |

|                   | (state of outstanding transactions are not preserved)                                                                                                                                                                                                                                                  |                                                                                           | ■ Assertion of RESET#                                       |

|                   | ■ The firmware resumes operation from where it was suspended (except when woken up by RESET# assertion) because the program counter does not reset                                                                                                                                                     |                                                                                           |                                                             |

|                   | ■ The power consumption in this mode does not exceed ISB3                                                                                                                                                                                                                                              |                                                                                           |                                                             |

|                   | ■ All configuration register settings and program/data RAM contents are preserved. However, data in the buffers or other parts of the data path, if any, is not guaranteed. Therefore, the external processor should take care that the data needed is read before putting FX3S into this Standby Mode |                                                                                           | ■ Detection of VBUS                                         |

|                   | ■ The program counter is reset after waking up from Standby                                                                                                                                                                                                                                            | ■ Firmware executing on ARM926EJ-S                                                        | ■ Level detect on UART_CTS                                  |

| Standby Mode (L3) | ■ GPIO pins maintain their configuration                                                                                                                                                                                                                                                               | core or external processor configures                                                     | (Programmable Polarity)                                     |

| (_0)              | ■ Crystal oscillator is turned off                                                                                                                                                                                                                                                                     | the appropriate register                                                                  | ■ GPIF II interface                                         |

|                   | ■ Internal PLL is turned off                                                                                                                                                                                                                                                                           |                                                                                           | assertion of CTL[0]                                         |

|                   | ■ USB transceiver is turned off                                                                                                                                                                                                                                                                        |                                                                                           | ■ Assertion of RESET#                                       |

|                   | ■ ARM926EJ-S core is powered down.<br>Upon wakeup, the core re-starts and runs<br>the program stored in the program/data<br>RAM                                                                                                                                                                        |                                                                                           |                                                             |

|                   | ■ Power supply for the wakeup source and core power must be retained. All other power domains can be turned on/off individually                                                                                                                                                                        |                                                                                           |                                                             |

Table 6. Entry and Exit Methods for Low-Power Modes (continued)

| Low-Power Mode               | Characteristics                                                                                                                              | Methods of Entry           | Methods of Exit                        |  |  |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------|--|--|

| Core Power Down<br>Mode (L4) | ■ The power consumption in this mode does not exceed ISB <sub>4</sub>                                                                        |                            |                                        |  |  |

|                              | ■ Core power is turned off                                                                                                                   | ■ Turn off V <sub>DD</sub> |                                        |  |  |

|                              | All buffer memory, configuration<br>registers, and the program RAM do not<br>maintain state. After exiting this mode,<br>reload the firmware |                            | ■ Reapply VDD<br>■ Assertion of RESET# |  |  |

|                              | ■ In this mode, all other power domains can be turned on/off individually                                                                    |                            |                                        |  |  |

**Note:** The power consumption depends on how the FX3S IOs are utilized in the application. Refer to KBA85505 to estimate the current consumption by different power domains (VIO1–VIO5).

## **Configuration Options**

Configuration options are available for specific usage models. Contact Cypress Applications or Marketing for details.

## Digital I/Os

FX3S has internal firmware-controlled pull-up or pull-down resistors on all digital I/O pins. An internal 50-k $\Omega$  resistor pulls the pins high, while an internal 10-k $\Omega$  resistor pulls the pins low to prevent them from floating. The I/O pins may have the following states:

- Tristated (High-Z)

- Weak pull-up (via internal 50 kΩ)

- Pull-down (via internal 10 kΩ)

- Hold (I/O hold its value) when in low-power modes

- The JTAG TDI, TMC, and TRST# signals have fixed 50-k $\Omega$  internal pull-ups, and the TCK signal has a fixed 10-k $\Omega$  pull-down resistor.

All unused I/Os should be pulled high by using the internal pull-up resistors. All unused outputs should be left floating. All I/Os can be driven at full-strength, three-quarter strength, half-strength, or quarter-strength. These drive strengths are configured separately for each interface.

### **GPIOs**

EZ-USB enables a flexible pin configuration both on the GPIF II and the serial peripheral interfaces. Any unused control pins (except CTL[15]) on the GPIF II interface can be used as GPIOs.

Similarly, any unused pins on the serial peripheral interfaces may be configured as GPIOs. See the Pin Description on page 17 for pin configuration options.

All GPIF II and GPIO pins support an external load of up to 16 pF for every pin.

#### EMI

FX3S meets EMI requirements outlined by FCC 15B (USA) and EN55022 (Europe) for consumer electronics. FX3S can tolerate reasonable EMI, conducted by the aggressor, outlined by these specifications and continue to function as expected.

### System-level ESD

FX3S has built-in ESD protection on the D+, D-, and GND pins on the USB interface. The ESD protection levels provided on these ports are:

- ±2.2-KV human body model (HBM) based on JESD22-A114 Specification

- ±6-KV contact discharge and ±8-KV air gap discharge based on IEC61000-4-2 level 3A

- ± 8-KV Contact Discharge and ±15-KV Air Gap Discharge based on IEC61000-4-2 level 4C.

This protection ensures the device continues to function after ESD events up to the levels stated in this section.

The SSRX+, SSRX-, SSTX+, and SSTX- pins only have up to ±2.2-KV HBM internal ESD protection.

### **Pinouts**

Figure 11. FX3S Ball Map (Top View)

|   | 1        | 2        | 3        | 4        | 5        | 6        | 7        | 8        | 9            | 10           | 11       |

|---|----------|----------|----------|----------|----------|----------|----------|----------|--------------|--------------|----------|

| Α | U3VSSQ   | U3RXVDDQ | SSRXM    | SSRXP    | SSTXP    | SSTXM    | AVDD     | VSS      | DP           | DM           | NC       |

| В | VIO4     | FSLC[0]  | R_USB3   | FSLC[1]  | U3TXVDDQ | CVDDQ    | AVSS     | vss      | VSS          | VDD          | TRST#    |

| С | GPIO[54] | GPIO[55] | VDD      | GPIO[57] | RESET#   | XTALIN   | XTALOUT  | R_USB2   | OTG_ID       | TDO          | VIO5     |

| D | GPIO[50] | GPIO[51] | GPI0[52] | GPIO[53] | GPIO[56] | CLKIN_32 | CLKIN    | VSS      | 12C_GPIO[58] | I2C_GPIO[59] | NC       |

| E | GPIO[47] | VSS      | VIO3     | GPI0[49] | GPIO[48] | FSLC[2]  | TDI      | TMS      | VDD          | VBATT        | VBUS     |

| F | VIO2     | GPIO[45] | GPI0[44] | GPI0[41] | GPIO[46] | TCK      | GPIO[2]  | GPIO[5]  | GPIO[1]      | GPIO[0]      | VDD      |

| G | VSS      | GPIO[42] | GPI0[43] | GPIO[30] | GPIO[25] | GPI0[22] | GPI0[21] | GPIO[15] | GPIO[4]      | GPIO[3]      | VSS      |

| Н | VDD      | GPIO[39] | GPI0[40] | GPIO[31] | GPIO[29] | GPIO[26] | GPIO[20] | GPI0[24] | GPI0[7]      | GPIO[6]      | VIO1     |

| J | GPIO[38] | GPIO[36] | GPI0[37] | GPIO[34] | GPI0[28] | GPI0[16] | GPIO[19] | GPI0[14] | GPIO[9]      | GPIO[8]      | VDD      |

| K | GPIO[35] | GPIO[33] | VSS      | VSS      | GPI0[27] | GPIO[23] | GPIO[18] | GPI0[17] | GPIO[13]     | GPI0[12]     | GPIO[10] |

| L | VSS      | VSS      | VSS      | GPI0[32] | VDD      | VSS      | VDD      | INT#     | VIO1         | GPIO[11]     | VSS      |

# **Pin Description**

Table 7. Pin Description

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Pin | Power Domain | I/O | Name     | FX3S Pin Description    |                             |         |               |                |              |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------|-----|----------|-------------------------|-----------------------------|---------|---------------|----------------|--------------|--|

| F10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |              |     |          |                         |                             | P-Port  |               |                |              |  |

| F9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |              |     |          |                         | Slave FIFO<br>Interface [3] | РММС    | Async<br>SRAM | Async<br>ADMux | SyncADMux    |  |

| F7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | F10 | VIO1         | I/O | GPIO[0]  | DQ[0]                   | DQ[0]                       | MMC_D0  | DQ[0]         | DQ[0]/A[0]     | DQ[0]/A[0]   |  |

| G10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | F9  | VIO1         | I/O | GPIO[1]  | DQ[1]                   | DQ[1]                       | MMC_D1  | DQ[1]         | DQ[1]/A[1]     | DQ[1]/A[1]   |  |