# HM-65262

# 16K x 1 Asynchronous CMOS Static RAM

March 1997

### Features

- Low Operating Current ...... 50mA Max

- Data Retention at 2.0V......20μA Max

- TTL Compatible Inputs and Outputs

- JEDEC Approved Pinout

- No Clocks or Strobes Required

- Temperature Range ......+55°C to +125°C

- Equal Cycle and Access Time

- Single 5V Supply

- Gated Inputs-No Pull-Up or Pull-Down Resistors Required

## Description

The HM-65262 is a CMOS 16384 x 1-bit Static Random Access Memory manufactured using the Intersil Advanced SAJI V process. The device utilizes asynchronous circuit design for fast cycle times and ease of use. The HM-65262 is available in both JEDEC standard 20 pin, 0.300 inch wide CERDIP and 20 pad CLCC packages, providing high board-level packing density. Gated inputs lower standby current, and also eliminate the need for pull-up or pull-down resistors.

The HM-65262, a full CMOS RAM, utilizes an array of six transistor (6T) memory cells for the most stable and lowest possible standby supply current over the full military temperature range. In addition to this, the high stability of the 6T RAM cell provides excellent protection against soft errors due to noise and alpha particles. This stability also improves the radiation tolerance of the RAM over that of four transistor (4T) devices.

# **Ordering Information**

| PACKAGE               | TEMP. RANGE     | <b>70ns/20</b> μ <b>A</b> (NOTE 1) | <b>85ns/20</b> μ <b>A</b> (NOTE 1) | (NOTE 1)<br><b>85ns/400</b> μ <b>A</b> | PKG. NO. |  |

|-----------------------|-----------------|------------------------------------|------------------------------------|----------------------------------------|----------|--|

| CERDIP                | -40°C to +85°C  | HM1-65262B-9                       | HM1-65262-9                        | -                                      | F20.3    |  |

| JAN # -55°C to +125°C |                 | 29109BRA                           | 29103BRA                           | -                                      | F20.3    |  |

| SMD#                  | -55°C to +125°C | 8413203RA                          | 8413201RA                          | -                                      | F20.3    |  |

| CLCC (SMD#)           | -55°C to +125°C | 8413203YA                          | 8413201YA                          | -                                      | J20.C    |  |

NOTE:

1. Access Time/Data Retention Supply Current.

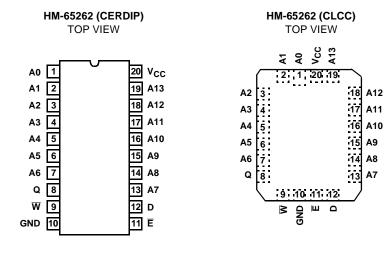

# **Pinouts**

| A0 - A13             | Address Input          |  |  |  |

|----------------------|------------------------|--|--|--|

| Ē                    | Chip Enable/Power Down |  |  |  |

| Q                    | Data Out               |  |  |  |

| D                    | Data In                |  |  |  |

| V <sub>SS</sub> /GND | Ground                 |  |  |  |

| V <sub>CC</sub>      | Power (+5)             |  |  |  |

| W                    | Write Enable           |  |  |  |

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. 1-888-INTERSIL or 321-724-7143 | Intersil (and design) is a trademark of Intersil Americas Inc. Copyright © Intersil Americas Inc. 2002. All Rights Reserved 1

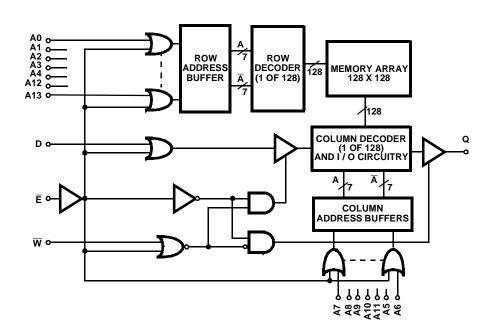

# Functional Diagram

| Absolute Maximum Ratings                                                                                                                                      | Thermal Information                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Supply Voltage +7.0V<br>Input or Output Voltage Applied for all grades0.3V to V <sub>CC</sub> +0.3V<br>Typical Derating Factor                                | Thermal Resistance (Typical) $\theta_{JA}$ $\theta_{JC}$ CERDIP Package. $66^{\circ}$ C/W $13^{\circ}$ C/W         CLCC Package $75^{\circ}$ C/W $18^{\circ}$ C/W         Maximum Storage Temperature Range $-65^{\circ}$ C to $+150^{\circ}$ C         Maximum Junction Temperature $+175^{\circ}$ C         Maximum Lead Temperature (Soldering 10s) $+300^{\circ}$ C |  |  |  |  |

|                                                                                                                                                               | Die Characteristics                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|                                                                                                                                                               | Gate Count                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may ca<br>of the device at these or any other conditions above those indicated in the oper | ause permanent damage to the device. This is a stress only rating and operation rational sections of this specification is not implied.                                                                                                                                                                                                                                 |  |  |  |  |

#### **Operating Conditions**

| <b>DC Electrical Specifications</b> | $V_{CC} = 5V \pm 10\%$ ; T <sub>A</sub> = -40 <sup>o</sup> C to +85 <sup>o</sup> C (HM-65262B-9, HM-65262C-9), HM-65262C-9) |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

|        | LIMITS                            |                      |                      |       |                                                                                                                                                                                                                    |  |  |

|--------|-----------------------------------|----------------------|----------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SYMBOL | PARAMETER                         | MIN                  | MAX                  | UNITS | TEST CONDITIONS                                                                                                                                                                                                    |  |  |

| ICCSB1 | Standby Supply Current            | -od                  | 50                   | μΑ    | $\frac{\text{HM-65262B-9, HM-65262-9, IO} = 0\text{mA,}}{\overline{\text{E}} = \text{V}_{\text{CC}} - 0.3\text{V}, \text{V}_{\text{CC}} = 5.5\text{V}}$                                                            |  |  |

|        |                                   | -                    | 900                  | μΑ    | $\label{eq:HM-65262C-9, IO = 0mA,} \begin{split} &HM\text{-}65262C\text{-}9, \text{ IO = 0mA,} \\ &\overline{\text{E}} = \text{V}_{\text{CC}} \text{-}0.3\text{V}, \text{V}_{\text{CC}} = 5.5\text{V} \end{split}$ |  |  |

| ICCSB  | Standby Supply Current            | -                    | 5                    | mA    | $\overline{E}$ = 2.2V, IO = 0mA, V <sub>CC</sub> = 5.5V                                                                                                                                                            |  |  |

| ICCEN  | Enabled Supply Current            | -                    | 50                   | mA    | $\overline{E}$ = 0.8V, IO = 0mA, V <sub>CC</sub> = 5.5V                                                                                                                                                            |  |  |

| ICCOP  | Operating Supply Current (Note 1) | -                    | 50                   | mA    | $\overline{E}$ = 0.8V, IO = 0mA, f = 1MHz,<br>V <sub>CC</sub> = 5.5V                                                                                                                                               |  |  |

| ICCDR  | Data Retention Supply Current     | -                    | 20                   | μΑ    | HM-65262B-9, HM-65262-9, $V_{CC} = 2.0V, \overline{E} = V_{CC}$                                                                                                                                                    |  |  |

|        |                                   | -                    | 400                  | μΑ    | HM-65262C-9, $V_{CC}$ = 2.0V, $\overline{E}$ = $V_{CC}$                                                                                                                                                            |  |  |

| ICCDR1 | Data Retention Supply Current     | -                    | 30                   | μΑ    | HM-65262B-9, HM-65262-9, $V_{CC} = 3.0V, \overline{E} = V_{CC}$                                                                                                                                                    |  |  |

|        |                                   | -                    | 550                  | μΑ    | HM-65262C-9, $V_{CC} = 3.0V$ , $\overline{E} = V_{CC}$                                                                                                                                                             |  |  |

| VCCDR  | Data Retention Supply Voltage     | 2.0                  | -                    | V     |                                                                                                                                                                                                                    |  |  |

| II     | Input Leakage Current             | -1.0                 | +1.0                 | μΑ    | $VI = V_{CC}$ or GND, $V_{CC} = 5.5V$                                                                                                                                                                              |  |  |

| IOZ    | Output Leakage Current            | -1.0                 | +1.0                 | μΑ    | $VIO = V_{CC} \text{ or GND}, V_{CC} = 5.5V$                                                                                                                                                                       |  |  |

| VIL    | Input Low Voltage                 | -0.3                 | 0.8                  | V     | $V_{CC} = 4.5V$                                                                                                                                                                                                    |  |  |

| VIH    | Input High Voltage                | 2.2                  | V <sub>CC</sub> +0.3 | V     | $V_{CC} = 5.5V$                                                                                                                                                                                                    |  |  |

| VOL    | Output Low Voltage                | -                    | 0.4                  | V     | IO = 8.0mA, V <sub>CC</sub> = 4.5V                                                                                                                                                                                 |  |  |

| VOH1   | Output High Voltage               | 2.4                  | -                    | V     | IO = -4.0mA, V <sub>CC</sub> = 4.5V                                                                                                                                                                                |  |  |

| VOH2   | Output High Voltage (Note 2)      | V <sub>CC</sub> -0.4 | -                    | V     | $IO = -100\mu A, V_{CC} = 4.5V$                                                                                                                                                                                    |  |  |

## **Capacitance** $T_A = +25^{\circ}C$

| SYMBOL | PARAMETER                         | MAX | UNITS | TEST CONDITIONS                |

|--------|-----------------------------------|-----|-------|--------------------------------|

| CI     | Input Capacitance (Note 2)        | 10  | pF    | f = 1MHz, All measurements are |

| CIO    | Input/Output Capacitance (Note 2) | 12  | pF    | referenced to device GND       |

NOTES:

1. Typical derating 5mA/MHz increase in ICCOP.

2. Tested at initial design and after major design changes.

# HM-65262

|        |         |                                     | LIMITS                 |     |     |             |     |     |       |                    |

|--------|---------|-------------------------------------|------------------------|-----|-----|-------------|-----|-----|-------|--------------------|

| SYMBOL |         | PARAMETER                           | HM-65262B-9 HM-65262-9 |     |     | HM-65262C-9 |     | 1   | тгет  |                    |

|        |         |                                     | MIN                    | MAX | MIN | MAX         | MIN | MAX | UNITS | TEST<br>CONDITIONS |

| READ   | CYCLE   |                                     |                        |     |     | •           |     |     |       |                    |

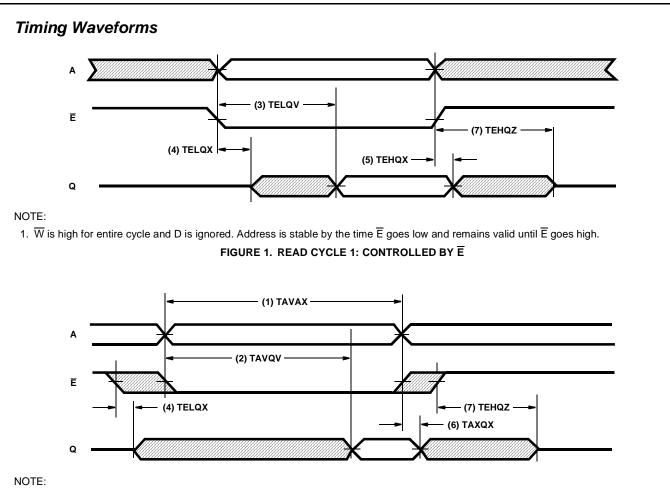

| (1)    | TAVAX   | Read/Cycle Time                     | 70                     | -   | 85  | -           | 85  | -   | ns    | (Notes 1, 3)       |

| (2)    | TAVQV   | Address Access Time                 | -                      | 70  | -   | 85          | -   | 85  | ns    | (Notes 1, 3)       |

| (3)    | TELQV   | Chip Enable Access Time             | -                      | 70  | -   | 85          | -   | 85  | ns    | (Notes 1, 3)       |

| (4)    | TELQX   | Chip Enable Output Enable<br>Time   | 5                      | -   | 5   | -           | 5   | -   | ns    | (Notes 2, 3)       |

| (5)    | TEHQX   | Chip Disable Output Hold<br>Time    | 5                      | -   | 5   | -           | 5   | -   | ns    | (Notes 2, 3)       |

| (6)    | TAXQX   | Address Invalid Output Hold<br>Time | 5                      | -   | 5   | -           | 5   | -   | ns    | (Notes 2, 3)       |

| (7)    | TEHQZ   | Chip Enable Output Disable<br>Time  | -                      | 30  | -   | 30          | -   | 30  | ns    | (Notes 2, 3)       |

| WRIT   | E CYCLE | -                                   |                        | -   | =   | -           |     |     | -     |                    |

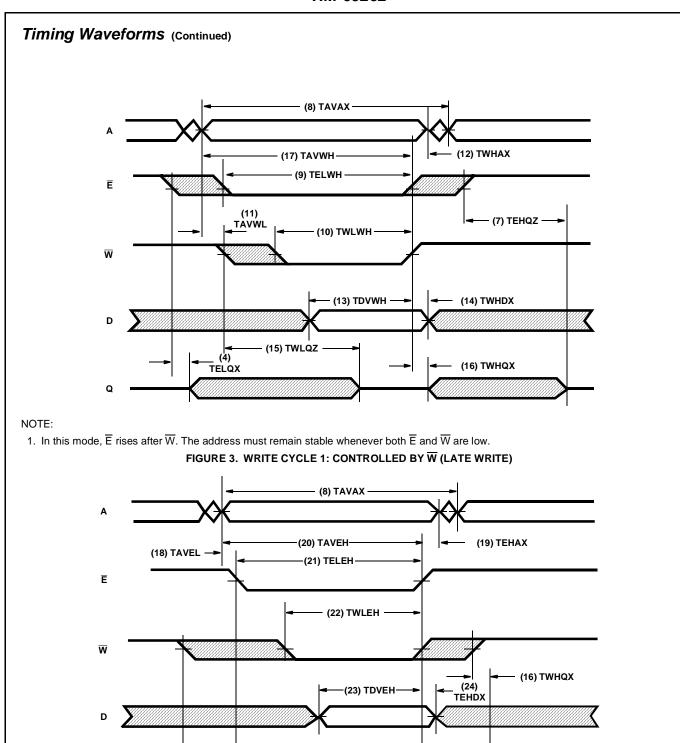

| (8)    | TAVAX   | Write Cycle Time                    | 70                     | -   | 85  | -           | 85  | -   | ns    | (Notes 1, 3)       |

| (9)    | TELWH   | Chip Selection to End of<br>Write   | 55                     | -   | 65  | -           | 65  | -   | ns    | (Notes 1, 3)       |

| (10)   | TWLWH   | Write Enable Pulse Width            | 40                     | -   | 45  | -           | 45  | -   | ns    | (Notes 1, 3)       |

| (11)   | TAVWL   | Address Setup Time                  | 0                      | -   | 0   | -           | 0   | -   | ns    | (Notes 1, 3)       |

| (12)   | TWHAX   | Address Hold Time                   | 0                      | -   | 0   | -           | 0   | -   | ns    | (Notes 1, 3)       |

| (13)   | TDVWH   | Data Setup Time                     | 30                     | -   | 35  | -           | 35  | -   | ns    | (Notes 1, 3)       |

| (14)   | TWHDX   | Data Hold Time                      | 0                      | -   | 0   | -           | 0   | -   | ns    | (Notes 1, 3)       |

| (15)   | TWLQZ   | Write Enable Output Disable<br>Time | -                      | 30  | -   | 30          | -   | 30  | ns    | (Notes 2, 3)       |

| (16)   | TWHQX   | Write Disable Output Enable<br>Time | 0                      | -   | 0   | -           | 0   | -   | ns    | (Notes 2, 3)       |

| (17)   | TAVWH   | Address Valid to End of Write       | 55                     | -   | 65  | -           | 65  | -   | ns    | (Notes 1, 3)       |

| (18)   | TAVEL   | Address Setup Time                  | 0                      | -   | 0   | -           | 0   | -   | ns    | (Notes 1, 3)       |

| (19)   | TEHAX   | Address Hold Time                   | 0                      | -   | 0   | -           | 0   | -   | ns    | (Notes 1, 3)       |

| (20)   | TAVEH   | Address Valid to End of Write       | 55                     | -   | 65  | -           | 65  | -   | ns    | (Notes 1, 3        |

| (21)   | TELEH   | Enable Pulse Width                  | 55                     | -   | 65  | -           | 65  | -   | ns    | (Notes 1, 3        |

| (22)   | TWLEH   | Write Enable Pulse Setup<br>Time    | 40                     | -   | 45  | -           | 45  | -   | ns    | (Notes 1, 3)       |

| (23)   | TDVEH   | Chip Setup Time                     | 30                     | -   | 35  | -           | 35  | 0   | ns    | (Notes 1, 3)       |

| (24)   | TEHDX   | Data Hold Time                      | 0                      | -   | 0   | -           | 0   | -   | ns    | (Notes 1, 3        |

NOTES:

1. Input pulse levels: 0 to 3.0V; Input rise and fall times: 5ns (max); Input and output timing reference level: 1.5V; Output load: 1 TTL gate equivalent and C<sub>L</sub> = 50pF (min) - for C<sub>L</sub> greater than 50pF, access time is derated by 0.15ns per pF.

2. Tested at initial design and after major design changes.

3.  $V_{CC}$  = 4.5 and 5.5V.

# HM-65262

1.  $\overline{W}$  is high for the entire cycle and D is ignored.  $\overline{E}$  is stable prior to A becoming valid and after A becomes invalid. FIGURE 2. READ CYCLE 2: CONTROLLED BY ADDRESS

TEHQZ (Max) TWHQZ (Min), then Q will remain in the high impedance state throughout the cycle.

NOTE:

#### FIGURE 4. WRITE CYCLE 2: CONTROLLED BY E (EARLY WRITE)

1. In this mode, W rises after E. If W falls before E by a time exceeding TWLQZ (Max) TELQX (Min), and rises after E by a time exceeding

(7) TEHQZ

(4) TELQX

(15) TWLQZ

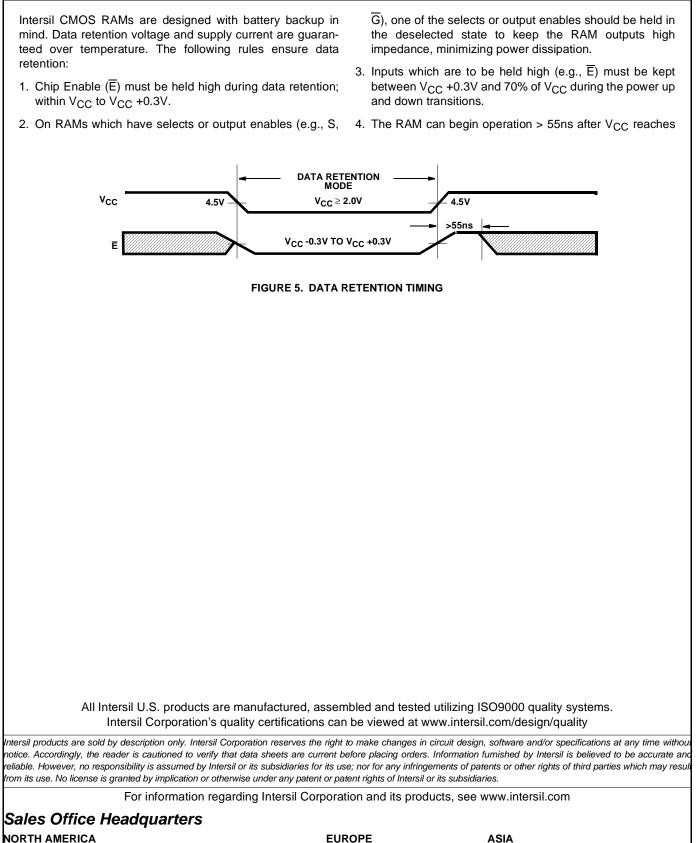

Low Voltage Data Retention

Q

Intersil Corporation 7585 Irvine Center Drive Suite 100 Irvine, CA 92618 TEL: (949) 341-7000 FAX: (949) 341-7123

Intersil Corporation 2401 Palm Bay Rd. Palm Bay, FL 32905 TEL: (321) 724-7000 FAX: (321) 724-7946 EUROPE Intersil Europe Sarl Ave. William Graisse, 3 1006 Lausanne Switzerland TEL: +41 21 6140560 FAX: +41 21 6140579 ASIA Intersil Corporation Unit 1804 18/F Guangdong Water Building 83 Austin Road TST, Kowloon Hong Kong TEL: +852 2723 6339 FAX: +852 2730 1433

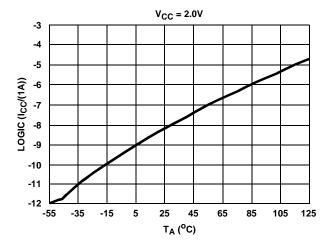

# Typical Performance Curve

FIGURE 6. TYPICAL ICCDR vs TA