A Schlumberger Company

# 93L422 256 x 4-Bit Static **Random Access Memory**

Memory and High Speed Logic

# Description

The 93L422 is a 1024-bit read/write Random Access Memory (RAM), organized 256 words by four bits. It is designed for high speed cache, control and buffer storage applications. The 93L422 is available in two speeds, "standard" speed and an "A" grade. The device includes full on-chip decoding, separate Data inputs and non-inverting Data outputs, as well as two Chip Select lines.

- Commercial Address Access Time 93L422 - 60 ns Max 93L422A - 45 ns Max

- Military Address Access Time 93L422 -- 75 ns Max 93L422A - 55 ns Max

- Fully TTL Compatible

- **Features Three State Outputs**

- Power Dissipation 0.25 mW/Bit Typ

- Power Dissipation Decreases with Increasing Temperature

# Pin Names

| Address Inputs                   |

|----------------------------------|

| Data Inputs                      |

| Chip Select Input (Active LOW)   |

| Chip Select Input (Active HIGH)  |

| Write Enable Input (Active LOW)  |

| Output Enable Input (Active LOW) |

| Data Outputs                     |

|                                  |

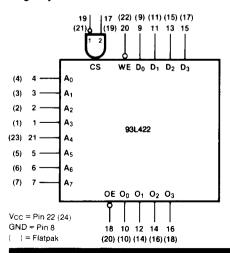

# **Logic Symbol**

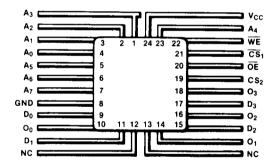

# **Connection Diagrams** 22-Pin DIP (Top View)

# 24-Pin Flatpak (Top View)

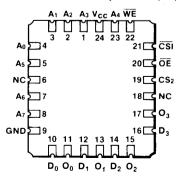

# 24-Pin Leadless Chip Carrier (i op View)

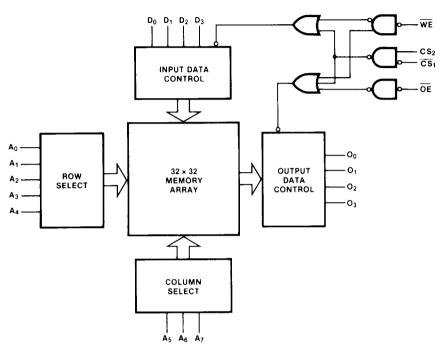

# Logic Diagram

# **Functional Description**

The 93L422 is a fully decoded 1024-bit Random Access Memory organized 256 words by four bits. Word selection is achieved by means of an 8-bit address,  $A_0$  through  $A_7$ .

Two Chip Select inputs, inverting and non-inverting, are provided for logic flexibility. For larger memories, the fast chip select access time permits the decoding of the chip selects from the address without increasing address access time.

The read and write operations are controlled by the state of the active LOW Write Enable  $(\overline{WE})$  input. When  $\overline{WE}$  is

held LOW and the chip is selected, the data at  $D_0-D_3$  is written into the addressed location. Since the write function is level-triggered, data must be held stable for at least  $twsD_{(min)}$  plus  $tw_{(min)}$  plus  $twHD_{(min)}$  to insure a valid write. To read,  $\overline{WE}$  is held HIGH and the chip selected. Non-inverted data is then presented at the outputs  $(O_0-O_3)$ .

The 93L422 has 3-state outputs which provide active pull-ups when enabled and high output impedance when disabled. This allows optimization of word expansion in bus organized systems.

# **Truth Table**

|    | Inţ | Inputs          |    |                  |                 |

|----|-----|-----------------|----|------------------|-----------------|

| ŌE | CS₁ | CS <sub>2</sub> | WE | 3-State          | Mode            |

| X  | н   | Х               | Х  | HIGH Z           | Not Selected    |

| X  | X   | L               | ×  | HIGH Z           | Not Selected    |

| L  | L   | н               | Н  | D <sub>OUT</sub> | READ            |

| Χ  | L   | Н               | L  | HIGH Z           | WRITE           |

| Н  | X   | Х               | Х  | HIGH Z           | Output Disabled |

H = HIGH Voltage Level (2.4 V)

L = LOW Voltage Level (.5 V)

X = Don't Care (HIGH or LOW)

High Z = High-Impedance

# DC Performance Characteristics: Over operating temperature ranges (Note 1)

| Symbol           | Characteristic                            | Min | Тур  | Max       | Unit | Condition                                                                |                                                       |

|------------------|-------------------------------------------|-----|------|-----------|------|--------------------------------------------------------------------------|-------------------------------------------------------|

| VoL              | Output LOW Voltage                        |     | 0.3  | 0.45      | V    | V <sub>CC</sub> = Min, I <sub>OL</sub> = 8 mA                            |                                                       |

| VIH              | Input HIGH Voltage                        | 2.1 | 1.6  |           | V    | Guaranteed Input HIGH Voltage for All Inputs <sup>5</sup>                |                                                       |

| VIL              | Input LOW Voltage                         |     | 1.5  | 0.8       | V    | Guaranteed Infor All Inputs 5                                            | put LOW Voltage                                       |

| Vон              | Output HIGH Voltage                       | 2.4 |      |           | V    | Vcc = Min, IoH                                                           | <sub>H</sub> = −5.2 mA                                |

| lıL              | Input LOW Current                         |     | -150 | -300      | μΑ   | $V_{CC} = Max$ , $V_{IN} = 0.4 V$                                        |                                                       |

| l <sub>ін</sub>  | Input HIGH Current                        |     | 1.0  | 40        | μΑ   | $V_{CC} = Max$ , $V_{IN} = 4.5 V$                                        |                                                       |

| I <sub>IHB</sub> | Input Breakdown Current                   |     |      | 1.0       | mA   | V <sub>CC</sub> = Max, V <sub>IN</sub> = V <sub>CC</sub>                 |                                                       |

| Vic              | Input Diode Clamp Voltage                 |     | -1.0 | -1.5      | V    | V <sub>CC</sub> = Max, I <sub>IN</sub>                                   | =-10 mA                                               |

| lozh<br>lozh     | Output Current (HIGH Z)                   |     |      | 50<br>-50 | μΑ   | $V_{CC} = Max$ , $V_{OUT} = 2.4 V$<br>$V_{CC} = Max$ , $V_{OUT} = 0.5 V$ |                                                       |

| los              | Output Current<br>Short Circuit to Ground | -10 |      | -70       | mA   | V <sub>CC</sub> = Max, Note 3                                            |                                                       |

| Icc              | Power Supply Current                      |     |      | 80<br>90  | mA   | Commercial<br>Military                                                   | V <sub>CC</sub> = Max All Inputs GND All Outputs Open |

#### Note

- Typical values are at V<sub>CC</sub> = 5.0 V. T<sub>C</sub> = +25°C and maximum loading.

- 2. The maximum address access time is guaranteed to be the worst case bit in the memory using a pseudorandom testing pattern.

- 3. Short circuit to ground not to exceed one second.

- 4.  $t_W$  measured at  $t_{WSA}$  = Min.  $t_{WSA}$  measured at  $t_W$  = Min.

- 5. Static condition only.

# Commercial

AC Performance Characteristics: V<sub>CC</sub> = 5.0 V  $\pm$  5%, GND = 0 V, T<sub>C</sub> = 0° C to +75° C

|        |                                                |     | A   | Std |     |      |                    |

|--------|------------------------------------------------|-----|-----|-----|-----|------|--------------------|

| Symbol | Characteristic                                 | Min | Max | Min | Max | Unit | Condition          |

|        | Read Timing                                    |     |     |     |     |      |                    |

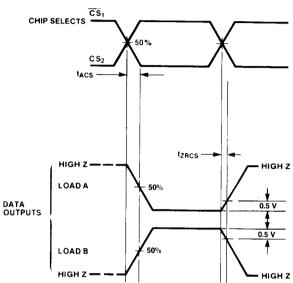

| tacs   | Chip Select Access Time                        |     | 30  |     | 35  | ns   |                    |

| tzrcs  | Chip Select to HIGH Z                          |     | 30  |     | 35  | ns   |                    |

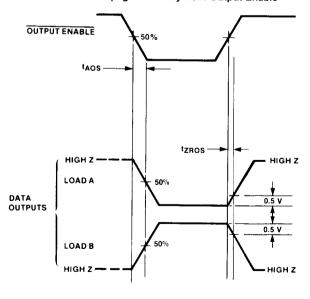

| taos   | Output Enable Access Time                      |     | 30  |     | 35  | ns   | Figures 3a, 3b, 3c |

| tzros  | Output Enable to HIGH Z                        |     | 30  |     | 35  | ns   |                    |

| taa    | Address Access Time <sup>2</sup>               |     | 45  |     | 60  | ns   |                    |

|        | Write Timing                                   |     |     |     |     |      |                    |

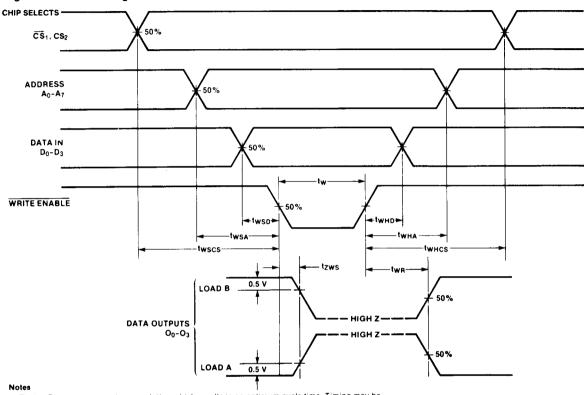

| tw     | Write Pulse Width to Guarantee Writing 4       | 30  |     | 45  | l   | ns   |                    |

| twsp   | Data Setup Time Prior to Write                 | 5   |     | 5   |     | ns   |                    |

| twhp   | Data Hold Time after Write                     | 5   |     | 5   |     | ns   |                    |

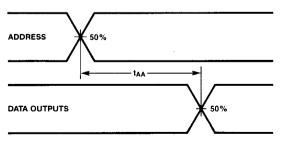

| twsa   | Address Setup Time Prior to Write <sup>4</sup> | 5   |     | 5   |     | ns   | Figure 4           |

| twha   | Address Hold Time after Write                  | 5   |     | 5   |     | ns   |                    |

| twscs  | Chip Select Setup Time Prior to Write          | 5   |     | 5   |     | ns   |                    |

| twncs  | Chip Select Hold Time after Write              | 5   |     | 5   |     | ns   |                    |

| tzws   | Write Enable to HIGH Z                         |     | 35  |     | 40  | ns   |                    |

| twn    | Write Recovery Time                            |     | 40  |     | 45  | ns   |                    |

# Military

AC Performance Characteristics: VCC = 5.0 V  $\pm$  10%, GND = 0 V, TC =  $-55^{\circ}$  C to  $+125^{\circ}$  C

|        |                                                | A Std |      | td  |     |      |                    |

|--------|------------------------------------------------|-------|------|-----|-----|------|--------------------|

| Symbol | Characteristic                                 | Min   | Max  | Min | Max | Unit | Condition          |

|        | Read Timing                                    |       |      |     |     |      |                    |

| tacs   | Chip Select Access Time                        |       | 40   |     | 45  | ns   |                    |

| tzrcs  | Chip Select to HIGH Z                          |       | 40   |     | 45  | ns   |                    |

| taos   | Output Enable Access Time                      |       | 40   |     | 45  | ns   | Figures 3a, 3b, 3c |

| tzros  | Output Enable to HIGH Z                        |       | 40   |     | 45  | ns   |                    |

| taa    | Address Access Time <sup>2</sup>               |       | (55) | (   | 75  | ns   |                    |

|        | Write Timing                                   |       |      |     |     |      |                    |

| tw     | Write Pulse Width to Guarantee Writing 4       | 40    |      | 55  |     | ns   |                    |

| twsp   | Data Setup Time Prior to Write                 | 5     |      | 5   |     | ns   |                    |

| twhD   | Data Hold Time after Write                     | 5     |      | 5   |     | ns   |                    |

| twsa   | Address Setup Time Prior to Write <sup>4</sup> | 5     |      | 5   |     | ns   | Figure 4           |

| twha   | Address Hold Time after Write                  | 5     |      | 5   |     | ns   |                    |

| twscs  | Chip Select Setup Time Prior to Write          | 5     |      | 5   |     | ns   |                    |

| twncs  | Chip Select Hold Time after Write              | 5     |      | 5   |     | ns   |                    |

| tzws   | Write Enable to HIGH Z                         |       | 45   |     | 45  | ns   |                    |

| twn    | Write Recovery Time                            |       | 50   |     | 50  | ns   |                    |

Notes on preceding page

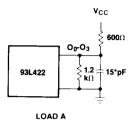

Fig. 1 AC Test Output Load

\*Includes jig and probe capacitance

Note: Load A is used for all production testing.

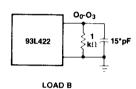

Fig. 2 AC Test Input Levels

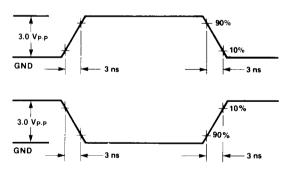

Fig. 3 Read Mode Timing

3a Read Mode Propagation Delay from Address

# 3b Read Mode Propagation Delay from Chip Select

# 3c Read Mode Propagation Delay from Output Enable

Fig. 4 Write Mode Timing

- Timing Diagram represents one solution which results in an optimum cycle time. Timing may be changed to fit various applications as long as the worst case limits are not violated.

- 2. Input voltage levels for worst case AC test are 3.0/0.0 V.

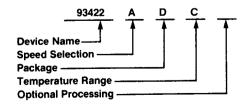

# **Ordering Information**

# Speed Selection

Blank = Standard Speed A = 'A' Grade

## Packages and Outlines (See Section 9)

D = Ceramic DIP

F = Flatpak

L = Leadless Chip Carrier

P = Plastic DIP

#### Temperature Range

C = 0°C to +75°C M = -55°C to +125°C

## **Optional Processing**

QB = Mil Std 883

Method 5004 and 5005, Level B QR = Commercial Device with

160 Hour Burn In or Equivalent