# Four Output Differential Buffer for PCI-Express

#### **Recommended Application:**

DB400 Intel Yellow Cover part with PCI-Express support.

#### **Output Features:**

- 4 0.7V current-mode differential output pairs

- Supports zero delay buffer mode and fanout mode

- Bandwidth programming available

#### **Key Specifications:**

- Outputs cycle-cycle jitter: < 50ps

- Outputs skew: < 50ps

- +/- 300ppm frequency accuracy on output clocks

#### Features/Benefits:

- Supports tight ppm accuracy clocks for Serial-ATA

- Spread spectrum modulation tolerant, 0 to -0.5% down spread and +/- 0.25% center spread

- 28-p Supports undriven differential output pair in PD# and SRC\_STOP# for power management.

#### **Pin Configuration**

| DIF_1<br>DIF_1#<br>OE_1<br>DIF_2<br>DIF_2#<br>VDD | 2 27<br>3 26<br>4 25<br>5 24<br>6 23<br>7 22<br>8 21<br>9 20<br>10 19<br>11 18<br>12 17<br>13 | VDDA<br>GNDA<br>IREF<br>GND<br>VDD<br>DIF_6<br>DIF_6#<br>OE_6<br>DIF_5<br>DIF_5#<br>VDD<br>HIGH_BW#<br>SRC_STOP#<br>PD# |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

|---------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

28-pin SSOP & TSSOP

# **Pin Description**

| PIN# | PIN NAME    | PIN TYPE | DESCRIPTION                                                                                                                                                                                                                           |

|------|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | VDD         | PWR      | Power supply, nominal 3.3V                                                                                                                                                                                                            |

| 2    | SRC_IN      | IN       | 0.7 V Differential SRC TRUE input                                                                                                                                                                                                     |

| 3    | SRC_IN#     | IN       | 0.7 V Differential SRC COMPLEMENTARY input                                                                                                                                                                                            |

| 4    | GND         | PWR      | Ground pin.                                                                                                                                                                                                                           |

| 5    | VDD         | PWR      | Power supply, nominal 3.3V                                                                                                                                                                                                            |

| 6    | DIF_1       | OUT      | 0.7V differential true clock outputs                                                                                                                                                                                                  |

| 7    | DIF_1#      | OUT      | 0.7V differential complement clock outputs                                                                                                                                                                                            |

| 8    | OE_1        | IN       | Active high input for enabling outputs.  0 = tri-state outputs, 1= enable outputs                                                                                                                                                     |

| 9    | DIF_2       | OUT      | 0.7V differential true clock outputs                                                                                                                                                                                                  |

| 10   | <br>DIF_2#  | OUT      | 0.7V differential complement clock outputs                                                                                                                                                                                            |

| 11   | VDD         | PWR      | Power supply, nominal 3.3V                                                                                                                                                                                                            |

| 12   | BYPASS#/PLL | IN       | Input to select Bypass(fan-out) or PLL (ZDB) mode 0 = Bypass mode, 1= PLL mode                                                                                                                                                        |

| 13   | SCLK        | IN       | Clock pin of SMBus circuitry, 5V tolerant.                                                                                                                                                                                            |

| 14   | SDATA       | I/O      | Data pin for SMBus circuitry, 5V tolerant.                                                                                                                                                                                            |

| 15   | PD#         | IN       | Asynchronous active low input pin used to power down the device. The internal clocks are disabled and the VCO and the crystal are stopped.                                                                                            |

| 16   | SRC_STOP#   | IN       | Active low input to stop diff outputs.                                                                                                                                                                                                |

| 17   | HIGH_BW#    | IN       | 3.3V input for selecting PLL Band Width 0 = High, 1= Low                                                                                                                                                                              |

| 18   | VDD         | PWR      | Power supply, nominal 3.3V                                                                                                                                                                                                            |

| 19   | DIF_5#      | OUT      | 0.7V differential complement clock outputs                                                                                                                                                                                            |

| 20   | DIF_5       | OUT      | 0.7V differential true clock outputs                                                                                                                                                                                                  |

| 21   | OE_6        | IN       | Active high input for enabling outputs.  0 = tri-state outputs, 1= enable outputs                                                                                                                                                     |

| 22   | DIF_6#      | OUT      | 0.7V differential complement clock outputs                                                                                                                                                                                            |

| 23   | DIF_6       | OUT      | 0.7V differential true clock outputs                                                                                                                                                                                                  |

| 24   | VDD         | PWR      | Power supply, nominal 3.3V                                                                                                                                                                                                            |

| 25   | GND         | PWR      | Ground pin.                                                                                                                                                                                                                           |

| 26   | IREF        | OUT      | This pin establishes the reference current for the differential current-mode output pairs. This pin requires a fixed precision resistor tied to ground in order to establish the appropriate current. 475 ohms is the standard value. |

| 27   | GNDA        | PWR      | Ground pin for the PLL core.                                                                                                                                                                                                          |

| 28   | VDDA        | PWR      | 3.3V power for the PLL core.                                                                                                                                                                                                          |

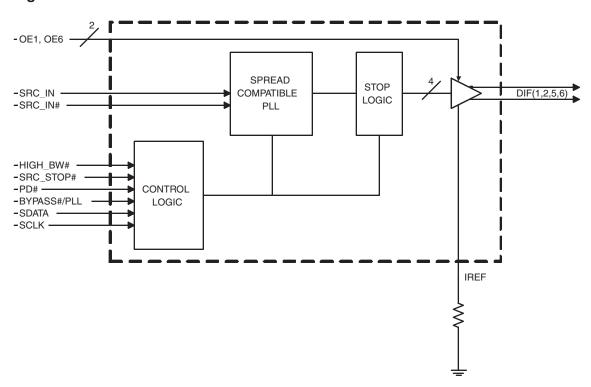

## **General Description**

ICS9DB104 follows the Intel DB400 Differential Buffer Specification. This buffer provides four SRC clocks for PCI-Express, next generation I/O devices. ICS9DB104 is driven by a differential input pair from a CK409/CK410 main clock generator, such as the ICS952601 or ICS954101. ICS9DB104 can run at speeds up to 200MHz. It provides ouputs meeting tight cycle-to-cycle jitter (50ps) and output-to-output skew (50ps) requirements.

# **Block Diagram**

## **Power Groups**

| Pin N      | lumber | Description                   |  |  |  |

|------------|--------|-------------------------------|--|--|--|

| VDD        | GND    | Description                   |  |  |  |

| 1          | 4      | SRC_IN/SRC_IN#                |  |  |  |

| 5,11,18,24 | 4,25   | DIF Outputs                   |  |  |  |

| 28         | 27     | IREF                          |  |  |  |

| 28         | 27     | Analog VDD & GND for PLL core |  |  |  |

## **Absolute Max**

| Symbol   | Parameter                 | Min     | Max           | Units |

|----------|---------------------------|---------|---------------|-------|

| VDD_A    | 3.3V Core Supply Voltage  |         | 4.6           | V     |

| VDD_In   | 3.3V Logic Supply Voltage |         | 4.6           | V     |

| $V_{IL}$ | Input Low Voltage         | GND-0.5 |               | V     |

| $V_{IH}$ | Input High Voltage        |         | $V_{DD}+0.5V$ | V     |

| Ts       | Storage Temperature       | -65     | 150           | °C    |

| Tambient | Ambient Operating Temp    | 0       | 70            | °C    |

| Tcase    | Case Temperature          |         | 115           | °C    |

|          | Input ESD protection      |         |               |       |

| ESD prot | human body model          | 2000    |               | V     |

# **Electrical Characteristics - Input/Supply/Common Output Parameters**

$T_A = 0 - 70$ °C; Supply Voltage  $V_{DD} = 3.3 \text{ V +/-5}\%$

| PARAMETER                        | SYMBOL               | CONDITIONS                                                        | MIN       | TYP                | MAX            | UNITS | NOTES |

|----------------------------------|----------------------|-------------------------------------------------------------------|-----------|--------------------|----------------|-------|-------|

| Input High Voltage               | V <sub>IH</sub>      | 3.3 V +/-5%                                                       | 2         |                    | $V_{DD} + 0.3$ | V     |       |

| Input Low Voltage                | $V_{IL}$             | 3.3 V +/-5%                                                       | GND - 0.3 |                    | 0.8            | V     |       |

| Input High Current               | I <sub>IH</sub>      | $V_{IN} = V_{DD}$                                                 | -5        |                    | 5              | uA    |       |

| lanut lanu Commant               | I <sub>IL1</sub>     | V <sub>IN</sub> = 0 V; Inputs with no pull-up resistors           | -5        |                    |                | uA    |       |

| Input Low Current                | I <sub>IL2</sub>     | $V_{IN} = 0 V$ ; Inputs with pull-up resistors                    | -200      |                    |                | uA    |       |

| Operating Supply Current         | I <sub>DD3.3OP</sub> | Full Active, $C_L = Full load$ ;                                  |           |                    | 200            | mA    |       |

| Powerdown Current                | I <sub>DD3.3PD</sub> | all diff pairs driven                                             |           |                    | 40             | mA    |       |

| 1 owerdown Current               | טאנ.נטטי             | all differential pairs tri-stated                                 |           |                    | 12             | mA    |       |

| Input Frequency <sup>3</sup>     | Fi                   | $V_{DD} = 3.3 \text{ V}$                                          | 80        | 100/133<br>166/200 | 220            | MHz   | 3     |

| Pin Inductance <sup>1</sup>      | $L_{pin}$            |                                                                   |           |                    | 7              | nΗ    | 1     |

| Input Capacitance <sup>1</sup>   | $C_{IN}$             | Logic Inputs                                                      | 1.5       |                    | 5              | рF    | 1     |

| input Capacitance                | $C_OUT$              | Output pin capacitance                                            |           |                    | 6              | pF    | 1     |

| PLL Bandwidth                    | BW                   | PLL Bandwidth when PLL BW=0                                       |           | 4                  |                | MHz   | 1     |

| PLL Bandwidth                    | DVV                  | PLL Bandwidth when PLL BW=1                                       |           | 2                  |                | MHz   | 1     |

|                                  |                      | From V <sub>DD</sub> Power-Up and after                           |           |                    |                |       |       |

| Clk Stabilization <sup>1,2</sup> | $T_{STAB}$           | input clock stabilization or de-<br>assertion of PD# to 1st clock |           |                    | 1              | ms    | 1,2   |

| Modulation Frequency             |                      | Triangular Modulation                                             | 30        |                    | 33             | kHz   | 1     |

| Tdrive_SRC_STOP#                 |                      | DIF output enable after SRC_Stop# de-assertion                    | - 50      |                    | 10             | ns    | 1,3   |

| Tdrive_PD#                       |                      | DIF output enable after PD# de-assertion                          |           |                    | 300            | us    | 1,3   |

| Tfall                            |                      | Fall time of PD# and<br>SRC_STOP#                                 |           |                    | 5              | ns    | 1     |

| Trise                            |                      | Rise time of PD# and<br>SRC_STOP#                                 |           |                    | 5              | ns    | 2     |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup>See timing diagrams for timing requirements. <sup>3</sup>Time from deassertion until outputs are >200 mV

## **Electrical Characteristics - DIF 0.7V Current Mode Differential Pair**

$T_{A} = 0 - 70^{\circ}C; \ V_{DD} = 3.3 \ V \ + / -5\%; \ C_{L} = 2pF, \ R_{S} = 33.2\Omega, \ R_{P} = 49.9\Omega, \ I_{REF} = 475\Omega$

| PARAMETER                          | SYMBOL                | CONDITIONS                                                        | MIN    | TYP | MAX     | UNITS | NOTES |

|------------------------------------|-----------------------|-------------------------------------------------------------------|--------|-----|---------|-------|-------|

| Current Source Output<br>Impedance | Zo <sup>1</sup>       | $V_O = V_x$                                                       | 3000   |     |         | Ω     | 1     |

| Voltage High                       | VHigh                 | Statistical measurement on single ended signal using oscilloscope | 660    |     | 850     | mV    | 1,3   |

| Voltage Low                        | VLow                  | math function.                                                    | -150   |     | 150     | 1110  | 1,3   |

| Max Voltage                        | Vovs                  | Measurement on single ended                                       |        |     | 1150    | mV    | 1     |

| Min Voltage                        | Vuds                  | signal using absolute value.                                      | -300   |     |         | IIIV  | 1     |

| Crossing Voltage (abs)             | Vcross(abs)           |                                                                   | 250    |     | 550     | mV    | 1     |

| Crossing Voltage (var)             | d-Vcross              | Variation of crossing over all edges                              |        |     | 140     | mV    | 1     |

| Long Accuracy                      | ppm                   | see Tperiod min-max values                                        |        |     | 0       | ppm   | 1,2   |

|                                    |                       | 200MHz nominal                                                    | 4.9985 |     | 5.0015  | ns    | 2     |

|                                    |                       | 200MHz spread                                                     | 4.9985 |     | 5.0266  | ns    | 2     |

|                                    | period Tperiod        | 166.66MHz nominal                                                 | 5.9982 |     | 6.0018  | ns    | 2     |

| Average period                     |                       | 166.66MHz spread                                                  | 5.9982 |     | 6.0320  | ns    | 2     |

| Average period                     |                       | 133.33MHz nominal                                                 | 7.4978 |     | 7.5023  | ns    | 2     |

|                                    |                       | 133.33MHz spread                                                  | 7.4978 |     | 5.4000  | ns    | 2     |

|                                    |                       | 100.00MHz nominal                                                 | 9.9970 |     | 10.0030 | ns    | 2     |

|                                    |                       | 100.00MHz spread                                                  | 9.9970 |     | 10.0533 | ns    | 2     |

|                                    |                       | 200MHz nominal                                                    | 4.8735 |     |         | ns    | 1,2   |

| Absolute min period                | $T_{absmin}$          | 166.66MHz nominal/spread                                          | 5.8732 |     |         | ns    | 1,2   |

| Absolute IIIII period              | absmin                | 133.33MHz nominal/spread                                          | 7.3728 |     |         | ns    | 1,2   |

|                                    |                       | 100.00MHz nominal/spread                                          | 9.8720 |     |         | ns    | 1,2   |

| Rise Time                          | t <sub>r</sub>        | $V_{OL} = 0.175V, V_{OH} = 0.525V$                                | 175    |     | 700     | ps    | 1     |

| Fall Time                          | t <sub>f</sub>        | $V_{OH} = 0.525 V V_{OL} = 0.175 V$                               | 175    |     | 700     | ps    | 1     |

| Rise Time Variation                | d-t <sub>r</sub>      |                                                                   |        |     | 125     | ps    | 1     |

| Fall Time Variation                | d-t <sub>f</sub>      |                                                                   |        |     | 125     | ps    | 1     |

| Duty Cycle                         | d <sub>t3</sub>       | Measurement from differential wavefrom                            | 45     |     | 55      | %     | 1     |

| Skew                               | t <sub>sk3</sub>      | V <sub>T</sub> = 50%                                              |        |     | 50      | ps    | 1     |

| Jitter, Cycle to cycle             | t <sub>jcyc-cyc</sub> | PLL mode,<br>Measurement from differential<br>wavefrom            |        |     | 50      | ps    | 1     |

|                                    |                       | BYPASS mode as additive jitter                                    |        |     | 50      | ps    | 1     |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup> All Long Term Accuracy and Clock Period specifications are guaranteed with the assumption that the input clock complies with CK409/CK410 accuracy requirements

$<sup>^{3}</sup>I_{REF} = V_{DD}/(3xR_{R})$ . For  $R_{R} = 475\Omega$  (1%),  $I_{REF} = 2.32mA$ .  $I_{OH} = 6~x~I_{REF}$  and  $V_{OH} = 0.7V~@~Z_{O} = 50\Omega$ .

# General SMBus serial interface information for the ICS9DB104

## **How to Write:**

- · Controller (host) sends a start bit.

- Controller (host) sends the write address DC (h)

- ICS clock will acknowledge

- Controller (host) sends the begining byte location = N

- ICS clock will acknowledge

- Controller (host) sends the data byte count = X

- ICS clock will acknowledge

- Controller (host) starts sending Byte N through Byte N + X -1

- ICS clock will acknowledge each byte one at a time

- Controller (host) sends a Stop bit

| Ind   | ex Block W                  | /rit                 | e Operation        |

|-------|-----------------------------|----------------------|--------------------|

| Cor   | ntroller (Host)             | ICS (Slave/Receiver) |                    |

| Т     | starT bit                   |                      |                    |

| Slav  | e Address DC <sub>(h)</sub> |                      |                    |

| WR    | WRite                       |                      |                    |

|       |                             |                      | ACK                |

| Begi  | nning Byte = N              |                      |                    |

|       |                             |                      | ACK                |

| Data  | Byte Count = X              |                      |                    |

|       |                             |                      | ACK                |

| Begir | ning Byte N                 |                      |                    |

|       |                             |                      | ACK                |

|       | $\Diamond$                  | ′te                  |                    |

|       | $\Diamond$                  | X Byte               | $\diamond$         |

|       | <b>\Q</b>                   | ×                    | <b>\rightarrow</b> |

|       |                             |                      | <b>\Q</b>          |

| Byte  | e N + X - 1                 |                      |                    |

|       |                             |                      | ACK                |

| Р     | stoP bit                    |                      |                    |

### How to Read:

- Controller (host) will send start bit.

- Controller (host) sends the write address DC (h)

- ICS clock will acknowledge

- Controller (host) sends the begining byte location = N

- ICS clock will acknowledge

- Controller (host) will send a separate start bit.

- Controller (host) sends the read address DD (h)

- ICS clock will acknowledge

- ICS clock will send the data byte count = X

- ICS clock sends Byte N + X -1

- ICS clock sends Byte 0 through byte X (if X<sub>(h)</sub> was written to byte 8).

- · Controller (host) will need to acknowledge each byte

- Controllor (host) will send a not acknowledge bit

- · Controller (host) will send a stop bit

| Ind      | ex Block Rea              | ad                  | Operation          |  |  |

|----------|---------------------------|---------------------|--------------------|--|--|

|          | troller (Host)            | IC                  | S (Slave/Receiver) |  |  |

| Т        | starT bit                 |                     |                    |  |  |

| Slave    | Address DC <sub>(h)</sub> |                     |                    |  |  |

| WR       | WRite                     |                     |                    |  |  |

|          |                           |                     | ACK                |  |  |

| Begir    | nning Byte = N            |                     |                    |  |  |

|          |                           |                     | ACK                |  |  |

| RT       | Repeat starT              |                     |                    |  |  |

| Slave    | Address DD <sub>(h)</sub> |                     |                    |  |  |

| RD       | ReaD                      |                     |                    |  |  |

|          |                           | ACK                 |                    |  |  |

|          |                           |                     |                    |  |  |

|          |                           | Data Byte Count = X |                    |  |  |

|          | ACK                       |                     |                    |  |  |

|          |                           |                     | Beginning Byte N   |  |  |

|          | ACK                       |                     |                    |  |  |

|          |                           | /te                 | <b>\Q</b>          |  |  |

|          | <b>O</b>                  | X Byte              | <b>\Q</b>          |  |  |

|          | <b>O</b>                  | ×                   | <b>\Q</b>          |  |  |

| <b>O</b> |                           |                     |                    |  |  |

|          |                           |                     | Byte N + X - 1     |  |  |

| N        | Not acknowledge           |                     |                    |  |  |

| Р        | stoP bit                  |                     |                    |  |  |

SMBus Table: Frequency Select Register, READ/WRITE ADDRESS (DC/DD)

| Byte 0 |   | Pin # | Name   | Control Function | Туре | 0        | 1      | PWD |

|--------|---|-------|--------|------------------|------|----------|--------|-----|

| Bit 7  | - |       | PD# dr | ive mode         | RW   | driven   | Hi-Z   | 0   |

| Bit 6  | - |       | SRC_S  | top# drive       | RW   | driven   | Hi-Z   | 0   |

| Bit 5  | - |       | Res    | erved            | RW   | Rese     | erved  | Χ   |

| Bit 4  | - |       | Res    | erved            | RW   | Reserved |        | Χ   |

| Bit 3  | - |       | Res    | erved            | RW   | Rese     | erved  | Χ   |

| Bit 2  | - |       | PLL_B\ | N# adjust        | RW   | High BW  | Low BW | 1   |

| Bit 1  | - |       | BYPA   | SS#/PLL          | RW   | fan-out  | ZDB    | 1   |

| Bit 0  | - | ·     | SRC    | _DIV#            | RW   | div /2   | x1     | 1   |

**SMBus Table: Output Control Register**

| Byt   | Byte 1 Pin # |   | Name  | Control<br>Function | Туре | 0                                       | 1                          | PWD |

|-------|--------------|---|-------|---------------------|------|-----------------------------------------|----------------------------|-----|

| Bit 7 | -            |   | Res   | Reserved            |      | User should write '0' to minimize power |                            | 1   |

| Bit 6 | 23,2         | 2 | DIF_6 | Output<br>Control   | RW   | Disable                                 | Enable                     | 1   |

| Bit 5 | 20,1         | 9 | DIF_5 | Output<br>Control   | RW   | Disable                                 | Enable                     | 1   |

| Bit 4 | -            |   | Res   | erved               | RW   | User should write '( to minimize power  |                            | 1   |

| Bit 3 | -            |   | Res   | erved               | RW   |                                         | uld write '0'<br>ize power | 1   |

| Bit 2 | 9,10         | ) | DIF_2 | Output<br>Control   | RW   | Disable                                 | Enable                     | 1   |

| Bit 1 | 6,7          |   | DIF_1 | Output<br>Control   | RW   | Disable Enable                          |                            | 1   |

| Bit 0 | -            |   | Res   | erved               | RW   | User should write '0' to minimize power |                            | 1   |

**SMBus Table: Output Control Register**

| Byte 2 Pin # |       |   | Name     | Control<br>Function | Туре | 0        | 1         | PWD |

|--------------|-------|---|----------|---------------------|------|----------|-----------|-----|

| Bit 7        | -     |   | Res      | erved               | RW   | Res      | erved     | 0   |

| Bit 6        | 23,22 |   | DIF_6    | Output<br>Control   | RW   | Free-run | Stoppable | 0   |

| Bit 5        | 20,19 |   | DIF_5    | Output<br>Control   | RW   | Free-run | Stoppable | 0   |

| Bit 4        | •     |   | Res      | erved               | RW   | Reserved |           | 0   |

| Bit 3        | •     |   | Reserved |                     | RW   | Reserved |           | 0   |

| Bit 2        | 9,10  | ) | DIF_2    | Output<br>Control   | RW   | Free-run | Stoppable | 0   |

| Bit 1        | 6,7   |   | DIF_1    | Output<br>Control   | RW   | Free-run | Stoppable | 0   |

| Bit 0        | -     |   | Res      | erved               | RW   | Res      | erved     | 0   |

**SMBus Table: Output Control Register**

|            | abioi o ditpe |       |          |                  |      |          |       |   |     |

|------------|---------------|-------|----------|------------------|------|----------|-------|---|-----|

| Byte 3 Pir |               | Pin # | Name     | Control Function | Туре | 0        | 1     |   | PWD |

| Bit 7      |               |       | Res      | served           | RW   | Rese     | erved |   | Χ   |

| Bit 6      |               |       | Res      | served           | RW   | Rese     | erved |   | Χ   |

| Bit 5      | 5             |       | Reserved |                  | RW   | Reserved |       | Х |     |

| Bit 4      |               |       | Res      | served           | RW   | Rese     | erved |   | Χ   |

| Bit 3      |               |       | Res      | served           | RW   | Rese     | erved |   | Х   |

| Bit 2      |               |       | Res      | served           | RW   | Reserved |       |   | Х   |

| Bit 1      |               | ·     | Res      | served           | RW   | Reserved |       | Χ |     |

| Bit 0      |               | ·     | Res      | served           | RW   | Res      | erved |   | Х   |

SMBus Table: Vendor & Revision ID Register

| Byt   | e 4 | Pin # | Name | Control<br>Function | Туре | 0 | 1 | PWD |

|-------|-----|-------|------|---------------------|------|---|---|-----|

| Bit 7 | •   |       | RID3 |                     | R    | ı | • | Х   |

| Bit 6 | ı   |       | RID2 | REVISION            | R    | ı | • | Х   |

| Bit 5 | ı   |       | RID1 | ID                  | R    | ı | • | Х   |

| Bit 4 | ı   |       | RID0 |                     | R    | ı | • | Х   |

| Bit 3 | -   |       | VID3 |                     | R    | - | - | 0   |

| Bit 2 | -   |       | VID2 | VENDOR              | R    | - | - | 0   |

| Bit 1 | -   |       | VID1 | ID                  | R    | - | - | 0   |

| Bit 0 | 1   |       | VID0 |                     | R    | 1 | - | 1   |

SMBus Table: DEVICE ID

| Byte 5 Pin |         | Pin # | Name              | Control<br>Function | Туре | 0        | 1        | PWD |

|------------|---------|-------|-------------------|---------------------|------|----------|----------|-----|

| Bit 7      | Bit 7 - |       | Device ID 7 (MSB) |                     | RW   | Res      | erved    | 0   |

| Bit 6      | Bit 6 - |       | Device ID 6       |                     | RW   | Reserved |          | 0   |

| Bit 5      | Bit 5 - |       | Device ID 5       |                     | RW   | Reserved |          | 0   |

| Bit 4      | 4 -     |       | Device ID 4       |                     | RW   | Res      | Reserved |     |

| Bit 3      | Bit 3 - |       | Device ID 3       |                     | RW   | Rese     | erved    | 1   |

| Bit 2      | Bit 2 - |       | Device ID 2       |                     | RW   | Reserved |          | 0   |

| Bit 1      | -       |       | Device ID 1       |                     | RW   | Reserved |          | 0   |

| Bit 0      | -       |       | Device ID 0       |                     | RW   | Reserved |          | 0   |

SMBus Table: Byte Count Register

| ome do rabio. Eyto ocum riogisto. |      |       |      |                          |      |   |   |     |

|-----------------------------------|------|-------|------|--------------------------|------|---|---|-----|

| Byt                               | te 6 | Pin # | Name | Control<br>Function      | Туре | 0 | 1 | PWD |

| Bit 7                             | -    |       | BC7  | Writing to               | RW   | ı | • | 0   |

| Bit 6                             | -    |       | BC6  | Writing to this register | RW   | - | - | 0   |

| Bit 5                             | -    |       | BC5  | configures               | RW   | - | - | 0   |

| Bit 4                             | -    |       | BC4  | how many                 | RW   | ı | 1 | 0   |

| Bit 3                             | -    |       | BC3  | bytes will               | RW   | ı | 1 | 0   |

| Bit 2                             | -    |       | BC2  | be read                  | RW   | ı | - | 1   |

| Bit 1                             | -    |       | BC1  | be read<br>back.         | RW   | - | - | 0   |

| Bit 0                             | -    |       | BC0  | Dack.                    | RW   | - | - | 1   |

0767E-12/14/07

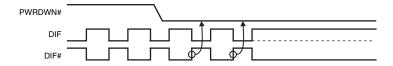

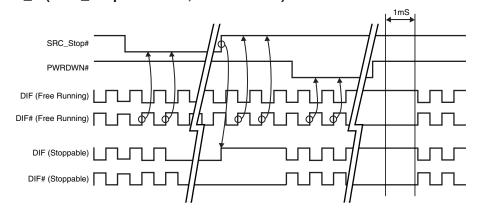

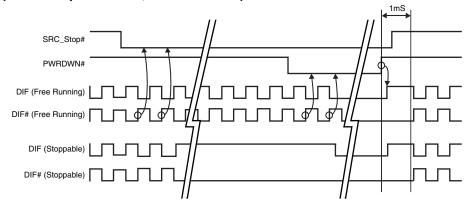

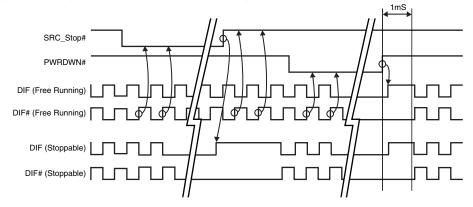

#### PD#

The PD# pin cleanly shuts off all clocks and places the device into a power saving mode. PD# must be asserted before shutting off the input clock or power to insure an orderly shutdown. PD is asynchronous active-low input for both powering down the device and powering up the device. When PD# is asserted, all clocks will be driven high, or tri-stated (depending on the PD# drive mode and Output control bits) before the PLL is shut down.

#### PD# Assertion

When PD# is sampled low by two consecutive rising edges of DIF#, all DIF outputs must be held High, or tri-stated (depending on the PD# drive mode and Output control bits) on the next High-Low transition of the DIF# outputs. When the PD# drive mode bit is set to '0', all clock outputs will be held with DIF driven High with 2 x I<sub>REF</sub> and DIF# tri-stated. If the PD# drive mode bit is set to '1', both DIF and DIF# are tri-stated.

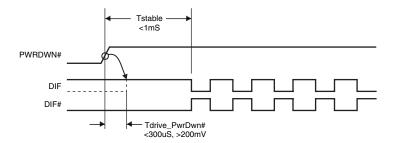

#### PD# De-assertion

Power-up latency is less than 1 ms. This is the time from de-assertion of the PD# pin, or VDD reaching 3.3V, or the time from valid SRC\_IN clocks until the time that stable clocks are output from the device (PLL Locked). If the PD# drive mode bit is set to '1', all the DIF outputs must driven to a voltage of >200 mV within 300 ms of PD# de-assertion.

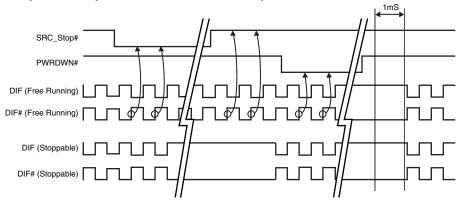

#### SRC STOP#

The SRC\_STOP# signal is an active-low asynchronous input that cleanly stops and starts the DIF outputs. A valid clock must be present on SRC\_IN for this input to work properly. The SRC\_STOP# signal is de-bounced and must remain stable for two consecutive rising edges of DIF# to be recognized as a valid assertion or de-assertion.

## SRC\_STOP# - Assertion (transition from '1' to '0')

Asserting SRC\_STOP# causes all DIF outputs to stop after their next transition (if the control register settings allow the output to stop). When the SRC\_STOP# drive bit is '0', the final state of all stopped DIF outputs is DIF = High and DIF# = Low. There is no change in output drive current. DIF is driven with 6xI<sub>REF</sub> DIF# is not driven, but pulled low by the termination. When the SRC\_STOP# drive bit is '1', the final state of all DIF output pins is Low. Both DIF and DIF# are not driven.

## SRC\_STOP# - De-assertion (transition from '0' to '1')

All stopped differential outputs resume normal operation in a glitch-free manner. The de-assertion latency to active outputs is 2-6 DIF clock periods, with all DIF outputs resuming simultaneously. If the SRC\_STOP# drive control bit is '1' (tri-state), all stopped DIF outputs must be driven High (>200 mV) within 10 ns of de-assertion.

### SRC\_STOP\_1 (SRC\_Stop = Driven, PD = Driven)

# SRC\_STOP\_2 (SRC\_Stop =Tristate, PD = Driven)

# SRC\_STOP\_3 (SRC\_Stop = Driven, PD = Tristate)

# SRC\_STOP\_4 (SRC\_Stop = Tristate, PD = Tristate)

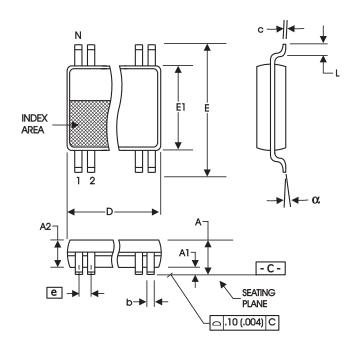

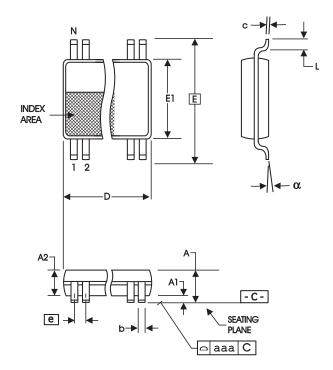

| 209 mil SSOP |          |            |                   |          |  |  |  |  |

|--------------|----------|------------|-------------------|----------|--|--|--|--|

|              | In Mill  | limeters   | In Inches         |          |  |  |  |  |

| SYMBOL       | COMMON I | DIMENSIONS | COMMON DIMENSIONS |          |  |  |  |  |

|              | MIN      | MAX        | MIN               | MAX      |  |  |  |  |

| Α            |          | 2.00       | -                 | .079     |  |  |  |  |

| A1           | 0.05     |            | .002              |          |  |  |  |  |

| A2           | 1.65     | 1.85       | .065              | .073     |  |  |  |  |

| b            | 0.22     | 0.38       | .009              | .015     |  |  |  |  |

| С            | 0.09     | 0.25       | .0035             | .010     |  |  |  |  |

| D            | SEE VA   | RIATIONS   | SEE VA            | RIATIONS |  |  |  |  |

| E            | 7.40     | 8.20       | .291              | .323     |  |  |  |  |

| E1           | 5.00     | 5.60       | .197              | .220     |  |  |  |  |

| е            | 0.65     | BASIC      | 0.0256 BASIC      |          |  |  |  |  |

| L            | 0.55     | 0.95       | .022              | .037     |  |  |  |  |

#### **VARIATIONS**

| N  | D    | mm.   | D (inch) |      |  |

|----|------|-------|----------|------|--|

|    | MIN  | MAX   | MIN      | MAX  |  |

| 28 | 9.90 | 10.50 | .390     | .413 |  |

SEE

0°

Reference Doc.: JEDEC Publication 95, MO-150

10-0033

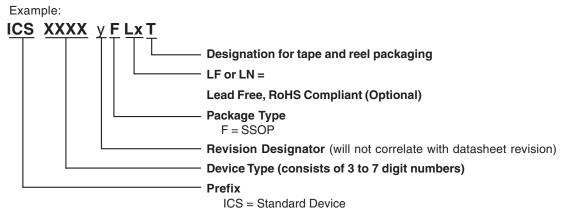

# **Ordering Information**

# ICS9DB104yFLxT

0767E-12/14/07

## 4.40 mm. Body, 0.65 mm. Pitch TSSOP (25.6 mil)

(173 mil)

|        | In Milli | meters    | In Inches         |      |  |

|--------|----------|-----------|-------------------|------|--|

| SYMBOL | COMMON D | IMENSIONS | COMMON DIMENSIONS |      |  |

|        | MIN      | MAX       | MIN               | MAX  |  |

| Α      |          | 1.20      |                   | .047 |  |

| A1     | 0.05     | 0.15      | .002              | .006 |  |

| A2     | 0.80     | 1.05      | .032              | .041 |  |

| b      | 0.19     | 0.30      | .007              | .012 |  |

| С      | 0.09     | 0.20      | .0035             | .008 |  |

| D      | SEE VAF  | RIATIONS  | SEE VARIATIONS    |      |  |

| E      | 6.40 E   | BASIC     | 0.252 BASIC       |      |  |

| E1     | 4.30     | 4.50      | .169              | .177 |  |

| е      | 0.65 E   | BASIC     | 0.0256 BASIC      |      |  |

| L      | 0.45     | 0.75      | .018 .030         |      |  |

# aaa **VARIATIONS**

Ν

| N  | D n  | nm.  | D (inch) |      |  |

|----|------|------|----------|------|--|

|    | MIN  | MAX  | MIN      | MAX  |  |

| 28 | 9.60 | 9.80 | .378     | .386 |  |

0.10

SEE VARIATIONS

.004

0°

SEE VARIATIONS

Reference Doc.: JEDEC Publication 95, MO-153

0°

10-0035

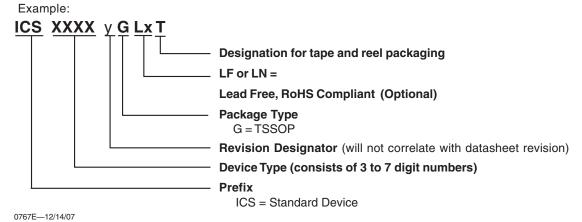

# **Ordering Information**

# ICS9DB104yGLxT

**Revision History**

| Rev. | Issue Date | Description                                  | Page # |

|------|------------|----------------------------------------------|--------|

| D    | 10/26/05   | Updated LF Ordering Information to LN or LF. | 12, 13 |

| Е    | 12/14/07   | Updated SMBus serial Interface Information.  | 6      |

|      |            |                                              |        |

|      |            |                                              |        |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

# **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

www.renesas.com/contact/