# Programmable Timing Control Hub<sup>™</sup> for Next Gen P4<sup>™</sup> Processor

#### Recommended Application:

CK409B clock, Intel Yellow Cover part, Server Applications

#### **Output Features:**

- 4 0.7V current-mode differential CPU pairs

- 1 0.7V current-mode differential SRC pair

- 7 PCI (33MHz)

- 3 PCICLK\_F, (33MHz) free-running

- 1 USB, 48MHz

- 1 DOT, 48MHz

- 2 REF, 14.318MHz

- 4 3V66, 66.66MHz

- 1 VCH/3V66, selectable 48MHz or 66MHz

#### **Key Specifications:**

- CPU/SRC outputs cycle-cycle jitter < 125ps

- 3V66 outputs cycle-cycle jitter < 250ps

- PCI outputs cycle-cycle jitter < 250ps

- CPU outputs skew: < 100ps

- +/- 300ppm frequency accuracy on CPU & SRC clocks

#### Functionality

|      |      |      | CPU                | SRC                | 3V66               | PCI                | REF                | USB/DOT            |

|------|------|------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| B6b5 | FS_A | FS_B | MHz                | MHz                | MHz                | MHz                | MHz                | MHz                |

|      | 0    | 0    | 100                | 100/200            | 66.66              | 33.33              | 14.318             | 48.00              |

|      | 0    | MID  | Ref/N <sub>0</sub> | Ref/N <sub>1</sub> | Ref/N <sub>2</sub> | Ref/N <sub>3</sub> | Ref/N <sub>4</sub> | Ref/N <sub>5</sub> |

| 0    | 0    | 1    | 200                | 100/200            | 66.66              | 33.33              | 14.318             | 48.00              |

| U    | 1    | 0    | 133                | 100/200            | 66.66              | 33.33              | 14.318             | 48.00              |

|      | 1    | 1    | 166                | 100/200            | 66.66              | 33.33              | 14.318             | 48.00              |

|      | 1    | MID  | Hi-Z               | Hi-Z               | Hi-Z               | Hi-Z               | Hi-Z               | Hi-Z               |

|      | 0    | 0    | 200                | 100/200            | 66.66              | 33.33              | 14.318             | 48.00              |

| 1    | 0    | 1    | 400                | 100/200            | 66.66              | 33.33              | 14.318             | 48.00              |

| '    | 1    | 0    | 266                | 100/200            | 66.66              | 33.33              | 14.318             | 48.00              |

|      | 1    | 1    | 333                | 100/200            | 66.66              | 33.33              | 14.318             | 48.00              |

#### Features/Benefits:

- Supports tight ppm accuracy clocks for Serial-ATA

- Supports spread spectrum modulation, 0 to -0.5% down spread and +/- 0.25% center spread

- Supports CPU clks up to 400MHz in test mode

- Uses external 14.318MHz crystal

#### Pin Configuration

|           | 4  | 50                             |            |

|-----------|----|--------------------------------|------------|

| REF0      |    |                                | FS_B       |

| REF1      | 2  |                                | VDDA       |

| VDDREF    |    |                                | GNDA       |

| X1        | -  |                                | GND        |

| X2        |    |                                | IREF       |

| GND       | 6  |                                | FS_A       |

| PCICLK_F0 | 7  | 50                             | CPUCLKT3   |

| PCICLK_F1 | 8  | 49                             | CPUCLKC3   |

| PCICLK_F2 | 9  | 48                             | VDDCPU     |

| VDDPCI    | 10 | 47                             | CPUCLKT2   |

| GND       | 11 | <b>~</b> <sup>46</sup>         | CPUCLKC2   |

| PCICLK0   | 12 | <b>80</b> 45                   | GND        |

| PCICLK1   | 13 | 44<br>45                       | CPUCLKT1   |

| PCICLK2   | 14 | N 43                           | CPUCLKC1   |

| PCICLK3   | 15 | <b>£</b> 42                    | VDDCPU     |

| VDDPCI    | 16 | <b>CE 43</b><br>42<br>41<br>40 | CPUCLKT0   |

| GND       | 17 | <u>0</u> 40                    | CPUCLKC0   |

| PCICLK4   | 18 |                                | GND        |

| PCICLK5   | 19 | 38                             | SRCCLKT    |

| PCICLK6   | 20 | 37                             | SRCCLKC    |

| PD#       | 21 | 36                             | VDD        |

| 3V66_0    | 22 | 35                             | Vtt_PWRGD# |

| 3V66_1    | 23 | 34                             | VDD48      |

| VDD3V66   | 24 | 33                             | GND        |

| GND       | 25 | 32                             | 48MHz_DOT  |

| 3V66_2    | 26 | 31                             | 48MHz_USB  |

| 3V66_3    | 27 | 30                             | SDATA      |

| SCLK      | 28 | 29                             | 3V66_4/VCH |

## 56-pin SSOP & TSSOP

## ICS932S208

## **Pin Description**

| PIN # | PIN NAME  | PIN TYPE | DESCRIPTION                                                            |

|-------|-----------|----------|------------------------------------------------------------------------|

| 1     | REF0      | OUT      | 14.318 MHz reference clock.                                            |

| 2     | REF1      | OUT      | 14.318 MHz reference clock.                                            |

| 3     | VDDREF    | PWR      | Ref, XTAL power supply, nominal 3.3V                                   |

| 4     | X1        | IN       | Crystal input, Nominally 14.318MHz.                                    |

| 5     | X2        | OUT      | Crystal output, Nominally 14.318MHz                                    |

| 6     | GND       | PWR      | Ground pin.                                                            |

| 7     | PCICLK_F0 | OUT      | Free running PCI clock not affected by PCI_STOP# .                     |

| 8     | PCICLK_F1 | OUT      | Free running PCI clock not affected by PCI_STOP# .                     |

| 9     | PCICLK_F2 | OUT      | Free running PCI clock not affected by PCI_STOP# .                     |

| 10    | VDDPCI    | PWR      | Power supply for PCI clocks, nominal 3.3V                              |

| 11    | GND       | PWR      | Ground pin.                                                            |

| 12    | PCICLK0   | OUT      | PCI clock output.                                                      |

| 13    | PCICLK1   | OUT      | PCI clock output.                                                      |

| 14    | PCICLK2   | OUT      | PCI clock output.                                                      |

| 15    | PCICLK3   | OUT      | PCI clock output.                                                      |

| 16    | VDDPCI    | PWR      | Power supply for PCI clocks, nominal 3.3V                              |

| 17    | GND       | PWR      | Ground pin.                                                            |

| 18    | PCICLK4   | OUT      | PCI clock output.                                                      |

| 19    | PCICLK5   | OUT      | PCI clock output.                                                      |

| 20    | PCICLK6   | OUT      | PCI clock output.                                                      |

|       |           |          | Asynchronous active low input pin used to power down the device into a |

| 01    | PD#       | 15.1     | low power state. The internal clocks are disabled and the VCO and the  |

| 21    | PD#       | IN       | crystal are stopped. The latency of the power down will not be greater |

|       |           |          | than 1.8ms. Internal pull-up of 150K nominal.                          |

| 22    | 3V66_0    | OUT      | 3.3V 66.66MHz clock output                                             |

| 23    | 3V66_1    | OUT      | 3.3V 66.66MHz clock output                                             |

| 24    | VDD3V66   | PWR      | Power pin for the 3V66 clocks.                                         |

| 25    | GND       | PWR      | Ground pin.                                                            |

| 26    | 3V66_2    | OUT      | 3.3V 66.66MHz clock output                                             |

| 27    | 3V66_3    | OUT      | 3.3V 66.66MHz clock output                                             |

| 28    | SCLK      | IN       | Clock pin of I2C circuitry 5V tolerant                                 |

## **Pin Description (continued)**

| PIN # | PIN NAME   | PIN TYPE | DESCRIPTION                                                                                                                                                                                                                                     |

|-------|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |            |          | 66.66MHz clock output for AGP support. AGP-PCI should be aligned                                                                                                                                                                                |

| 29    | 3V66_4/VCH | OUT      | with a skew window tolerance of 500ps.                                                                                                                                                                                                          |

|       |            |          | VCH is 48MHz clock output for video controller hub.                                                                                                                                                                                             |

| 30    | SDATA      | I/O      | Data pin for I2C circuitry 5V tolerant                                                                                                                                                                                                          |

| 31    | 48MHz_USB  | OUT      | 48MHz clock output.                                                                                                                                                                                                                             |

| 32    | 48MHz_DOT  | OUT      | 48MHz clock output.                                                                                                                                                                                                                             |

| 33    | GND        | PWR      | Ground pin.                                                                                                                                                                                                                                     |

| 34    | VDD48      | PWR      | Power pin for the 48MHz output.3.3V                                                                                                                                                                                                             |

| 35    | Vtt_PWRGD# | IN       | This 3.3V LVTTL input is a level sensitive strobe used to determine<br>when latch inputs are valid and are ready to be sampled. This is an<br>active low input.                                                                                 |

| 36    | VDD        | PWR      | Power supply for SRC clocks, nominal 3.3V                                                                                                                                                                                                       |

| 37    | SRCCLKC    | OUT      | Complement clock of differential pair for S-ATA support.<br>+/- 300ppm accuracy required.                                                                                                                                                       |

| 38    | SRCCLKT    | OUT      | True clock of differential pair for S-ATA support.<br>+/- 300ppm accuracy required.                                                                                                                                                             |

| 39    | GND        | PWR      | Ground pin.                                                                                                                                                                                                                                     |

| 40    | CPUCLKC0   | OUT      | Complimentary clock of differential pair CPU outputs. These are current mode outputs. External resistors are required for voltage bias.                                                                                                         |

| 41    | CPUCLKT0   | OUT      | True clock of differential pair CPU outputs. These are current mode outputs. External resistors are required for voltage bias.                                                                                                                  |

| 42    | VDDCPU     | PWR      | Supply for CPU clocks, 3.3V nominal                                                                                                                                                                                                             |

| 43    | CPUCLKC1   | OUT      | Complimentary clock of differential pair CPU outputs. These are current mode outputs. External resistors are required for voltage bias.                                                                                                         |

| 44    | CPUCLKT1   | OUT      | True clock of differential pair CPU outputs. These are current mode outputs. External resistors are required for voltage bias.                                                                                                                  |

| 45    | GND        | PWR      | Ground pin.                                                                                                                                                                                                                                     |

| 46    | CPUCLKC2   | OUT      | Complimentary clock of differential pair CPU outputs. These are current mode outputs. External resistors are required for voltage bias.                                                                                                         |

| 47    | CPUCLKT2   | OUT      | True clock of differential pair CPU outputs. These are current mode outputs. External resistors are required for voltage bias.                                                                                                                  |

| 48    | VDDCPU     | PWR      | Supply for CPU clocks, 3.3V nominal                                                                                                                                                                                                             |

| 49    | CPUCLKC3   | OUT      | Complimentary clock of differential pair CPU outputs. These are current mode outputs. External resistors are required for voltage bias.                                                                                                         |

| 50    | CPUCLKT3   | OUT      | True clock of differential pair CPU outputs. These are current mode outputs. External resistors are required for voltage bias.                                                                                                                  |

| 51    | FS_A       | IN       | Frequency select pin, see Frequency table for functionality                                                                                                                                                                                     |

| 52    | IREF       | OUT      | This pin establishes the reference current for the differential current-<br>mode output pairs. This pin requires a fixed precision resistor tied to<br>ground in order to establish the appropriate current. 475 ohms is the<br>standard value. |

| 53    | GND        | PWR      | Ground pin.                                                                                                                                                                                                                                     |

| 54    | GNDA       | PWR      | Ground pin for core.                                                                                                                                                                                                                            |

| 55    | VDDA       | PWR      | 3.3V power for the PLL core.                                                                                                                                                                                                                    |

| 56    | FS_B       | IN       | Frequency select pin, see Frequency table for functionality                                                                                                                                                                                     |

IDT<sup>®</sup> Programmable Timing Control Hub<sup>™</sup> for Next Gen P4<sup>™</sup> Processor

#### **General Description**

**ICS932S208** follows Intel CK409B Yellow Cover specification. This clock synthesizer provides a single chip solution for next generation P4 Intel processors and Intel chipsets. **ICS932S208** is driven with a 14.318MHz crystal. It generates CPU outputs up to 200MHz. It also provides a tight ppm accuracy output for Serial ATA support.

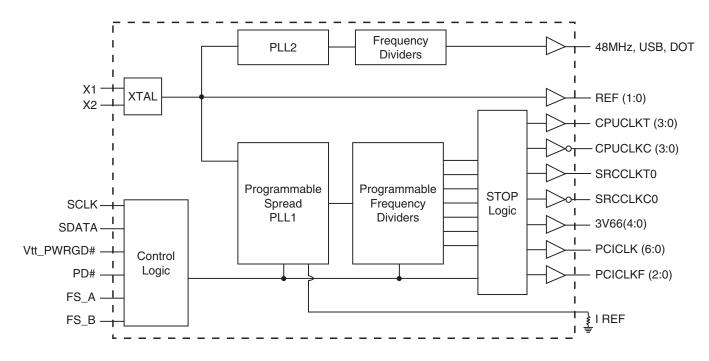

## **Block Diagram**

### **Power Groups**

| Pin N  | lumber | Description              |

|--------|--------|--------------------------|

| VDD    | GND    | Description              |

| 3      | 6      | Xtal, Ref                |

| 24     | 25     | 3V66 [0:4]               |

| 10,16  | 11,17  | PCICLK outputs           |

| 36     | 39     | SRCCLK outputs           |

| 55     | 54     | Master clock, CPU Analog |

| 34     | 33     | 48MHz, PLL               |

| N/A    | 53     | IREF                     |

| 48, 42 | 45     | CPUCLK clocks            |

## Absolute Maximum Ratings

| Symbol   | Parameter                       | Min       | Max             | Units |

|----------|---------------------------------|-----------|-----------------|-------|

| VDD_A    | 3.3V Core Supply Voltage        |           | $V_{DD} + 0.5V$ | V     |

| VDD_In   | 3.3V Logic Input Supply Voltage | GND - 0.5 | $V_{DD} + 0.5V$ | V     |

| Ts       | Storage Temperature             | -65       | 150             | °C    |

| Tambient | Ambient Operating Temp          | 0         | 70              | °C    |

| Tcase    | Case Temperature                |           | 115             | °C    |

|          | Input ESD protection            |           |                 |       |

| ESD prot | human body model                | 2000      |                 | V     |

### **Electrical Characteristics - Input/Supply/Common Output Parameters**

$T_A = 0 - 70^{\circ}C$ ; Supply Voltage  $V_{DD} = 3.3 \text{ V} \pm -5\%$

| PARAMETER                        | SYMBOL               | CONDITIONS                                                            | MIN                   | TYP      | MAX                   | UNITS | NOTES |

|----------------------------------|----------------------|-----------------------------------------------------------------------|-----------------------|----------|-----------------------|-------|-------|

| Input High Voltage               | V <sub>IH</sub>      | 3.3 V +/-5%                                                           | 2                     |          | V <sub>DD</sub> + 0.3 | V     |       |

| Input MID Voltage                | V <sub>MID</sub>     | 3.3 V +/-5%                                                           | 1                     |          | 1.8                   | V     |       |

| Input Low Voltage                | V <sub>IL</sub>      | 3.3 V +/-5%                                                           | V <sub>SS</sub> - 0.3 |          | 0.8                   | V     |       |

| Input High Current               | I <sub>IH</sub>      | $V_{IN} = V_{DD}$                                                     | -5                    |          | 5                     | uA    |       |

|                                  | I <sub>IL1</sub>     | V <sub>IN</sub> = 0 V; Inputs with no pull-up resistors               | -5                    |          |                       | uA    |       |

| Input Low Current                | $I_{\rm IL2}$        | V <sub>IN</sub> = 0 V; Inputs with pull-up resistors                  | -200                  |          |                       | uA    |       |

| Operating Supply Current         | I <sub>DD3.3OP</sub> | Full Active, $C_L = Full load;$                                       |                       |          | 350                   | mA    |       |

| Powerdown Current                |                      | all diff pairs driven                                                 |                       |          | 35                    | mA    |       |

| 1 Owerdown Current               | DD3.3PD              | all differential pairs tri-stated                                     |                       |          | 12                    | mA    |       |

| Input Frequency <sup>3</sup>     | F <sub>i</sub>       | $V_{DD} = 3.3 V$                                                      |                       | 14.31818 |                       | MHz   | 3     |

| Pin Inductance <sup>1</sup>      | L <sub>pin</sub>     |                                                                       |                       |          | 7                     | nH    | 1     |

|                                  | CIN                  | Logic Inputs                                                          |                       |          | 5                     | pF    | 1     |

| Input Capacitance <sup>1</sup>   | C <sub>OUT</sub>     | Output pin capacitance                                                |                       |          | 6                     | pF    | 1     |

|                                  | C <sub>INX</sub>     | X1 & X2 pins                                                          |                       |          | 5                     | pF    | 1     |

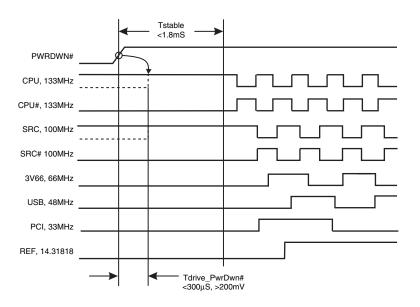

| Clk Stabilization <sup>1,2</sup> | T <sub>STAB</sub>    | From V <sub>DD</sub> Power-Up or de-<br>assertion of PD# to 1st clock |                       |          | 1.8                   | ms    | 1,2   |

| Modulation Frequency             |                      | Triangular Modulation                                                 | 30                    |          | 33                    | kHz   | 1     |

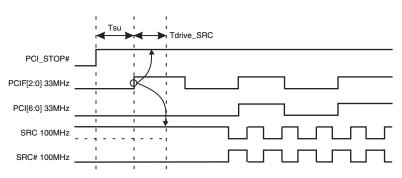

| Tdrive_SRC                       |                      | SRC output enable after<br>PCI_Stop# de-assertion                     |                       |          | 15                    | ns    | 1     |

| Tdrive_PD#                       |                      | CPU output enable after<br>PD# de-assertion                           |                       |          | 300                   | us    | 1     |

| Tfall_Pd#                        |                      | PD# fall time of                                                      |                       |          | 5                     | ns    | 1     |

| Trise_Pd#                        |                      | PD# rise time of                                                      |                       |          | 5                     | ns    | 2     |

| Tdrive_CPU_Stop#                 |                      | CPU output enable after<br>CPU_Stop# de-assertion                     |                       |          | 10                    | us    | 1     |

| Tfall_CPU_Stop#                  |                      | PD# fall time of                                                      |                       |          | 5                     | ns    | 1     |

| Trise_CPU_Stop#                  |                      | PD# rise time of                                                      |                       |          | 5                     | ns    | 2     |

<sup>1</sup>Guaranteed by design, not 100% tested in production.

<sup>2</sup>See timing diagrams for timing requirements.

<sup>3</sup> Input frequency should be measured at the REF output pin and tuned to ideal 14.31818MHz to meet ppm frequency accuracy on PLL outputs.

## Electrical Characteristics - CPU & SRC 0.7V Current Mode Differential Pair

$T_A = 0 - 70^{\circ}C$ ;  $V_{DD} = 3.3 V + -5\%$ ;  $C_L = 2pF$

| PARAMETER                          | SYMBOL                | CONDITIONS                                                        | MIN    | TYP | MAX     | UNITS                                                                           | NOTES |

|------------------------------------|-----------------------|-------------------------------------------------------------------|--------|-----|---------|---------------------------------------------------------------------------------|-------|

| Current Source Output<br>Impedance | Zo <sup>1</sup>       | $V_{O} = V_{x}$                                                   | 3000   |     |         | Ω                                                                               | 1     |

| Output High Voltage                | V <sub>OH3</sub>      | I <sub>OH</sub> = -1 mA                                           | 2.4    |     |         | V                                                                               |       |

| Output Low Voltage                 | V <sub>OL3</sub>      | I <sub>OL</sub> = 1 mA                                            |        |     | 0.4     |                                                                                 |       |

| Voltage High                       | VHigh                 | Statistical measurement on single ended signal using oscilloscope | 660    |     | 850     | mV                                                                              | 1     |

| Voltage Low                        | VLow                  | math function.                                                    | -150   |     | 150     |                                                                                 | 1     |

| Max Voltage                        | Vovs                  | Measurement on single ended                                       |        |     | 1150    | m\/                                                                             | 1     |

| Min Voltage                        | Vuds                  | signal using absolute value.                                      | -300   |     |         | IIIV                                                                            | 1     |

| Crossing Voltage (abs)             | Vcross(abs)           |                                                                   | 250    |     | 550     | mV                                                                              | 1     |

| Crossing Voltage (var)             | d-Vcross              | Variation of crossing over all<br>edges                           |        |     | 140     | mV                                                                              | 1     |

| Long Accuracy                      | ppm                   | see Tperiod min-max values                                        | -300   |     | 300     | ppm                                                                             | 1,2   |

|                                    |                       | 200MHz nominal                                                    | 4.9985 |     | 5.0015  | ns                                                                              | 2     |

|                                    |                       | 200MHz spread                                                     | 4.9985 |     | 5.0266  | ns                                                                              | 2     |

|                                    | Tperiod               | 166.66MHz nominal                                                 | 5.9982 |     | 6.0018  | ns                                                                              | 2     |

| Average period                     |                       | 166.66MHz spread                                                  | 5.9982 |     | 6.0320  | ns                                                                              | 2     |

| Average period                     |                       | 133.33MHz nominal                                                 | 7.4978 |     | 7.5023  | ns                                                                              | 2     |

|                                    |                       | 133.33MHz spread                                                  | 7.4978 |     | 5.4000  | ns                                                                              | 2     |

|                                    |                       | 100.00MHz nominal                                                 | 9.9970 |     | 10.0030 | ns                                                                              | 2     |

|                                    |                       | 100.00MHz spread                                                  | 9.9970 |     | 10.0533 | ns                                                                              | 2     |

|                                    |                       | 200MHz nominal                                                    | 4.8735 |     |         | ns                                                                              | 1,2   |

| Absolute min period                | T <sub>absmin</sub>   | 166.66MHz nominal/spread                                          | 5.8732 |     |         | ns                                                                              | 1,2   |

| Absolute min period                | absmin                | 133.33MHz nominal/spread                                          | 7.3728 |     |         | mV<br>mV<br>mV<br>mV<br>mV<br>mV<br>mV<br>mV<br>mV<br>mV<br>mV<br>mV<br>mV<br>m | 1,2   |

|                                    |                       | 100.00MHz nominal/spread                                          | 9.8720 |     |         | ns                                                                              | 1,2   |

| Rise Time                          | t <sub>r</sub>        | V <sub>OL</sub> = 0.175V, V <sub>OH</sub> = 0.525V                | 175    |     | 700     | ps                                                                              | 1     |

| Fall Time                          | t <sub>f</sub>        | $V_{OH} = 0.525 V V_{OL} = 0.175 V$                               | 175    |     | 700     | ps                                                                              | 1     |

| Rise Time Variation                | d-t <sub>r</sub>      |                                                                   |        |     | 125     | ps                                                                              | 1     |

| Fall Time Variation                | d-t <sub>f</sub>      |                                                                   |        |     | 125     | ps                                                                              | 1     |

| Duty Cycle                         | d <sub>t3</sub>       | Measurement from differential<br>wavefrom                         | 45     |     | 55      | •                                                                               | 1     |

| Skew                               | t <sub>sk3</sub>      | $V_{\rm T} = 50\%$                                                |        |     | 100     | ps                                                                              | 1     |

| Jitter, Cycle to cycle             | t <sub>jcyc-cyc</sub> | Measurement from differential<br>wavefrom                         |        |     | 125     | •                                                                               | 1     |

<sup>1</sup>Guaranteed by design, not 100% tested in production.

<sup>2</sup> All Long Term Accuracy and Clock Period specifications are guaranteed with the assumption that Ref output is at 14.31818MHz

SRC clock outputs run at only 100MHz or 200MHz, specs for 133.33 and 166.66 do not apply to SRC clock pair.

## Electrical Characteristics - 3V66 Mode: 3V66 [4:0]

| PARAMETER           | SYMBOL                | pF (unless otherwise specified)<br>CONDITIONS    | MIN     | TYP | MAX     | UNITS      | Notes |

|---------------------|-----------------------|--------------------------------------------------|---------|-----|---------|------------|-------|

|                     |                       | see Tperiod min-max values                       | -300    |     | 300     |            | -     |

| Long Accuracy       | ppm                   |                                                  |         |     |         | ppm        | 1,2   |

| Clock period        | T <sub>period</sub>   | 66.66MHz output nominal                          | 14.9955 |     | 15.0045 | ns         | 2     |

| •                   |                       | 66.66MHz output spread                           | 14.9955 |     | 15.0799 | ns         | 2     |

| Output High Voltage | V <sub>OH</sub>       | I <sub>OH</sub> = -1 mA                          | 2.4     |     |         | V          |       |

| Output Low Voltage  | V <sub>OL</sub>       | $I_{OL} = 1 \text{ mA}$                          |         |     | 0.55    | V          |       |

| Output High Current | 1                     | V <sub>OH</sub> @ MIN = 1.0 V                    | -33     |     |         | mA         |       |

|                     | I <sub>OH</sub>       | V <sub>OH</sub> @ MAX = 3.135 V                  |         |     | -33     | 3 mA<br>mA |       |

| Output Low Current  | le.                   | V <sub>OL</sub> @ MIN = 1.95 V                   | 30      |     |         | mA         |       |

|                     | I <sub>OL</sub>       | V <sub>OL</sub> @ MAX = 0.4 V                    |         |     | 38      | mA         |       |

| Edge Rate           |                       | Rising edge rate                                 | 1       |     | 4       | V/ns       | 1     |

| Edge Rate           |                       | Falling edge rate                                | 1       |     | 4       | V/ns       | 1     |

| Rise Time           | t <sub>r1</sub>       | $V_{OL} = 0.4 \text{ V}, V_{OH} = 2.4 \text{ V}$ | 0.5     |     | 2       | ns         | 1     |

| Fall Time           | t <sub>f1</sub>       | $V_{OH} = 2.4 \text{ V}, V_{OL} = 0.4 \text{ V}$ | 0.5     |     | 2       | ns         | 1     |

| Duty Cycle          | d <sub>t1</sub>       | $V_{T} = 1.5 V$                                  | 45      |     | 55      | %          | 1     |

| Skew                | t <sub>sk1</sub>      | V <sub>T</sub> = 1.5 V                           |         |     | 250     | ps         | 1     |

| Jitter              | t <sub>jcyc-cyc</sub> | V <sub>T</sub> = 1.5 V 3V66                      |         |     | 250     | ps         | 1     |

$T_A = 0 - 70^{\circ}C$ ;  $V_{DD} = 3.3 \text{ V} \pm -5\%$ ;  $C_L = 10-30 \text{ pF}$  (unless otherwise specified)

<sup>1</sup>Guaranteed by design, not 100% tested in production.

<sup>2</sup> All Long Term Accuracy and Clock Period specifications are guaranteed with the assumption that Ref output is at 14.31818MHz

## Electrical Characteristics - PCICLK/PCICLK\_F

$T_A = 0 - 70^{\circ}C$ ;  $V_{DD} = 3.3 \text{ V} + /-5\%$ ;  $C_L = 10-30 \text{ pF}$  (unless otherwise specified)

| PARAMETER           | SYMBOL                | CONDITIONS                                       | MIN     | TYP | MAX     | UNITS | Notes |

|---------------------|-----------------------|--------------------------------------------------|---------|-----|---------|-------|-------|

| Long Accuracy       | ppm                   | see Tperiod min-max values                       | -300    |     | 300     | ppm   | 1,2   |

| Clock period        | T <sub>period</sub>   | 33.33MHz output nominal                          | 29.9910 |     | 30.0090 | ns    | 2     |

| Clock period        | <sup>I</sup> period   | 33.33MHz output spread                           | 29.9910 |     | 30.1598 | ns    | 2     |

| Output High Voltage | V <sub>OH</sub>       | I <sub>OH</sub> = -1 mA                          | 2.4     |     |         | V     |       |

| Output Low Voltage  | V <sub>OL</sub>       | I <sub>OL</sub> = 1 mA                           |         |     | 0.55    | V     |       |

| Output High Current | L                     | V <sub>OH</sub> @MIN = 1.0 V                     | -33     |     |         | mA    |       |

| Output High Current | I <sub>ОН</sub>       | V <sub>OH</sub> @ MAX = 3.135 V                  |         |     | -33     | mA    |       |

| Output Low Current  |                       | V <sub>OL</sub> @ MIN = 1.95 V                   | 30      |     |         | mA    |       |

| Output Low Cultern  | I <sub>OL</sub>       | V <sub>OL</sub> @ MAX = 0.4 V                    |         |     | 38      | mA    |       |

| Edge Rate           |                       | Rising edge rate                                 | 1       |     | 4       | V/ns  | 1     |

| Edge Rate           |                       | Falling edge rate                                | 1       |     | 4       | V/ns  | 1     |

| Rise Time           | t <sub>r1</sub>       | $V_{OL} = 0.4 \text{ V}, V_{OH} = 2.4 \text{ V}$ | 0.5     |     | 2       | ns    | 1     |

| Fall Time           | t <sub>f1</sub>       | $V_{OH} = 2.4 \text{ V}, V_{OL} = 0.4 \text{ V}$ | 0.5     |     | 2       | ns    | 1     |

| Duty Cycle          | d <sub>t1</sub>       | V <sub>T</sub> = 1.5 V                           | 45      |     | 55      | %     | 1     |

| Skew                | t <sub>sk1</sub>      | V <sub>T</sub> = 1.5 V                           |         |     | 500     | ps    | 1     |

| Jitter              | t <sub>jcyc-cyc</sub> | $V_{T} = 1.5 V 3V66$                             |         |     | 250     | ps    | 1     |

|                     |                       |                                                  |         |     |         |       |       |

<sup>1</sup>Guaranteed by design, not 100% tested in production.

<sup>2</sup> All Long Term Accuracy and Clock Period specifications are guaranteed with the assumption that Ref output is at 14.31818MHz

## **Electrical Characteristics - 48MHz DOT Clock**

$T_A = 0 - 70^{\circ}C$ ;  $V_{DD} = 3.3 \text{ V} \pm -5\%$ ;  $C_L = 5-10 \text{ pF}$  (unless otherwise specified)

|                     |                 | CONDITIONS                                                      | MINI    |     | MAX     |       | Nistaa |

|---------------------|-----------------|-----------------------------------------------------------------|---------|-----|---------|-------|--------|

| PARAMETER           | SYMBOL          | CONDITIONS                                                      | MIN     | TYP | MAX     | UNITS | Notes  |

| Long Accuracy       | ppm             | see Tperiod min-max<br>values                                   | -200    |     | 200     | ppm   | 1,2    |

| Clock period        | Tperiod         | 66.66MHz output nominal                                         | 20.8257 |     | 20.8340 | ns    | 2      |

| Output High Voltage | V <sub>OH</sub> | I <sub>ОН</sub> = -1 mA                                         | 2.4     |     |         | V     |        |

| Output Low Voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 1 mA                                          |         |     | 0.55    | V     |        |

| Output High Current | 1               | V <sub>OH</sub> @ MIN = 1.0 V                                   | -33     |     |         | mA    |        |

| Output High Current | I <sub>OH</sub> | V <sub>OH</sub> @ MAX = 3.135 V                                 |         |     | -33     | mA    |        |

| Output Low Current  | 1               | V <sub>OL</sub> @ MIN = 1.95 V                                  | 30      |     |         | mA    |        |

| Output Low Current  | I <sub>OL</sub> | V <sub>OL</sub> @ MAX = 0.4 V                                   |         |     | 38      | mA    |        |

| Edge Rate           |                 | Rising edge rate                                                | 2       |     | 4       | V/ns  | 1      |

| Edge Rate           |                 | Falling edge rate                                               | 2       |     | 4       | V/ns  | 1      |

| Rise Time           | t <sub>r1</sub> | $V_{OL} = 0.4 \text{ V}, V_{OH} = 2.4 \text{ V}$                | 0.5     |     | 1       | ns    | 1      |

| Fall Time           | t <sub>f1</sub> | $V_{OH} = 2.4 \text{ V}, V_{OL} = 0.4 \text{ V}$                | 0.5     |     | 1       | ns    | 1      |

| Duty Cycle          | d <sub>t1</sub> | V <sub>T</sub> = 1.5 V                                          | 45      |     | 55      | %     | 1      |

| Long Term Jitter    |                 | 125us period jitter<br>(8kHz frequency<br>modulation amplitude) |         |     | 2       | ns    | 1      |

<sup>1</sup>Guaranteed by design, not 100% tested in production. <sup>2</sup> All Long Term Accuracy and Clock Period specifications are guaranteed with the assumption that Ref output is at 14.31818MHz

## **Electrical Characteristics - VCH, 48MHz, USB**

$T_A = 0 - 70^{\circ}C$ ;  $V_{DD} = 3.3 \text{ V} \pm -5\%$ ;  $C_L = 10-20 \text{ pF}$  (unless otherwise specified)

| PARAMETER           | SYMBOL              | CONDITIONS                                                      | MIN     | TYP | MAX     | UNITS | Notes |

|---------------------|---------------------|-----------------------------------------------------------------|---------|-----|---------|-------|-------|

| Long Accuracy       | ppm                 | see Tperiod min-max values                                      | -200    |     | 200     | ppm   | 1,2   |

| Clock period        | T <sub>period</sub> | 66.66MHz output nominal                                         | 20.8257 |     | 20.8340 | ns    | 2     |

| Output High Voltage | V <sub>OH</sub>     | I <sub>OH</sub> = -1 mA                                         | 2.4     |     |         | V     |       |

| Output Low Voltage  | V <sub>OL</sub>     | I <sub>OL</sub> = 1 mA                                          |         |     | 0.55    | V     |       |

| Output High Current | 1                   | V <sub>OH</sub> @ MIN = 1.0 V                                   | -33     |     |         | mA    |       |

| Output High Current | I <sub>OH</sub>     | V <sub>OH</sub> @ MAX = 3.135 V                                 |         |     | -33     | mA    |       |

| Output Low Current  |                     | V <sub>OL</sub> @MIN = 1.95 V                                   | 30      |     |         | mA    |       |

| Output Low Current  | I <sub>OL</sub>     | V <sub>OL</sub> @ MAX = 0.4 V                                   |         |     | 38      | mA    |       |

| Edge Rate           |                     | Rising edge rate                                                | 1       |     | 2       | V/ns  | 1     |

| Edge Rate           |                     | Falling edge rate                                               | 1       |     | 2       | V/ns  | 1     |

| Rise Time           | t <sub>r1</sub>     | $V_{OL} = 0.4 \text{ V}, V_{OH} = 2.4 \text{ V}$                | 1       |     | 2       | ns    | 1     |

| Fall Time           | t <sub>f1</sub>     | $V_{OH} = 2.4 \text{ V}, V_{OL} = 0.4 \text{ V}$                | 1       |     | 2       | ns    | 1     |

| Duty Cycle          | d <sub>t1</sub>     | V <sub>T</sub> = 1.5 V                                          | 45      |     | 55      | %     | 1     |

| Long Term Jitter    |                     | 125us period jitter<br>(8kHz frequency modulation<br>amplitude) |         |     | 6       | ns    | 1     |

<sup>1</sup>Guaranteed by design, not 100% tested in production.

<sup>2</sup> All Long Term Accuracy and Clock Period specifications are guaranteed with the assumption that Ref output is at 14.31818MHz

IDT<sup>®</sup> Programmable Timing Control Hub<sup>™</sup> for Next Gen P4<sup>™</sup> Processor

## **Electrical Characteristics - REF-14.318MHz**

$T_{A}$  = 0 - 70°C;  $V_{DD}$  = 3.3 V +/-5%;  $C_{L}$  = 10-20 pF (unless otherwise specified)

| PARAMETER           | SYMBOL                       | CONDITIONS                                                      | MIN     | TYP | MAX     | UNITS |

|---------------------|------------------------------|-----------------------------------------------------------------|---------|-----|---------|-------|

| Long Accuracy       | ppm <sup>1</sup>             | see Tperiod min-max values                                      | -300    |     | 300     | ppm   |

| Clock period        | T <sub>period</sub>          | 14.318MHz output nominal                                        | 69.8270 |     | 69.8550 | ns    |

| Output High Voltage | V <sub>OH</sub> <sup>1</sup> | I <sub>OH</sub> = -1 mA                                         | 2.4     |     |         | V     |

| Output Low Voltage  | V <sub>OL</sub> <sup>1</sup> | I <sub>OL</sub> = 1 mA                                          |         |     | 0.4     | V     |

| Output High Current | I <sub>OH</sub> <sup>1</sup> | V <sub>OH</sub> @MIN = 1.0 V, V<br><sub>OH</sub> @MAX = 3.135 V | -29     |     | -23     | mA    |

| Output Low Current  | I <sub>OL</sub> <sup>1</sup> | V <sub>OL</sub> @ MIN = 1.95 V, V <sub>OL</sub><br>@MAX = 0.4 V | 29      |     | 27      | mA    |

| Rise Time           | t <sub>r1</sub> 1            | $V_{OL} = 0.4 \text{ V}, V_{OH} = 2.4 \text{ V}$                | 1       |     | 2       | ns    |

| Fall Time           | t <sub>f1</sub> 1            | $V_{OH} = 2.4 \text{ V}, V_{OL} = 0.4 \text{ V}$                | 1       |     | 2       | ns    |

| Skew                | t <sub>sk1</sub> 1           | V <sub>T</sub> = 1.5 V                                          |         |     | 500     | ps    |

| Duty Cycle          | d <sub>t1</sub> <sup>1</sup> | V <sub>T</sub> = 1.5 V                                          | 45      |     | 55      | %     |

| Jitter              | t <sub>icvc-cvc</sub> 1      | V <sub>T</sub> = 1.5 V                                          |         |     | 1000    | ps    |

<sup>1</sup>Guaranteed by design, not 100% tested in production.

## Group to Group Skews at Common Transition Edges

|                  |                                          | 0                              |      |      |      |       |

|------------------|------------------------------------------|--------------------------------|------|------|------|-------|

| GROUP            | SYMBOL                                   | CONDITIONS                     | MIN  | TYP  | MAX  | UNITS |

| 200MHZ CPU to 3V | 66 <sup>1</sup> S <sub>CPU200-3V66</sub> | 3V66 (4:0) leads 200MHZ<br>CPU | -2.0 | -1.5 | -1.0 | ns    |

| 3V66 to PCI      | S <sub>3V66-PCI</sub>                    | 3V66 (4:0) leads 33MHz PCI     | 1.50 |      | 3.50 | ns    |

| DOT-USB          | S <sub>DOT_USB</sub>                     | 180 degrees out of phase       | 0.00 |      | 1.00 | ns    |

| DOT-VCH          | S <sub>DOT_VCH</sub>                     | in phase                       | 0.00 |      | 1.00 | ns    |

1.  $3V66 \text{ MHz } C_L = 0 \text{pf}$ , Rseries = 33 ohm. CPU CL = 2 pf, Rseries = 33 ohm, Rshunt = 49.9 ohms. Measured at the pins of the 932S208.

# General I<sup>2</sup>C serial interface information for the ICS932S208

## How to Write:

- Controller (host) sends a start bit.

- Controller (host) sends the write address D2 (H)

- ICS clock will *acknowledge*

- Controller (host) sends the begining byte location = N

- ICS clock will acknowledge

- Controller (host) sends the data byte count = X

- ICS clock will acknowledge

- Controller (host) starts sending *Byte N through Byte N + X -1*

- (see Note 2)

- ICS clock will acknowledge each byte one at a time

- Controller (host) sends a Stop bit

## How to Read:

- Controller (host) will send start bit.

- Controller (host) sends the write address D2 (H)

- ICS clock will *acknowledge*

- Controller (host) sends the begining byte location = N

- ICS clock will acknowledge

- Controller (host) will send a separate start bit.

- Controller (host) sends the read address  $D3_{(H)}$

- ICS clock will *acknowledge*

- ICS clock will send the data byte count = X

- ICS clock sends Byte N + X -1

- ICS clock sends Byte 0 through byte X (if X<sub>(H)</sub> was written to byte 8).

- · Controller (host) will need to acknowledge each byte

- Controllor (host) will send a not acknowledge bit

- Controller (host) will send a stop bit

| In    | dex Block W                 | /rit     | e Operation          |

|-------|-----------------------------|----------|----------------------|

| Со    | ntroller (Host)             |          | ICS (Slave/Receiver) |

| Т     | starT bit                   |          |                      |

| Slav  | e Address D2 <sub>(H)</sub> |          |                      |

| WR    | WRite                       |          |                      |

|       |                             |          | ACK                  |

| Beg   | inning Byte = N             |          |                      |

|       |                             |          | ACK                  |

| Data  | Byte Count = X              |          |                      |

|       |                             |          | ACK                  |

| Begir | nning Byte N                |          |                      |

|       |                             |          | ACK                  |

|       | 0                           | te       |                      |

|       | 0                           | X Byte   | 0                    |

|       | 0                           | $\times$ | 0                    |

|       |                             |          | Ō                    |

| Byte  | e N + X - 1                 |          |                      |

|       |                             |          | ACK                  |

| Р     | stoP bit                    |          |                      |

| In   | dex Block Rea               | ad (   | Operation          |

|------|-----------------------------|--------|--------------------|

| Co   | ntroller (Host)             | IC     | S (Slave/Receiver) |

| Т    | starT bit                   |        |                    |

| Slav | e Address D2 <sub>(H)</sub> |        |                    |

| WR   | WRite                       |        |                    |

|      |                             |        | ACK                |

| Beg  | inning Byte = N             |        |                    |

|      | -                           |        | ACK                |

| RT   | Repeat starT                |        |                    |

| Slav | e Address D3 <sub>(H)</sub> |        |                    |

| RD   | ReaD                        |        |                    |

|      |                             |        | ACK                |

|      |                             |        |                    |

|      |                             | D      | ata Byte Count = X |

|      | ACK                         |        |                    |

|      | 101/                        |        | Beginning Byte N   |

|      | ACK                         |        |                    |

|      | 0                           | yte    | 0                  |

|      | -                           | X Byte | 0                  |

|      | <u> </u>                    | (      | <b>•</b>           |

|      |                             |        | Byte N + X - 1     |

| N    | Not acknowledge             |        |                    |

| Р    | stoP bit                    |        |                    |

#### I<sup>2</sup>C Table: Read-Back Register

| By    | te 0 | Pin # | Name     | <b>Control Function</b>    | Туре | 0        | 1              | PWD |

|-------|------|-------|----------|----------------------------|------|----------|----------------|-----|

| Bit 7 | -    | -     | RESERVED | RESERVED                   | -    | RES      | SERVED         | Х   |

| Bit 6 |      | -     | RESERVED | RESERVED                   | -    | RES      | SERVED         | Х   |

| Bit 5 | -    | -     | RESERVED | RESERVED                   | -    | RESERVED |                | Х   |

| Bit 4 |      | -     | RESERVED | RESERVED                   | -    | RESERVED |                | Х   |

| Bit 3 | -    | -     | RESERVED | RESERVED                   | -    | RESERVED |                | Х   |

| Bit 2 | -    |       | RESERVED | RESERVED                   | -    | RESERVED |                | Х   |

| Bit 1 | -    | -     | FSB      | Freq Select 1 Read<br>Back | R    | READBAC  | CK of CPU(3:0) | х   |

| Bit 0 | -    | -     | FSA      | Freq Select 0 Read<br>Back | R    | Fre      | equency        | х   |

## I<sup>2</sup>C Table: Spreading and Device Behavior Control Register

| Ву    | te 1   | Pin #         | Name        | <b>Control Function</b>     | Туре | 0        | 1         | PWD |

|-------|--------|---------------|-------------|-----------------------------|------|----------|-----------|-----|

| Bit 7 | 38, 37 |               | SRC/SRC#    | SRC Free-Running<br>Control | RW   | FREE-RUN | STOPPABLE | 0   |

| Bit 6 | 38     | , 37          | SRC         | Output Control              | RW   | Disable  | Enable    | 1   |

| Bit 5 | -      |               | RESERVED    | RESERVED                    | -    | RESERVED |           | Х   |

| Bit 4 |        | -             | RESERVED    | RESERVED                    | -    | RESERVED |           | Х   |

| Bit 3 |        | -             | RESERVED    | RESERVED                    | -    | RES      | SERVED    | Х   |

| Bit 2 | 47     | <b>'</b> , 46 | CPUT2/CPUC2 | Output Control              | RW   | Disable  | Enable    | 1   |

| Bit 1 | 44     | , 43          | CPUT1/CPUC1 | Output Control              | RW   | Disable  | Enable    | 1   |

| Bit 0 | 41     | , 40          | CPUT0/CPUC0 | Output Enable               | RW   | Disable  | Enable    | 1   |

## I<sup>2</sup>C Table: Output Control Register

| Ву    | te 2 | Pin # | Name                    | <b>Control Function</b>          | Туре | 0      | 1      | PWD |

|-------|------|-------|-------------------------|----------------------------------|------|--------|--------|-----|

| Bit 7 | 38,  | , 37  | SRC_PD#<br>Drive Mode   | 0: Driven in PD#                 | RW   | Driven | Hi-Z   | 0   |

| Bit 6 | 38,  | , 37  | SRC_Stop#<br>Drive Mode | 0: Driven in<br>PCI_Stop#        | RW   | Driven | Hi-Z   | 0   |

| Bit 5 | 47   | , 46  | CPUT2_PD# Drive<br>Mode |                                  | RW   | Driven | Hi-Z   | 0   |

| Bit 4 | 44,  | , 43  | CPUT1_PD# Drive<br>Mode | 0:driven in PD#<br>1: Tri-stated | RW   | Driven | Hi-Z   | 0   |

| Bit 3 | 41,  | , 40  | CPUT0_PD# Drive<br>Mode |                                  | RW   | Driven | Hi-Z   | 0   |

| Bit 2 |      | -     | RESERVED                | RESERVED                         | -    | RES    | SERVED | Х   |

| Bit 1 | -    |       | RESERVED                | RESERVED                         | -    | RES    | SERVED | Х   |

| Bit 0 |      | -     | RESERVED                | RESERVED                         | -    | RES    | SERVED | Х   |

## I<sup>2</sup>C Table: Output Control Register

| By    | rte 3                                 | Pin # | Name      | <b>Control Function</b>                                 | Туре | 0       | 1       | PWD |

|-------|---------------------------------------|-------|-----------|---------------------------------------------------------|------|---------|---------|-----|

| Bit 7 | 7,8,9,12,13,14,15,<br>18,19,20,37,38, |       | PCI_Stop# | PCI_Stop# Control<br>0:all stoppable PCI<br>are stopped | RW   | Enable  | Disable | 1   |

| Bit 6 | 2                                     | 20    | PCICLK6   | Output Control                                          | RW   | Disable | Enable  | 1   |

| Bit 5 | 1                                     | 9     | PCICLK5   | Output Control                                          | RW   | Disable | Enable  | 1   |

| Bit 4 | 1                                     | 8     | PCICLK4   | Output Control                                          | RW   | Disable | Enable  | 1   |

| Bit 3 | 1                                     | 5     | PCICLK3   | Output Control                                          | RW   | Disable | Enable  | 1   |

| Bit 2 | 1                                     | 4     | PCICLK2   | Output Control                                          | RW   | Disable | Enable  | 1   |

| Bit 1 | 1                                     | 3     | PCICLK1   | Output Control                                          | RW   | Disable | Enable  | 1   |

| Bit 0 | 1                                     | 2     | PCICLK0   | Output Control                                          | RW   | Disable | Enable  | 1   |

## I<sup>2</sup>C Table: Output Control Register

| Ву    | te 4 | Pin # | Name                         | <b>Control Function</b> | Туре | 0        | 1         | PWD |

|-------|------|-------|------------------------------|-------------------------|------|----------|-----------|-----|

| Bit 7 | 31   |       | 48MHz_USB<br>2x output drive | 0=2x drive              | RW   | 2x drive | normal    | 1   |

| Bit 6 | 31   |       | 48MHz_USB                    | Output Control          | RW   | Disable  | Enable    | 1   |

| Bit 5 | 9    |       | PCIF2                        | PCI FREE-RUN            | RW   | FREE-RUN | STOPPABLE | 0   |

| Bit 4 |      | 8     | PCIF1                        | NING CONTROL            | RW   | FREE-RUN | STOPPABLE | 0   |

| Bit 3 |      | 7     | PCIF0                        |                         | RW   | FREE-RUN | STOPPABLE | 0   |

| Bit 2 | 9    |       | PCICLK_F2                    | Output Control          | RW   | Disable  | Enable    | 1   |

| Bit 1 | 8    |       | PCICLK_F1                    | Output Control          | RW   | Disable  | Enable    | 1   |

| Bit 0 |      | 7     | PCICLK_F0                    | Output Control          | RW   | Disable  | Enable    | 1   |

## I<sup>2</sup>C Table: Output Control Register

| By    | rte 5 | Pin # | Name                 | <b>Control Function</b> | Туре | 0       | 1      | PWD |

|-------|-------|-------|----------------------|-------------------------|------|---------|--------|-----|

| Bit 7 | ;     | 32    | 48MHZ_DOT            | Output Control          | RW   | Disable | Enable | 1   |

| Bit 6 | 50/49 |       | CPUT3/CPUC3          | Output Control          | RW   | Disable | Enable | 1   |

| Bit 5 | 29    |       | 3V66_4/VCH<br>Select | Output Select           | RW   | 3V66    | VCH    | 0   |

| Bit 4 |       | 29    | 3V66_4/VCH           | Output Control          | RW   | Disable | Enable | 1   |

| Bit 3 |       | 27    | 3V66_3               | Output Control          | RW   | Disable | Enable | 1   |

| Bit 2 |       | 26    | 3V66_2               | Output Control          | RW   | Disable | Enable | 1   |

| Bit 1 | 23    |       | 3V66_1               | Output Control          | RW   | Disable | Enable | 1   |

| Bit 0 |       | 22    | 3V66_0               | Output Control          | RW   | Disable | Enable | 1   |

#### I<sup>2</sup>C Table: Output Control and Fix Frequency Register

| Ву    | /te 6                                                                                   | Pin # | Name            | <b>Control Function</b>    | Туре | 0             | 1            | PWD |

|-------|-----------------------------------------------------------------------------------------|-------|-----------------|----------------------------|------|---------------|--------------|-----|

| Bit 7 | 1,2,7,8,9,12,13,14,<br>15,18,19,20,22,23,2<br>6,27,29,31,32,37,38<br>,40,41,43,44,46,47 |       | Test Clock Mode | Test Clock Mode            | RW   | Disable       | Enable       | 0   |

| Bit 6 | -                                                                                       |       | RESERVED        | -                          | -    | -             | -            | 0   |

| Bit 5 | 40,41,43,44,46,47                                                                       |       | FS Testmode     | FS_A and FS_B<br>Operation | RW   | Normal        | Test Mode    | 0   |

| Bit 4 | 37,38                                                                                   |       | SRC100#         | SRC Frequency<br>Select    | RW   | 100MHz        | 200MHz       | 0   |

| Bit 3 |                                                                                         |       | RESERVED        | -                          | -    | -             | -            | 0   |

| Bit 2 | 7,8,9,12,13,14,15,1<br>8,19,20,22,23,26,27<br>,29,31,32,37,38,40,<br>41,43,44,46,47     |       | SSEN            | Spread Spectrum<br>Enable  | RW   | Spread<br>OFF | Spread<br>ON | 0   |

| Bit 1 | 2                                                                                       |       | REF1            | Output Control             | RW   | Disable       | Enable       | 1   |

| Bit 0 | 1                                                                                       |       | REF0            | Output Control             | RW   | Disable       | Enable       | 1   |

## I<sup>2</sup>C Table: Vendor & Revision ID Register

| Ву    | te 7 | Pin # | Name | <b>Control Function</b> | Туре | 0 | 1 | PWD |

|-------|------|-------|------|-------------------------|------|---|---|-----|

| Bit 7 | -    |       | RID3 |                         | R    | - | - | Х   |

| Bit 6 | -    |       | RID2 | REVISION ID             | R    | - | - | Х   |

| Bit 5 | -    |       | RID1 |                         | R    | - | - | Х   |

| Bit 4 | -    |       | RID0 | 1 – – – – –             | R    | - | - | Х   |

| Bit 3 | -    |       | VID3 |                         | R    | - | - | 0   |

| Bit 2 | -    |       | VID2 | VENDOR ID               | R    | - | - | 0   |

| Bit 1 | -    |       | VID1 |                         | R    | - | - | 0   |

| Bit 0 | -    |       | VID0 |                         | R    | - | - | 1   |

## **PCI Stop Functionality**

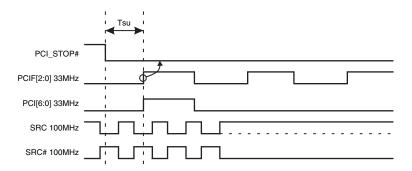

The PCI\_STOP# signal is on an active low input controlling PCI and SRC outputs. If PCIF (2:0) and SRC clocks can be set to be free-running through I2C programming. Outputs set to be free-running will ignore both the PCI\_STOP pin and the PCI\_STOP register bit.

| PCI_STOP# | CPU    | CPU #  | SRC                  | SRC#   | 3V66  | PCIF/PCI | USB/DOT | REF       | Note |

|-----------|--------|--------|----------------------|--------|-------|----------|---------|-----------|------|

| 1         | Normal | Normal | Normal               | Normal | 66MHz | 33MHz    | 48MHz   | 14.318MHz |      |

| 0         | Normal | Normal | Iref * 6<br>or Float | Low    | 66MHz | Low      | 48MHz   | 14.318MHz |      |

### PCI\_STOP# Assertion (transition from '1' to '0')

The clock samples the PCI\_STOP# signal on a rising edge of PCIF clock. After detecting the PCI\_STOP# assertion low, all PCI[6:0] and stoppable PCIF[2:0] clocks will latch low on their next high to low transition. After the PCI clocks are latched low, the SRC clock, (if set to stoppable) will latch high at Iref \* 6 (or tristate if Byte 2 Bit 6 = 1) upon its next low to high transition and the SRC# will latch low as shown below.

### PCI\_STOP# - De-assertion

The de-assertion of the PCI\_Stop# signal is to be sampled on the rising edge of the PCIF free running clock domain. After detecting PCI\_Stop# de-assertion, all PCI[6:0], stoppable PCIF[2:0] and stoppable SRC clocks will resume in a glitch free manner.

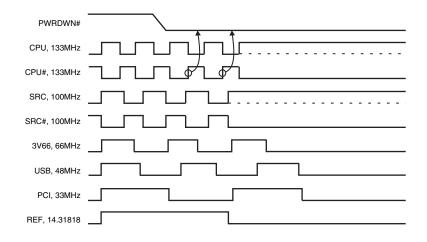

### PD#, Power Down

PD# is an asynchronous active low input used to shut off all clocks cleanly prior to clock power. When PD# is asserted low all clocks will be driven low before turning off the VCO. In PD# de-assertion all clocks will start without glitches.

| PWRDWN# | CPU                  | CPU #  | SRC                  | SRC#   | 3V66  | PCIF/PCI | USB/DOT | REF       | Note |

|---------|----------------------|--------|----------------------|--------|-------|----------|---------|-----------|------|

| 1       | Normal               | Normal | Normal               | Normal | 66MHz | 33MHz    | 48MHz   | 14.318MHz |      |

| 0       | Iref * 2 or<br>Float | Float  | Iref * 2<br>or Float | Float  | Low   | Low      | Low     | Low       |      |

Notes:

Refer to tristate control of CPU and SRC clocks in section 7.7 for tristate timing and operation.

Refer to Control Registers in section 16 for CPU\_Stop, SRC\_Stop and PwrDwn SMBus tristate control addresses.

#### **PD#** Assertion

PD# should be sampled low by 2 consecutive CPU# rising edges before stopping clocks. All single ended clocks will be held low on their next high to low transition.

All differential clocks will be held high on the next high to low transition of the complimentary clock. If the control register determining to drive mode is set to 'tri-state', the differential pair will be stopped in tri-state mode, undriven. When the drive mode but corresponding to the CPU or SRC clock of interest is set to '0' the true clock will be driven high at

2 x Iref and the complementary clock will be tristated. If the control register is programmed to '1' both clocks will be tristated.

#### **PD# De-assertion**

The time from the de-assertion of PD# or until power supply ramps to get stable clocks will be less than 1.8ms. If the drive mode control bit for PD# tristate is programmed to '1' the stopped differential pair must first be driven high to a minimum of 200mV in less than  $300\mu$ s of PD# deassertion.

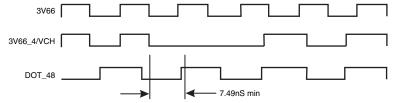

## 3V66\_4/VCH Pin Functionality

The 3V66\_4/VCH pin can be configured to be a 66.66MHz modulated output or a non-spread 48MHz output. The default is 3V66 clock. The switching is controlled by Byte 5 Bit 5. If it is set to '1' this pin will output the 48MHz VCH clock. The output will go low on the falling edge of 3V66 for a minimum of 7.49ns. Then the output will transition to 48MHz on the next rising edge of DOT\_48 clock.

## **Differential Clock Tristate**

To minimize power consumption, CPU[2:0] clock outputs are individually configurable through SMBus to be driven or tristated during PwrDwn# and CPU\_Stop# mode and the SRC clock is configurable to be driven or tristated during PCI\_Stop# and PwrDwn# mode. Each differential clock (SRC, CPU[2:0]) output can be disabled by setting the corresponding output's register OE bit to "0" (disable). Disabled outputs are to be tristated regardless of "CPU\_Stop", "SRC\_Stop" and "PwrDwn" register bit settings.

| Signal   | Pin PD# | Pin<br>CPU_Stop# | CPU_Stop<br>Tristate Bit | Pwrdwn<br>Tristate Bit | Non-Stoppable<br>Outputs | Stoppable<br>Outputs |

|----------|---------|------------------|--------------------------|------------------------|--------------------------|----------------------|

| CPU[2:0} | 1       | 1                | Х                        | х                      | Running                  | Running              |

| CPU[2:0} | 1       | 0                | 0                        | х                      | Running                  | Driven @ Iref x 6    |

| CPU[2:0} | 1       | 0                | 1                        | х                      | Running                  | Tristate             |

| CPU[2:0} | 0       | Х                | х                        | 0                      | Driven @ Iref x 2        | Driven @ Iref x 2    |

| CPU[2:0} | 0       | Х                | Х                        | 1                      | Tristate                 | Tristate             |

Notes:

- 1. Each output has four corresponding control register bits, OE, PwrDwn, CPU\_Stop and "Free Running"

- 2. Iref x 6 and Iref x 2 is the output current in the corresponding mode

- 3. See Control Registers section for bit address

| Signal | Pin PD# | Pin<br>PCI_Stop# | PCI_Stop<br>Tristate Bit | Pwrdwn<br>Tristate Bit | Non-Stoppable<br>Output | Stoppable<br>Output |

|--------|---------|------------------|--------------------------|------------------------|-------------------------|---------------------|

| SRC    | 1       | 1                | Х                        | Х                      | Running                 | Running             |

| SRC    | 1       | 0                | 0                        | Х                      | Running                 | Driven @ Iref x 6   |

| SRC    | 1       | 0                | 1                        | х                      | Running                 | Tristate            |

| SRC    | 0       | Х                | х                        | 0                      | Driven @ Iref x 2       | Driven @ Iref x 2   |

| SRC    | 0       | Х                | Х                        | 1                      | Tristate                | Tristate            |

Notes:

- 1. SRC output has four corresponding control register bits, OE, PwrDwn, SRC\_Stop and "Free Running"

- 2. Iref x 6 and Iref x 2 is the output current in the corresponding mode

- 3. See Control Registers section for bit address

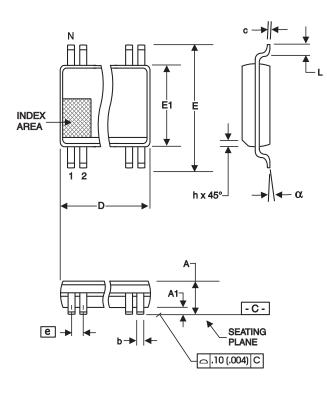

## **SSOP Package Drawing and Dimensions**

|        | In Milli | meters         | In Inches         |          |  |

|--------|----------|----------------|-------------------|----------|--|

| SYMBOL | COMMON D | IMENSIONS      | COMMON DIMENSIONS |          |  |

|        | MIN      | MAX            | MIN               | MAX      |  |

| A      | 2.41     | 2.80           | .095              | .110     |  |

| A1     | 0.20     | 0.40           | .008              | .016     |  |

| b      | 0.20     | 0.34           | .008              | .0135    |  |

| С      | 0.13     | 0.25           | .005              | .010     |  |

| D      | SEE VAF  | RIATIONS       | SEE VARIATIONS    |          |  |

| E      | 10.03    | 10.68          | .395              | .420     |  |

| E1     | 7.40     | 7.60           | .291              | .299     |  |

| е      | 0.635    | BASIC          | 0.025 BASIC       |          |  |

| h      | 0.38     | 0.64           | .015              | .025     |  |

| L      | 0.50     | 1.02           | .020              | .040     |  |

| N      | SEE VAF  | SEE VARIATIONS |                   | RIATIONS |  |

| а      | 0°       | 8°             | 0°                | 8°       |  |

|        |          |                |                   |          |  |

VARIATIONS

| N  | Dr    | nm.   | D (inch) |      |  |

|----|-------|-------|----------|------|--|

| IN | MIN   | MAX   | MIN      | MAX  |  |

| 56 | 18.31 | 18.55 | .720     | .730 |  |

Reference Doc.: JEDEC Publication 95, MO-118

10-0034

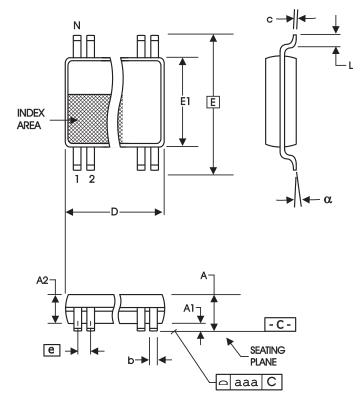

| TSSOP | Package | Drawing | and | Dimensions |

|-------|---------|---------|-----|------------|

|-------|---------|---------|-----|------------|

|        | 6.10 mm. Body, 0.50 mm. Pitch TSSOP<br>(240 mil) (20 mil) |          |                  |      |  |  |  |  |

|--------|-----------------------------------------------------------|----------|------------------|------|--|--|--|--|

|        | In Millir                                                 | neters   | In Inches        |      |  |  |  |  |

| SYMBOL | COMMON D                                                  | MENSIONS | COMMON DIMENSION |      |  |  |  |  |

|        | MIN                                                       | MAX      | MIN              | MAX  |  |  |  |  |

| А      |                                                           | 1.20     |                  | .047 |  |  |  |  |

| A1     | 0.05                                                      | 0.15     | .002             | .006 |  |  |  |  |

| A2     | 0.80                                                      | 1.05     | .032             | .041 |  |  |  |  |

| b      | 0.17                                                      | 0.27     | .007             | .011 |  |  |  |  |

| С      | 0.09                                                      | 0.20     | .0035            | .008 |  |  |  |  |

| D      | SEE VAR                                                   | IATIONS  | SEE VARIATIONS   |      |  |  |  |  |

| E      | 8.10 B                                                    | ASIC     | 0.319 BASIC      |      |  |  |  |  |

| E1     | 6.00                                                      | 6.20     | .236             | .244 |  |  |  |  |

| е      | 0.50 B                                                    | ASIC     | 0.020 BASIC      |      |  |  |  |  |

| L      | 0.45                                                      | 0.75     | .018             | .030 |  |  |  |  |

| N      | SEE VARIATIONS                                            |          | SEE VARIATIONS   |      |  |  |  |  |

| α      | 0°                                                        | 8°       | 0°               | 8°   |  |  |  |  |

| aaa    |                                                           | 0.10     |                  | .004 |  |  |  |  |

#### VARIATIONS

| N                                            | D m   | ım.   | D (inch) |      |  |  |

|----------------------------------------------|-------|-------|----------|------|--|--|

| N                                            | MIN   | MAX   | MIN      | MAX  |  |  |

| 56                                           | 13.90 | 14.10 | .547     | .555 |  |  |

| Reference Doc.: JEDEC Publication 95, MO-153 |       |       |          |      |  |  |

10-0039

# **Ordering Information**

| Part / Order Number | Shipping Packaging | Package      | Temperature |

|---------------------|--------------------|--------------|-------------|

| 932S208DFLF         | Tubes              | 56-pin SSOP  | 0 to +70° C |

| 932S208DFLFT        | Tape and Reel      | 56-pin SSOP  | 0 to +70° C |

| 932S208DGLN         | Tubes              | 56-pin TSSOP | 0 to +70° C |

| 932S208DGLNT        | Tape and Reel      | 56-pin TSSOP | 0 to +70° C |

| 932S208DGLF         | Tubes              | 56-pin TSSOP | 0 to +70° C |

| 932S208DGLFT        | Tape and Reel      | 56-pin TSSOP | 0 to +70° C |

"LF" or "LN" suffix are the Annealed Pb-Free configuration, RoHS compliant.

"D" is the device revision designator (will not correlate to with the datasheet revision).

## **Revision History**

| Rev. | Issue Date | Description                                  | Page # |

|------|------------|----------------------------------------------|--------|

| F    | 12/2/2008  | Removed ICS prefix from ordering information | 12-20  |

| G    | 1/26/2010  | Updated document template                    |        |

| Н    | 3/15/2013  | Updated ordering information                 | 20     |

|      |            |                                              |        |

|      |            |                                              |        |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.