# **TMC2601**

# Digital Video Serial Transmission Encoder 8- or 10-bit Parallel Data Into Serial Format 140-370 MHz Output Frequency

### **Features**

- 0.6 µ CMOS technology

- Single +5 V power supply

- 44 pin PQFP or PLCC

- 0.5 W typical power dissipation

- 140-370 Megabit/s data rate

- Complies with the following digital video interface standards:

- SMPTE 259MBit-Serial 4:2:2 Component (D1)

- SMPTE 125MBit-Parallel 4:2:2 Component (D1)

- SMPTE 244MBit-Parallel 4\*f<sub>SC</sub> NTSC Composite (D2)

- Accepts 8- or 10-bit TTL or CMOS-compatible parallel data

- Outputs differential pseudo-ECL serial data and clock

- Byte sync on Timing Reference Signal (TRS)

- Modulo 2 division by  $G(X) = (X^9 + X^4 + 1)*(X+1)$ scrambler

- Phase-locked loop clock synthesizer

- Transmitter jitter < 500 ps at 270 Mb/s

- · Power saving feature on unused clock and data outputs

### **Applications**

- Encoder for 140 to 370 Mb/s serial data

- · Serial transmission interface for:

$\begin{array}{lll} - & \text{Video cameras} & 360 \text{ Mb/s} \\ - & 4:2:2 \text{ signals} & 270 \text{ Mb/s} \\ - & 4*f_{\text{sc}} \text{ PAL} & 177 \text{ Mb/s} \\ - & 4*f_{\text{sc}} \text{ NTSC} & 143 \text{ Mb/s} \end{array}$

### **Description**

The TMC2601 is a CMOS integrated circuit which can serialize 8- or 10-bit parallel data streams, including SMPTE 125M, CCIR 656, and SMPTE 244M. Fixed functions include parallel-to-serial conversion and 10-fold clock frequency multiplication. The user may also enable sync (TRS word) detection, data scrambling ( $\rm X^9 + \rm X^4 + 1$ ), and conversion of NRZ serial data into NRZI format (X+1). Using control bis FS<sub>1-0</sub>, the user may select a nominal operating frequency of 143, 177, 270, or 360MHz.

The TMC2601 provides pseudo-ECL outputs: complementary for the serial data and serial clock, single-ended for the regenerated parallel clock. It requires a single 5-volt supply and consumes less than 1/2 watt while driving 100-ohm loads.

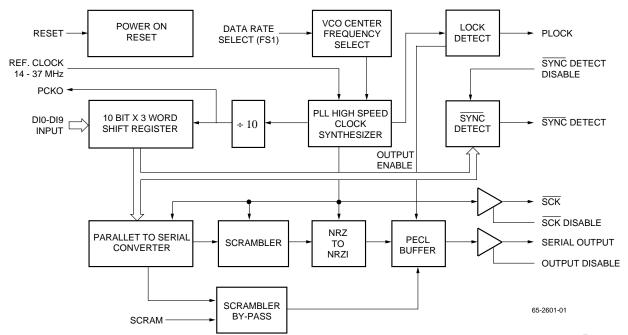

### **Block Diagram**

Rev 1.00

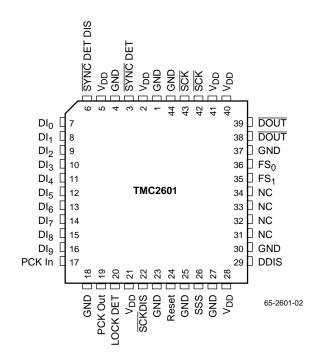

### **Pin Assignments**

# **Pin Descriptions**

| Pin Name          | Pin Number | Туре    | Pin Function Description                                                                                                                                                           |

|-------------------|------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND               | 1          | Supply  | Ground                                                                                                                                                                             |

| V <sub>DD</sub>   | 2          | Supply  | +5V supply                                                                                                                                                                         |

| SYNC DET          | 3          | TTL out | TRS detected flag. If and only if DI <sub>9-2</sub> =FFh or 00h, flag does low on the following clock cycle.                                                                       |

| GND               | 4          | Supply  | Ground                                                                                                                                                                             |

| V <sub>DD</sub>   | 5          | Supply  | +5V supply                                                                                                                                                                         |

| SYNC DET DIS      | 6          | TTL in  | TRS formatter disable. When low, chip forces $\mathrm{DI}_{1-0}$ to 00b if $\mathrm{DI}_{9-2}$ =00h and to 11b if $\mathrm{DI}_{9-2}$ =FF. When high, passes input data unaltered. |

| DI <sub>0-9</sub> | 7-16       | TTL in  | Bit-parallel Input data DI <sub>0</sub> is LSB in 10-Bit mode LSB, DI2 is LSB in 8-Bit mode. DI <sub>9</sub> is MSB in all modes                                                   |

| PCK In            | 17         | TTL in  | Parallel clock input. Rising edge strobes DI9-0 into chip.                                                                                                                         |

| GND               | 18         | Supply  | Ground                                                                                                                                                                             |

| PCK Out           | 19         | ECL out | Parallel clock output. This pseudo-ECL signal is derived from the internal VCO and maintains a constant phase relationship with PCKI when the loop is locked.                      |

| LOCK DET          | 20         | TTL out | Phase locked flag goes high when the loop is locked.                                                                                                                               |

| $V_{DD}$          | 21         | Supply  | +5V supply                                                                                                                                                                         |

### Pin Descriptions (continued)

| Pin Name          | Pin Number | Туре    | Pin Function Description                                                                                           |

|-------------------|------------|---------|--------------------------------------------------------------------------------------------------------------------|

| SCKDIS            | 22         | TTL in  | Grounding this pin disables the serial clock output. <sup>1</sup>                                                  |

| GND               | 23         | Supply  | Ground                                                                                                             |

| Reset             | 24         | TTL in  | When forced high, this pin (which has an internal pull-down) resets the part.                                      |

| GND               | 25         | Supply  | Ground                                                                                                             |

| SSS               | 26         | TTL in  | When high, this pin bypasses the scrambler and NRZI conversion blocks, providing direct serialization of the data. |

| GND               | 27         | Supply  | Ground                                                                                                             |

| V <sub>DD</sub>   | 28         | Supply  | +5V supply                                                                                                         |

| DDIS              | 29         | TTL in  | Grounding this pin disables the serial data output.1                                                               |

| GND               | 30         | Supply  | Ground                                                                                                             |

| NC                | 34:31      | NC      | May be grounded directly or via a resistor.                                                                        |

| FS <sub>1-0</sub> | 35-36      | TTL in  | Frequency select input. Selects VCO frequency range                                                                |

| GND               | 37         | Supply  | Ground                                                                                                             |

| DOUT              | 38         | ECL out | Differential pseudo-ECL serial data output requiring an external >100-ohm resistor to DOUT.                        |

| DOUT              | 39         | ECL out | Differential serial data output, compement of DOUT.                                                                |

| V <sub>DD</sub>   | 40         | Supply  | +5V supply                                                                                                         |

| V <sub>DD</sub>   | 41         | Supply  | +5V supply                                                                                                         |

| SCK               | 42         | ECL out | Differential pseudo-ECL serial clock output, requiring external 100-ohm resistor to SCK.                           |

| SCK               | 43         | ECL out | Differential serial clock output, complement to SCK.                                                               |

| GND               | 44         | Supply  | Ground                                                                                                             |

### Note

<sup>1.</sup> These pins may be left open or AC coupled. Do not DC couple to ground unless the corresponding output is to be disabled; logic 1 or high-Z (due to internal pull up) enables the output and 0 disables it.

### **Functional Description**

The TMC2601 serializer is a CMOS integrated circuit which converts parallel data in a format such as SMPTE125M or SMPTE244M into a serial format, such as SMPTE 259M. It encodes 8- or 10-bit TTL-compatible parallel signals into serial differential pseudo-ECL signals at up to 370Mb/s. It operates from a single 5V supply and is packaged in a 44-pin PLCC.

The internal functional blocks include the sync detector, data serializer, polynomial scrambler and NRZ to NRZI converter, and 10-fold clock frequency multiplier.

### Sync Detector

On each rising edge of PCKI, the Sync Detector looks for combinations of all 1's or all 0's on pins  $DI_{9-2}$ . Whenever it encounters one of these combinations, the Sync Detector drives  $\overline{\text{SYNC}}$  DET low on the next parallel clock cycle. If control  $\overline{\text{SYNC}}$  DET DIS is low, it also overrides  $DI_{1-0}$  to match  $DI_{9-2}$ , such that 000 through 003 (hex) become 000, and 3FC through 3FF become 3FF, to comply with SMPTE259.

### **Polynomial Scrambler**

This feedback shift register pseudorandomizes the incoming data, using the SMPTE-specified fixed polynomial  $X^9 + X^4 + 1$ , thereby minimizing the DC component in the output stream. A second polynomial operator, cascaded with the first and based on X+1, converts NRZ data into NRZI, turning any long sequences of 1's into series of transitions. When high, control SSS bypasses these two blocks, allowing direct serialization of the incoming data.

### **Phase-Locked Loop**

The PLL, which multiplies the clock frequency by 10, comprises a phase detector, a charge pump, a loop filter, a VCO, and a divide-by-ten counter. On each parallel clock cycle, the loop filter receives a charge proportional to the phase error and perturbs the VCO's frequency appropriately.

### **VCO Frequency Selector**

The chip provides four nominal frequency ranges, selected by FS<sub>1-0</sub>, as follows:

| FS <sub>0</sub> | FS <sub>1</sub> | Nominal Frequency (MHz) |

|-----------------|-----------------|-------------------------|

| 0               | 0               | 270 (D1)                |

| 0               | 1               | 360                     |

| 1               | 0               | 143 (NTSC D2)           |

| 1               | 1               | 177 (PAL D2)            |

The lock detect circuit disables the serial data output when the loop is not locked, at which time the Lock Detect flag will be low.

Complementary serial data emerge on SDO and SDO, whereas the serial clock appears on SCK and SCK. To reduce system noise and to save power, user not needing the serial clock may disable it by grounding LOOPF/SCKDIS.

The chip also provides a single-ended ECL parallel clock output, PCKO, regenerated from the internal PLL.

### **Absolute Maximum Ratings**

| Parameter                                                   | Min.  | Тур. | Max.               | Units |

|-------------------------------------------------------------|-------|------|--------------------|-------|

| Power Supply Voltage, V <sub>DD</sub>                       | -0.5  |      | 7.0                | V     |

| Digital Inputs                                              |       | •    |                    |       |

| Applied Voltage <sup>2</sup>                                | -0.5  |      | $V_{\rm DD}$ + 0.5 | V     |

| Forced Current <sup>3,4</sup>                               | -20.0 |      | 20.0               | mA    |

| Outputs                                                     |       |      |                    |       |

| Applied Voltage <sup>2</sup>                                | -0.5  |      | $V_{\rm DD} + 0.5$ | V     |

| Forced Current <sup>3,4</sup>                               | -3.0  |      | 6.0                | mA    |

| Short Circuit Duration (single output in HIGH State to GND) |       |      |                    |       |

| Temperature                                                 |       |      | 1                  |       |

| Operating, Ambient                                          | 0     |      | 70                 | °C    |

| Junction                                                    |       |      | 140                | °C    |

| Storage                                                     | -65   |      | 150                | °C    |

| Lead Soldering (10 seconds)                                 |       |      | 300                | °C    |

| Vapor Phase Soldering (1 minute)                            |       |      | 220                | °C    |

### Notes:

- 1. Absolute maximum ratings are limiting values applied individually while all other parameters are within specified operating conditions. Functional operation under any of these conditions is NOT implied.

- 2. Applied voltage must be current limited to specified range, and measured with respect to GND.

- 3. Forcing voltage must be limited to specified range.

- 4. Current is specified as conventional current, flowing into the device.

## **Operating Conditions**

| Paramete        | Parameter                              |      | Тур. | Max. | Units |

|-----------------|----------------------------------------|------|------|------|-------|

| V <sub>DD</sub> | Supply voltage                         | 4.75 |      | 5.25 | V     |

| V <sub>IH</sub> | Digital inputs, HIGH                   | 2.0  |      |      | V     |

| V <sub>IL</sub> | Digital inputs, LOW                    |      |      | 0.8  | V     |

| t <sub>S</sub>  | Data setup (to PCKI rising edge)       | 5    |      |      | ns    |

| t <sub>H</sub>  | Data hold (from PCKI rising edge)      | 0    |      |      | ns    |

| tPWH            | Parallel clock pulse width HIGH (PCKI) | 8    |      |      | ns    |

| tPWL            | Parallel clock pulse width LOW (PCKI)  | 8    |      |      | ns    |

# **Electrical Characteristics**

| Paramete         | er                                                   | Min.   | Тур. | Max. | Units |

|------------------|------------------------------------------------------|--------|------|------|-------|

| Power Co         | wer Consumption I <sub>DD</sub>                      |        |      | 800  | mW    |

| V <sub>OHS</sub> | Serial output high logic level, from V <sub>DD</sub> | -0.875 |      | -0.7 | V     |

| V <sub>OLS</sub> | Serial output low logic level, from V <sub>DD</sub>  | -1.8   |      | -1.5 | V     |

| V <sub>OHP</sub> | TTL output high logic level                          | 2.4    |      |      | V     |

| V <sub>OLP</sub> | TTL output low logic level                           |        |      | 0.5  | V     |

| I <sub>IH</sub>  | TTL input high current                               | -50    |      | 50   |       |

| I <sub>IL</sub>  | TTL input low current                                | -50    |      | 50   |       |

# **Switching Characteristics**

| Parameter                             |                                      | Conditions               | Min. | Тур. | Max. | Units |

|---------------------------------------|--------------------------------------|--------------------------|------|------|------|-------|

| f <sub>OUT</sub>                      | Output clock & bit rate              | R <sub>L</sub> =100 ohms | 110  |      | 400  | MHz   |

| V <sub>SD</sub>                       | Output data & clock amplitude, p-p   |                          | 700  |      | 850  | mV    |

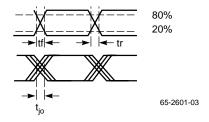

| t <sub>jo</sub>                       | Output clock jitter                  | 270Mb/s                  |      |      | 700  | ps    |

| t <sub>D</sub>                        | Serial clock to data lag             |                          |      | 1.4  |      | ns    |

| SDO t <sub>R</sub> /t <sub>F</sub>    | Serial Data Output Rise/Fall time    |                          |      | 650  |      |       |

| t <sub>LOCK</sub>                     | Lock Time                            |                          |      | 25   |      |       |

| f <sub>PCKOUT</sub>                   | Parallel Clock Output Frequency      |                          | 11   |      |      | 40    |

| PCKOUT t <sub>R</sub> /t <sub>F</sub> | Parallel Clock Output Rise/Fall Time |                          |      | 700  |      |       |

| V <sub>PCKOUT</sub>                   | Parallel Clock Output Signal Swing   |                          |      | 950  |      |       |

| t <sub>jPCKOUT</sub>                  | Parallel Clock Output Jitter         |                          |      |      |      | 700   |

# **Preliminary Information**

# **Input Timing**

PCKI

DATA 9-0

# **Output Timing**

$\mathsf{DOUT},\,\overline{\mathsf{DOUT}}$

DOUT, DOUT

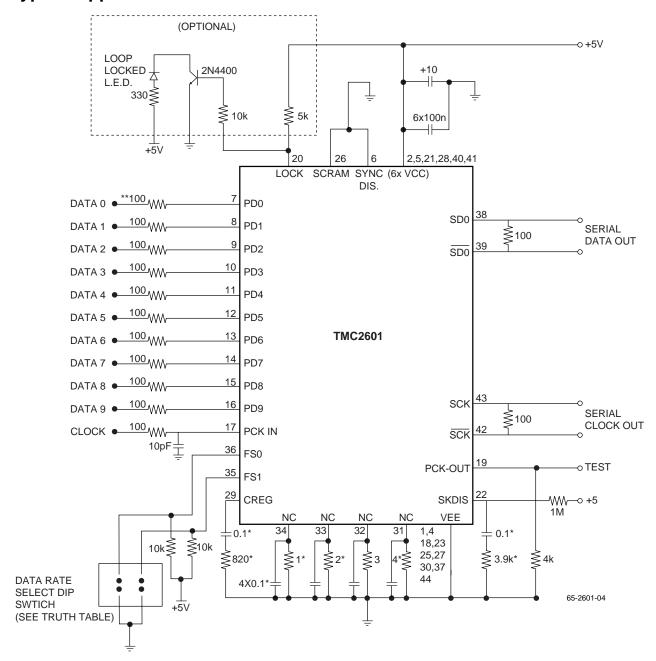

# **Typical Application Circuit**

### Notes:

All resistors in ohms, all capacitors in microfarads unless otherwise stated.

<sup>\*</sup>These components may be omitted, without affecting functionality. See Text.

<sup>\*\*</sup>These resistors slow down fast INPUT edges (≤500ps) and prevent the input signals from ringing.

# **Preliminary Information**

# **Equivalent Circuits and Threshold Levels**

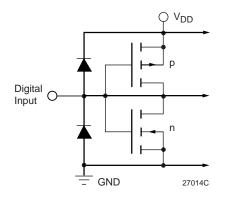

Figure 1. Equivalent Digital Input Circuit

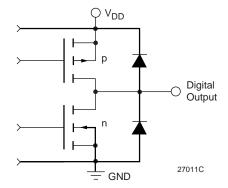

Figure 2. Equivalent Digital Output Circuit

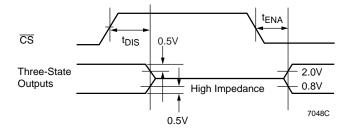

Figure 3. Threshold Levels for Three-State Measurements

# **Notes:**

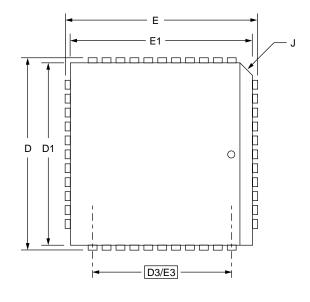

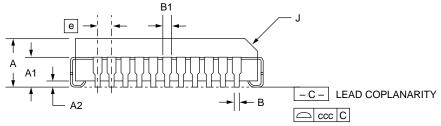

# **Mechanical Dimensions – 44-Pin PLCC Package**

| Cumbal | Inc  | hes      | Millimeters |       | Notes |

|--------|------|----------|-------------|-------|-------|

| Symbol | Min. | Max.     | Min.        | Max.  | Notes |

| Α      | .165 | .180     | 4.20        | 4.57  |       |

| A1     | .090 | .120     | 2.29        | 3.04  |       |

| A2     | .020 | _        | .51         | _     |       |

| В      | .013 | .021     | .33         | .53   |       |

| B1     | .026 | .032     | .66         | .81   |       |

| D/E    | .685 | .695     | 17.40       | 17.65 |       |

| D1/E1  | .650 | .656     | 16.51       | 16.66 | 3     |

| D3/E3  | .500 | .500 BSC |             | BSC   |       |

| е      | .050 | BSC      | 1.27        | BSC   |       |

| J      | .042 | .056     | 1.07        | 1.42  | 2     |

| ND/NE  | 1    | 1        | 11          |       |       |

| N      | 4    | 4        | 44          |       |       |

| CCC    |      | .004     |             | 0.10  |       |

### Notes:

- 1. All dimensions and tolerances conform to ANSI Y14.5M-1982

- 2. Corner and edge chamfer (J) =  $45^{\circ}$

- 3. Dimension D1 and E1 do not include mold protrusion. Allowable protrusion is .101" (.25mm)

TMC2601 PRODUCT SPECIFICATION

### **Ordering Information**

| Product Number | Temperature Range | Screening  | Package      | Package Marking |

|----------------|-------------------|------------|--------------|-----------------|

| TMC2601R2C     | 0°C to 70°C       | Commercial | 44-Lead PLCC | 2601R2C         |

### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com