National Semiconductor is now part of

Texas Instruments.

Search <u>http://www.ti.com/</u> for the latest technical

information and details on our current products and services.

# LM96530 Ultrasound Transmit/Receive Switch

# LM96530

# **Ultrasound Transmit/Receive Switch**

### **General Description**

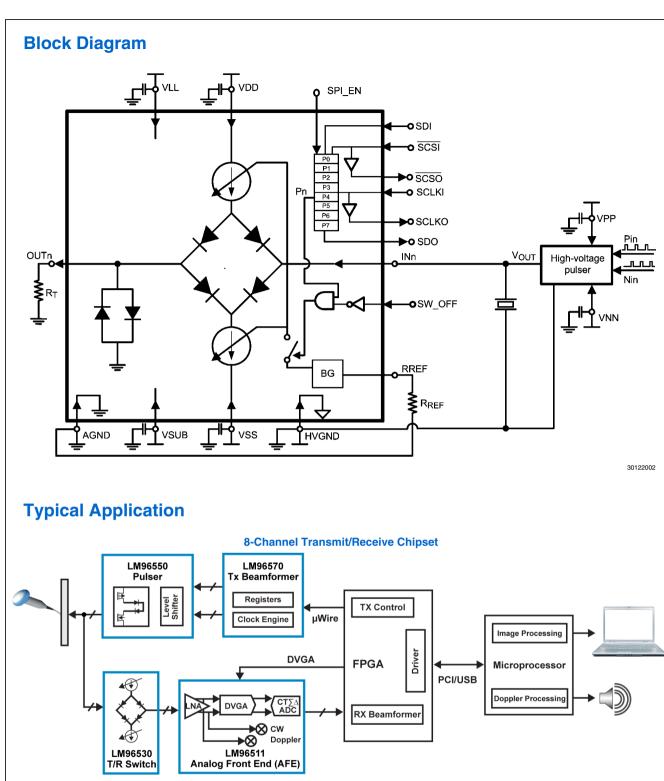

The LM96530 is an eight-channel monolithic high-voltage, high-speed T/R (Transmit/Receive) switch for multi-channel medical ultrasound applications. It is well-suited for use with National's LM965XX series chipset which offers a complete medical ultrasound solution targeted towards low-power, portable systems.

The LM96530 contains eight high-voltage T/R switches with integrated clamping diodes. This chip protects the inputs of the receive channel's LNA (Low Noise Amplifier) from the high-voltage pulses of the transmit channel. Advanced features include a diode bridge with internal current sources that are programmable via an external resistor. Low-power operation is enabled via per-channel-selectable switching.

National Semiconductor also offers a development package for sale which includes a driver hardware and software package with a graphical user interface for configuration and monitoring.

### **Applications**

Ultrasound Imaging

### **Features**

- 8-channel high-voltage receive side switches without charge-injection

- Can be used for receive protection and/or receive multiplexing with SPI<sup>TM</sup> compatible bus control

- Channel bandwidth supports 1MHz to 20MHz transducers

- Input accepts pulses and continuous-wave signals within ±60V

- Integrated output clamping diodes limit output to ±0.7V

- Low harmonic distortion HD2 at -75dBc at 5MHz

- Continuous-wave operation

- Soft-switcher based on a diode bridge architecture yielding better noise performance and faster turn-on and off times than competing T-gate switch architectures

- 2.5V to 3.3V CMOS SPI<sup>™</sup> compatible logic interface with daisy chain capability

- Bias current source (I<sub>S</sub>) can be scaled between 0 and 8mA via an external resistor

### **Key Specifications**

| Input voltage                                  | ±60      | V      |

|------------------------------------------------|----------|--------|

| Output voltage<br>clamp (I <sub>S</sub> = 1mA) | ±0.7     | V      |

| On-resistance                                  | 18       | Ω      |

| Off-isolation @<br>5MHz                        | -58      | dB     |

| Noise spectral<br>density @ 5MHz               | 0.5      | nV/√Hz |

| Harmonic<br>distortion                         |          |        |

| HD2                                            | -75      | dB     |

| HD3                                            | -75      | dB     |

| Channel crosstalk<br>@ 5MHz                    | -73      | dB     |

| Operating Temp.                                | 0 to +70 | °C     |

30122007

| Package Type | NSC Package Drawing | Supplied As |

|--------------|---------------------|-------------|

|              |                     | 1000        |

| 60 Lead LLP  | SQA60A              | 250         |

|              |                     | 2000        |

|              |                     |             |

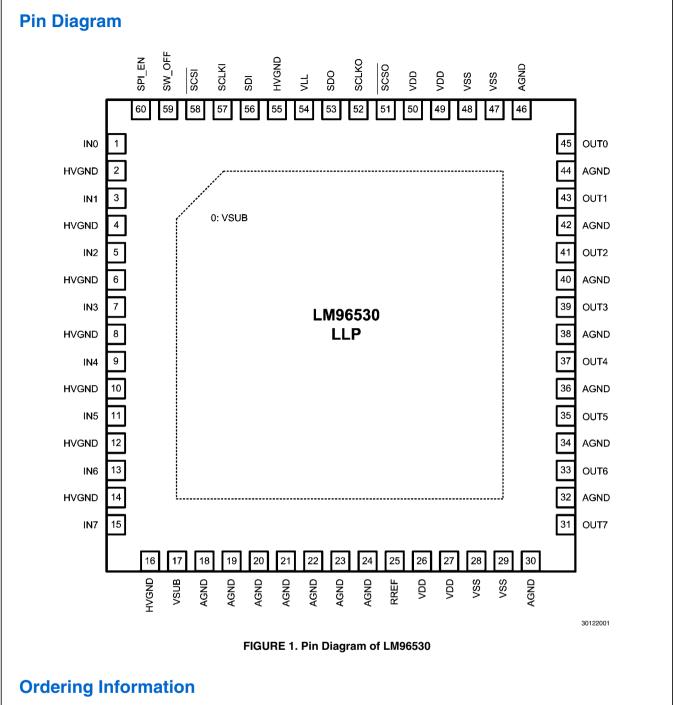

## **TABLE 1. Pin Descriptions**

| Pin No.                           | Name          | Туре   | Function and Connection                                                                                                                                                                                                                                                                                                             |

|-----------------------------------|---------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 3, 5, 7, 9, 11, 13,<br>15      | INn<br>n=0,,7 | Input  | High-voltage input                                                                                                                                                                                                                                                                                                                  |

| 45, 43, 41, 39, 37,<br>35, 33, 31 | OUTn<br>n=0,  | Output | Low-voltage output                                                                                                                                                                                                                                                                                                                  |

| 25                                | RREF          | Output | External resistor to AGND. Used to set internal current sources.<br>$R_{REF} = 6.25 \text{ k}\Omega \rightarrow I_S = 8\text{mA};$<br>$R_{REF} = 12.5 \text{ k}\Omega \rightarrow I_S = 4\text{mA};$<br>$R_{REF} = 25 \text{ k}\Omega \rightarrow I_S = 2\text{mA};$<br>$R_{REF} = 50 \text{ k}\Omega \rightarrow I_S = 1\text{mA}$ |

| 59                                | SW_OFF        | Input  | 1 = Switch all channels OFF<br>0 = Use SPI™ to control switch                                                                                                                                                                                                                                                                       |

| 60                                | SPI_EN        | Input  | <ul> <li>1 = Enable the SPI<sup>™</sup> Interface</li> <li>0 = Disable the SPI<sup>™</sup> Interface and presets SPI<sup>™</sup> registers for all switches ON.</li> </ul>                                                                                                                                                          |

| 58                                | SCSI          | Input  | SPI™ chip select input,<br>0 = Chip Select                                                                                                                                                                                                                                                                                          |

| 57                                | SCKI          | Input  | SPI™ compatible clock input                                                                                                                                                                                                                                                                                                         |

| 56                                | SDI           | Input  | SPI™ compatible data input                                                                                                                                                                                                                                                                                                          |

| 53                                | SDO           | Output | SPI™ compatible data buffered output                                                                                                                                                                                                                                                                                                |

| 52                                | SCKO          | Output | SPI™ compatible clock buffered output                                                                                                                                                                                                                                                                                               |

| 51                                | SCSO          | Output | SPI™ chip select buffered output                                                                                                                                                                                                                                                                                                    |

| 26, 27, 49, 50                    | VDD           | Power  | Positive analog supply voltage (+5V)                                                                                                                                                                                                                                                                                                |

| 28, 29, 47, 48                    | VSS           | Power  | Negative analog supply voltage (-5V)                                                                                                                                                                                                                                                                                                |

| 54                                | VLL           | Power  | Logic voltage supply (+2.5 to 3.3V)                                                                                                                                                                                                                                                                                                 |

| 0, 17                             | VSUB          | Power  | Negative high voltage supply (-65V)                                                                                                                                                                                                                                                                                                 |

| 2, 4, 6, 8, 10, 12,<br>14, 16, 55 | HVGND         | Ground | High voltage reference potential (0V)                                                                                                                                                                                                                                                                                               |

| All others                        | AGND          | Ground | Analog and logic low voltage reference input, logic ground (0V)                                                                                                                                                                                                                                                                     |

SPI<sup>™</sup> is a trademark of Motorola, Inc.

### Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Maximum Junction Temperature (T <sub>JMAX</sub> ) | +150°C                                            |

|---------------------------------------------------|---------------------------------------------------|

| Storage Temperature Range                         | –40°C to +125°C                                   |

| Supply Voltage (VDD)                              | +0.3V to +5.5V                                    |

| Supply Voltage (VSS)                              | +0.3V and -5.5V                                   |

| Supply Voltage (VSUB)                             | -70V (Must<br>always be most<br>negative voltage) |

| IO Supply Voltage (VLL)                           | -0.3V to +3.6V                                    |

Voltage at High Voltage Analog Inputs Voltage at Logic Inputs (SCLKI, SDI SCSI, SW\_OFF)

# **Operating Ratings**

| Operation Junction Temperature               | 0°C to + 70°C     |

|----------------------------------------------|-------------------|

| VDD, –VSS, Analog Supply                     | +4.7V to 5.3V     |

| VLL, Logic Supply                            | +2.4V to 3.5V     |

| High Voltage Analog Inputs                   | -60V to +60V,     |

|                                              | VSUB must be most |

|                                              | negative supply   |

| VSUB, Substrate bias supply                  | -50V to -65V      |

| Package Thermal Resistance ( $\theta_{JA}$ ) | 20°C/W            |

| ESD Tolerance                                |                   |

| Human Body Model                             | 2kV               |

| Machine Model                                | 150V              |

| Charge Device Model                          | 750V              |

### **Analog Characteristics**

Unless otherwise stated, the following conditions apply.

| VLL = +2.5V, | VDD = -VSS = 5V, VSUB = - | -60V, $R_{REF} = 50 \text{ k}\Omega$ , $R_T = 50\Omega$ , $f_{IN} = 5$ | MHz, SW_O | FF = SPI_EI | N = 0V, T <sub>A</sub> = | 25°C. |

|--------------|---------------------------|------------------------------------------------------------------------|-----------|-------------|--------------------------|-------|

|              |                           |                                                                        |           |             |                          |       |

| Symbol                | Parameter                  | Conditions                                                   | Min | Тур  | Max | Units  |

|-----------------------|----------------------------|--------------------------------------------------------------|-----|------|-----|--------|

| V <sub>IN</sub>       | High Voltage Analog Inputs | VSUB must be most negative voltage.<br>See ( <i>Note 2</i> ) | -60 |      | +60 | V      |

| e <sub>n</sub>        | Voltage Noise              | at 5MHz                                                      |     | 0.8  |     | nV/√Hz |

| BW                    | -3dB Bandwidth             |                                                              |     | 150  |     | MHz    |

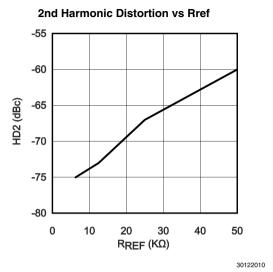

| HD2                   | Second harmonic distortion |                                                              |     | -60  |     | dBc    |

| HD3                   | Third harmonic distortion  | 0.1V <sub>PP</sub> 5MHz tone applied as input                |     | -65  |     | dBc    |

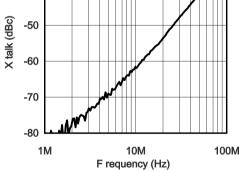

| X <sub>TALK</sub>     | Channel crosstalk          |                                                              |     | -69  |     | dB     |

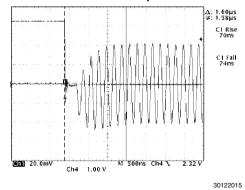

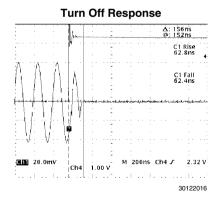

| T <sub>ON</sub>       | Turn-on time               |                                                              |     | 2    |     | μs     |

| T <sub>OFF</sub>      | Turn-off time              |                                                              |     | 0.2  |     | μs     |

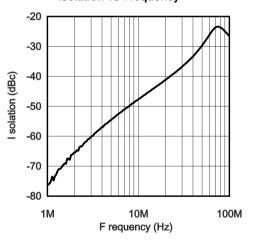

| lso_off               | Off isolation              | 0.1Vpp 5MHz tone is applied as input                         |     | -55  |     | dB     |

| R <sub>ON</sub>       | On resistance of TR switch |                                                              |     | 125  |     | Ω      |

| IL                    | Insertion Loss             | f <sub>IN</sub> = 5MHz                                       |     | -5.5 |     | dB     |

| V <sub>CLAMP</sub>    | Output clamped voltage     |                                                              |     | ±0.7 |     | V      |

| I <sub>MISMATCH</sub> | Current source mis-match   |                                                              |     | 0.03 | 0.2 | mA     |

| VDD & VSS             |                            |                                                              |     | 14   | 20  | mA     |

| VLL                   | Power Supply Current       |                                                              |     | 5    |     | μA     |

| VSUB                  |                            |                                                              |     | 0.45 |     | mA     |

-70V to 70V

-0.3V to VLL

+0.3v

| Symbol             | Parameter                  | Conditions                                                   | Min | Тур   | Max  | Units  |

|--------------------|----------------------------|--------------------------------------------------------------|-----|-------|------|--------|

| V <sub>IN</sub>    | High Voltage Analog Inputs | VSUB must be most negative voltage.<br>See ( <i>Note 2</i> ) | -60 |       | +60  | v      |

| e <sub>n</sub>     | Voltage Noise              | at 5MHz                                                      |     | 0.7   |      | nV/√Hz |

| BW                 | -3dB Bandwidth             |                                                              |     | 150   |      | MHz    |

| HD2                | Second harmonic distortion |                                                              |     | -67   |      | dBc    |

| HD3                | Third harmonic distortion  | 0.1V <sub>PP</sub> 5MHz tone applied as input                |     | -70   |      | dBc    |

| X <sub>TALK</sub>  | Channel crosstalk          |                                                              |     | -73   |      | dB     |

| T <sub>ON</sub>    | Turn-on time               |                                                              |     | 2     |      | μs     |

| T <sub>OFF</sub>   | Turn-off time              |                                                              |     | 0.2   |      | μs     |

| lso_off            | Off isolation              | 0.1Vpp 5MHz tone is applied as input                         |     | -58   |      | dB     |

| R <sub>ON</sub>    | On resistance of TR switch |                                                              |     | 48    |      | Ω      |

| IL                 | Insertion Loss             | f <sub>IN</sub> = 5MHz                                       |     | -4    |      | dB     |

| V <sub>CLAMP</sub> | Output clamped voltage     |                                                              |     | ±0.75 |      | V      |

| MISMATCH           | Current source mis-match   |                                                              |     | 0.1   | 0.35 | mA     |

| VDD & VSS          |                            |                                                              |     | 23    | 30   | mA     |

| VLL                | Power Supply Current       |                                                              |     | 5     |      | μΑ     |

| VSUB               |                            |                                                              |     | 1     |      | mA     |

| Symbol                | Parameter                  | Conditions                                                   | Min | Тур   | Max | Units  |

|-----------------------|----------------------------|--------------------------------------------------------------|-----|-------|-----|--------|

| V <sub>IN</sub>       | High Voltage Analog Inputs | VSUB must be most negative voltage.<br>See ( <i>Note 2</i> ) | -60 |       | +60 | V      |

| e <sub>n</sub>        | Voltage Noise              | at 5MHz                                                      |     | 0.55  |     | nV/√Hz |

| BW                    | -3dB Bandwidth             |                                                              |     | 180   |     | MHz    |

| HD2                   | Second harmonic distortion |                                                              |     | -73   |     | dBc    |

| HD3                   | Third harmonic distortion  | 0.1V <sub>PP</sub> 5MHz tone applied as input                |     | -75   |     | dBc    |

| X <sub>TALK</sub>     | Channel crosstalk          |                                                              |     | -73   |     | dB     |

| T <sub>ON</sub>       | Turn-on time               |                                                              |     | 2     |     | μs     |

| T <sub>OFF</sub>      | Turn-off time              |                                                              |     | 0.2   |     | μs     |

| lso_off               | Off isolation              | 0.1Vpp 5MHz tone is applied as input                         |     | -58   |     | dB     |

| R <sub>ON</sub>       | On resistance of TR switch |                                                              |     | 27    |     | Ω      |

| IL                    | Insertion Loss             | f <sub>IN</sub> = 5MHz                                       |     | -3    |     | dB     |

| V <sub>CLAMP</sub>    | Output clamped voltage     |                                                              |     | ±0.78 |     | V      |

| I <sub>MISMATCH</sub> | Current source mis-match   |                                                              |     | 0.25  | 0.6 | mA     |

| VDD & VSS             |                            |                                                              |     | 40    | 49  | mA     |

| VLL                   | Power Supply Current       | Γ                                                            |     | 5     |     | μA     |

| VSUB                  |                            | Γ                                                            |     | 2.2   |     | mA     |

| Unless other          | wise stated, the following cond          | litions apply                                                                 |                 |             |                                |                  |

|-----------------------|------------------------------------------|-------------------------------------------------------------------------------|-----------------|-------------|--------------------------------|------------------|

| VLL = +2.5V<br>Symbol | , VDD = -VSS = 5V, VSUB = -<br>Parameter | $-60V, R_{REF} = 6.25 \text{ k}\Omega, R_T = 50\Omega, f_{IN} = 5$ Conditions | MHz, SW_<br>Min | OFF = SPI_E | EN = 0V, T <sub>A</sub><br>Max | = 25°C.<br>Units |

| V <sub>IN</sub>       | High Voltage Analog Inputs               | VSUB must be most negative voltage.<br>See ( <i>Note 2</i> )                  | -60             | Typ         | +60                            | V                |

| e <sub>n</sub>        | Voltage Noise                            | at 5MHz                                                                       |                 | 0.5         |                                | nV/√Hz           |

| BW                    | -3dB Bandwidth                           |                                                                               |                 | 180         |                                | MHz              |

| HD2                   | Second harmonic distortion               |                                                                               |                 | -75         |                                | dBc              |

| HD3                   | Third harmonic distortion                | 0.1V <sub>PP</sub> 5MHz tone applied to input                                 |                 | -75         |                                | dBc              |

| X <sub>TALK</sub>     | Channel crosstalk                        |                                                                               |                 | -73         |                                | dB               |

| T <sub>ON</sub>       | Turn-on time                             |                                                                               |                 | 2           |                                | μs               |

| T <sub>OFF</sub>      | Turn-off time                            |                                                                               |                 | 0.2         |                                | μs               |

| Iso_off               | Off isolation                            | 0.1Vpp 5MHz tone is applied as input                                          |                 | -58         |                                | dB               |

| R <sub>ON</sub>       | On resistance of TR switch               |                                                                               |                 | 18          |                                | Ω                |

| I <sub>L</sub>        | Insertion Loss                           | f <sub>IN</sub> = 5MHz                                                        |                 | -2.5        |                                | dB               |

| V <sub>CLAMP</sub>    | Output clamped voltage                   |                                                                               |                 | ±0.8        |                                | V                |

| I <sub>MISMATCH</sub> | Current source mis-match                 |                                                                               |                 | 0.6         | 1.2                            | mA               |

| VDD & VSS             |                                          |                                                                               |                 | 75          | 86                             | mA               |

| VLL                   | Power Supply Current                     | [                                                                             |                 | 5           |                                | μA               |

| VSUB                  |                                          | [ [                                                                           |                 | 5           |                                | mA               |

### **Digital Characteristics**

Unless otherwise stated, the following conditions apply.

| Symbol                | Parameter                                       | Conditions            | Min | Тур | Max | Unit               |

|-----------------------|-------------------------------------------------|-----------------------|-----|-----|-----|--------------------|

| V <sub>IH</sub>       | Logical Input "HI" Voltage                      |                       | 2   |     |     | V                  |

| V <sub>IL</sub>       | Logical Input "LO" Voltage                      |                       |     |     | 0.5 | V                  |

| I <sub>IN-H/L</sub>   | Logic Input Current                             |                       | -1  | 0.2 | +1  | μΑ                 |

| V <sub>OH</sub>       | Logical Output "HI" Voltage                     |                       | 2.2 |     |     | V                  |

| V <sub>OL</sub>       | Logical Output "LO" Voltage                     |                       |     |     | 0.3 | V                  |

| t <sub>SSELS</sub>    | SPI™ SCSI Setup Time                            |                       | 11  |     |     | ns                 |

| t <sub>SSELH</sub>    | SPI™ SCSI Hold Time                             |                       | 11  |     |     | ns                 |

| t <sub>SSELHI</sub>   | SPI™ SCSI HI Time                               |                       |     | 250 |     | ns                 |

| t <sub>ws</sub>       | SPI™ SDI Setup Time                             |                       | 11  |     |     | ns                 |

| t <sub>WH</sub>       | SPI™ SDI Hold Time                              |                       | 11  |     |     | ns                 |

| t <sub>OD</sub>       | SPI™ SCLKI to SDO<br>Propagation Delay          | C <sub>L</sub> = 5 pF |     |     | 25  | ns                 |

| t <sub>VALID</sub>    | SPI™ SCSI to T/R Switch<br>State Change Delay   |                       |     | 30  |     | ns                 |

| t <sub>SCLK</sub>     | SPI™ SCLKI Period                               |                       | 100 |     |     | ns                 |

|                       | SPI™ SCLKI Duty Cycle                           | See ( <i>Note 5</i> ) | 45  |     | 55  | % of CLM<br>Period |

| t <sub>SCLKOD-H</sub> | SPI™ SCLKI-HI to SCLKO-<br>HI Propagation Delay |                       |     |     | 12  | ns                 |

| t <sub>SCLKOD-L</sub> | SPI™ SCLKI-LO to SCLKO-<br>LO Propagation Delay |                       |     |     | 12  | ns                 |

| t <sub>scsod-н</sub>  | SPI™ SCSI-HI to SCSO-HI<br>Propagation Delay    |                       |     |     | 12  | ns                 |

| t <sub>SCSOD-L</sub>  | SPI™ SCLSI-LO to SCLSO-<br>LO Propagation Delay |                       |     |     | 12  | ns                 |

|                       | Maximum Number of Daisy-<br>Chained devices     | SCLKI Freq. = 10MHz   |     | 16  |     |                    |

Note 1: Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is guaranteed to be functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics.

Note 2: Total input signal levels, including any transient voltage overshoots, must be within this maximum voltage range.

Note 3: The human body model is a 100pF capacitor discharged through a  $1.5k\Omega$  resistor into each pin.

Note 4: Min and Max limits are 100% production tested at 25°C. Limits over the operating temperature range are guaranteed through correlation using Statistical Quality Control (SQC) methods. Limits are used to calculate National's Average Outgoing Quality Level (AOQL).

Note 5: Guarantee by design

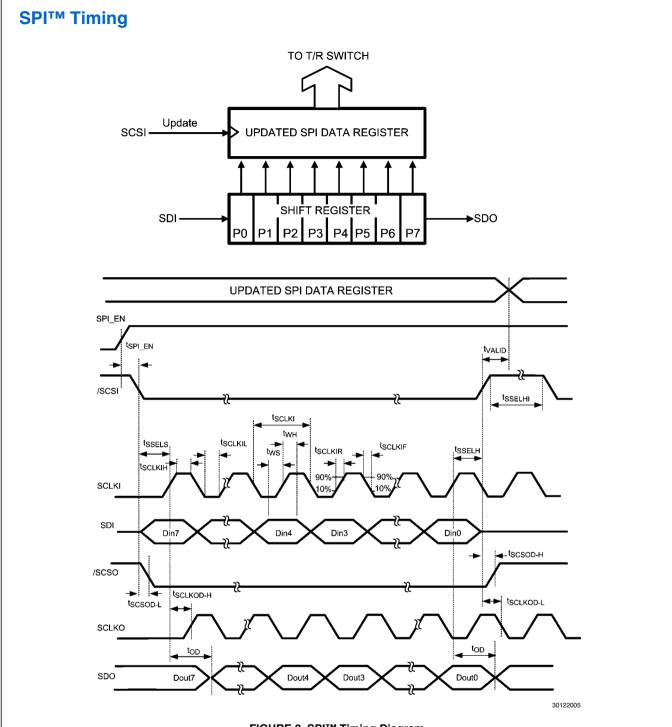

FIGURE 2. SPI™ Timing Diagram

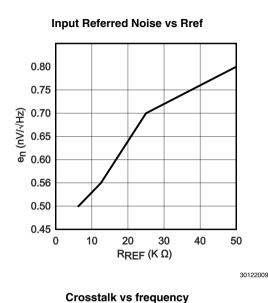

### **Typical Performance Characteristics**

VLL = +2.5V, VDD = -VSS = 5V, VSUB = -60V,  $R_{REF} = 50 \text{ k}\Omega$ ,  $R_{T} = 50\Omega$ ,  $f_{IN} = 5 \text{ MHz}$ ,  $T_{A} = 25^{\circ}\text{C}$ .

Turn On Respone

Isolation vs Frequency

30122012

30122011

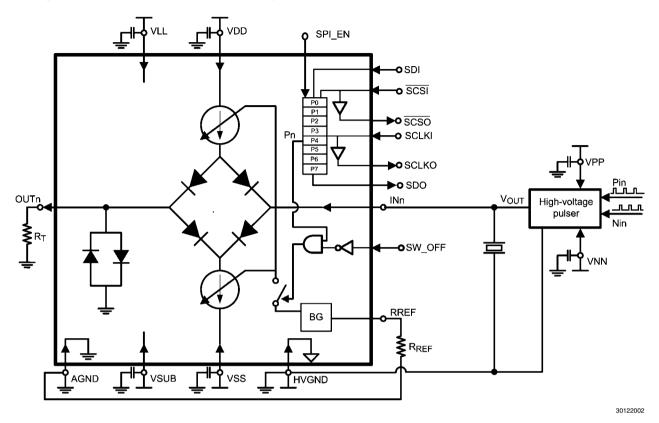

### **Functional Description**

The LM96530 RX switch provides an 8-channel receive side interface solution for medical ultrasound applications suitable for integration into multi-channel (128/256 channel) systems.

Its diode-bridge-based architecture allows high-speed lowdistortion channel designs targeting low-power, portable systems. A complete system can be designed using National's companion LM965XX chipset.

FIGURE 3. Block Diagram of T/R Channel

A functional block diagram of the IC is shown in . Each RX switch channel on the IC has a high-voltage input that can be directly connected to a transducer driven by a high-voltage pulser, such as the LM96550. The input feeds into a diode bridge with its output being diode-clamped to  $\pm$  0.7V. The diode bridge bias current is set to 1 mA with Rref = 50K $\Omega$ . Therefore, the output can be directly connected to a low noise amplifier (LNA) stage which must be protected from the high-voltage signals on the transducer.

The bias current of the bridge is determined by two equallysized current sources with their current value ranging between 0 and 8mA depending on the external resistor Rref at the input of the bandgap reference block. While the bias current is the same value for all channels on the IC, each channel can be switched on and off individually with an 8–bit shift register that is programmed via a SPI<sup>™</sup> compatible bus.

The on-chip analog circuitry requires dual 5V supplies VDD and VSS, a single logic supply VLL, and a high voltage negative bias, VSUB.

### SERIAL INTERFACE OPERATION

The digital interface is comprised of an 8-bit shift register and a latch. Each bit controls one T/R switch channel, where the MSB bit, i.e., the first bit written (D7) controls channel 7, and the LSB bit (D0) controls channel 0. The three input pins, SDI, SCSI and SCKI, are all Schmitt Trigger inputs with 0.5V typical hysteresis. The output pins SDO, SCSO, and SCLKO are SPI<sup>TM</sup> compatible. The serial data input SDI is synchronously read into the shift register on the rising edge of the clock SCKI. When SCSI changes from low to high, the data in the shift register is transferred to the latch circuit, and output on the parallel data signals P0 through P7 which drive the switched bias current sources for channels n=0,..., 7, respectively. When SCSI changes from high to low, the latch output Pn, and thus the biasing condition, does not change.

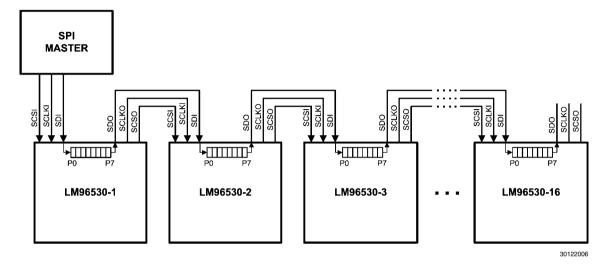

### **DAISY CHAINING MULTIPLE LM96530 ICs**

For connecting multiple T/R switch ICs, the LM965XX SPI<sup>™</sup>compatible bus can be daisy-chained up to 16 ICs at 10MHz SCLKI for easy PCB routing. The inputs SDI, SCSI and SCLKI are daisy-chained together with SDO, SCSO and SCLKO. Therefore, the next IC's SDI is connected to the previous IC's SDO. Similarly, the next IC's SCSI is connected to the previous IC's SCSO, and the next IC's SCLKI is connected to the previous IC's SCLKO, as shown in . Daisy-chaining multiple LM96530 devices amounts to one large shift register with the number of bits being equal to 8 times the number of LM96530 ICs. For example, if 3 LM96530 ICs are daisy-chained, one can picture a 24-bit shift register. Thus, the MSB or first bit written on the SDI line (D23) will control channel 7 of the last LM96530, i.e., the IC that is daisy-chained the farthest away from the SPI master. The LSB or last bit written on the SDI line (D0) will control channel 0 of the first LM96530, i.e., the IC that is closest to the SPI master. It is important to note that If only one particular channel of an IC in the daisy-chain requires updating, all of the ICs, i.e., the entire shift register, must be written to.

FIGURE 4. 16 LM96530 Devices Daisy Chained @ SCLKI = 16MHz

# BASIC OPERATION WITHOUT SERIAL INTERFACE COMMUNICATION

### POWER-UP AND POWER-DOWN SEQUENCES

To disable the SPI<sup>™</sup> compatible interface, connect the pin SPI\_EN to AGND. To reverse bias all 8 channels of the T/R switch, connect the pin, SW\_OFF to VLL. To forward bias all 8 channels of the T/R switch, connect the pin, SW\_OFF to AGND.

VSUB needs to always be the most negative supply – equal to or more negative than VSS or the most negative transmit pulse at all times. The power sequence should be to applied to VSUB first, followed by the remaining supplies in any order.

Physical Dimensions inches (millimeters) unless otherwise noted (8,6 TYP) DIMENSIONS ARE IN MILLIMETERS DIMENSION IN () FOR REFERENCE ONLY (60X 0.8)-(0.1) (60X 0.25) \_ — (56X 0.5) L C -0.8 MAX RECOMMENDED LAND PATTERN - 7.2±0.1 -- (0.1) טַסססססססססססססססס (45°X 0.25) PIN 1 10 -PIN 1 INDEX AREA 4X 7 9±0.1 60X 0.6±0 В ► A 9±0.1 60X 0.25±0.05 0.1@CASBS 0.05@C 56X 0.5 SQA60A (Rev A) 60-Lead LLP Package NS Package Number SQA60A

# Notes

For more National Semiconductor product information and proven design tools, visit the following Web sites at: www.national.com

| Products                       |                              | Design Support                  |                                |

|--------------------------------|------------------------------|---------------------------------|--------------------------------|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH® Tools                  | www.national.com/webench       |

| Audio                          | www.national.com/audio       | App Notes                       | www.national.com/appnotes      |

| Clock and Timing               | www.national.com/timing      | Reference Designs               | www.national.com/refdesigns    |

| Data Converters                | www.national.com/adc         | Samples                         | www.national.com/samples       |

| Interface                      | www.national.com/interface   | Eval Boards                     | www.national.com/evalboards    |

| LVDS                           | www.national.com/lvds        | Packaging                       | www.national.com/packaging     |

| Power Management               | www.national.com/power       | Green Compliance                | www.national.com/quality/green |

| Switching Regulators           | www.national.com/switchers   | Distributors                    | www.national.com/contacts      |

| LDOs                           | www.national.com/ldo         | Quality and Reliability         | www.national.com/quality       |

| LED Lighting                   | www.national.com/led         | Feedback/Support                | www.national.com/feedback      |

| Voltage References             | www.national.com/vref        | Design Made Easy                | www.national.com/easy          |

| PowerWise® Solutions           | www.national.com/powerwise   | Applications & Markets          | www.national.com/solutions     |

| Serial Digital Interface (SDI) | www.national.com/sdi         | Mil/Aero                        | www.national.com/milaero       |

| Temperature Sensors            | www.national.com/tempsensors | SolarMagic™                     | www.national.com/solarmagic    |

| PLL/VCO                        | www.national.com/wireless    | PowerWise® Design<br>University | www.national.com/training      |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

### Copyright© 2011 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959

National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com