EIGHT-BIT PARITY CHECKER and GENERATOR

# MC1046 MC1246

## **Advance Information**

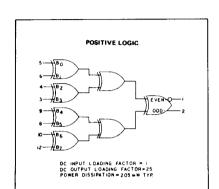

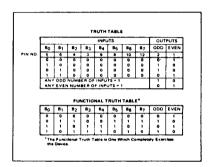

Seven Exclusive-OR gates in a single package, interconnected to provide simultaneous ODD-EVEN parity generation or checking.

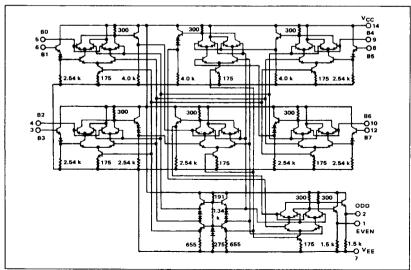

#### CIRCUIT SCHEMATIC

### MC1046, MC1246 (continued)

| ELECTRICAL CHARACTERISTICS @ 25°C |                  |                       |             |        |         | TEST VOLTAGE (Vdc)/CURRENT (mAdc) VALUES |              |                       |                         |     |     |

|-----------------------------------|------------------|-----------------------|-------------|--------|---------|------------------------------------------|--------------|-----------------------|-------------------------|-----|-----|

| Characteristic                    | Symbol           | Pin<br>Under<br>Test  | Test Limits |        | Unit    | VIL                                      | VIH          | V <sub>IH max</sub>   | VEE                     | vcc | 1,  |

|                                   |                  |                       | Min         | Max    | Unit    | -1 500                                   | -0 850       | -0.700                | -5 2                    | Gnd | -25 |

| Power Supply Drain Current        | ¹E               | ,                     |             | 53     | mAdic   |                                          |              |                       | 3,4,5 6,7,<br>8,9,10,12 | 14  | 1   |

| Input Current                     | *l <sub>in</sub> | 3,4,5,6,<br>8,9,10,12 | -           | 100    | μAdc    |                                          |              | 3,4,5,6,<br>8,9,10,12 | , , ,                   | 14  | 1   |

| Input Leakage Current             | *IR              | 3,4,5,6,<br>8,9,10,12 |             | 1.0    | μAdc    |                                          |              |                       | 3,4,5,6,7,<br>8,9,10,12 | 14  | †   |

| Logic "1" Output Voltage          | vон              | 1                     | -0.850      | -0.700 | Vdc     | 3,4,5,6,<br>3,9,10,12                    |              |                       | 7                       | 14  | ,   |

|                                   |                  | 2                     |             |        |         | 3,5,9                                    | 4.6,8,10,12  | İ                     | 1                       | il  | 2   |

|                                   |                  | 1                     |             |        |         | 4,10                                     | 3,5,6,8,9,12 |                       | ļ                       |     | 1   |

|                                   |                  | 2                     | 7           |        | *       | 6,8,12                                   | 3,4,5,9.10   |                       | <b>†</b>                |     | 2   |

| Logic "0" Output Voltage          | VOL              | 2                     | -1.800      | -1.500 | Vdc<br> | 3,4,5,6<br>8,9,10,12                     |              |                       | 7                       | 14  |     |

|                                   |                  | 1                     |             |        |         | 3,5,9                                    | 4,6,8,10,12  |                       |                         |     |     |

|                                   |                  | 2                     | 1           |        |         | 4.10                                     | 3,5,6,8,9,12 | į                     | 1                       |     |     |

|                                   |                  | ¹                     | 7           | . 🕴 ]  |         | 6,8,12                                   | 3,4.5,9.10   |                       | *                       |     |     |

ndividually test each Input using the pin connections shown

<sup>\*\*</sup>Logic "1" limits apply from no load (0 mAdc) to full load (-2.5 mAdc)

| Switching Speed***<br>(fan-out = 15 pF) | Symbol          | Pin<br>Under<br>Test | AC Parameters<br>(typical) | Unit  | Pulse In | Pulse Out | -4.0 Vdc VEE            | +1.2 Vdc VCC |  |

|-----------------------------------------|-----------------|----------------------|----------------------------|-------|----------|-----------|-------------------------|--------------|--|

| Propagation Dalay                       | 112+2+          | 2                    | 13                         | ns    | 12       | 2         | 3. 4, 5, 6, 7, 8, 9, 10 | 14           |  |

|                                         | 112-2-          | 2                    | 14                         | 1 1   | 1        | 1 1       | 1                       | 1 ;          |  |

| Rise Time                               | t2+             | 2                    | 4                          | 111   |          | 1   [     |                         |              |  |

| Fall Time                               | t <sub>2-</sub> | 2                    | 6                          | 1 1 ! |          |           |                         |              |  |

| Propagation Delay                       | t12-1+          | 1                    | 13                         | 111   | -        |           |                         |              |  |

|                                         | t12+1-          | j ,                  | 14                         | 1 1 1 |          | 1 1 1     |                         |              |  |

| Rise Time                               | 11.             | 1                    | 4                          | 111   |          |           |                         | 1            |  |

| Fall Time                               | t <sub>1-</sub> | 1 1                  | 6                          | 🛊     | ÷        |           | •                       | 1            |  |

which presents the longest delay path to the signal. Delays from all other inputs are shorter.

--- 0 V

ty ty - 6 0 ns

#### APPLICATIONS INFORMATION

The MC1046 may be used as a parity checker-generator for EVEN or ODD parity simultaneously.

A highly versatile, can-count saving use of the MC1046 is in a Single-error Hamming Parity Code Detection and Correction circuit as shown here. A system word of 8-bits was used for simplicity in this example although any number of bits may be used.

In this 8-bit system, 4-bits of parity are generated and the 12 bit resulting word (8 message bits and 4-parity bits) is transmitted or otherwise processed. The Hamming Parity Detection circuit re-examines the input MESSAGE BITS exactly as the generator did. However, the parity bits generated at the receiver are compared with the transmitted parity bits via the high-speed MECL II MC1030 (Quad Exclusive "OR" Gate). The output Code (if the interconnections are correct) indicates, in a Binary Code, the bit which was in error. For example, if the output of the MC1030 were 8 = 0, 4 = 1, 2 = 0 and 1 = 1 (0101), the indication would be that the fifth bit was in error.

The system shown does not fully utilize the MC1046 by taking advantage of the 8 inputs and complimentary outputs. However, larger and more complex systems can more fully utilize its available input-output capability.

The state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the state of the s

264