## 4-BIT ARITHMETIC LOGIC UNIT

(With Carry Lookahead)

**DESCRIPTION** — The '40 is a high speed arithmetic logic unit with full onchip carry lookahead circuitry. It can perform the arithmetic operations add or subtract in parallel, or any of six logic functions on two 4-bit binary words. The internal carry lookahead provides either a ripple carry output or carry lookahead outputs. An internal carry input network accepts carry lookahead outputs from up to three other packages producing a 16-bit full carry lookahead ALU without additional gates. Ripple carries can be used between additional blocks of 12 bits to further expand the word length.

- MULTIFUNCTION CAPABILITY

TWO ARITHMETIC OPERATIONS ADD, SUBTRACT

SIX LOGIC FUNCTIONS A EX OR B, A AND B, PLUS FOUR OTHERS

- ADD TWO 4-BIT WORDS IN 23 ns TYPICAL

- SUBTRACT TWO 4-BIT WORDS IN 28 ns

- LOOKAHEAD CARRY INPUT AND OUTPUT NETWORKS ON-CHIP

- EASILY EXPANDABLE TO LONGER WORD LENGTHS

- TYPICAL POWER DISSIPATION OF 425 mW

**ORDERING CODE:** See Section 9

|                    | PIN | COMMERCIAL GRADE                                                                             | MILITARY GRADE                                                                                          | PKG<br>TYPE |  |

|--------------------|-----|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------|--|

| PKGS               | оит | $V_{CC} = +5.0 \text{ V } \pm 5\%,$<br>$T_A = 0^{\circ} \text{ C to } +70^{\circ} \text{ C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$<br>$T_A = -55^{\circ} \text{ C} \text{ to } +125^{\circ} \text{ C}$ |             |  |

| Plastic<br>DIP (P) | Α   | 9340PC                                                                                       |                                                                                                         | 9N          |  |

| Ceramic<br>DIP (D) | А   | 9340DC                                                                                       | 9340DM                                                                                                  | 6N          |  |

| Flatpak<br>(F)     | A   | 9340FC                                                                                       | 9340FM                                                                                                  | 4M          |  |

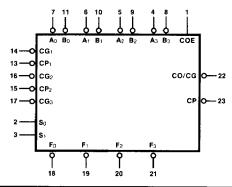

# CONNECTION DIAGRAM PINOUT A

#### LOGIC SYMBOL

Vcc = Pin 24

GND = Pin 12

| PIN NAMES                                                              | DESCRIPTION                                                            | 93XX (U.L.)<br>HIGH/LOW |  |

|------------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------|--|

| $\overline{A_0} - \overline{A_3}$<br>$\overline{B_0} - \overline{B_3}$ | Operand Inputs (Active LOW)                                            | 3.0/3.0                 |  |

| S <sub>0</sub> , S <sub>1</sub>                                        | Mode Select Inputs                                                     | 1.0/1.0                 |  |

| CG <sub>1</sub>                                                        | Carry Generate Input from immediately<br>preceeding stage (Active LOW) | 3.0/3.0                 |  |

| CP <sub>1</sub>                                                        | Carry Propagate Input from immediately preceeding stage (Active LOW)   | 1.0/1.0                 |  |

| ÖG₂                                                                    | Carry Generate Input from second preceeding stage (Active LOW)         | 2.0/2.0                 |  |

| ĈP₂                                                                    | Carry Propagate Input from second preceeding stage (Active LOW)        | 1.0/1.0                 |  |

| G₃                                                                     | Carry Generate Input from third preceeding stage (Active LOW)          | 1.0/1.0                 |  |

| COE                                                                    | Carry Out Enable Input                                                 | 1.5/1.5                 |  |

| 0 — F <sub>3</sub>                                                     | Function Outputs (Active LOW)                                          | 20/10                   |  |

| O/CG<br>P                                                              | Carry Out/Carry Generate Output (Active LOW)                           | 20/10                   |  |

| CP P                                                                   | Carry Propagate Output (Active LOW)                                    | 20/10                   |  |

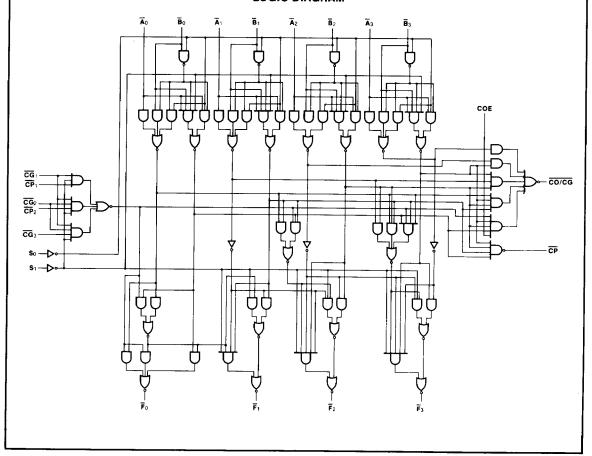

### LOGIC DIAGRAM

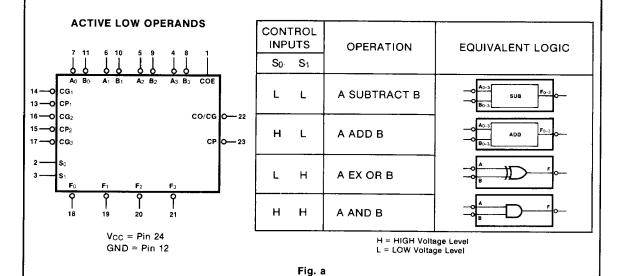

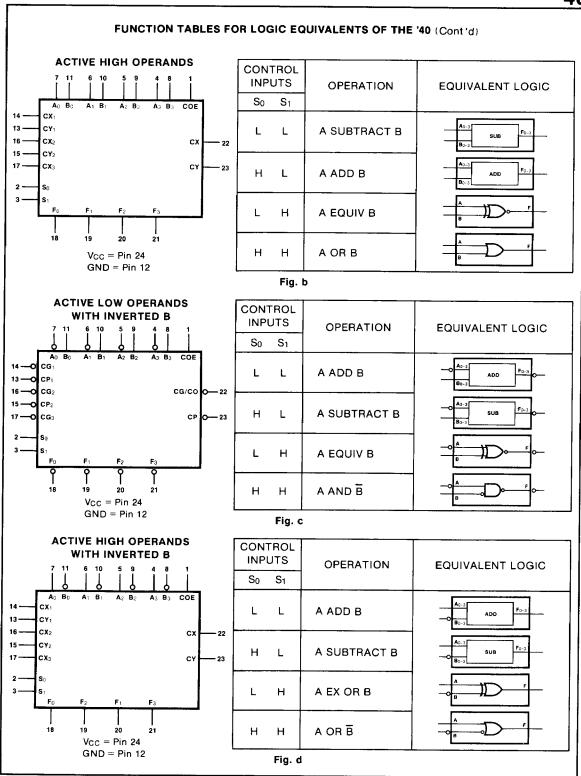

**FUNCTIONAL DESCRIPTION** — The '40 accepts two 4-bit words,  $\overline{A}_0$ ,  $\overline{A}_1$ ,  $\overline{A}_2$ ,  $\overline{A}_3$  and  $\overline{B}_0$ ,  $\overline{B}_1$ ,  $\overline{B}_2$ ,  $\overline{B}_3$ , and produces a 4-bit output,  $\overline{F}_0$ ,  $\overline{F}_1$ ,  $\overline{F}_2$ ,  $\overline{F}_3$ . The output function is determined by the states on the control lines  $S_0$  and  $S_1$ . The inputs and outputs of the '40 may be considered to be active LOW or active HIGH. Logic equivalents for four representations of the '40 are shown in Figure a, b, c, and d.

The add and subtract operations are performed on the entire word, with carries or borrows propagated between bits of different weight. The arithmetic may be performed in 1's complement, 2's complement, or sign-magnitude notation. In the logic modes, carries are inhibited and the device acts like four gates as shown.

To achieve high speed operation, the '40 is designed to be used in a carry lookahead system. Full carry lookahead is used inside the device to propagate carries between bits. Carry lookahead functions over the 4-bit block are available as outputs. These outputs are labeled  $\overline{\text{CO/CG}}$  (Carry Out/Carry Generate) and  $\overline{\text{CP}}$  (Carry Propagate) on the logic symbol. The carry in to the device is formed from a set of Carry Generate and Carry Propagate inputs (equation 1) so that three '40's can be interconnected without any additional gates to form a 12-bit full carry lookahead ALU with a carry in. The pin labeled COE (Carry Out Enable) controls the  $\overline{\text{CO/CG}}$  output according to equation 2. When  $\overline{\text{COE}}$  is HIGH,  $\overline{\text{CO/CG}}$  becomes a Carry Out which can be used to ripple carries between blocks of 12 bits. The  $\overline{\text{CG}}$ 1 input can be used for a ripple carry input, since this signal is sufficient to produce a carry in.

#### EQUATION:

- (1)  $(\overline{CG_1}) + (\overline{CP_1}) (\overline{CG_2}) + (\overline{CP_1}) (\overline{CP_2}) (\overline{CG_3}) = C_{in} (internal)$

- (2)  $\overline{CO/CG} = (\overline{CG}) + (\overline{CP}) (C_{in}) (COE)$

#### FUNCTION TABLES FOR LOGIC EQUIVALENTS OF THE '40

Note that when the input operands are defined as active HIGH, the carry lookahead inputs and outputs are not formally carry generate and carry propagate. Consequently, these pins have been relabled CX and CY in the active HIGH cases. However, the signals are connected in the same manner as  $\overline{CG}$  and  $\overline{CP}$ .

## DC CHARCTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

| SYMBOL | PARAMETER            |    | 93XX |     | UNITS  | CONDITIONS            |

|--------|----------------------|----|------|-----|--------|-----------------------|

|        |                      |    | Min  | Max | 0.1110 | CONDITIONS            |

| loc    | Power Supply Current | XM |      | 135 | mA     | V <sub>CC</sub> = Max |

|        |                      | xc |      | 146 |        |                       |

# AC CHARACTERISTICS: $V_{CC} = +5.0 \text{ V}$ , $T_A = +25^{\circ}\text{C}$ (See Section 3 for waveforms and load configurations)

|              |                                                                                | 93XX<br>C <sub>L</sub> = 15 pF |          | UNITS | CONDITIONS                                                                                                                                                                                                                        |

|--------------|--------------------------------------------------------------------------------|--------------------------------|----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYMBOL       | PARAMETER                                                                      |                                |          |       |                                                                                                                                                                                                                                   |

|              |                                                                                | Min                            | Max      |       |                                                                                                                                                                                                                                   |

| tpLH<br>tpHL | Propagation Delay Add Mode, $\overline{B}_0$ to $\overline{F}_3$               |                                | 30<br>30 | ns    | $S_0$ , $\overline{CG_1}$ , $\overline{CP}$ , $\overline{B_1}$ , $\overline{B_2} = 4.5 \text{ V}$<br>$S_1$ , $\overline{A_0}$ - $\overline{A_3}$ , $\overline{B_3} = \text{Gnd}$<br>Figs. 3-1, 3-5                                |

| tplH<br>tpHL | Propagation Delay for Subtract Mode, $\overline{B}_0$ to $\overline{F}_3$      |                                | 37<br>32 | ns    | $\overline{CG}_{1}$ , $\overline{CP}_{1}$ , $\overline{B}_{3} = 4.5 \text{ V}$ ; $S_{0}$ , $S_{1}$ , $\overline{A}_{0}$ - $\overline{A}_{3}$ , $\overline{B}_{1}$ , $\overline{B}_{2} = Gnd$ Figs. 3-1, 3-4                       |

| tpLH<br>tpHL | Propagation Delay for Add Mode, $\overline{B}_0$ to $\overline{CO/CG}$         |                                | 20<br>20 | ns    | $S_0$ , $\overline{CG_1}$ , $\overline{CP_1}$ ,<br>$\overline{B}_1 - \overline{B}_3 = 4.5 \text{ V}$ ; $S_1$ , $COE$ ,<br>$\overline{A_0} - \overline{A_1} = Gnd$<br>Figs. 3-1, 3-5                                               |

| tplH<br>tpHL | Propagation Delay for Subtract Mode, Bo to CO/CG                               |                                | 25<br>22 | ns    | $\overline{CG_1}$ , $\overline{CP} = 4.5 \text{ V}$ ; $S_0$ , $S_1$ , $COE$ , $A_0 - \overline{A_3}$ , $\overline{B_1} - \overline{B_3} = Gnd$ Figs. 3-1, 3-4                                                                     |

| tplH<br>tpHL | Propagation Delay for Either Mode, CG <sub>3</sub> to CO/CG                    |                                | 19<br>19 | ns    | $S_0$ , $\overline{CG_1}$ , $\overline{CG_2}$ , $\overline{COE}$ ,<br>$\overline{A_0}$ - $\overline{A_3}$ = 4.5 V; $S_1$ ,<br>$\overline{B_0}$ - $\overline{B_3}$ $\overline{CP_1}$ , $\overline{CP_2}$ = Gnd<br>Figs. 3-1, 3-5   |

| tplH<br>tpHL | Propagation <u>Delay for</u><br>Either Mode, CG <sub>3</sub> to F <sub>3</sub> |                                | 31<br>29 | ns    | $S_0$ , $\overline{CG_1}$ , $\overline{CG_2}$ , $\overline{B_3}$ ,<br>$\overline{A_0}$ - $\overline{A_3}$ = 4.5 V; $S_1$ ,<br>$\overline{B_0}$ - $\overline{B_2}$ , $\overline{CP_1}$ , $\overline{CP_2}$ = Gnd<br>Figs. 3-1, 3-5 |