### **Data Sheet**

# Wide Bandwidth, Low Noise, Triaxial Vibration Sensor

# ADcmXL3021

### FEATURES

Triaxial, digital output MEMS vibration sensing module ±50 *g* measurement range

Ultralow output noise density, 26 µg/√Hz (MTC mode) Wide bandwidth: dc to 10 kHz within 3 dB flatness (RTS mode) Embedded fast data sampling: 220 kSPS per axis

6 digital FIR filters, 32 taps (coefficients), default options: High-pass filter cutoff frequencies: 1 kHz, 5 kHz, 10 kHz Low-pass filter cutoff frequencies: 1 kHz, 5 kHz, 10 kHz User configurable digital filter option (32 coefficients) Spectral analysis through internal FFT

Extended record length: 2048 bins per axis with user configurable bin sizes from 0.42 Hz to 53.7 Hz Manual or timer-based (automatic) triggering Windowing options: rectangular, Hanning, flat top FFT record averaging, configurable up to 255 records Spectral defined alarm monitoring, 6 alarms per axis

- Time domain capture with statistical metrics Extended record length: 4096 samples per axis Mean, standard deviation, peak, crest factor, skewness, and kurtosis

- Configurable alarm monitoring

- **Real-time data streaming**

- 220 kSPS on each axis by default

- User programmable sample rates

- Burst mode communication with CRC-16 error checking

- Storage: 10 data records for each axis

- On demand self test with status flags

- Sleep mode with external and timer driven wakeup Digital temperature and power supply measurements

- Digital temperature and power sup

- SPI-compatible serial interface

- Identification registers: factory preprogrammed serial number, device ID, user programmable ID

- Single-supply operation: 3.0 V to 3.6 V Operating temperature range: -40°C to +105°C Automatic shutdown at 125°C (junction temperature) 23.7 mm × 27.0 mm × 12.4 mm aluminum package 36 mm flexible, 14-pin connector interface

Mass: 13 g

### **APPLICATIONS**

Vibration analysis CBM systems Machine health Instrumentation and diagnostics Safety shutoff sensing

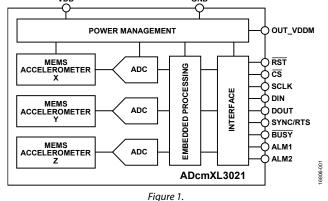

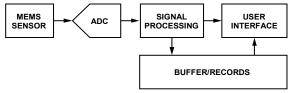

### FUNCTIONAL BLOCK DIAGRAM

### **GENERAL DESCRIPTION**

The ADcmXL3021 is a complete vibration sensing system that combines high performance vibration sensing (using microelectromechanical systems (MEMS) accelerometers) with a variety of signal processing functions to simplify the development of smart sensor nodes in condition-based monitoring (CBM) systems. The typical ultralow noise density (26  $\mu g/\sqrt{Hz}$ ) in the MEMS accelerometers supports excellent resolution. The wide bandwidth (dc to 10 kHz within 3 dB flatness) enables tracking of key vibration signatures on many machine platforms.

The signal processing includes high speed data sampling (220 kSPS), 4096 time sample record lengths, filtering, windowing, fast Fourier transform (FFT), user configurable spectral or time statistic alarms, and error flags. The serial peripheral interface (SPI) provides access to a register structure that contains the vibration data and a wide range of user configurable functions.

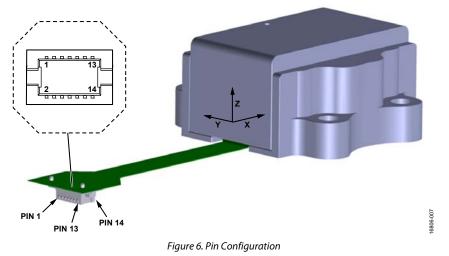

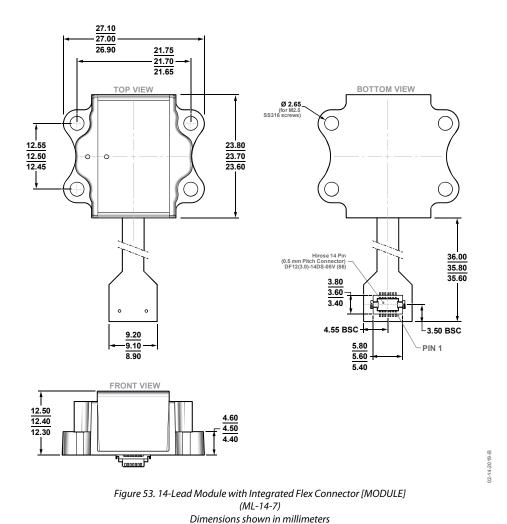

The ADcmXL3021 is available in a 23.7 mm  $\times$  27.0 mm  $\times$  12.4 mm aluminum package with four mounting flanges to support installation with standard machine screws. This package provides consistent mechanical coupling to the core sensors over a broad frequency range. The electrical interface is through a 14-pin connector on a 36 mm flexible cable, which enables a wide range of location and orientation options for system mating connectors.

The ADcmXL3021 requires only a single, 3.3 V power supply and supports an operating temperature range of  $-40^{\circ}$ C to  $+105^{\circ}$ C.

#### Rev. A

#### **Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change withhout notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2019–2021 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

## TABLE OF CONTENTS

| Features 1                                  |

|---------------------------------------------|

| Applications1                               |

| Functional Block Diagram 1                  |

| General Description                         |

| Revision History                            |

| Specifications                              |

| Timing Specifications                       |

| Absolute Maximum Ratings7                   |

| Thermal Resistance                          |

| ESD Caution7                                |

| Pin Configuration and Function Descriptions |

| Typical Performance Characteristics         |

| Theory of Operation14                       |

| Core Sensors14                              |

| Signal Processsing14                        |

| Modes of Operation15                        |

| Data Recording Options16                    |

| User Interface                              |

| Basic Operation                             |

| Device Configuration                        |

| Dual Memory Structure                       |

| Power-Up Sequence                           |

| Trigger                                     |

| Sample Rate                                 |

| Datapath Processing                         |

| Spectral Alarms                             |

| Mechanical Mounting Recommendations25       |

| User Register Memory Map 26                 |

| User Register Details                       |

| PAGE_ID (Page Number)                       |

| TEMP_OUT (Internal Temperature)             |

| SUPPLY_OUT (Power Supply Voltage)           |

| FFT_AVG1, Spectral Averaging                |

| FFT_AVG2, Spectral Averaging                |

| BUF_PNTR, Buffer Pointer                    |

| REC_PNTR, Record Pointer                    |

| X_BUF, Buffer Access Register, X-Axis       |

| Y_BUF, Buffer Access Register, Y-Axis       |

| Z_BUF/RSS_BUF, Buffer Access Register, Z-Axis           |

|---------------------------------------------------------|

| X_ANULL, X-AXIS Bias Calibration Register               |

| Y_ANULL, Y-AXIS Bias Calibration Register               |

| Z_ANULL, Z-AXIS Bias Calibration Register               |

| REC_CTRL, Recording Control                             |

| RT_CTRL, Real TIme Streaming Control                    |

| REC_PRD, Record Period                                  |

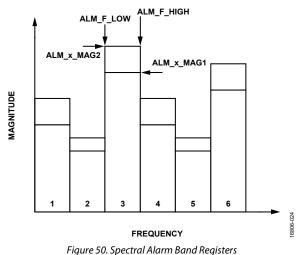

| ALM_F_LOW, Alarm Frequency Band                         |

| ALM_F_HIGH, Alarm Frequency Band                        |

| ALM_X_MAG1, Alarm Level 1 X-Axis                        |

| ALM_Y_MAG1, Alarm Level 1 Y-Axis                        |

| ALM_Z_MAG1, Alarm Level 1 Z-Axis                        |

| ALM_X_MAG2, Alarm Level 2 X-Axis                        |

| ALM_Y_MAG2, Alarm Level 2 Y-Axis                        |

| ALM_Z_MAG2, Alarm Level 2 Z-Axis                        |

| ALM_PNTR, Alarm Pointer                                 |

| ALM_S_MAG Alarm Level 40                                |

| ALM_CTRL, Alarm Conrol                                  |

| FILT_CTRL, Filter Control                               |

| AVG_CNT, Decimation Control                             |

| DIAG_STAT, Status, and Error Flags                      |

| GLOB_CMD, Global Commands                               |

| ALM_X_STAT, Alarm Status X-Axis                         |

| ALM_Y_STAT, Alarm Status Y-Axis                         |

| ALM_Z_STAT, Alarm Status Z-axis                         |

| ALM_X_PEAK, Alarm Peak Level X-Axis                     |

| ALM_Y_PEAK, Alarm Peak LeveL Y-AXIS                     |

| ALM_Z_PEAK, Alarm Peak Level Z-AXIS                     |

| TIME_STAMP_L and TIME_STAMP_H, Data Record<br>Timestamp |

| DAY_REV, Day and Revision                               |

| YEAR_MON, Year and Month                                |

| PROD_ID, Product Identification                         |

| SERIAL NUM, Serial Number                               |

| USER_SCRATCH                                            |

| REC_FLASH_CNT, Record Flash Endurance                   |

| MISC_CTRL, Miscellaneous Control                        |

| REC_INFO1, Record Information                           |

|                                                         |

## **Data Sheet**

| Record Information, REC_INFO2       | 45 |

|-------------------------------------|----|

| REC_CNTR, Record Counter            | 45 |

| ALM_X_FREQ, Severe Alarm Frequency  | 45 |

| ALM_Y_FREQ, Severe Alarm Frequency  | 45 |

| ALM_Z_FREQ, Severe Alarm Frequency  | 46 |

| STAT_PNTR, Statistic Result Pointer | 46 |

| X_STAT, Statistic Result X-Axis     | 46 |

| Y_STAT, Statistic Result Y-Axis     | 47 |

| Z_STAT, Statistic Result Z-Axis     | 47 |

|                                     |    |

| REVISION HISTORY                                            |

|-------------------------------------------------------------|

| 3/2021—Rev. 0 to Rev. A                                     |

| Changes to Features Section1                                |

| Changed Error Parameter to Error Over Temperature           |

| Parameter, Table 1                                          |

| Changes to Table 25                                         |

| Changes to Figure 5 Caption                                 |

| Deleted Figure 19; Renumbered Sequentially11                |

| Changes to Figure 1911                                      |

| Changes to MTC Data Format Section17                        |

| Changes to Table 9 and RTS Data Format Section              |

| Delete Table 10; Renumbered Sequentially                    |

| Changes to Table 20                                         |

| Changes to Table 21                                         |

| Changes to REC_PNTR, Record Pointer Section and Table 40 34 |

| Changes to X_BUF, Buffer Access Register, X-Axis Section,   |

| Table 44, and Table 4635                                    |

| Deleted Table 44                                            |

| Changes to Real-Time Burst Mode Timeout Enabled Section.37  |

| Added RT_CTRL, Real-Time Streaming Control Section,         |

| Table 56, and Table 57                                      |

|                                                             |

# ADcmXL3021

| FUND_FREQ, Fundamental Frequency    | .47 |

|-------------------------------------|-----|

| FLASH_CNT_l, Flash Memory Endurance | .47 |

| FLASH_CNT_U, Flash Memory Endurance | .48 |

| FIR Filter Registers                | .48 |

| Applications Information            | .49 |

| Mechanical Interface                | .49 |

| Outline Dimensions                  | .50 |

| Ordering Guide                      | .50 |

| Changes to Table 77 and Table 7940                       |

|----------------------------------------------------------|

| Deleted DIO_CTRL, Digital Input/Output Line Control      |

| Section, Table 83, and Table 8440                        |

| Changes to Table 84                                      |

| Changes to Table 88, Table 90, and Table 9242            |

| Changes to Table 94, Table 96, and Table 10243           |

| Changes to Table 104, Table 106, Table 108 to Table 112, |

| Table 114, and Table 11844                               |

| Changed DATE_REV, Day and Revision Section to DAY_REV,   |

| Day and Revision Section44                               |

| Added USER_SCRATCH Section, Table 116, and Table 11744   |

| Changes to Table 120, Table 122, Table 124, Table 126,   |

| Table 128, and Table 13045                               |

| Changes to Table 132, Table 134, and Table 13646         |

| Changes to Table 141, Table 143, and Table 14747         |

| Changes to Table 148 and FIR Filter Design Guidelines    |

3/2019—Revision 0: Initial Version

## **SPECIFICATIONS**

$T_A = 25^{\circ}$ C, VDD = 3.3 V, unless otherwise noted.

### Table 1.

| Parameter                               | Test Conditions/Comments                                                        | Min    | Тур    | Мах   | Unit            |

|-----------------------------------------|---------------------------------------------------------------------------------|--------|--------|-------|-----------------|

| ACCELEROMETERS                          |                                                                                 |        |        |       |                 |

| Measurement Range <sup>1</sup>          |                                                                                 |        | ±50    |       | g               |

| Sensitivity                             |                                                                                 |        |        |       |                 |

| FFT                                     |                                                                                 |        | 0.9535 |       | mg/LSB          |

| Time Domain                             |                                                                                 |        | 1.907  |       | mg/LSB          |

| Error Over Temperature                  |                                                                                 |        | ±5     |       | %               |

| Nonlinearity                            | Best fit, straight line, full scale (FS) = $\pm 50 g$                           |        | ±0.2   | ±1.25 | %               |

| Cross Axis Sensitivity                  |                                                                                 |        | 2      |       | %               |

| Alignment Error                         | With respect to package                                                         |        | 2      |       | Degrees         |

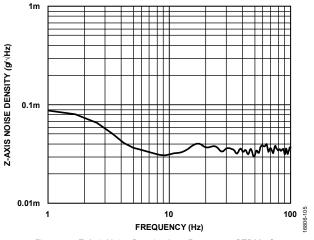

| Offset Error over Temperature           | $T_{A} = -40^{\circ}C \text{ to } +105^{\circ}C$                                |        | ±5     |       | g               |

| Offset Temperature Coefficient          | $T_A = -40^{\circ}C \text{ to } +105^{\circ}C$                                  |        | 34     |       | mg∕°C           |

| Output Noise                            | Real-time streaming (RTS) mode                                                  |        | 3.2    |       | mg rms          |

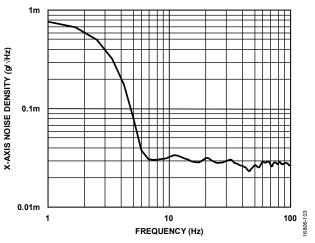

| Output Noise Density                    | 100 Hz to 10 kHz, all axes, AVG_CNT = 0, MTC mode                               |        | 26     |       | µ <i>g/√</i> Hz |

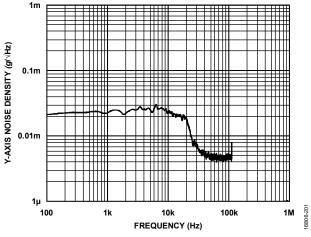

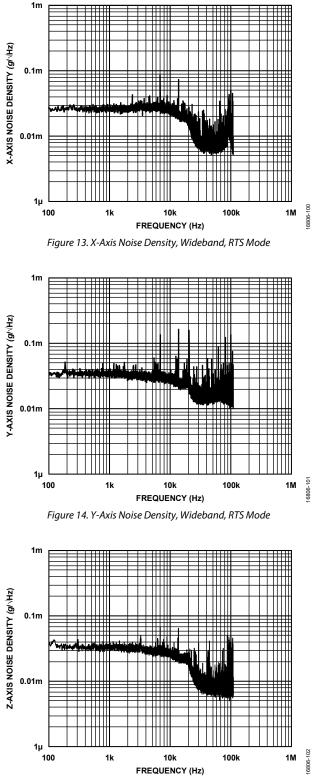

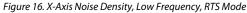

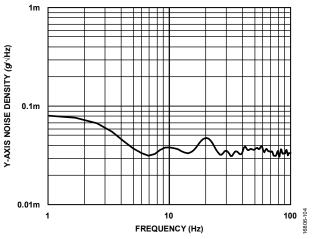

| Output Noise Density                    | 1 Hz to 10 kHz, all axes, no filtering, RTS mode                                |        | 32     |       | µ <i>g/√</i> Hz |

| 3 dB Bandwidth                          | All axes                                                                        | 10,000 |        |       | Hz              |

| Sensor Resonant Frequency               |                                                                                 |        | 21     |       | kHz             |

| CONVERSION RATE                         |                                                                                 |        |        | 220   | kSPS            |

| Clock Accuracy                          |                                                                                 |        | 3      |       | %               |

| FUNCTIONAL TIMING                       |                                                                                 |        |        |       |                 |

| Factory Reset Time Recovery             |                                                                                 |        | 130    |       | ms              |

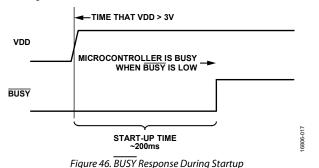

| Start Up Time                           | Time from supply voltage reaching 3.0 V from power-down until ready for command |        | 220    |       | ms              |

| Self Test Time                          |                                                                                 |        | 93     |       | ms              |

| LOGIC INPUTS                            |                                                                                 |        |        |       |                 |

| Input High Voltage, V <sub>INH</sub>    |                                                                                 | 2.5    |        |       | V               |

| Input Low Voltage, VINL                 |                                                                                 |        |        | 0.45  | V               |

| Logic 1 Input Current, I <sub>INH</sub> | $V_{IH} = 3.3 V$                                                                |        | 0.01   | 0.2   | μΑ              |

| Logic 0 Input Current, I <sub>INL</sub> | $V_{IL} = 0 V$                                                                  |        |        |       |                 |

| All Except RST                          |                                                                                 |        |        | 100   | μΑ              |

| RST                                     |                                                                                 |        | 1      |       | mA              |

| Input Capacitance, C <sub>IN</sub>      |                                                                                 |        | 10     |       | рF              |

| DIGITAL OUTPUTS                         |                                                                                 |        |        |       |                 |

| Output Voltage                          |                                                                                 |        |        |       |                 |

| High, V <sub>он</sub>                   | $I_{OH} = -1 \text{ mA}$                                                        | 1.4    |        |       | V               |

| Low, V <sub>OL</sub>                    | $I_{OL} = 1 \text{ mA}$                                                         |        |        | 0.4   | V               |

| Output Current                          |                                                                                 |        |        |       |                 |

| н <b>igh, I</b> он                      | $I_{OH} = -1 \text{ mA}$                                                        |        |        | 2     | mA              |

| Low, IoL                                | $I_{OL} = 1 \text{ mA}$                                                         |        |        | 2     | mA              |

| FLASH MEMORY                            |                                                                                 | 1      |        |       |                 |

| Endurance <sup>2</sup>                  |                                                                                 | 10,000 |        |       | Cycles          |

| Data Retention <sup>3</sup>             | $T_1 = 85^{\circ}C$ , see Figure 52                                             |        | 10     |       | Years           |

| THERMAL SHUTDOWN                        |                                                                                 |        |        |       | -               |

| Thermal Shutdown Threshold              | T <sub>J</sub> rising                                                           |        | 125    |       | °C              |

| Thermal Shutdown Hysteresis             |                                                                                 |        | 15     |       | °C              |

| Parameter Test Conditions/Comments                                           |                                                      | Min | Тур  | Max | Unit |

|------------------------------------------------------------------------------|------------------------------------------------------|-----|------|-----|------|

| OUT_VDDM MONITOR OUTPUT                                                      | UT Logic output; logic high indicates good condition |     |      |     |      |

| Output ResistanceLogic low when internal temperature exceed<br>allowed range |                                                      | 90  | 100  | 110 | kΩ   |

| POWER SUPPLY VOLTAGE Operating voltage range, VDD                            |                                                      | 3.0 | 3.3  | 3.6 | V    |

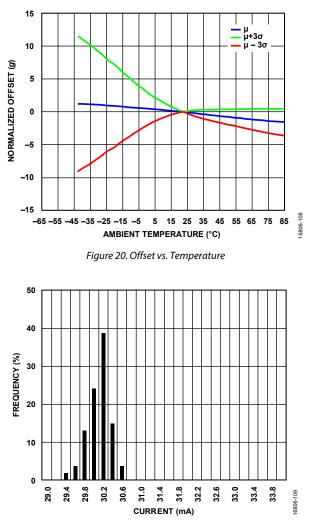

| Power Supply Current                                                         | Operating mode, VDD = 3.0 V                          |     | 30.2 |     | mA   |

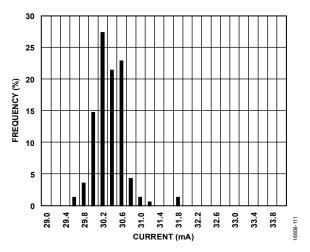

|                                                                              | Operating mode, VDD = 3.3 V                          |     | 30.6 |     | mA   |

|                                                                              | Operating mode, VDD = 3.6 V                          |     | 31.6 |     | mA   |

|                                                                              | Sleep mode, VDD = 3.0 V                              |     | 1    |     | mA   |

|                                                                              | Sleep mode, VDD = 3.3 V                              |     | 1.5  |     | mA   |

|                                                                              | Sleep mode, VDD = 3.6 V                              |     | 2.3  |     | mA   |

<sup>1</sup> The maximum range depends on the frequency of vibration.

<sup>2</sup> Endurance is qualified as per JEDEC Standard 22, Method A117 and measured at -40°C, +25°C, +85°C, and +125°C.

<sup>3</sup> Retention lifetime equivalent at junction temperature (T<sub>i</sub>) = 85°C as per JEDEC Standard 22, Method A117. Retention lifetime depends on junction temperature.

### TIMING SPECIFICATIONS

$T_c = 25^{\circ}C$ , VDD = 3.3 V, unless otherwise noted.

Table 2.

|                   |                                                                                                     | No               | ormal Mo | de               |                   | <b>RTS Mode</b>  |                  |      |

|-------------------|-----------------------------------------------------------------------------------------------------|------------------|----------|------------------|-------------------|------------------|------------------|------|

| Parameter         | Description                                                                                         | Min <sup>1</sup> | Тур      | Max <sup>1</sup> | Min               | Тур              | Max <sup>1</sup> | Unit |

| fsclk             | SCLK frequency                                                                                      | 0.01             |          | 14               | 12.5 <sup>2</sup> |                  | 14               | MHz  |

| tstall            | Stall period between data bytes                                                                     | 16               |          |                  |                   | N/A <sup>3</sup> |                  | μs   |

| tcls              | SCLK low period                                                                                     | 35.7             |          |                  | 35.7              |                  |                  | ns   |

| t <sub>CHS</sub>  | SCLK high period                                                                                    | 35.7             |          |                  | 35.7              |                  |                  | ns   |

| t <sub>cs</sub>   | CS to SCLK edge                                                                                     | 35.7             |          |                  | 35.7              |                  |                  | ns   |

| t <sub>DAV</sub>  | DOUT valid after SCLK edge                                                                          |                  |          | 20               |                   |                  | 20               | ns   |

| t <sub>DSU</sub>  | DIN setup time before SCLK rising edge                                                              | 6                |          |                  | 6                 |                  |                  | ns   |

| <b>t</b> DHD      | DIN hold time after SCLK rising edge                                                                | 8                |          |                  | 8                 |                  |                  | ns   |

| t <sub>DSOE</sub> | CS assertion to DOUT active                                                                         |                  |          | 20               | 0                 |                  | 20               | ns   |

| t <sub>HD</sub>   | SCLK edge to DOUT invalid                                                                           |                  |          | 20               |                   |                  | 20               | ns   |

| t <sub>SFS</sub>  | Last SCLK edge to $\overline{CS}$ deassertion                                                       | 35.7             |          |                  | 35.7              |                  |                  | ns   |

| trts_busy         | RTS mode only, data out valid burst<br>readout period end before BUSY rising<br>edge for next burst |                  | N/A      |                  | 5                 |                  |                  | μs   |

<sup>1</sup> Guaranteed by design and characterization, but not tested in production.

<sup>2</sup> Assuming a sample rate of 220 kSPS. If in RTS mode the sample rate is reduced by using the RT\_CTRL register, f<sub>SCLK</sub> can be lower than 12.5 MHz. The minimum f<sub>SCLK</sub> is bound by the period of one RTS data frame read. If f<sub>SCLK</sub> is lowered further, and the entire RTS data frames are not read within a cycle, CRC errors may occur because SPI read out is not keeping up with the real-time data generation.

<sup>3</sup> N/A means not applicable. When using RTS mode, the stall period is not applicable.

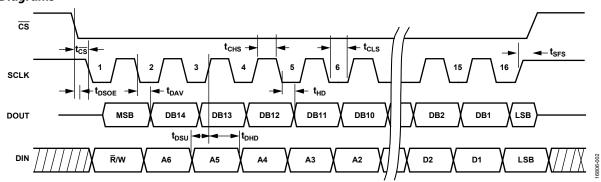

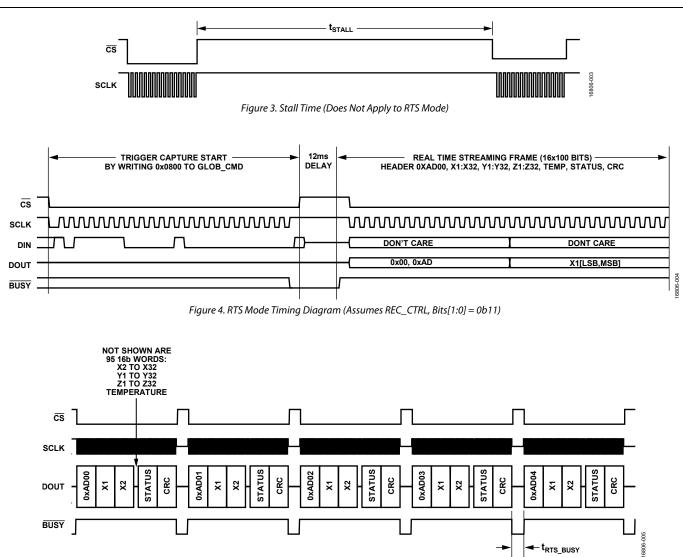

### **Timing Diagrams**

Figure 2. SPI Timing and Sequence

Figure 5. RTS Read Function Sequence Diagram, First Five Segments

### ABSOLUTE MAXIMUM RATINGS

#### Table 3.

| Tuble 5.                      |                  |

|-------------------------------|------------------|

| Parameter                     | Rating           |

| Acceleration                  |                  |

| Any Axis, Unpowered           | 2000 g           |

| Any Axis, Powered             | 2000 g           |

| VDD to GND                    | –0.3 V to +3.6 V |

| Digital Input Voltage to GND  | –0.3 V to +3.6 V |

| Digital Output Voltage to GND | –0.3 V to +3.6 V |

| Temperature, T <sub>A</sub>   |                  |

| Operating Range               | -40°C to +105°C  |

| Storage Range                 | -65°C to +150°C  |

|                               |                  |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Pay careful attention to PCB thermal design.

$\theta_{JA}$  is the natural convection junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.

$\theta_{\text{JC}}$  is the junction to case thermal resistance.

The ADcmXL3021 is a multichip module, which includes many active components. The values in Table 4 identify the thermal response of the hottest component inside of the ADcmXL3021, with respect to the overall power dissipation of the module. This approach enables a simple method for predicting the temperature of the hottest junction, based on either ambient or case temperature.

For example, when  $T_A = 70^{\circ}$ C, under normal operation mode with a typical 34 mA current and 3.3 V supply voltage, the hottest junction temperature in the ADcmXL3021 is 77.3°C.

$T_J = \theta_{JA} \times V_{DD} \times I_{DD} + 70^{\circ}\text{C}$  $T_J = 65.1^{\circ}\text{C/W} \times 3.3 \text{ V} \times 0.034 \text{ A} + 70^{\circ}\text{C}$  $T_J \approx 77.3^{\circ}\text{C}$

where  $I_{DD}$  is the current consumption of the device.

#### Table 4. Thermal Resistance

| Package Type         | θιΑ      | θις      |

|----------------------|----------|----------|

| ML-14-7 <sup>1</sup> | 65.1°C/W | 33.2°C/W |

$^1$  Thermal impedance simulated values come from a case with four machine screws at a size of M2.5  $\times$  0.4 mm (torque = 25 inch-pounds). Secure the ADcmXL3021 to the PCB.

### ESD CAUTION

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

## **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

### Table 5. Pin Function Descriptions

| Pin No. | Mnemonic | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | GND      | Supply | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2       | ALM1     | Output | Digital Output Only, Alarm 1 Output. This pin is configured by the ALM_CTRL register and is not used in real-time streaming mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3       | SYNC/RTS | Input  | Sync Function (SYNC)/RTS Burst Start/Stop (RTS). This pin is an digital input only, and is edge (not level) sensitive. This pin must be enabled in the MISC_CTRL register (Bit 12) before being used as an external trigger. The SYNC pulse width must be at least 50 ns.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|         |          |        | In MTC and MFFT modes, the SYNC pin acts as a manual trigger, this pin initiates a record capture event<br>when a low to high transition is detected, equivalent to SPI Command 0x0800 to the GLOB_CMD<br>register. In RTS and AFFT mode, when the logic level on this pin is high, conversion is active. When the<br>logic level on this pin is low, conversion is stopped after the current data record is completed.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4       | ALM2     | Output | Digital Output Only, Alarm 2 Output. This pin is configured by the ALM_CTRL register and is not used in real-time streaming mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5       | BUSY     | Output | Busy or Data Ready Indicator, Digital Output Only. In RTS mode, this pin is a logical output to indicate that data is ready and available for download. The logical state resets to logic low when data is loading to the output buffers. The pin is set high when data is ready for download. In other capture modes, the busy indicator identifies the state of the module processor and if it is available for external commands. When a command is executing, SPI access is not allowed and the device is in a busy state. After this process completes, whether a command or a record, the SPI is released and the BUSY pin is set to logic high state. Note that there is one exception to SPI port access while in the busy state: a capture can be terminated by writing the unique 16-bit escape code, 0x00E8, to the GLOB_CMD register. |

| 6       | OUT_VDDM | Output | Power Supply Monitor (Digital Output). This pin is logic low when temperature exceeds threshold and automatic shutdown occurs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 7       | RST      | Input  | Hardware Reset, Digital Input Only, Active Low. This pin enters the device in a known state by resetting the microcontroller. This pin also loads the user configurable parameters from flash memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 8       | VDD      | Supply | Power Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 9       | GND      | Supply | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 10      | GND      | Supply | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 11      | DIN      | Input  | SPI, Data Input Line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 12      | DOUT     | Output | SPI, Data Output. DOUT is an output when $\overline{CS}$ is low. When $\overline{CS}$ is high, DOUT is in a three-state, high impedance mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 13      | SCLK     | Input  | SPI, Serial Clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 14      | CS       | Input  | SPI, Chip Select.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

## **TYPICAL PERFORMANCE CHARACTERISTICS**

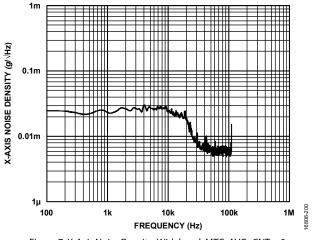

Figure 7. X-Axis Noise Density, Wideband, MTC, AVG\_CNT = 0

Figure 8. Y-Axis Noise Density, Wideband, MTC, AVG\_CNT = 0

Figure 9. Z-Axis Noise Density, Wideband, MTC, AVG\_CNT = 0

Figure 12. Z-Axis Sine Sweep Response, RTS Mode

Figure 15. Z-Axis Noise Density, Wideband, RTS Mode

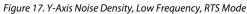

Figure 18. Z-Axis Noise Density, Low Frequency, RTS Mode

### **Data Sheet**

#### 10 9 8 7 6 5 4 3 2 1 0 -1 2 3 4 -5 6 -7 8 -9 -10 SENSITIVITY ERROR (% of Full-Scale) μ 3806-107 -50 -40 -30 -20 -10 70 80 90 100 0 10 20 30 40 50 60 AMBIENT TEMPERATURE (°C)

Figure 19. Sensitivity Error vs. Ambient Temperature, Normalized at 25°C

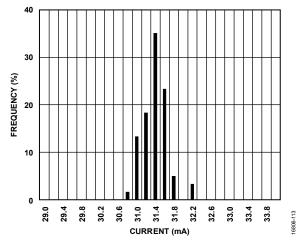

Figure 21. Operating Mode Current Distribution at 3.0 V Supply

Figure 22. Operating Mode Current Distribution at 3.3 V Supply

Figure 23. Operating Mode Current Distribution at 3.6 V Supply

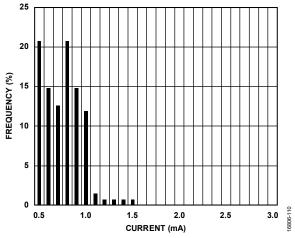

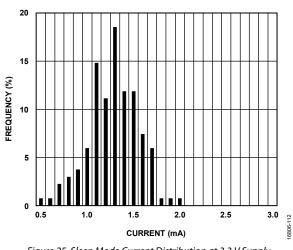

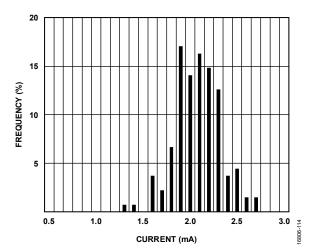

Figure 24. Sleep Mode Current Distribution at 3.0 V Supply

Figure 25. Sleep Mode Current Distribution at 3.3 V Supply

Figure 26. Sleep Mode Current Distribution at 3.6 V Supply

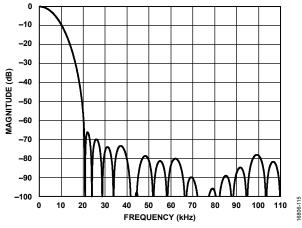

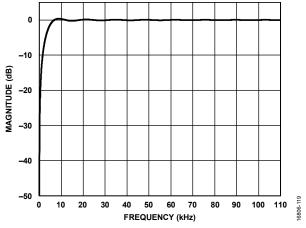

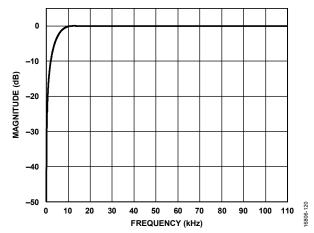

Figure 27. Digital Filter Frequency Response of the 1 kHz Low-Pass Filter

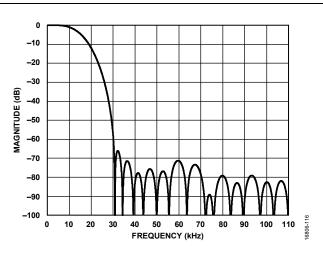

Figure 28. Digital Filter Frequency Response of the 5 kHz Low-Pass Filter

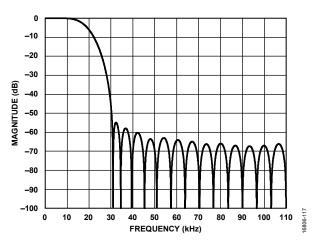

Figure 29. Digital Filter Frequency Response of the 10 kHz Low-Pass Filter

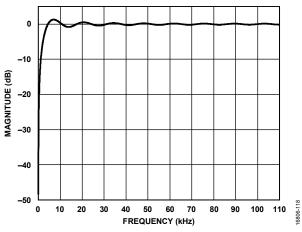

Figure 30. Digital Filter Frequency Response of the 1 kHz High-Pass Filter

## Data Sheet

Figure 31. Digital Filter Frequency Response of the 5 kHz High-Pass Filter

Figure 32. Digital Filter Frequency Response of the 10 kHz High-Pass Filter

### THEORY OF OPERATION

The ADcmXL3021 is a triaxial, vibration monitoring subsystem that includes wide bandwidth, low noise MEMS accelerometers, an analog-to-digital converter (ADC), high performance signal processing, data buffers, record storage, and a user interface that easily interfaces with most embedded processors. See Figure 33 for a basic signal chain. The subsystem is housed in an aluminum module that is mounted using four screws (accepts screw size M2.5) and is designed to be mechanically stable beyond 40 kHz. The combination of this mechanical mounting and oversampling ensures that aliasing artifacts are minimized.

Figure 33. Basic Signal Chain

3806-009

The ADcmXL3021 has a high operating input range of  $\pm 50 g$  and is suitable for vibration measurements in high bandwidth applications, such as vibration analysis systems that monitor and diagnose machine or system health. User configurable internal processing supports both time domain and frequency domain calculations.

The low noise and high frequency bandwidth enable the measurement of both repetitive vibration patterns and single shock events caused by small moving parts, such as internal bearings. The high *g* range provides the dynamic range to be used in high vibration environments, such as heating, ventilation, and air conditioning systems (HVAC), and heavy machine equipment. To achieve best performance, be aware of system noise, mounting, and signal conditioning for the particular application.

Proper mounting is required to ensure full mechanical transfer of vibration to accurately measure the desired vibration. A common technique for high frequency mechanical coupling is to use a combination of a threaded screw mount system and adhesive where possible. For lower frequencies (below the full capable bandwidth of the sensor), it is possible to use magnetic or adhesive mounting. Proper mounting techniques ensure accurate and repeatable results that are not influenced by measurement system mechanical resonances and/or damping at the desired frequencies, and represents an efficient and proper mechanical transfer to the system being monitored.

### **CORE SENSORS**

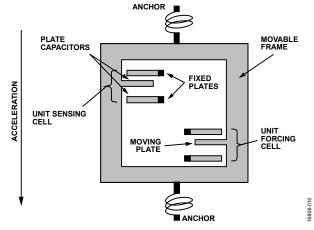

The ADcmXL3021 uses three ADXL1002 MEMS accelerometers, with sensing axes configured to be mutually orthogonal to each other. Figure 34 is a simple mechanical diagram that shows how MEMS accelerometers translate linear acceleration to representative output signals.

The moving component of the sensor is a polysilicon surfacemicromachined structure built on top of a silicon wafer. Polysilicon springs suspend the structure over the surface of the wafer and provide a resistance against acceleration forces.

Deflection of the structure is measured using differential capacitors that consist of independent fixed plates and plates attached to the moving mass. Acceleration deflects the structure and unbalances the differential capacitor, resulting in a sensor output with an amplitude proportional to acceleration. Phase sensitive demodulation determines the magnitude and polarity of the acceleration.

Figure 34. MEMS Sensor Diagram

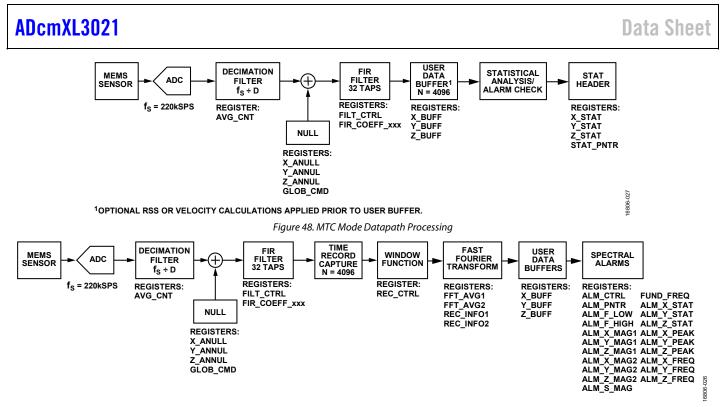

### SIGNAL PROCESSSING

The signal chain of the ADcmXL3021 includes wideband accelerometers to monitor three axes, a low-pass analog filter with a 13.5 kHz cutoff frequency, an oversampling ADC (sampling at 220 kSPS per axis), a microcontroller, and discrete components to provide a flexible vibration monitor subsystem that supports multiple processed output modes. There are four modes of operation. One mode of operation is the full rate real-time streaming (RTS) output. The three other modes include system level signal processing: manual FFT mode (MFFT), automatic FFT mode (AFFT), and manual time capture (MTC) mode

MTC mode supports 4096 consecutive time domain samples to which averaging, finite impulse response (FIR), and windowing signal processing can be enabled, along with the calculation of statistics, alarm configuring, and monitoring. In MTC mode, the raw time domain data is made available in register buffers for all three axes for the user to access and externally process.

In both FFT modes, manual fast Fourier transform (MFFT) and AFFT modes support the process of calculating an FFT of the current time domain record.

Finally, a continuous RTS mode bypasses all device digital computations and alarm monitoring, outputting real-time data over the SPI in burst data output format (see Figure 5).

### **MODES OF OPERATION**

The ADcmXL3021 supports four different modes of operation: RTS mode, MTC mode, MFFT mode, and AFFT mode. Users can select the mode of operation by writing the corresponding code to the REC\_CTRL register, Bits[1:0] (see Table 55).

In three of these modes (MFFT, AFFT, and MTC), the ADcmXL3021 captures, analyzes, and stores vibration data in discrete events, known as capture events, and generates a record. Each capture event concludes with storing the data as configured in REC\_CTRL register in the user data buffers, which are accessible through the BUF\_PNTR register (see Table 36).

The two different FFT modes that produce vibration data in spectral terms are MFFT and AFFT. The difference between these two modes is the manner in which data capture and analysis starts. In MFFT mode, users trigger a capture event by an external digital signal or through a software command using the GLOB\_CMD register, Bit 11 (see Table 91). In AFFT mode, an internal timer automatically triggers additional spectral record captures without the need for an external trigger. Up to four different sample rate profiles can be selected for the modes to cycle through. The REC\_PRD register (see Table 59) contains the user configuration settings for the time that elapses between each capture event when operating in the AFFT mode.

### Manual Time Capture (MTC) Mode

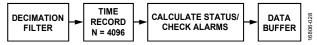

When operating in MTC mode, the ADcmXL3021 captures 4096 consecutive time domain samples. An offset null signal can be calculated and applied to the data using the command register option. Signal processing functions such as low-pass and high-pass FIR filtering and averaging can be applied. After digital processing is complete, the 4096 time domain sample data (per axis) record of vibration data is stored into the user data buffers, using the signal flow diagram shown in Figure 36.

Capturing is triggered by either a SPI write to the GLOB\_CMD register or by an external trigger. The ADcmXL3021 toggles the output  $\overline{\text{BUSY}}$  when the data record is stored and the alarms are checked.

The decimation filter reduces the effective rate of stored data capture in the time record by averaging the sequential samples together and filtering out of band signal and noise. This filter has eight decimation rate settings (1, 2, 4, 8, 16, 32, 64, and 128) and can support up to four different settings. These time data records are time continuous captures with decimation filter acting on real time data from the ADC to produce 4096 samples (to produce the 4096 time domain samples requires 2<sup>N</sup> samples to be processed internally, where N is the average count value, AVG\_CNT). When more than one user configured sample record setting is in use, the ADcmXL3021 applies a single filter for each data record and cycles through all desired options, one for each data capture. Time statistic alarms can be configured for three levels of reporting: normal, critical, and warning. A record mode option allows all enabled time domain statistics to be stored, depending on user preference, and is configured by setting the record mode in Register REC\_CTRL, Bits[3:2] (Register 0x1A, 0x1B) = 0b10.

The output data can be configured to provide the root sum of squares (RSS) of all three axes or convert accelerometer data to equivalent velocity.

Figure 35. Signal Processing Diagram for Manual Time Capture (MTC) Mode

### MFFT Mode

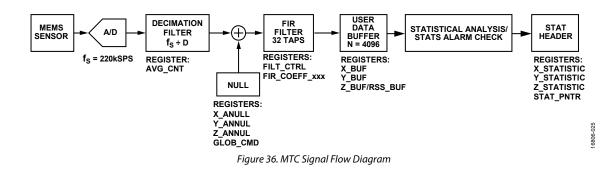

MFFT mode can be used to manually trigger a capture to create a single FFT record with 2048 bins and allows various configuration options. The ADcmXL3021 has configurable high-pass and low-pass filters, decimation filtering, FFT averaging and spectral alarms. The ADcmXL3021 also has options to calculate velocity, apply windowing, and apply offset compensations. MFFT mode is configured by setting the record mode in Register REC\_CTRL, Bits[1:0] (Register 0x1A, 0x1B) = 0b00.

Processing steps collect 4096 consecutive time domain samples and filters the data similar to the MTC case. Additional windowing and FFT averaging can be enabled and configured using the 4096 sample burst captures. The ADcmXL3021 provides three different mathematical filtering options to processes the time record data, prior to performing an FFT, the filter options are rectangular, Hanning, or flat. See the REC\_CTRL register in Table 55 for more information on selecting the window option.

When a capture event is triggered by the user, the event follows the process flow diagram shown in Figure 37. The FIR filter has 32 coefficients and processes at the full internal ADC sample rate of 220 kSPS per axis. Users can select from one of six FIR filter bank options. Three of these filter banks have preset coefficients that provide low-pass responses to support half power bandwidths of 1 kHz, 5 kHz, and 10 kHz, respectively. The other three filter banks have preset coefficients that provide high-pass responses to support half power bandwidths of 1 kHz, 5 kHz, and 10 kHz filter. All six filter banks can be overwritten through user programming and stored to flash memory.

After the FIR filter is applied to the time domain data, if enabled, the data is decimated according to the AVG\_CNT setting until a full 4096 time sample capture fills the data buffer. This decimation produces a time record that is converted to a spectral record and averaged, depending on the FFT\_AVG1 or FFT\_ AVG2 setting, as appropriate (see Figure 49 for the FFT capture datapath and appropriate registers).

### AFFT Mode

AFFT mode is configured by setting the record mode in Register REC\_CTRL, Bits[1:0] (Register 0x1A, 0x1B) = 0b01. AFFT mode supports the same functionality as MFFT mode, except AFFT mode automatically advances and independently controls new capture events. New capture events are triggered periodically and are configured in the register map using REC\_PRD.

To save power for long off time durations, the device can be configured to sleep between auto captures using Bit 7 in the REC\_CTRL register.

### **RTS Mode**

RTS mode is configured by setting the record mode in Register REC\_CTRL, Bits[1:0] (Register 0x1A, 0x1B) = 0b11.

When operating in the RTS mode, the ADcmXL3021 samples each axis at a rate of 220 kSPS and makes this data available through a burst pattern via the SPI.

### DATA RECORDING OPTIONS

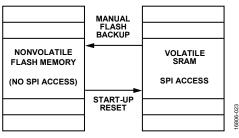

The ADcmXL3021 creates data records in FFT and MTC modes and supports three methods of data storage for each data record: immediate only mode, alarm triggered mode, and all mode. In MTC mode, the time domain statistics are stored and are not the time records.

When immediate only mode is selected, only the most recent capture data record is retained and accessible.

In alarm triggered mode, only data that triggered an alarm is stored. When an alarm event is triggered, the ADcmXL3021 stores the header registers and the FFT data to flash memory. Alarm triggered mode is helpful for continuous operation while minimally impacting the limited endurance of the flash memory. In the case of any alarm event, even on a single axis, all available axes are saved.

In all mode, each data record is stored. The data stored includes FFT header information and FFT data for all available axes. Up to 10 FFT records can be stored and retrieved.

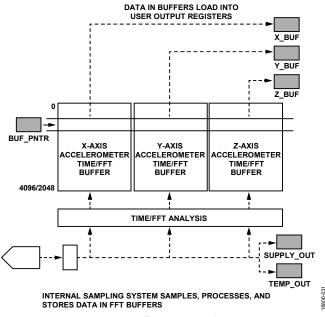

The ADcmXL3021 samples, processes, and stores vibration data from three axes (x, y, and z) to the FFT or MTC data. In MTC mode, the record for each axis contains 4096 samples. In MFFT mode and AFFT mode, each record contains the 2048 bin FFT result for each accelerometer axis. Table 6 describes the registers that provide access to processed sensor data.

Table 6. Output Data Registers

| Register     | Address | Description                       |

|--------------|---------|-----------------------------------|

| TEMP_OUT     | 0x02    | Internal temperature measurement  |

| SUPPLY_OUT   | 0x04    | Internal power supply measurement |

| BUF_PNTR     | 0x0A    | Data buffer index pointer         |

| REC_PNTR     | 0x0C    | FFT record index pointer          |

| X_BUF        | 0x0E    | X-axis accelerometer buffer       |

| Y_BUF        | 0x10    | Y-axis accelerometer buffer       |

| Z_BUF        | 0x12    | Z-axis accelerometer buffer       |

| GLOB_CMD     | 0x3E    | Global command register           |

| TIME_STAMP_L | 0x4C    | Timestamp, lower word             |

| TIME_STAMP_H | 0x4E    | Timestamp, upper word             |

| REC_INFO1    | 0x66    | FFT record header information     |

| REC_INFO2    | 0x68    | FFT record header information     |

### Reading Data from the Data Buffer

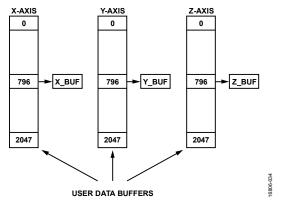

After completing a spectral record and updating each data buffer, the ADcmXL3021 loads the first data sample from each data buffer to the x\_BUF registers (see Table 10, Table 11, and Table 12) and sets the buffer index pointer in the BUF\_PNTR register (see Table 7) to 0x0000. The index pointer determines which data samples load to the x\_BUF registers. For example, writing 0x009F to the BUF\_PNTR register (DIN = 0x8A9F, DIN = 0x8B00) causes the 160th sample in each data buffer location to load to the x\_BUF registers. The index pointer automatically increments with each x\_BUF read command, which causes the next set of capture data to load to each capture buffer register. This enables an efficient method for reading all 4096 time samples or 2048 FFT points in a record, using sequential read commands, without needing to manipulate the BUF\_PNTR register.

Figure 38. Data Buffer Structure and Operation

| Bits    | Description (Default = 0x0000)                       |  |  |

|---------|------------------------------------------------------|--|--|

| [15:12] | Not used                                             |  |  |

| [11:0]  | Data bits; range = 0 to 2047 (FFT), 0 to 4095 (time) |  |  |

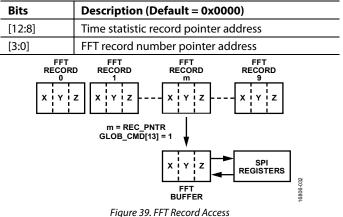

### Accessing FFT Record Data

Up to 10 FFT records can be stored in flash memory. The REC\_PNTR register (see Table 8) and GLOB\_CMD bit (Bit 13, see Figure 39) provide access to the FFT records.

The process when FFT averaging is enabled is as follows:

- 1. Initiate a capture.

- 2. Time domain samples are captured and filtered according to AVG\_CNT setting until 4096 time samples fill the buffer.

- 3. The FFT is calculated from the time samples in the buffer and the record is stored.

- 4. After the number of FFT averages is reached, all FFT records in memory are averaged and stored.

- 5. Alarms are checked, flags are set, and the data record is stored as per configuration

- 6. In either manual or automatic mode, the next sample rate option is set.

- 7. Finally, the  $\overline{BUSY}$  signal is set.

Note that an FFT record is an FFT stored in flash, and an FFT capture is an FFT stored in RAM.

| Table 8. REC | <b>PNTR</b> | (Base Address = | = 0x0C) | , Read/Write |

|--------------|-------------|-----------------|---------|--------------|

|--------------|-------------|-----------------|---------|--------------|

### **MTC Data Format**

In MTC mode the X\_BUF, Y\_BUF, and Z\_BUF registers each contain a single time domain sample for the noted axis. When reading X\_BUF (as well as Y\_BUF and Z\_BUF), BUF\_PNTR automatically advances from 0 to 4095. The time domain data is 16-bit, twos complement acceleration data by default with a resolution of 1 LSB = 1.907 mg. If velocity data is selected by setting REC\_CTRL, Bit 5 = 1, velocity data is stored in the buffer registers instead. Velocity data is calculated by integrating the acceleration data, its resolution and scale factor depend on the sample rate and AVG\_CNT value:

*Velocity* 1 LSB = (2<sup>AVG\_CNT</sup>/*Sample Rate*) × 18.70 mm/s

For instance, if the default sample rate is 220 kSPS and AVG\_CNT = 5, 1 LSB = 2.72  $\mu m/sec.$

Table 10, Table 11, and Table 12 list the bit assignments for the X\_BUF, Y\_BUF, and Z\_BUF registers. The acceleration data format depends on the record type setting in the REC\_CTRL register. Table 42 shows data formatting examples for the 16-bit, twos complement format used in manual time mode.

In MTC mode, time domain statistic can be calculated by enabling Bit 6 in the REC\_CTRL register. The statistics value scales are calculated based on setting of accelerometer or velocity, and if RSS is enabled, all statistics are calculated based on the RSS values. The time domain statistics available are mean, standard deviation, peak, peak-to-peak, crest factor, kurtosis, and skewness.

The scale of all statistics are consistent with the data format selected (for example, 1 LSB = 1.907 mg for acceleration), except the crest factor, kurtosis, and skew, which require fractional numbers.

| (1.907 mg/LSB) LSB Hex Binary         |             |

|---------------------------------------|-------------|

| (1.907 mg/LSB) LSB Hex Binary         |             |

| +62486.7 +32,767 0x7FFF 0111 111      | 1 1111 1111 |

| +12498.5 +6554 0x199A 0001 100        | 1 1001 1010 |

| +3.9 +2 0x0002 0000 000               | 0 0000 0010 |

| +1.9 +1 0x0001 0000 000               | 0 0000 0001 |

| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | 0 0000 0000 |

| -1.9 -1 0xFFFF 1111 111               | 1 1111 1111 |

| -3.8 -2 0xFFFE 1111 111               | 1 1111 1110 |

| -12498.5 -6554 0xE666 1110 011        | 0 0110 0110 |

| -62488.6 -32,768 0x8000 1000 000      | 0 0000 0000 |

If RSS calculation is enabled in MTC mode, the RSS of all three axes is placed in the Z\_BUF registers. X and y time domain data is still available in the respective buffers, but the contents of Z\_BUF are replaced with the RSS values. If RSS is enabled, the x-axis and y-axis alarms still apply to the respective axes, but the z-axis alarms apply to the RSS values.

### Table 10. X\_BUF (Base Address = 0x0E), Read Only

| Bits   | Description (Default = 0x8000)                          |  |  |

|--------|---------------------------------------------------------|--|--|

| [15:0] | X-axis acceleration data buffer register. Format = twos |  |  |

|        | complement (time), unsigned integer (FFT).              |  |  |

### Table 11. Y\_BUF (Base Address = 0x10), Read Only

| Bits    | Description (Default = 0x8000)                                                                     |

|---------|----------------------------------------------------------------------------------------------------|

| [15:0]  | Y-axis acceleration data buffer register. Format = twos complement (time), unsigned integer (FFT). |

| Tabla 1 | 2.7 PUE (Pass Address - 0x12) Pasd Only                                                            |

| Table I | $Z_BUF$ (Base Address = 0x12), Read Or | пy |

|---------|----------------------------------------|----|

|         |                                        |    |

| Bits   | Description (Default = 0x8000)                       |  |  |

|--------|------------------------------------------------------|--|--|

| [15:0] | Z-acceleration or RSS data buffer register. Format = |  |  |

|        | twos complement (time), unsigned integer (FFT).      |  |  |

### FFT Data Format (for AFFT and MFFT modes)

In both AFFT and MFFT modes, the X\_BUF, Y\_BUF, and Z\_BUF registers contain a calculated FFT bin magnitude. The values contained in buffer locations from 0 to 2047 represent the magnitude of frequency bins of size, depending on the AVG\_CNT value as shown in Table 19.

The magnitude (x) can be calculated from the value read by using the following equation:

$$x(1) = \left(\frac{2^{\frac{X_{BUF[1]}}{2048}}}{Number of \ FFT \ Averages}\right) \times 0.9535 \ mg$$

This formula is consistent for the y and z buffer values. Table 13 and Table 43 show the data formatting examples for FFT mode conversions from the X\_BUF value to acceleration.

When reading the X\_BUF register (as well as Y\_BUF and Z\_BUF), BUF\_PNTR automatically advances from 0 to 2047. The FFT data is unsigned 16-bit data.

| Table 13. FFT Magnitude Conversion from Register Value, |

|---------------------------------------------------------|

| Data Format Examples                                    |

| FFT Buffer Read Value (Bits) | FFT Averages | Magnitude           |

|------------------------------|--------------|---------------------|

| 0x0001                       | 1            | 0.953823 m <i>g</i> |

| 0x0002                       | 1            | 0.954146 m <i>g</i> |

| 0x00FF                       | 1            | 1.039447 m <i>g</i> |

| 0x7D00                       | 1            | 48.18528 g          |

| 0x0001                       | 2            | 0.476911 m <i>g</i> |

| 0x0002                       | 2            | 0.477073 m <i>g</i> |

| 0x00FF                       | 2            | 0.519724 m <i>g</i> |

| 0x0005                       | 4            | 0.238779 m <i>g</i> |

| 0x05FF                       | 4            | 0.400762 m <i>g</i> |

| 0x7530                       | 4            | 6.121809 <i>g</i>   |

| 0x00FF                       | 8            | 0.129931 m <i>g</i> |

| 0x7D00                       | 8            | 6.02316 g           |

| 0x7D00                       | 16           | 3.01158 g           |

| 0xAFCE                       | 128          | 30.65768 g          |

### **RTS Data Format**

In RTS mode, continuous data is burst out of the SPI interface. Each data frame consists of 32 samples each of x-, y-, and z-axis accelerometer data plus a frame header, temperature reading, status bits, and a 16-bit cyclical redundancy check (CRC) code. To calculate CRC, the CCITT-16 bit algorithm with an initial seed of 0xFFFF is used. Each data sample is 16-bit, twos complement acceleration data by default with a resolution of 1 LSB = 1.907 mg. It is important that the external host device is able to retrieve the burst data in a sufficient time allotment, which is approximately 135  $\mu$ s per data frame. No internal corrections are applied to this data. Therefore, the data may deviate from the results of other capture modes. Data is unsigned and must be offset (subtract) by 0x8000 to obtain  $\pm g$  (signed data).

When first entering RTS mode capture, the first eight samples are all 0s and the CRC for the first frame is invalid. Anytime a frame is skipped (not read), the subsequent frame CRC is invalid. It is recommended that the first frame be ignored and data for the second frame and all subsequent frames be used.

In RTS mode, the default sample rate is 220 kSPS. Users can set the decimation ratio or select from preset sample rates using the RT\_CTRL register according to Table 56 and Table 57.

### Data Sheet

Table 14 shows several examples of how to translate RTS data values, assuming nominal sensitivity and zero bias error.

| 0                                       |        |        |                     |  |  |  |  |  |  |

|-----------------------------------------|--------|--------|---------------------|--|--|--|--|--|--|

| Table 14. RTS Mode Data Format Examples |        |        |                     |  |  |  |  |  |  |

| Acceleration (g)                        | LSB    | Hex.   | Binary              |  |  |  |  |  |  |

| +62.532                                 | 65,535 | 0xFFFF | 1111 1111 1111 1111 |  |  |  |  |  |  |

| +50                                     | 58,967 | 0xE657 | 1110 0110 0101 0111 |  |  |  |  |  |  |

| +0.003816                               | 32,770 | 0x8002 | 1000 0000 0000 0010 |  |  |  |  |  |  |

| +0.001908                               | 32,769 | 0x8001 | 1000 0000 0000 0001 |  |  |  |  |  |  |

| 0                                       | 32,768 | 0x8000 | 1000 0000 0000 0000 |  |  |  |  |  |  |

| -0.001908                               | 32,767 | 0x7FFF | 0111 1111 1111 1111 |  |  |  |  |  |  |

| -0.003816                               | 32,766 | 0x7FFE | 0111 1111 1111 1110 |  |  |  |  |  |  |

| -50                                     | 6567   | 0x19A7 | 0001 1001 1010 0111 |  |  |  |  |  |  |

| -62.534                                 | 0      | 0x0000 | 0000 0000 0000 0000 |  |  |  |  |  |  |

### USER INTERFACE

The user interface includes a number of important functions: a data communications port, a trigger input, a busy indicator, and two alarm indicator signals.

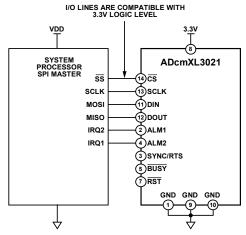

Data communication between an embedded processor (master) and the ADcmXL3021 takes place through the SPI, which includes the chip select  $\overline{(CS)}$ , serial clock (SCLK), data input (DIN), and data output (DOUT) pins (see Table 5).

The SYNC/RTS (see Table 5) pin provides user triggering options in manual triggering modes. The alarm pins, ALM1 and ALM2, are configurable to alert the user of an event that exceeds a user defined threshold of a parameter.

The SYNC/RTS pin is used in RTS mode to support start and stop control over data capture and analysis operations. The BUSY pin (see Table 5) provides an indication of internal operation when the ADcmXL3021 is executing a command. This signal helps the master processor avoid SPI communication when the ADcmXL3021 cannot support a response and can trigger an external data acquisition after data capture and analysis events are complete.

The ADcmXL3021 uses an SPI for communication, which enables simple connection with most embedded processor platforms, as shown in Figure 40.

Figure 40. Electrical Hookup Diagram

The register structure uses a paged addressing scheme that contains seven pages, with each page containing 64 register locations. Each register is 16 bits wide, with each 2-byte word having its own unique address within the memory map of that page. The SPI port has access to one page at a time. Select the page to activate for SPI access by writing the corresponding code to the PAGE\_ID register. Read the PAGE\_ID register to determine which page is currently active. Table 15 displays the PAGE\_ID contents for each page and the basic functions. The PAGE\_ID register is located at Address 0x00 on each page.

#### Table 15. User Register Page Assignments

| Page No. | PAGE_ID | Function                        |

|----------|---------|---------------------------------|

| 0        | 0x00    | Configuration, data acquisition |

| 1        | 0x01    | FIR Filter Bank A               |

| 2        | 0x02    | FIR Filter Bank B               |

| 3        | 0x03    | FIR Filter Bank C               |

| 4        | 0x04    | FIR Filter Bank D               |

| 5        | 0X05    | FIR Filter Bank E               |

| 6        | 0x06    | FIR Filter Bank F               |

The factory default configuration for the BUSY pin provides a busy indicator signal that transitions high when an event completes and data is available for user access and remains low during processing.

| ssor Pin Names and Functions |

|------------------------------|

|                              |

| Pin Name   | Function                            |

|------------|-------------------------------------|

| SS         | Slave select                        |

| SCLK       | Serial clock                        |

| MOSI       | Master output, slave input          |

| MISO       | Master input, slave output          |

| IRQ1, IRQ2 | Interrupt request inputs (optional) |

The ADcmXL3021 SPI supports full duplex serial communication (simultaneous transmit and receive) and uses the bit sequence shown in Figure 44. Table 17 shows a list of the most common settings that control the operation of SPI-compatible ports in most embedded processor platforms.

Embedded processors typically use control registers to configure serial ports for communicating with SPI slave devices, such as the ADcmXL3021. Table 17 lists settings that describe the SPI protocol of the ADcmXL3021. The initialization routine of the master processor typically establishes these settings using firmware commands to write them into the serial control registers.

### Table 17. Generic Master Processor SPI Settings

| <b>Processor Setting</b> | Description                                |

|--------------------------|--------------------------------------------|

| Master                   | ADcmXL3021operates as a slave.             |

| SCLK Rate $\leq$ 14 MHz  | Bit rate setting.                          |

| SPI Mode 3               | Clock polarity/phase (CPOL = 1, CPHA = 1). |

| MSB First                | Bit sequence.                              |

| 16-Bit Mode              | Shift register/data length.                |

| Readout Formatting       | Little Endian.                             |

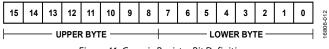

Table 20 lists user registers with lower byte addresses. Each register consists of two bytes. Each byte has a unique 7-bit address. Figure 41 relates the bits of each register to the upper and lower addresses.

Figure 41. Generic Register Bit Definitions

### **Register Structure**

All communication with the ADcmXL3021 involves accessing the user registers. The register structure contains both output data and control registers. The output data registers include the latest sensor data, alarm information, error flags, and identification data. The control register contained in Page 0 includes configurable options, such as time domain averaging, FFT averaging, filtering, alarm parameters, diagnostics, and data collection mode settings. Each user accessible register has two bytes (upper and lower), and each byte has a unique address. See Table 20 for a detailed list of all user registers, along with the corresponding addresses.

All communication between the ADcmXL3021 and an external processor involves either reading or writing these 16 bit user registers.

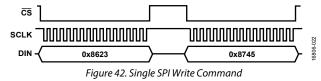

### SPI Write Commands

User control registers govern many internal operations. The DIN bit sequence in Figure 44 provides a description to write to these registers. Each configuration register contains 16 bits (two bytes). Bits[7:0] contain the low byte, and Bits[15:8] contain the high byte of each register. Each byte has a unique address in the user register map (see Table 20). Updating the contents of a register requires writing both bytes in the following sequence: low byte first, high byte second. There are three parts to coding a SPI command (see Figure 44) that write a new byte of data to a register: the write bit (R/W = 1), the address of the byte [A6:A0], followed by the new data for that register address [D7:D0].

Figure 42 provides a coding example for writing 0x2345 to the FFT\_AVG1 register, the 0x8623 command writes 0x23 to Address 0x06 (lower byte) and the 0x8745 command writes 0x45 to Address 0x07 (upper byte).

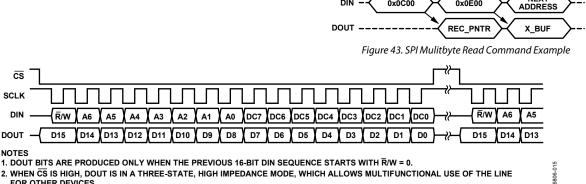

### SPI Read Commands

A single register read requires two 16-bit SPI cycles that use the bit assignments shown in Figure 44. The beginning sequence sets R/W = 0 and communicates the target address (Bits[A6:A0]). Bits[DC7:DC0] are don't care bits for a read DIN sequence. DOUT clocks out the requested register contents during the second sequence. The second sequence can also use DIN to set up the next read.